Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Obsolete                                                  |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |  |

| Number of I/O              | 17                                                        |  |

| Program Memory Size        | 8KB (8K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 1K x 8                                                    |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |

| Mounting Type              | Through Hole                                              |  |

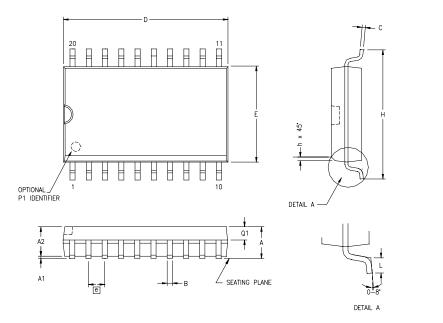

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081aph020sc |  |

## **Low-Power Operational Amplifier**

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

### Internal Precision Oscillator

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

## **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

# **Low Voltage Detector**

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

# **On-Chip Debugger**

The Z8 Encore! XP<sup>®</sup> F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints, and executing code.

PS022825-0908 Overview

Table 3. Pin Characteristics (20- and 28-pin Devices) (Continued)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction      | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down            | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                            | 5 V<br>Tolerance                        |

|--------------------|-----------|-------------------------|---------------------------------------|--------------------|-------------------------------------------------|------------------------------|-------------------------------------------------|-----------------------------------------|

| PC[7:0]            | I/O       | I                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | PC[7:3]<br>unless<br>pullups<br>enabled |

| RESET/PD0          | I/O       | I/O (defaults to RESET) | Low (in<br>Reset<br>mode)             | Yes (PD0 only)     | Programmable<br>for PD0; always<br>on for RESET | Yes                          | Programmable<br>for PD0; always<br>on for RESET | Yes, unless pullups enabled             |

| VDD                | N/A       | N/A                     | N/A                                   | N/A                |                                                 |                              | N/A                                             | N/A                                     |

| VSS                | N/A       | N/A                     | N/A                                   | N/A                |                                                 |                              | N/A                                             | N/A                                     |

**Note:** *PB6* and *PB7* are available only in those devices without *ADC*.

**Table 4. Pin Characteristics (8-Pin Devices)**

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                      | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal Pull-<br>up<br>or Pull-down            | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                            | 5 V<br>Tolerance                   |

|--------------------|-----------|-------------------------------------------------------------------------|---------------------------------------|--------------------|-------------------------------------------------|------------------------------|-------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during reset<br>if key<br>sequence<br>detected) | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | I                                                                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| RESET/PA2          | I/O       | I/O (defaults<br>to RESET)                                              | Low (in<br>Reset<br>mode)             | Yes                | Programmable<br>for PA2; always<br>on for RESET | Yes                          | Programmable<br>for PA2; always<br>on for RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                       | N/A                                   | Yes                | Programmable<br>Pull-up                         | Yes                          | Yes,<br>Programmable                            | Yes, unless<br>pull-ups<br>enabled |

| $V_{DD}$           | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                             | N/A                          | N/A                                             | N/A                                |

| $V_{SS}$           | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                             | N/A                          | N/A                                             | N/A                                |

PS022825-0908 Pin Description

Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

| Port   | Pin                            | Mnemonic                | Alternate Function Description                         | Alternate Function<br>Set Register AFS1 |

|--------|--------------------------------|-------------------------|--------------------------------------------------------|-----------------------------------------|

| Port C | PC0                            | Reserved                |                                                        | AFS1[0]: 0                              |

|        |                                | ANA4/CINP/LED<br>Drive  | ADC or Comparator Input, or LED drive                  | AFS1[0]: 1                              |

|        | PC1                            | Reserved                |                                                        | AFS1[1]: 0                              |

|        |                                | ANA5/CINN/ LED<br>Drive | ADC or Comparator Input, or LED drive                  | AFS1[1]: 1                              |

|        | PC2                            | Reserved                |                                                        | AFS1[2]: 0                              |

|        | ANA6/LED/<br>VREF*<br>PC3 COUT |                         | ADC Analog Input or LED Drive or ADC Voltage Reference | AFS1[2]: 1                              |

|        |                                |                         | Comparator Output                                      | AFS1[3]: 0                              |

|        |                                | LED                     | LED drive                                              | AFS1[3]: 1                              |

|        | PC4                            | Reserved                |                                                        | AFS1[4]: 0                              |

|        |                                | LED                     | LED Drive                                              | AFS1[4]: 1                              |

|        | PC5                            | Reserved                |                                                        | AFS1[5]: 0                              |

|        |                                | LED                     | LED Drive                                              | AFS1[5]: 1                              |

|        | PC6                            | Reserved                |                                                        | AFS1[6]: 0                              |

|        | LED                            |                         | LED Drive                                              | AFS1[6]: 1                              |

|        | PC7                            | Reserved                |                                                        | AFS1[7]: 0                              |

|        |                                | LED                     | LED Drive                                              | AFS1[7]: 1                              |

**Note:** Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A–D Alternate Function Sub-Registers on page 47 must also be enabled.

\*VREF is available on PC2 in 20-pin parts only.

PAFS1[7:0]—Port Alternate Function Set 1

0 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

1 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

## Port A-D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register (Table 26) is accessed through the Port A–D Control register by writing 08H to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15.

Note:

Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

| BITS  | 7        | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | PAFS27   | PAFS26                                                                                | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |  |  |

| RESET |          | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device)                    |        |        |        |        |        |        |  |  |

| R/W   | R/W      | R/W         R/W         R/W         R/W         R/W         R/W         R/W           |        |        |        |        |        |        |  |  |

| ADDR  | If 08H i | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |  |

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 15.

1 = Port Alternate Function selected as defined in Table 15.

# Port A-C Input Data Registers

Reading from the Port A–C Input Data registers (Table 27) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

Table 27. Port A–C Input Data Registers (PxIN)

| BITS      | 7            | 6                | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------|--------------|------------------|------|------|------|------|------|------|--|

| FIELD     | PIN7         | PIN6             | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET     | Х            | Х                | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W       | R            | R                | R    | R    | R    | R    | R    | R    |  |

| ADDR      |              | FD2H, FD6H, FDAH |      |      |      |      |      |      |  |

| X = Undef | = Undefined. |                  |      |      |      |      |      |      |  |

To avoid re-triggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, it is recommended that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as given in the following coding sample:

```

CLEARWDT:

LDX r0, RSTSTAT ; read reset status register to clear wdt bit

BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

```

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 33) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending.

Table 33. Interrupt Request 0 Register (IRQ0)

| BITS  | 7        | 6    | 5   | 4     | 3     | 2        | 1        | 0    |

|-------|----------|------|-----|-------|-------|----------|----------|------|

| FIELD | Reserved | T1I  | TOI | U0RXI | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0    | 0   | 0     | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W  | R/W | R/W   | R/W   | R/W      | R/W      | R/W  |

| ADDR  |          | FC0H |     |       |       |          |          |      |

Reserved—Must be 0.

T1I—Timer 1 Interrupt Request

0 = No interrupt request is pending for Timer 1.

1 = An interrupt request from Timer 1 is awaiting service.

T0I—Timer 0 Interrupt Request

0 =No interrupt request is pending for Timer 0.

1 = An interrupt request from Timer 0 is awaiting service.

PS022825-0908 Interrupt Controller

110 = 64 cycles delay

111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

## Timer 0-1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode (Table 49).

Table 49. Timer 0-1 Control Register 1 (TxCTL1)

| BITS  | 7   | 6          | 5   | 4          | 3   | 2   | 1   | 0   |

|-------|-----|------------|-----|------------|-----|-----|-----|-----|

| FIELD | TEN | TPOL       |     | PRES TMODE |     |     |     |     |

| RESET | 0   | 0          | 0   | 0          | 0   | 0   | 0   | 0   |

| R/W   | R/W | R/W        | R/W | R/W        | R/W | R/W | R/W | R/W |

| ADDR  |     | F07H, F0FH |     |            |     |     |     |     |

TEN—Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

### **ONE-SHOT mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

### **CONTINUOUS** mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

### **COUNTER** mode

If the timer is enabled the Timer Output signal is complemented after timer reload.

0 = Count occurs on the rising edge of the Timer Input signal.

1 = Count occurs on the falling edge of the Timer Input signal.

PS022825-0908 Timers

### **CAPTURE RESTART mode**

- 0 = Count is captured on the rising edge of the Timer Input signal.

- 1 = Count is captured on the falling edge of the Timer Input signal.

## **COMPARATOR COUNTER mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload. Also:

- 0 =Count is captured on the rising edge of the comparator output.

- 1 = Count is captured on the falling edge of the comparator output.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, TxOUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the Port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

### PRES—Prescale value

The timer input clock is divided by 2<sup>PRES</sup>, where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

- 000 = Divide by 1

- 001 = Divide by 2

- 010 = Divide by 4

- 011 = Divide by 8

- 100 = Divide by 16

- 101 = Divide by 32

- 110 = Divide by 64

- 111 = Divide by 128

### TMODE—Timer mode

This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of the timer. TMODEHI is the most significant bit of the Timer mode selection value. The entire operating mode bits are expressed as {TMODEHI, TMODE[2:0]}. The TMODEHI is bit 7 of the TxCTL0 register while TMODE[2:0] is the lower 3 bits of the TxCTL1 register.

- 0000 = ONE-SHOT mode

- 0001 = CONTINUOUS mode

- 0010 = COUNTER mode

- 0011 = PWM SINGLE OUTPUT mode

- 0100 = CAPTURE mode

- 0101 = COMPARE mode

- 0110 = GATED mode

- 0111 = CAPTURE/COMPARE mode

PS022825-0908 **Timers**

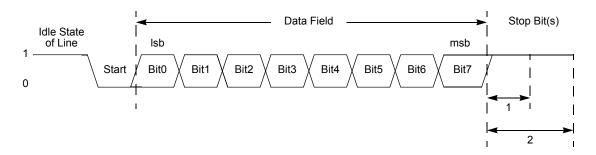

Figure 11. UART Asynchronous Data Format without Parity

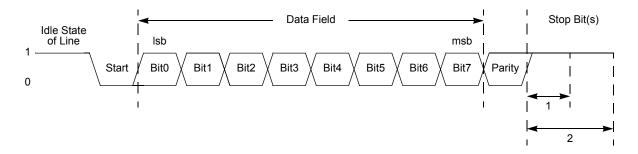

Figure 12. UART Asynchronous Data Format with Parity

## Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

# **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) register (Table 65) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

Table 65. UART Transmit Data Register (U0TXD)

| BITS  | 7 | 6    | 5 | 4 | 3  | 2 | 1 | 0 |  |  |

|-------|---|------|---|---|----|---|---|---|--|--|

| FIELD |   |      |   | T | (D |   |   |   |  |  |

| RESET | Х | X    |   |   |    |   |   |   |  |  |

| R/W   | W | W    | W | W | W  | W | W | W |  |  |

| ADDR  |   | F40H |   |   |    |   |   |   |  |  |

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

# **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) register (Table 66). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

Table 66. UART Receive Data Register (U0RXD)

| BITS      | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|------------|---|---|---|---|---|---|---|--|

| FIELD     | RXD        |   |   |   |   |   |   |   |  |

| RESET     | Х          | X | Х | X | Х | Х | Х | Х |  |

| R/W       | R          | R | R | R | R | R | R | R |  |

| ADDR      | F40H       |   |   |   |   |   |   |   |  |

| X = Undef | Indefined. |   |   |   |   |   |   |   |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

```

nop     ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definitions**

## **Comparator Control Register**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

Table 75. Comparator Control Register (CMP0)

| BITS  | 7      | 6      | 5      | 4   | 3   | 2   | 1                    | 0                        |

|-------|--------|--------|--------|-----|-----|-----|----------------------|--------------------------|

| FIELD | INPSEL | INNSEL | REFLVL |     |     |     | Reserved (<br>REFLVL | 20-/28-pin)<br>_ (8-pin) |

| RESET | 0      | 0      | 0      | 1   | 0   | 1   | 0                    | 0                        |

| R/W   | R/W    | R/W    | R/W    | R/W | R/W | R/W | R/W                  | R/W                      |

| ADDR  | F90H   |        |        |     |     |     |                      |                          |

INPSEL—Signal Select for Positive Input

0 = GPIO pin used as positive comparator input

1 = temperature sensor used as positive comparator input

INNSEL—Signal Select for Negative Input

0 = internal reference disabled, GPIO pin used as negative comparator input

1 = internal reference enabled as negative comparator input

REFLVL—Internal Reference Voltage Level (this reference is independent of the ADC voltage reference). Note that the 8-pin devices contain two additional LSBs for increased resolution.

For 20-/28-pin devices:

```

0000 = 0.0 V

0001 = 0.2 V

0010 = 0.4 V

0011 = 0.6 V

0100 = 0.8 V

0101 = 1.0 V (Default)

0110 = 1.2 V

0111 = 1.4 V

1000 = 1.6 V

```

PS022825-0908 Comparator

150

## Flash Status Register

The Flash Status (FSTAT) register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status register shares its Register File address with the Write-only Flash Control register.

Table 79. Flash Status Register (FSTAT)

| BITS  | 7    | 6     | 5     | 4         | 3 | 2 | 1 | 0 |  |

|-------|------|-------|-------|-----------|---|---|---|---|--|

| FIELD | Rese | erved | FSTAT |           |   |   |   |   |  |

| RESET | 0    | 0     | 0     | 0 0 0 0 0 |   |   |   |   |  |

| R/W   | R    | R     | R     | R         | R | R | R | R |  |

| ADDR  |      | FF8H  |       |           |   |   |   |   |  |

Reserved—Must be 0.

FSTAT—Flash Controller Status

000000 = Flash Controller locked

000001 = First unlock command received (73H written)

000010 = Second unlock command received (8CH written)

000011 = Flash Controller unlocked

000100 = Sector protect register selected

001xxx = Program operation in progress

010xxx = Page erase operation in progress

100xxx = Mass erase operation in progress

# Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

PS022825-0908 Flash Memory

**Table 117. Bit Manipulation Instructions**

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| TCM      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| TM       | dst, src    | Test Under Mask                                      |

| TMX      | dst, src    | Test Under Mask using Extended Addressing            |

**Table 118. Block Transfer Instructions**

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

## **Table 119. CPU Control Instructions**

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| El       | _        | Enable Interrupts     |

| HALT     | _        | Halt Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

PS022825-0908 eZ8 CPU Instruction Set

Table 124. eZ8 CPU Instruction Summary (Continued)

| Assembly        | Symbolic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Addres    | s Mode   | Opcode(s) | ) Flags |          |   |      |   |   | Fetch  | Instr. |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-----------|---------|----------|---|------|---|---|--------|--------|

| Mnemonic        | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dst       | src      | (Hex)     | С       | Z        | s | ٧    | D | Н | Cycles |        |

| OR dst, src     | $dst \leftarrow dst \ OR \ src$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r         | r        | 42        | -       | *        | * | 0    | _ | - | 2      | 3      |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r         | lr       | 43        | -       |          |   |      |   |   | 2      | 4      |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R         | R        | 44        | -       |          |   |      |   |   | 3      | 3      |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R         | IR       | 45        | -       |          |   |      |   |   | 3      | 4      |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R         | IM       | 46        | -       |          |   |      |   |   | 3      | 3      |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IR        | IM       | 47        | -       |          |   |      |   |   | 3      | 4      |

| ORX dst, src    | $dst \leftarrow dst \ OR \ src$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ER        | ER       | 48        | -       | *        | * | 0    | _ | _ | 4      | 3      |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ER        | IM       | 49        | -       |          |   |      |   |   | 4      | 3      |

| POP dst         | dst ← @SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R         |          | 50        | -       | -        | _ | -    | - | - | 2      | 2      |

|                 | SP ← SP + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IR        |          | 51        | -       |          |   |      |   |   | 2      | 3      |

| POPX dst        | dst ← @SP<br>SP ← SP + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ER        |          | D8        | -       | -        | _ | _    | - | - | 3      | 2      |

| PUSH src        | SP ← SP – 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R         |          | 70        | -       | -        | _ | -    | - | - | 2      | 2      |

|                 | @SP ← src                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IR        |          | 71        | -       |          |   |      |   |   | 2      | 3      |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IM        |          | IF70      | _       |          |   |      |   |   | 3      | 2      |

| PUSHX src       | SP ← SP – 1<br>@SP ← src                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ER        |          | C8        | _       | _        | _ | _    | _ | _ | 3      | 2      |

| RCF             | C ← 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |          | CF        | 0       | _        | _ | _    | _ | _ | 1      | 2      |

| RET             | PC ← @SP<br>SP ← SP + 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |          | AF        | -       | -        | _ | _    | - | - | 1      | 4      |

| RL dst          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R         |          | 90        | *       | *        | * | *    | _ | _ | 2      | 2      |

|                 | C D7 D6 D5 D4 D3 D2 D1 D0 dst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IR        |          | 91        | =       |          |   |      |   |   | 2      | 3      |