Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081ash020sc |

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

vii

| Watchdog Timer Time-Out Response                         |         |

|----------------------------------------------------------|---------|

| Watchdog Timer Reload Unlock Sequence                    |         |

| Watchdog Timer Calibration                               |         |

| Watchdog Timer Control Register Definitions              |         |

| Watchdog Timer Control Register                          |         |

| Watchdog Timer Reload Upper, High and Low Byte Registers |         |

| Universal Asynchronous Receiver/Transmitter              | 97      |

| Architecture                                             |         |

| Operation                                                | 98      |

| Data Format                                              | 98      |

| Transmitting Data using the Polled Method                |         |

| Transmitting Data using the Interrupt-Driven Method      |         |

| Receiving Data using the Polled Method                   |         |

| Receiving Data using the Interrupt-Driven Method         |         |

| Clear To Send (CTS) Operation                            |         |

| MULTIPROCESSOR (9-bit) Mode                              |         |

| External Driver Enable                                   |         |

| UART Interrupts                                          |         |

| UART Baud Rate Generator                                 |         |

| UART Control Register Definitions                        |         |

| UART Control 0 and Control 1 Registers                   |         |

| UART Status 0 Register                                   |         |

| UART Status 1 Register                                   |         |

| UART Transmit Data Register                              |         |

| UART Receive Data Register                               |         |

| UART Address Compare Register                            |         |

| UART Baud Rate High and Low Byte Registers               |         |

| Infrared Encoder/Decoder                                 | 117     |

| Architecture                                             | 117     |

| Operation                                                | 445     |

| Transmitting IrDA Data                                   |         |

| Receiving IrDA Data                                      |         |

| Infrared Encoder/Decoder Control Register Definitions    |         |

| Analog-to-Digital Converter                              | 121     |

| Architecture                                             |         |

| Operation                                                |         |

| Data Format                                              |         |

| =                                                        | · · · · |

PS022825-0908 Table of Contents

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Flash Sector Protect Register                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Flash Option Bits                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                 |

| Operation1Option Bit Configuration By Reset1Option Bit Types1Reading the Flash Information Page1Flash Option Bit Control Register Definitions1Trim Bit Address Register1Trim Bit Data Register1Flash Option Bit Address Space1Flash Program Memory Address 0000H1Flash Program Memory Address 0001H1Trim Bit Address Space1Trim Bit Address Space1Trim Bit Address 0000H1                                        | 53<br>54<br>55<br>55<br>56<br>56<br>56<br>58<br>58 |

| Trim Bit Address 0001H       1         Trim Bit Address 0002H       1         Trim Bit Address 0003H       1         Trim Bit Address 0004H       1         Zilog Calibration Data       1         ADC Calibration Data       1         Temperature Sensor Calibration Data       1         Watchdog Timer Calibration Data       1         Serialization Data       1         Randomized Lot Identifier       1 | 59<br>61<br>61<br>64<br>64<br>65                   |

| Non-Volatile Data Storage                                                                                                                                                                                                                                                                                                                                                                                        | 69                                                 |

| Operation       1         NVDS Code Interface       1         Byte Write       1         Byte Read       1         Power Failure Protection       1         Optimizing NVDS Memory Usage for Execution Speed       1                                                                                                                                                                                             | 69<br>69<br>70<br>71                               |

| On-Chip Debugger1                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                 |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                        | 73<br>74<br>74<br>75                               |

PS022825-0908 Table of Contents

**z**ilog\*

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

Table 5. Z8 Encore! XP F082A Series Program Memory Maps

| Program Memory Address (Hex) | Function                     |

|------------------------------|------------------------------|

| Z8F082A and Z8F081A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-1FFF                    | Program Memory               |

| Z8F042A and Z8F041A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-0FFF                    | Program Memory               |

PS022825-0908 Address Space

Table 5. Z8 Encore! XP F082A Series Program Memory Maps (Continued)

| Program Memory Address (Hex)                | Function                     |

|---------------------------------------------|------------------------------|

| Z8F022A and Z8F021A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-07FF                                   | Program Memory               |

| Z8F012A and Z8F011A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-03FF                                   | Program Memory               |

| * See Table 32 on page 56 for a list of the | e interrupt vectors.         |

### **Data Memory**

The Z8 Encore! XP F082A Series does not use the eZ8 CPU's 64 KB Data Memory address space.

#### Flash Information Area

Table 6 on page 18 describes the Z8 Encore! XP F082A Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FEOOH to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Infor-

PS022825-0908 Address Space

vector address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

**Table 10. Stop Mode Recovery Sources and Resulting Action**

| Operating Mode | Stop Mode Recovery Source                                                   | Action                                                               |

|----------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP mode      | Watchdog Timer time-out when configured for Reset                           | Stop Mode Recovery                                                   |

|                | Watchdog Timer time-out when configured for interrupt                       | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO Port pin enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

|                | Assertion of external RESET Pin                                             | System Reset                                                         |

|                | Debug Pin driven Low                                                        | System Reset                                                         |

#### Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

### **Stop Mode Recovery Using a GPIO Port Pin Transition**

Each of the GPIO Port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

Note:

The SMR pulses shorter than specified does not trigger a recovery (see Table 131 on page 229). When this happens, the STOP bit in the Reset Status (RSTSTAT) register is set to 1.

$\bigwedge$

**Caution:** In STOP mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can

To avoid re-triggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, it is recommended that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as given in the following coding sample:

```

CLEARWDT:

LDX r0, RSTSTAT ; read reset status register to clear wdt bit

BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

```

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

#### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 33) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 register to determine if any interrupt requests are pending.

Table 33. Interrupt Request 0 Register (IRQ0)

| BITS  | 7        | 6   | 5   | 4         | 3                     | 2   | 1        | 0    |  |

|-------|----------|-----|-----|-----------|-----------------------|-----|----------|------|--|

| FIELD | Reserved | T1I | TOI | U0RXI     | ORXI U0TXI Reserved F |     | Reserved | ADCI |  |

| RESET | 0        | 0   | 0   | 0         | 0                     | 0   | 0        | 0    |  |

| R/W   | R/W      | R/W | R/W | R/W R/W R |                       | R/W | R/W      | R/W  |  |

| ADDR  |          |     |     | FC        | 0H                    |     |          |      |  |

Reserved—Must be 0.

T1I—Timer 1 Interrupt Request

0 = No interrupt request is pending for Timer 1.

1 = An interrupt request from Timer 1 is awaiting service.

T0I—Timer 0 Interrupt Request

0 =No interrupt request is pending for Timer 0.

1 = An interrupt request from Timer 0 is awaiting service.

PS022825-0908 Interrupt Controller

zilog 68

PS022825-0908 Interrupt Controller

#### Receiving Data using the Interrupt-Driven Method

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore!<sup>®</sup> devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity.

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR mode bits MPMD[1:0].

# **Analog-to-Digital Converter**

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL mode.

- 10-bit resolution in SINGLE-ENDED mode.

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports.

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral.

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports.

- Low-power operational amplifier (LPO).

- Interrupt on conversion complete.

- Bandgap generated internal voltage reference with two selectable levels.

- Manual in-circuit calibration is possible employing user code (offset calibration).

- Factory calibrated for in-circuit error compensation.

#### **Architecture**

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes).

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes).

- LPO output with full pin access to the feedback path.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register may be written simultaneously:

- Write to the ANAIN [3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1.

- Set CEN to 1 to start the conversions.

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete.

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:3]}.

- Sends an interrupt request to the Interrupt Controller denoting conversion complete.

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

#### Interrupts

The ADC is able to interrupt the CPU when a conversion has been completed. When the ADC is disabled, no new interrupts are asserted; however, an interrupt pending when the ADC is disabled is not cleared.

# Calibration and Compensation

The Z8 Encore!  $XP^{\circledR}$  F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, you can perform your own calibration, storing the values into Flash themselves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL mode operation.

```

1001 = 1.8 V

1010–1111 = Reserved

```

#### For 8-pin devices:

000000 = 0.00 V

000001 = 0.05 V

000010 = 0.10 V

000011 = 0.15 V

000100 = 0.20 V

000101 = 0.25 V

000110 = 0.30 V

000111 = 0.35 V

001000 = 0.40 V

001001 = 0.45 V

001010 = 0.50 V

001011 = 0.55 V

001100 = 0.60 V

001101 = 0.65 V

001110 = 0.70 V

001111 = 0.75 V

001111 - 0.75 V

010000 = 0.80 V

010001 = 0.85 V

010010 = 0.90 V

010011 = 0.95 V

010100 = 1.00 V (Default)

010101 = 1.05 V

010110 = 1.10 V

010111 = 1.15 V

011000 = 1.20 V

011001 = 1.25 V

011010 = 1.30 V

011011 = 1.35 V

011100 = 1.40 V

011101 = 1.45 V

011110 = 1.50 V

011110 - 1.50 V0111111 = 1.55 V

100000 = 1.60 V

100001 = 1.65 V

100001 = 1.33 V100010 = 1.70 V

100011 = 1.75 V

100100 = 1.80 V

PS022825-0908 Comparator

zilog.

153

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F082A Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Oscillator mode selection-for high, medium, and low power crystal oscillators, or external RC oscillator

- Factory trimming information for the internal precision oscillator and low voltage detection

- Factory calibration values for ADC, temperature sensor, and Watchdog Timer compensation

- Factory serialization and randomized lot identifier (optional)

# **Operation**

### **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F082A Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

PS022825-0908 Flash Option Bits

Reserved—Must be 1.

#### LVD TRIM—Low Voltage Detect Trim

This trimming affects the low voltage detection threshold. Each LSB represents a 50 mV change in the threshold level. Alternatively, the low voltage threshold may be computed from the options bit value by the following equation:

LVD\_LVL =

$$3.6 \text{ V} - \text{LVD} \text{TRIM} \times 0.05 \text{ V}$$

| LV          | /D Threshold | (V)                   |

|-------------|--------------|-----------------------|

| LVD_TRIM    | Typical      | Description           |

| 00000       | 3.60         | Maximum LVD threshold |

| 00001       | 3.55         |                       |

| 00010       | 3.50         |                       |

| 00011       | 3.45         |                       |

| 00100       | 3.40         |                       |

| 00101       | 3.35         |                       |

| 00110       | 3.30         |                       |

| 00111       | 3.25         |                       |

| 01000       | 3.20         |                       |

| 01001       | 3.15         |                       |

| 01010       | 3.10         | Default on Reset      |

| 01011       | 3.05         |                       |

| 01100       | 3.00         |                       |

| 01101       | 2.95         |                       |

| 01110       | 2.90         |                       |

| 01111       | 2.85         |                       |

| 10000       | 2.80         |                       |

| 10001       | 2.75         |                       |

| 10010       | 2.70         |                       |

| 10011       | 2.70         |                       |

| to<br>11111 | to<br>1.65   | Minimum LVD threshold |

PS022825-0908 Flash Option Bits

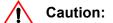

Figure 27 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20 MHz. Recommended 20 MHz crystal specifications are provided in Table 110. Printed circuit board layout must add no more than 4 pF of stray capacitance to either the  $X_{IN}$  or  $X_{OUT}$  pins. If oscillation does not occur, reduce the values of capacitors  $C_1$  and  $C_2$  to decrease loading.

Figure 27. Recommended 20 MHz Crystal Oscillator Configuration

**Table 110. Recommended Crystal Oscillator Specifications**

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | Ω     | Maximum  |

| Load Capacitance (C <sub>L</sub> )  | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

PS022825-0908 Crystal Oscillator

## **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 112. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 80   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 113. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

#### **eZ8 CPU Instruction Notation**

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 114.

PS022825-0908 eZ8 CPU Instruction Set

Table 124. eZ8 CPU Instruction Summary (Continued)

| Assembly<br>Mnemonic | Symbolic<br>Operation                                         | Addres        | Address Mode |                    | Flags |          |   |   |   |   | Fetch | Instr. |

|----------------------|---------------------------------------------------------------|---------------|--------------|--------------------|-------|----------|---|---|---|---|-------|--------|

|                      |                                                               | dst           | src          | Opcode(s)<br>(Hex) | С     | Z        | S | ٧ | D | Н |       | Cycles |

| XOR dst, src         | $dst \leftarrow dst \: XOR \: src$                            | r             | r            | B2                 | -     | *        | * | 0 | - | - | 2     | 3      |

|                      |                                                               | r             | Ir           | В3                 | -     |          |   |   |   |   | 2     | 4      |

|                      |                                                               | R             | R            | B4                 | -     |          |   |   |   |   | 3     | 3      |

|                      |                                                               | R             | IR           | B5                 | _     |          |   |   |   |   | 3     | 4      |

|                      |                                                               | R             | IM           | B6                 | _     |          |   |   |   |   | 3     | 3      |

|                      |                                                               | IR            | IM           | B7                 | _     |          |   |   |   |   | 3     | 4      |

| XORX dst, src        | $dst \leftarrow dst \ XOR \ src$                              | ER            | ER           | B8                 | -     | *        | * | 0 | _ | - | 4     | 3      |

|                      |                                                               | ER            | IM           | B9                 | _     |          |   |   |   |   | 4     | 3      |

| Flags Notation:      | * = Value is a function of<br>- = Unaffected<br>X = Undefined | of the result | of the o     | peration.          |       | Re<br>Se |   |   | ) |   |       |        |

PS022825-0908 eZ8 CPU Instruction Set

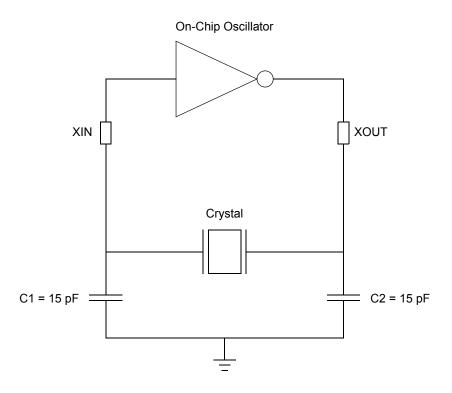

## **On-Chip Debugger Timing**

Figure 36 and Table 141 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

Table 141. On-Chip Debugger Timing

|                |                                  | Delay (ns) |         |  |

|----------------|----------------------------------|------------|---------|--|

| Parameter      | Abbreviation                     | Minimum    | Maximum |  |

| DBG            |                                  |            |         |  |

| T <sub>1</sub> | XIN Rise to DBG Valid Delay      | _          | 15      |  |

| T <sub>2</sub> | XIN Rise to DBG Output Hold Time | 2          | _       |  |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time | 5          | _       |  |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time  | 5          | _       |  |

PS022825-0908 Electrical Characteristics

# **Ordering Information**

Order the Z8 Encore! XP<sup>®</sup> F082A Series from Zilog<sup>®</sup>, using the following part numbers. For more information on ordering, please consult your local Zilog sales office. The Zilog website (<u>www.zilog.com</u>) lists all regional offices and provides additional Z8 Encore! XP product information.

| Part Number                                                                                                         | Flash | RAM  | NVDS | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------------------------------------------------------------------------------------|-------|------|------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP® F082A Series with 8 KB Flash, 10-Bit Analog-to-Digital Converter  Standard Temperature: 0 °C to 70°C |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020SC                                                                                                      | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020SC                                                                                                      | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | <u>'</u>       | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SC                                                                                                      | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SC                                                                                                      | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SC                                                                                                      | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SC                                                                                                      | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020SC                                                                                                      | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SC                                                                                                      | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SC                                                                                                      | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                                                                              |       |      |      |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EC                                                                                                      | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EC                                                                                                      | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EC                                                                                                      | 8 KB  | 1 KB | 0    | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EC                                                                                                      | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EC                                                                                                      | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EC                                                                                                      | 8 KB  | 1 KB | 0    | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EC                                                                                                      | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EC                                                                                                      | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EC                                                                                                      | 8 KB  | 1 KB | 0    | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                                                                            |       |      |      |           |            |                     |                     |                |            |                    |                     |

PS022825-0908 Ordering Information

| Part Number                                             | Flash | RAM  | NVDS  | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------------------------|-------|------|-------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082A Series with 4 KB Flash |       |      |       |           |            |                     |                     |                |            |                    |                     |

| Standard Temperature: 0 °C to 70 °C                     |       |      |       |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020SC                                          | 4 KB  | 1 KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020SC                                          | 4 KB  | 1 KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020SC                                          | 4 KB  | 1 KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020SC                                          | 4 KB  | 1 KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020SC                                          | 4 KB  | 1 KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020SC                                          | 4 KB  | 1 KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020SC                                          | 4 KB  | 1 KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020SC                                          | 4 KB  | 1 KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020SC                                          | 4 KB  | 1 KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                  |       |      |       |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020EC                                          | 4 KB  | 1 KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020EC                                          | 4 KB  | 1 KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020EC                                          | 4 KB  | 1 KB | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020EC                                          | 4 KB  | 1 KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020EC                                          | 4 KB  | 1 KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020EC                                          | 4 KB  | 1 KB | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020EC                                          | 4 KB  | 1 KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020EC                                          | 4 KB  | 1 KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020EC                                          | 4 KB  | 1 KB | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                |       |      |       |           |            |                     |                     |                |            |                    |                     |

PS022825-0908 Ordering Information

zilog

267

| register 201                                | RLC 206                                        |

|---------------------------------------------|------------------------------------------------|

| ADC control (ADCCTL) 130, 132               | rotate and shift instuctions 206               |

| ADC data high byte (ADCDH) 132              | rotate left 206                                |

| ADC data low bits (ADCDL) 133               | rotate left through carry 206                  |

| flash control (FCTL) 149, 155, 156          | rotate right 206                               |

| flash high and low byte (FFREQH and         | rotate right through carry 206                 |

| FREEQL) 152                                 | RP 202                                         |

| flash page select (FPS) 150, 151            | RR 201, 206                                    |

| flash status (FSTAT) 150                    | rr 201                                         |

| GPIO port A-H address (PxADDR) 46           | RRC 206                                        |

| GPIO port A-H alternate function sub-regis- |                                                |

| ters 48                                     |                                                |

| GPIO port A-H control address (PxCTL) 47    | S                                              |

| GPIO port A-H data direction sub-registers  | SBC 203                                        |

| 47                                          | SCF 204, 205                                   |

| OCD control 184                             | second opcode map after 1FH 219                |

| OCD status 185                              | set carry flag 204, 205                        |

| UARTx baud rate high byte (UxBRH) 114       | set register pointer 205                       |

| UARTx baud rate low byte (UxBRL) 114        | shift right arithmatic 207                     |

| UARTx Control 0 (UxCTL0) 108, 114           | <del>-</del>                                   |

| UARTx control 1 (UxCTL1) 109                | shift right logical 207 signal descriptions 11 |

| UARTx receive data (UxRXD) 113              |                                                |

| UARTx status 0 (UxSTAT0) 111                | single-shot conversion (ADC) 123               |

| UARTx status 1 (UxSTAT1) 112                | software trap 206                              |

| UARTx transmit data (UxTXD) 113             | source operand 202                             |

| Watchdog Timer control (WDTCTL) 31, 94,     | SP 202                                         |

| 136, 190                                    | SRA 207                                        |

| Watchdog Timer reload high byte (WDTH)      | src 202                                        |

| 95                                          | SRL 207                                        |

| Watchdog Timer reload low byte (WDTL)       | SRP 205                                        |

| 95                                          | stack pointer 202                              |

| Watchdog Timer reload upper byte (WD-       | STOP 205                                       |

| TU) 95                                      | STOP mode 33                                   |

| register file 15                            | stop mode 205                                  |

| register pair 201                           | Stop Mode Recovery                             |

| register pointer 202                        | sources 28                                     |

| reset                                       | using a GPIO port pin transition 29            |

| and stop mode characteristics 24            | using Watchdog Timer time-out 29               |

| and Stop Mode Recovery 23                   | stop mode recovery                             |

| carry flag 204                              | sources 30                                     |

| sources 25                                  | using a GPIO port pin transition 30            |

| RET 206                                     | SUB 203                                        |

| return 206                                  | subtract 203                                   |

| RL 206                                      | subtract - extended addressing 203             |

| NL ZUU                                      | subtract with carry 203                        |

PS022825-0908 Index