Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081asj020ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| General Purpose I/O Port Output Timing | 236 |

|----------------------------------------|-----|

| On-Chip Debugger Timing                | 237 |

| UART Timing                            | 238 |

| Packaging                              | 241 |

| Ordering Information                   | 251 |

| Index                                  | 261 |

| Customer Support                       | 271 |

### **Universal Asynchronous Receiver/Transmitter**

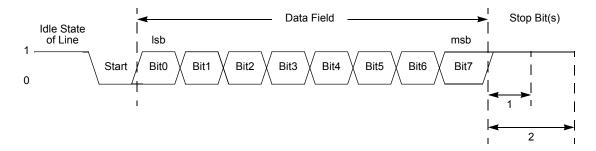

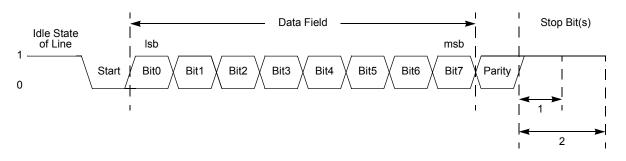

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

#### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

### General-Purpose Input/Output

The Z8 Encore! XP F082A Series features 6 to 25 port pins (Ports A–D) for general- purpose input/output (GPIO). The number of GPIO pins available is a function of package, and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

### **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, as well as factory serialization and read protection.

### Non-Volatile Data Storage

The non-volatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8 KB Flash memory do not include the NVDS feature.

# **Signal Descriptions**

Table 2 describes the Z8 Encore! XP F082A Series signals. See Pin Configurations on page 9 to determine the signals available for the specific package styles.

| Signal Mnemonic                                     | I/O     | Description                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/                                  | O Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                                             | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]                                             | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]                                             | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PD[0]                                               | I/O     | Port D. This pin is used for general-purpose output only.                                                                                                                                                                                                                                               |

| Note: PB6 and PB7 ar<br>replaced by AV <sub>E</sub> |         | vailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |

| UART Controllers                                    |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                                                | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                                                | Ι       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                                                | Ι       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                                                  | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal may be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                                              |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT                                         | 0       | Timer Output 0–1. These signals are outputs from the timers.                                                                                                                                                                                                                                            |

| T0OUT/T1OUT                                         | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN                                           | Ι       | Timer Input 0–1. These signals are used as the capture, gating and counter inputs.                                                                                                                                                                                                                      |

| Comparator                                          |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN                                           | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                                                | 0       | Comparator Output.                                                                                                                                                                                                                                                                                      |

### Table 2. Signal Descriptions

Zilog <sub>42</sub>

| Port   | Pin | Mnemonic    | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|--------------------------------|-----------------------------------------|

| Port B | PB0 | Reserved    |                                | AFS1[0]: 0                              |

|        |     | ANA0/AMPOUT | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|        | PB1 | Reserved    |                                | AFS1[1]: 0                              |

|        |     | ANA1/AMPINN | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|        | PB2 | Reserved    |                                | AFS1[2]: 0                              |

|        |     | ANA2/AMPINP | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|        | PB3 | CLKIN       | External Clock Input           | AFS1[3]: 0                              |

|        |     | ANA3        | ADC Analog Input               | AFS1[3]: 1                              |

|        | PB4 | Reserved    |                                | AFS1[4]: 0                              |

|        |     | ANA7        | ADC Analog Input               | AFS1[4]: 1                              |

|        | PB5 | Reserved    |                                | AFS1[5]: 0                              |

|        |     | VREF*       | ADC Voltage Reference          | AFS1[5]: 1                              |

|        | PB6 | Reserved    |                                | AFS1[6]: 0                              |

|        |     | Reserved    |                                | AFS1[6]: 1                              |

|        | PB7 | Reserved    |                                | AFS1[7]: 0                              |

|        |     | Reserved    |                                | AFS1[7]: 1                              |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Note: Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A-D Alternate Function Sub-Registers on page 47 must also be enabled.

\* VREF is available on PB5 in 28-pin products only.

PAFS1[7:0]—Port Alternate Function Set 1 0 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44. 1 = Port Alternate Function selected as defined in Table 14 and Table 15 on page 44.

### Port A–D Alternate Function Set 2 Sub-Registers

The Port A–D Alternate Function Set 2 sub-register (Table 26) is accessed through the Port A–D Control register by writing 08H to the Port A–D Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15.

• Note: Alternate function selection on port pins must also be enabled as described in Port A–D Alternate Function Sub-Registers on page 47.

| BITS  | 7        | 6            | 5             | 4             | 3             | 2              | 1            | 0        |

|-------|----------|--------------|---------------|---------------|---------------|----------------|--------------|----------|

| FIELD | PAFS27   | PAFS26       | PAFS25        | PAFS24        | PAFS23        | PAFS22         | PAFS21       | PAFS20   |

| RESET |          | 00H (all     | ports of 20/2 | 28 pin devic  | es); 04H (Pc  | ort A of 8-pin | device)      |          |

| R/W   | R/W      | R/W          | R/W           | R/W           | R/W           | R/W            | R/W          | R/W      |

| ADDR  | lf 08H i | n Port A–D / | Address Reg   | gister, acces | sible through | n the Port A-  | -D Control F | Register |

Table 26. Port A–D Alternate Function Set 2 Sub-Registers (PxAFS2)

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 15.

1 = Port Alternate Function selected as defined in Table 15.

### Port A–C Input Data Registers

Reading from the Port A–C Input Data registers (Table 27) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Table 27. Port A–C Input Data Registers (PxIN) | Table 27. | Port A–C | Input Data | Registers | (PxIN) |

|------------------------------------------------|-----------|----------|------------|-----------|--------|

|------------------------------------------------|-----------|----------|------------|-----------|--------|

| BITS      | 7     | 6                | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------|-------|------------------|------|------|------|------|------|------|--|

| FIELD     | PIN7  | PIN6             | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET     | Х     | Х                | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W       | R     | R                | R    | R    | R    | R    | R    | R    |  |

| ADDR      |       | FD2H, FD6H, FDAH |      |      |      |      |      |      |  |

| X = Undef | ined. |                  |      |      |      |      |      |      |  |

#### WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) register is set to 1. For more information on system reset, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) register are set to 1 following WDT time-out in STOP mode.

### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. Follow the steps below to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU) with the desired time-out value.

- 4. Write the Watchdog Timer Reload High Byte register (WDTH) with the desired time-out value.

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL) with the desired time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page (see Table 97 and Table 98 on page 165). Loading these values into the

Watchdog Timer Reload Registers results in a one-second timeout at room temperature and 3.3 V supply voltage.

Timeouts other than one second may be obtained by scaling the calibration values up or down as required.

**Note:** *The Watchdog Timer accuracy still degrades as temperature and supply voltage vary. See* Table 133 on page 230 *for* details.

# Watchdog Timer Control Register Definitions

### Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status register.

| BITS      | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|---------|---|---|---|---|---|---|---|

| FIELD     | WDTUNLK |   |   |   |   |   |   |   |

| RESET     | Х       | Х | Х | Х | Х | Х | Х | Х |

| R/W       | W       | W | W | W | W | W | W | W |

| ADDR      | FF0H    |   |   |   |   |   |   |   |

| X = Undef | ined.   |   |   |   |   |   |   |   |

### Table 57. Watchdog Timer Control Register (WDTCTL)

WDTUNLK—Watchdog Timer Unlock

The software must write the correct unlocking sequence to this register before it is allowed to modify the contents of the Watchdog Timer reload registers.

### Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers (Table 58 through Table 60) form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

Figure 11. UART Asynchronous Data Format without Parity

Figure 12. UART Asynchronous Data Format with Parity

### Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

**z**ilog<sup>°</sup>

configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- 1. Interrupt on all address bytes.

- 2. Interrupt on matched address bytes and correctly framed data bytes.

- 3. Interrupt only on correctly framed data bytes.

These modes are selected with MPMD [1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare Register. This mode introduces additional hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address).

01 = The UART generates an interrupt request only on received address bytes.

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.

#### MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode.

1 = Enable MULTIPROCESSOR (9-bit) mode.

#### MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).

#### DEPOL—Driver Enable Polarity

0 = DE signal is Active High.

1 = DE signal is Active Low.

#### BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

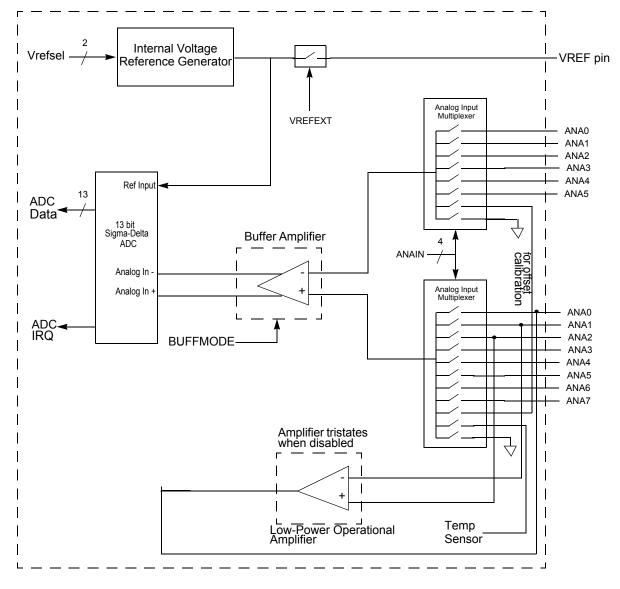

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

### Data Format

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL mode, the ADC

zilog

| BITS  | 7       | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|-------|---------|-----|-----|-----|------|-----|-----|-----|

| FIELD | INFO_EN |     |     |     | PAGE |     |     |     |

| RESET | 0       | 0   | 0   | 0   | 0    | 0   | 0   | 0   |

| R/W   | R/W     | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |

| ADDR  |         |     |     | FF  | 9H   |     |     |     |

#### Table 80. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices, the upper 4 bits must be zero. For Z8F02xx devices, the upper 5 bits must always be 0. For the Z8F01xx devices, the upper 6 bits must always be 0.

### **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) register is shared with the Flash Page Select Register. When the Flash Control Register is written with 73H followed by 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

R/W

R/W

R/W

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      |

|-------|--------|--------|--------|--------|--------|--------|--------|

| FIELD | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 |

| RESET | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

R/W

FF9H

R/W

Table 81. Flash Sector Protect Register (FPROT)

R/W

R/W

ADDR

R/W

0

SPROT0

0

R/W

#### 158

### Flash Program Memory Address 0001H

#### Table 87. Flash Options Bits at Program Memory Address 0001H

| BITS       | 7                                   | 6                    | 5   | 4      | 3   | 2    | 1     | 0   |  |

|------------|-------------------------------------|----------------------|-----|--------|-----|------|-------|-----|--|

| FIELD      |                                     | Reserved             |     | XTLDIS |     | Rese | erved |     |  |

| RESET      | U                                   | U                    | U   | U      | U   | U    | U     | U   |  |

| R/W        | R/W                                 | R/W                  | R/W | R/W    | R/W | R/W  | R/W   | R/W |  |

| ADDR       |                                     | Program Memory 0001H |     |        |     |      |       |     |  |

| Note:    = | Inchanged by Reset R/W = Read/Write |                      |     |        |     |      |       |     |  |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—Must be 1.

XTLDIS—State of Crystal Oscillator at Reset.

- **Note:** *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- 0 = Crystal oscillator is enabled during reset, resulting in longer reset timing

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

# **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 88 through Table 92.

### Trim Bit Address 0000H

| Table 88. Trim Options | Bits at Address 0000H |

|------------------------|-----------------------|

|------------------------|-----------------------|

| BITS      | 7                                               | 6               | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-----------|-------------------------------------------------|-----------------|-----|-----|-----|-----|-----|-----|--|

| FIELD     | Reserved                                        |                 |     |     |     |     |     |     |  |

| RESET     | U                                               | U U U U U U U U |     |     |     |     |     |     |  |

| R/W       | R/W                                             | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR      | Information Page Memory 0020H                   |                 |     |     |     |     |     |     |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                 |     |     |     |     |     |     |  |

Reserved—Altering this register may result in incorrect device operation.

159

### Trim Bit Address 0001H

### Table 89. Trim Option Bits at 0001H

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD     | Reserved                                        |     |     |     |     |     |     |     |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR      | Information Page Memory 0021H                   |     |     |     |     |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |

Reserved—Altering this register may result in incorrect device operation.

### Trim Bit Address 0002H

### Table 90. Trim Option Bits at 0002H (TIPO)

| BITS      | 7                                               | 6                             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|-------------------------------------------------|-------------------------------|---|---|---|---|---|---|--|

| FIELD     |                                                 | IPO_TRIM                      |   |   |   |   |   |   |  |

| RESET     |                                                 | U                             |   |   |   |   |   |   |  |

| R/W       |                                                 | R/W                           |   |   |   |   |   |   |  |

| ADDR      |                                                 | Information Page Memory 0022H |   |   |   |   |   |   |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                               |   |   |   |   |   |   |  |

iole. U – Unchangeu by Reset. R/W = Read/Write.

IPO\_TRIM—Internal Precision Oscillator Trim Byte Contains trimming bits for Internal Precision Oscillator.

# Trim Bit Address 0003H

**Note:** *The LVD is available on 8-pin devices only.*

### Table 91. Trim Option Bits at Address 0003H (TLVD)

| BITS      | 7                                               | 6   | 5   | 4        | 3   | 2   | 1   | 0   |  |

|-----------|-------------------------------------------------|-----|-----|----------|-----|-----|-----|-----|--|

| FIELD     | Reserved                                        |     |     | LVD_TRIM |     |     |     |     |  |

| RESET     | U                                               | U   | U   | U        |     |     |     |     |  |

| R/W       | R/W                                             | R/W | R/W | R/W      | R/W | R/W | R/W | R/W |  |

| ADDR      | Information Page Memory 0023H                   |     |     |          |     |     |     |     |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |          |     |     |     |     |  |

PS022825-0908

zilog 1

# Operation

### **OCD** Interface

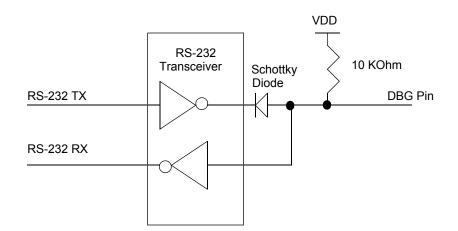

The on-chip debugger uses the DBG pin for communication with an external host. This one-pin interface is a bi-directional, open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface from the Z8 Encore! XP<sup>®</sup> F082A Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 24 and Figure 25. The recommended method is the buffered implementation displayed in Figure 25. The DBG pin has a internal pull-up resistor which is sufficient for some applications (for more details on the pull-up current, see Electrical Characteristics on page 221). For OCD operation at higher data rates or in noisy systems, an external pull-up resistor is recommended.

### Caution:

For operation of the on-chip debugger, all power pins ( $V_{DD}$  and  $AV_{DD}$ ) must be supplied with power, and all ground pins ( $V_{SS}$  and  $AV_{SS}$ ) must be properly grounded. The DBG pin is open-drain and may require an external pull-up resistor to ensure proper operation.

### Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (1)

zilog <sub>201</sub>

### Table 114. Notational Shorthand

| Notation | Description                    | Operand | Range                                                                                                                        |

|----------|--------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B)                                                                              |

| CC       | Condition Code                 | _       | Refer to Condition Codes section in the <i>eZ8 CPU Core User Manual (UM0128)</i> .                                           |

| DA       | Direct Address                 | Addrs   | Addrs. represents a number in the range of 0000H to FFFFH                                                                    |

| ER       | Extended Addressing Register   | Reg     | Reg. represents a number in the range of 000H to FFFH                                                                        |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH                                                                                          |

| lr       | Indirect Working Register      | @Rn     | n = 0–15                                                                                                                     |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH                                                                          |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |

| IRR      | Indirect Register Pair         | @Reg    | Reg. represents an even number in the range 00H to FEH                                                                       |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                    |

| r        | Working Register               | Rn      | n = 0 – 15                                                                                                                   |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH                                                                          |

| RA       | Relative Address               | Х       | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                             |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH                                                                    |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH                                                                        |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is<br>offset by the signed Index value (#Index) in a<br>+127 to<br>-128 range.   |

Table 115 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

236

# General Purpose I/O Port Output Timing

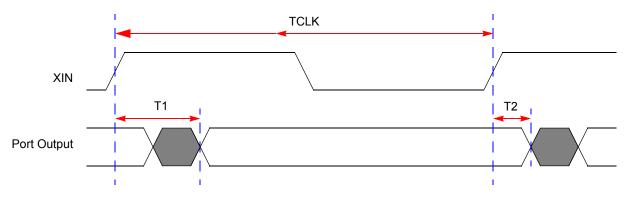

Figure 35 and Table 140 provide timing information for GPIO Port pins.

### Figure 35. GPIO Port Output Timing

|                |                                     | Delay (ns) |         |  |  |

|----------------|-------------------------------------|------------|---------|--|--|

| Parameter      | Abbreviation                        | Minimum    | Maximum |  |  |

| GPIO Port      | pins                                |            |         |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _          | 15      |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | _       |  |  |

### Table 140. GPIO Port Output Timing

261

# Index

# **Symbols**

# 202 % 202 @ 202

# **Numerics**

10-bit ADC 7 40-lead plastic dual-inline package 248, 249

# Α

absolute maximum ratings 221 AC characteristics 227 ADC 203 architecture 121 automatic power-down 122 block diagram 122 continuous conversion 124 control register 130, 132 control register definitions 130 data high byte register 132 data low bits register 133 electrical characteristics and timing 231 operation 122 single-shot conversion 123 ADCCTL register 130, 132 ADCDH register 132 ADCDL register 133 ADCX 203 ADD 203 add - extended addressing 203 add with carry 203 add with carry - extended addressing 203 additional symbols 202 address space 15 ADDX 203 analog signals 12 analog-to-digital converter (ADC) 121 AND 205

ANDX 205 arithmetic instructions 203 assembly language programming 199 assembly language syntax 200

# В

B 202 b 201 baud rate generator, UART 107 **BCLR 204** binary number suffix 202 **BIT 204** bit 201 clear 204 manipulation instructions 204 set 204 set or clear 204 swap 204 test and jump 206 test and jump if non-zero 206 test and jump if zero 206 bit jump and test if non-zero 206 bit swap 206 block diagram 4 block transfer instructions 204 **BRK 206** BSET 204 BSWAP 204, 206 **BTJ 206 BTJNZ 206 BTJZ 206**

# С

CALL procedure 206 CAPTURE mode 85, 86 CAPTURE/COMPARE mode 85 cc 201 CCF 204 characteristics, electrical 221 clear 205 CLR 205 COM 205

262

compare 85 compare - extended addressing 203 COMPARE mode 85 compare with carry 203 compare with carry - extended addressing 203 complement 205 complement carry flag 204 condition code 201 continuous conversion (ADC) 124 CONTINUOUS mode 84 control register definition, UART 108 Control Registers 15, 19 **COUNTER modes 84** CP 203 **CPC 203 CPCX 203** CPU and peripheral overview 5 CPU control instructions 204 **CPX 203** Customer Feedback Form 271

# D

DA 201, 203 data memory 17 DC characteristics 222 debugger, on-chip 173 **DEC 203** decimal adjust 203 decrement 203 decrement and jump non-zero 206 decrement word 203 **DECW 203** destination operand 202 device, port availability 37 DI 204 direct address 201 disable interrupts 204 **DJNZ 206** dst 202

### Ε

EI 204

electrical characteristics 221 ADC 231 flash memory and timing 230 GPIO input data sample timing 234 Watchdog Timer 230, 233 enable interrupt 204 ER 201 extended addressing register 201 external pin reset 27 eZ8 CPU features 5 eZ8 CPU instruction classes 202 eZ8 CPU instruction notation 200 eZ8 CPU instruction set 199 eZ8 CPU instruction summary 207

# F

FCTL register 149, 155, 156 features, Z8 Encore! 1 first opcode map 218 FLAGS 202 flags register 202 flash controller 7 option bit address space 156 option bit configuration - reset 153 program memory address 0000H 156 program memory address 0001H 158 flash memory 141 arrangement 142 byte programming 147 code protection 145 configurations 141 control register definitions 149, 155 controller bypass 148 electrical characteristics and timing 230 flash control register 149, 155, 156 flash option bits 146 flash status register 150 flow chart 144 frequency high and low byte registers 152 mass erase 147 operation 143 operation timing 145

**z**ilog<sup>°</sup>

268

subtract with carry - extended addressing 203 SUBX 203 SWAP 207 swap nibbles 207 symbols, additional 202

# Т

TCM 204 **TCMX 204 Technical Support 271** test complement under mask 204 test complement under mask - extended addressing 204 test under mask 204 test under mask - extended addressing 204 timer signals 11 timers 69 architecture 69 block diagram 70 CAPTURE mode 77, 78, 85, 86 CAPTURE/COMPARE mode 81, 85 COMPARE mode 79.85 CONTINUOUS mode 71, 84 COUNTER mode 72, 73 COUNTER modes 84 GATED mode 80, 85 ONE-SHOT mode 70, 84 operating mode 70 PWM mode 74, 76, 85 reading the timer count values 82 reload high and low byte registers 87 timer control register definitions 83 timer output signal operation 82 timers 0-3 control registers 83, 84 high and low byte registers 87, 88 TM 204 TMX 204 transmit IrDA data 118 transmitting UART data-polled method 99 transmitting UART dat-interrupt-driven method 100

TRAP 206

# U

### UART 7

architecture 97 baud rate generator 107 baud rates table 115 control register definitions 108 controller signals 11 data format 98 interrupts 105 multiprocessor mode 103 receiving data using interrupt-driven method 102 receiving data using the polled method 101 transmitting data usin the interrupt-driven method 100 transmitting data using the polled method 99 x baud rate high and low registers 114 x control 0 and control 1 registers 108 x status 0 and status 1 registers 111, 112 UxBRH register 114 UxBRL register 114 UxCTL0 register 108, 114 UxCTL1 register 109 UxRXD register 113 UxSTAT0 register 111 UxSTAT1 register 112 UxTXD register 113

# V

vector 201 Voltage Brownout reset (VBR) 26

# W

Watchdog Timer approximate time-out delay 91 approximate time-out delays 135 CNTL 26 control register 94, 136, 190