Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | ·                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f081asj020sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **CPU and Peripheral Overview**

#### eZ8 CPU Features

The eZ8 CPU, Zilog's latest 8-bit Central Processing Unit (CPU), meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{\text{(P)}}$  instruction set. The features of eZ8 CPU include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory.

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks.

- Compatible with existing Z8 code.

- Expanded internal Register File allows access of up to 4 KB.

- New instructions improve execution efficiency for code developed using higherlevel programming languages, including C.

- Pipelined instruction fetch and execution.

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL.

- New instructions support 12-bit linear addressing of the Register File.

- Up to 10 MIPS operation.

- C-Compiler friendly.

- 2 to 9 clock cycles per instruction.

For more information on eZ8 CPU, refer to eZ8 CPU Core User Manual (UM0128) available for download at <u>www.zilog.com</u>.

#### 10-Bit Analog-to-Digital Converter

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes. The ADC also features a unity gain buffer when high input impedance is required.

# **Pin Description**

The Z8 Encore! XP<sup>®</sup> F082A Series products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information on physical package specifications, see Packaging on page 241.

## **Available Packages**

The following package styles are available for each device in the Z8 Encore! XP F082A Series product line:

- SOIC

- 8-, 20-, and 28-pin

- PDIP

- 8-, 20-, and 28-pin

- SSOP

- 20- and 28- pin

- QFN (this is an MLF-S, a QFN style package with an 8-pin SOIC footprint)

- 8-pin

In addition, the Z8 Encore! XP F082A Series devices are available both with and without advanced analog capability (ADC, temperature sensor and op amp). Devices Z8F082A, Z8F042A, Z8F022A, and Z8F012A contain the advanced analog, while devices Z8F081A, Z8F041A, Z8F021A, and Z8F011A do not have the advanced analog capability.

## **Pin Configurations**

Figure 2 through Figure 4 display the pin configurations for all the packages available in the Z8 Encore! XP F082A Series. See Table 2 on page 11 for a description of the signals. The analog input alternate functions (ANAx) are not available on the Z8F081A, Z8F041A, Z8F021A, and Z8F011A devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all Port A, B and C pins default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general purpose input ports until programmed otherwise. At powerup, the PD0 pin defaults to the RESET alternate function.

Zilog <sub>17</sub>

| Program Memory Address (Hex)                | Function                     |

|---------------------------------------------|------------------------------|

| Z8F022A and Z8F021A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-07FF                                   | Program Memory               |

| Z8F012A and Z8F011A Products                |                              |

| 0000–0001                                   | Flash Option Bits            |

| 0002–0003                                   | Reset Vector                 |

| 0004–0005                                   | WDT Interrupt Vector         |

| 0006–0007                                   | Illegal Instruction Trap     |

| 0008–0037                                   | Interrupt Vectors*           |

| 0038–0039                                   | Reserved                     |

| 003A-003D                                   | Oscillator Fail Trap Vectors |

| 003E-03FF                                   | Program Memory               |

| * See Table 32 on page 56 for a list of the | interrupt vectors.           |

Table 5. Z8 Encore! XP F082A Series Program Memory Maps (Continued)

## **Data Memory**

The Z8 Encore! XP F082A Series does not use the eZ8 CPU's 64 KB Data Memory address space.

## **Flash Information Area**

Table 6 on page 18 describes the Z8 Encore! XP F082A Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Infor-

110 = 64 cycles delay 111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode (Table 49).

Table 49. Timer 0–1 Control Register 1 (TxCTL1)

| BITS  | 7   | 6    | 5   | 4     | 3    | 2   | 1     | 0   |

|-------|-----|------|-----|-------|------|-----|-------|-----|

| FIELD | TEN | TPOL |     | PRES  |      |     | TMODE |     |

| RESET | 0   | 0    | 0   | 0     | 0    | 0   | 0     | 0   |

| R/W   | R/W | R/W  | R/W | R/W   | R/W  | R/W | R/W   | R/W |

| ADDR  |     |      |     | F07H, | F0FH |     |       |     |

TEN-Timer Enable

0 = Timer is disabled.

1 = Timer enabled to count.

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### COUNTER mode

If the timer is enabled the Timer Output signal is complemented after timer reload.

0 = Count occurs on the rising edge of the Timer Input signal.

1 = Count occurs on the falling edge of the Timer Input signal.

89

| BITS  | 7    | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|-------|------|-----|-----|-------|------|-----|-----|-----|

| FIELD | PWML |     |     |       |      |     |     |     |

| RESET | 0    | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W  | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |      |     |     | F05H, | F0DH |     |     |     |

#### Table 55. Timer 0–1 PWM Low Byte Register (TxPWML)

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which may place the Z8 Encore! XP<sup>®</sup> F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator.

- A selectable time-out response: reset or interrupt.

- 24-bit programmable time-out value.

## Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 56 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

#### Table 56. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value – | Approximate Time-Out Delay<br>(with 10 kHz typical WDT oscillator frequency) |                        |  |  |

|------------------|--------------------|------------------------------------------------------------------------------|------------------------|--|--|

| (Hex)            | (Decimal)          | Typical                                                                      | Description            |  |  |

| 000004           | 4                  | 400 μs                                                                       | Minimum time-out delay |  |  |

| FFFFF            | 16,777,215         | 28 minutes                                                                   | Maximum time-out delay |  |  |

Zilog

Endec, and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

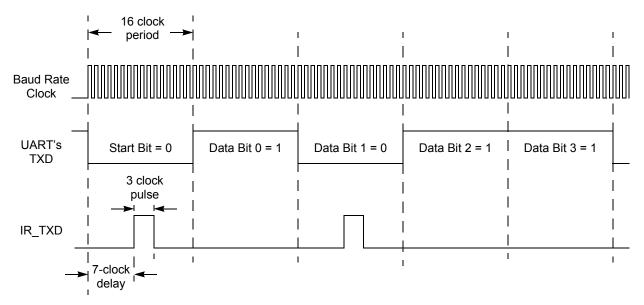

#### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP<sup>®</sup> F082A Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

129

| #5 MSB #5 LSB |

|---------------|

|---------------|

6. Add the gain correction factor to the original offset corrected value.

|   | #5 MSB | #5 LSB |

|---|--------|--------|

| + |        |        |

|   | #1 MSB | #1 LSB |

| = |        |        |

| #6 MSB #6 LSB |

|---------------|

|---------------|

7. Shift the result to the right, using the sign bit determined in Step 1. This allows for the detection of computational overflow.

| S-> #0 MSB #0 LSB |

|-------------------|

|-------------------|

#### **Output Data**

The following is the output format of the corrected ADC value.

| MSB      | LSB    |  |  |

|----------|--------|--|--|

| svba9876 | 543210 |  |  |

The overflow bit in the corrected output indicates that the computed value was greater than the maximum logical value (+1023) or less than the minimum logical value (-1024). Unlike the hardware overflow bit, this is not a simple binary Flag. For a normal sample (non-overflow), the sign and the overflow bit matches. If the sign bit and overflow bit do not match, a computational overflow has occurred.

#### Input Buffer Stage

Many applications require the measurement of an input voltage source with a high output impedance. This ADC provides a buffered input for such situations. The drawback of the buffered input is a limitation of the input range. When using unity gain buffered mode, the input signal must be prevented from coming too close to either  $V_{SS}$  or  $V_{DD}$ . See Table 135 on page 231 for details.

This condition applies only to the input voltage level (with respect to ground) of each differential input signal. The actual differential input voltage magnitude may be less than 300 mV.

The input range of the unbuffered ADC swings from  $V_{SS}$  to  $V_{DD}$ . Input signals smaller than 300 mV must use the unbuffered input mode. If these signals do not contain low output impedances, they might require off-chip buffering.

Signals outside the allowable input range can be used without instability or device damage. Any ADC readings made outside the input range are subject to greater inaccuracy than specified.

zilog |

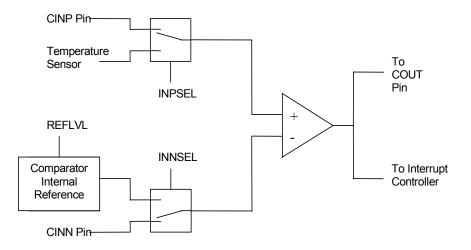

## Comparator

The Z8 Encore! XP<sup>®</sup> F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

## Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic HIGH. When the negative input exceeds the positive by more than the hysteresis, the output is a logic LOW. Otherwise, the comparator output retains its present value. See Table 137 on page 233 for details.

The comparator may be powered down to reduce supply current. See Power Control Register 0 on page 34 for details.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable or reconfigure the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts. The following example describes how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

```

zilog <sub>142</sub>

| 8 KB Flash<br>Program Memor | Addresses (hex) | 4 KB Flash<br>Program Memory | /<br>Addresses (hex)<br>1 0FFF | 2 KB Flash<br>Program Memory<br>Address | /<br>es (hex)        |

|-----------------------------|-----------------|------------------------------|--------------------------------|-----------------------------------------|----------------------|

| Sector 7                    | 1FFF<br>1C00    | Sector 7                     | 0E00                           | Sector 3                                | 07FF<br>0600         |

| Sector 6                    | 1BFF            | Sector 6                     | 0DFF                           | Sector 2                                | 05FF<br>0400<br>03FF |

| Castar 5                    | 1800<br>17FF    | Sector 5                     | 0C00<br>0BFF                   | Sector 1                                | 0200<br>01FF         |

| Sector 5                    | 1400<br>13FF    |                              | 0A00<br>09FF                   | Sector 0                                | 0000                 |

| Sector 4                    | 1000            | Sector 4                     | 0800                           |                                         |                      |

| Sector 3                    | 0FFF<br>0C00    | Sector 3                     | 07FF<br>0600                   | 1 KB Flash<br>Program Memory            | y<br>ses (hex)       |

| Sector 2                    | 0BFF<br>0800    | Sector 2                     | 05FF<br>0400                   | Sector 1                                | 03FF                 |

| Sector 1                    | 07FF<br>0400    | Sector 1                     | 03FF<br>0200                   | Sector 0                                | 01FF                 |

| Sector 0                    | 03FF<br>0000    | Sector 0                     | 01FF<br>0000                   |                                         |                      |

Figure 21. Flash Memory Arrangement

## **Flash Information Area**

The Flash information area is separate from Program Memory and is mapped to the address range FE00H to FFFFH. This area is readable but cannot be erased or overwritten. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

159

## Trim Bit Address 0001H

#### Table 89. Trim Option Bits at 0001H

| BITS      | 7                             | 6            | 5            | 4          | 3                                               | 2   | 1   | 0   |  |  |  |  |

|-----------|-------------------------------|--------------|--------------|------------|-------------------------------------------------|-----|-----|-----|--|--|--|--|

| FIELD     | Reserved                      |              |              |            |                                                 |     |     |     |  |  |  |  |

| RESET     | U                             | U            | U            | U          | U                                               | U   | U   | U   |  |  |  |  |

| R/W       | R/W                           | R/W          | R/W          | R/W        | R/W                                             | R/W | R/W | R/W |  |  |  |  |

| ADDR      | Information Page Memory 0021H |              |              |            |                                                 |     |     |     |  |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | = Read/Write | <b>)</b> . | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |  |  |  |  |

Reserved—Altering this register may result in incorrect device operation.

## Trim Bit Address 0002H

#### Table 90. Trim Option Bits at 0002H (TIPO)

| BITS      | 7                                               | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |

|-----------|-------------------------------------------------|-----------------|--|--|--|--|--|--|--|--|--|

| FIELD     | IPO_TRIM                                        |                 |  |  |  |  |  |  |  |  |  |

| RESET     | U                                               |                 |  |  |  |  |  |  |  |  |  |

| R/W       | R/W                                             |                 |  |  |  |  |  |  |  |  |  |

| ADDR      | Information Page Memory 0022H                   |                 |  |  |  |  |  |  |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                 |  |  |  |  |  |  |  |  |  |

IPO\_TRIM—Internal Precision Oscillator Trim Byte Contains trimming bits for Internal Precision Oscillator.

## Trim Bit Address 0003H

**Note:** *The LVD is available on 8-pin devices only.*

### Table 91. Trim Option Bits at Address 0003H (TLVD)

| BITS      | 7                                               | 6        | 5   | 4        | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|----------|-----|----------|-----|-----|-----|-----|--|--|

| FIELD     |                                                 | Reserved |     | LVD_TRIM |     |     |     |     |  |  |

| RESET     | U                                               | U        | U   |          |     |     |     |     |  |  |

| R/W       | R/W                                             | R/W      | R/W | R/W      | R/W | R/W | R/W | R/W |  |  |

| ADDR      | Information Page Memory 0023H                   |          |     |          |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |          |     |          |     |     |     |     |  |  |

PS022825-0908

## Trim Bit Address 0004H

#### Table 92. Trim Option Bits at 0004H

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| FIELD     | Reserved                                        |     |     |     |     |     |     |     |  |  |

| RESET     | U U U U U U U U                                 |     |     |     |     |     |     |     |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR      | Information Page Memory 0024H                   |     |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |

Reserved—Altering this register may result in incorrect device operation.

## Zilog Calibration Data

## ADC Calibration Data

## Table 93. ADC Calibration Bits

| BITS      | 7                                   | 6            | 5            | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------|-------------------------------------|--------------|--------------|---|---|---|---|---|--|--|--|

| FIELD     | ADC_CAL                             |              |              |   |   |   |   |   |  |  |  |

| RESET     | U U U U U U U U                     |              |              |   |   |   |   |   |  |  |  |

| R/W       | R/W R/W R/W R/W R/W R/W R/W         |              |              |   |   |   |   |   |  |  |  |

| ADDR      | Information Page Memory 0060H–007DH |              |              |   |   |   |   |   |  |  |  |

| Note: U = | Unchanged b                         | y Reset. R/W | = Read/Write |   |   |   |   |   |  |  |  |

ADC\_CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as described in Software Compensation Procedure Using Factory Calibration Data on page 126. The location of each calibration byte is provided in Table 94 on page 162.

zilog <sub>1</sub>

If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/ DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled High. At this point, the PA0/DBG pin may be used to autobaud and cause the device to enter DEBUG mode. See OCD Unlock Sequence (8-Pin Devices Only) on page 178.

#### Exiting DEBUG Mode

The device exits DEBUG mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brownout reset

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP mode initiates a System Reset

#### OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character transmitted and received by the OCD consists of 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 26.

|  |  | START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|--|--|-------|----|----|----|----|----|----|----|----|------|

|--|--|-------|----|----|----|----|----|----|----|----|------|

#### Figure 26. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. It is recommended that, if possible, the host drives the DBG pin using an open drain output to avoid this issue.

#### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The Auto-Baud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

## **On-Chip Debugger Control Register Definitions**

### **OCD Control Register**

The OCD Control register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP<sup>®</sup> F082A Series device.

A reset and stop function can be achieved by writing \$1H to this register. A reset and go function can be achieved by writing \$1H to this register. If the device is in DEBUG mode, a run function can be implemented by writing \$0H to this register.

#### Table 106. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4 | 3   | 2 | 1 | 0   |

|-------|---------|-------|--------|---|-----|---|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK |   | RST |   |   |     |

| RESET | 0       | 0     | 0      | 0 | 0   | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R   | R | R | R/W |

#### DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = The Z8 Encore! XP F082A Series device is operating in NORMAL mode.

1 = The Z8 Encore! XP F082A Series device is in DEBUG mode.

#### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

0 = Breakpoints are disabled.

1 = Breakpoints are enabled.

191

WDFEN-Watchdog Timer Oscillator Failure Detection Enable

1 = Failure detection of Watchdog Timer oscillator is enabled

0 = Failure detection of Watchdog Timer oscillator is disabled

SCKSEL—System Clock Oscillator Select

000 = Internal precision oscillator functions as system clock at 5.53 MHz

001 = Internal precision oscillator functions as system clock at 32 kHz

010 = Crystal oscillator or external RC oscillator functions as system clock

011 = Watchdog Timer oscillator functions as system

100 = External clock signal on PB3 functions as system clock

101 = Reserved

110 = Reserved

111 = Reserved

zilog

196

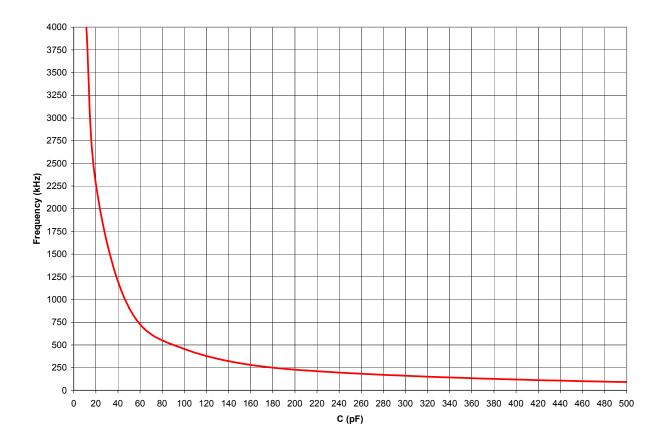

Figure 29 displays the typical (3.3 V and 25 °C) oscillator frequency as a function of the capacitor (C in pF) employed in the RC network assuming a 45 K $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator XIN pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20 pF are recommended.

# Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a 45 k $\Omega$ Resistor

**Caution**:

When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brownout threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

**z**ilog<sup>°</sup>

#### 229

## **On-Chip Peripheral AC and DC Electrical Characteristics**

#### Table 131. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = - | 40 °C to +           | 105 °C  |       |                                                                                                       |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                                      | Minimum            | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                            |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70    | V     | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75      | mV    |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | -                  | $V_{SS}$             | -       | V     |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>disabled                                                      |                    | 16                   |         | μs    | 66 Internal Precision<br>Oscillator cycles                                                            |  |

| T <sub>SMR</sub>  | Stop Mode Recovery<br>with crystal oscillator<br>enabled                                                       |                    | 1                    |         | ms    | 5000 Internal Precision<br>Oscillator cycles                                                          |  |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | -       | μs    | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |  |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | _                    | 100     | ms    |                                                                                                       |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |         | ns    | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |  |

only and are not tested in production.

## 231

#### Table 134. Non-Volatile Data Storage

|                        |         | = 2.7 V to<br>10 °C to + |         |        |                                           |  |

|------------------------|---------|--------------------------|---------|--------|-------------------------------------------|--|

| Parameter              | Minimum | Typical                  | Maximum | Units  | Notes                                     |  |

| NVDS Byte Read Time    | 34      | -                        | 519     | μs     | With system clock at 20 MHz               |  |

| NVDS Byte Program Time | 0.171   | -                        | 39.7    | ms     | With system clock at 20 MHz               |  |

| Data Retention         | 100     | _                        | -       | years  | 25 °C                                     |  |

| Endurance              | 160,000 | _                        | -       | cycles | Cumulative write cycles for entire memory |  |

### Table 135. Analog-to-Digital Converter Electrical Characteristics and Timing

|                     |                                                    | $T_A =$    | = 3.0 V to<br>0 °C to +<br>otherwis | 70 °C      |                  |                                                                                              |

|---------------------|----------------------------------------------------|------------|-------------------------------------|------------|------------------|----------------------------------------------------------------------------------------------|

| Symbol              | Parameter                                          | Minimum    | Typical                             | Maximum    | Units            | Conditions                                                                                   |

|                     | Resolution                                         | 10         |                                     | -          | bits             |                                                                                              |

|                     | Differential Nonlinearity<br>(DNL)                 | -1.0       | -                                   | 1.0        | LSB <sup>3</sup> | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |

|                     | Integral Nonlinearity (INL)                        | -3.0       | -                                   | 3.0        | LSB <sup>3</sup> | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |

|                     | Offset Error with Calibration                      |            | <u>+</u> 1                          |            | LSB <sup>3</sup> |                                                                                              |

|                     | Absolute Accuracy with Calibration                 |            | <u>+</u> 3                          |            | LSB <sup>3</sup> |                                                                                              |

| V <sub>REF</sub>    | Internal Reference Voltage                         | 1.0<br>2.0 | 1.1<br>2.2                          | 1.2<br>2.4 | V                | REFSEL=01<br>REFSEL=10                                                                       |

| V <sub>REF</sub>    | Internal Reference<br>Variation with Temperature   |            | <u>+</u> 1.0                        |            | %                | Temperature variation with $V_{DD}$ = 3.0                                                    |

| V <sub>REF</sub>    | Internal Reference Voltage Variation with $V_{DD}$ |            | <u>+</u> 0.5                        |            | %                | Supply voltage variation with $T_A = 30 \ ^\circ C$                                          |

| R <sub>REFOUT</sub> | Reference Buffer Output<br>Impedance               |            | 850                                 |            | Ω                | When the internal<br>reference is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |

263

page erase 147 page select register 150, 151 FPS register 150, 151 FSTAT register 150

## G

GATED mode 85 general-purpose I/O 37 GPIO 7, 37 alternate functions 38 architecture 38 control register definitions 45 input data sample timing 234 interrupts 45 port A-C pull-up enable sub-registers 50, 51 port A-H address registers 46 port A-H alternate function sub-registers 47 port A-H control registers 46 port A-H data direction sub-registers 47 port A-H high drive enable sub-registers 49 port A-H input data registers 51 port A-H output control sub-registers 48 port A-H output data registers 52 port A-H stop mode recovery sub-registers 49 port availability by device 37 port input timing 235 port output timing 236

## Η

H 202 HALT 204 halt mode 34, 204 hexadecimal number prefix/suffix 202

## I

I2C 7 IM 201 immediate data 201 immediate operand prefix 202 **INC 203** increment 203 increment word 203 **INCW 203** indexed 201 indirect address prefix 202 indirect register 201 indirect register pair 201 indirect working register 201 indirect working register pair 201 infrared encoder/decoder (IrDA) 117 Instruction Set 199 instruction set. eZ8 CPU 199 instructions ADC 203 ADCX 203 ADD 203 **ADDX 203** AND 205 **ANDX 205** arithmetic 203 **BCLR 204** BIT 204 bit manipulation 204 block transfer 204 **BRK 206 BSET 204** BSWAP 204, 206 **BTJ 206 BTJNZ 206 BTJZ 206 CALL 206** CCF 204 CLR 205 COM 205 CP 203 CPC 203 **CPCX 203** CPU control 204 **CPX 203** DA 203 **DEC 203 DECW 203**

DI 204

264

**DJNZ 206** EI 204 **HALT 204 INC 203 INCW 203 IRET 206** JP 206 LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204 LDX 205 LEA 205 logical 205 **MULT 203** NOP 204 OR 205 **ORX 206** POP 205 **POPX 205** program control 206 **PUSH 205** PUSHX 205 **RCF 204 RET 206** RL 206 **RLC 206** rotate and shift 206 RR 206 **RRC 206** SBC 203 SCF 204, 205 SRA 207 SRL 207 **SRP 205 STOP 205** SUB 203 SUBX 203 **SWAP 207** TCM 204 **TCMX 204** TM 204 TMX 204

**TRAP 206** Watchdog Timer refresh 205 XOR 206 **XORX 206** instructions, eZ8 classes of 202 interrupt control register 67 interrupt controller 55 architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 66 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 206 interrupt vector listing 55 interrupts **UART 105** IR 201 lr 201 IrDA architecture 117 block diagram 117 control register definitions 120 operation 117 receiving data 119 transmitting data 118 **IRET 206** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 63 IRQ2 enable high and low bit registers 65 **IRR 201** Irr 201

## J

JP 206 jump, conditional, relative, and relative conditional 206