# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082ahh020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

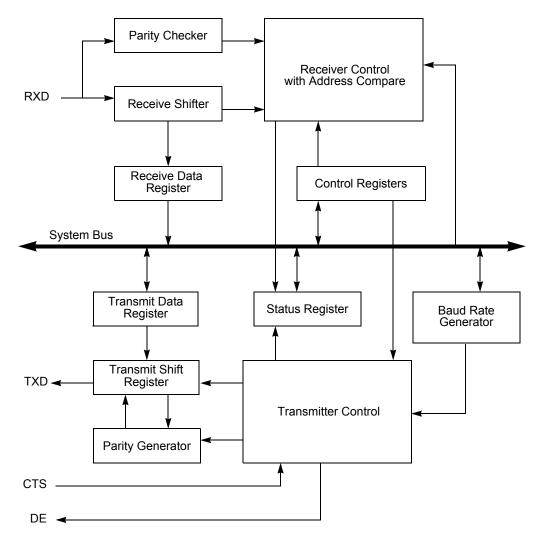

#### **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

#### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

#### General-Purpose Input/Output

The Z8 Encore! XP F082A Series features 6 to 25 port pins (Ports A–D) for general- purpose input/output (GPIO). The number of GPIO pins available is a function of package, and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

#### **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, as well as factory serialization and read protection.

#### Non-Volatile Data Storage

The non-volatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8 KB Flash memory do not include the NVDS feature.

# **Pin Description**

The Z8 Encore! XP<sup>®</sup> F082A Series products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information on physical package specifications, see Packaging on page 241.

## **Available Packages**

The following package styles are available for each device in the Z8 Encore! XP F082A Series product line:

- SOIC

- 8-, 20-, and 28-pin

- PDIP

- 8-, 20-, and 28-pin

- SSOP

- 20- and 28- pin

- QFN (this is an MLF-S, a QFN style package with an 8-pin SOIC footprint)

- 8-pin

In addition, the Z8 Encore! XP F082A Series devices are available both with and without advanced analog capability (ADC, temperature sensor and op amp). Devices Z8F082A, Z8F042A, Z8F022A, and Z8F012A contain the advanced analog, while devices Z8F081A, Z8F041A, Z8F021A, and Z8F011A do not have the advanced analog capability.

# **Pin Configurations**

Figure 2 through Figure 4 display the pin configurations for all the packages available in the Z8 Encore! XP F082A Series. See Table 2 on page 11 for a description of the signals. The analog input alternate functions (ANAx) are not available on the Z8F081A, Z8F041A, Z8F021A, and Z8F011A devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all Port A, B and C pins default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general purpose input ports until programmed otherwise. At powerup, the PD0 pin defaults to the RESET alternate function.

zilog

vector address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                         | Action                                                               |

|----------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP mode      | Watchdog Timer time-out when configured for Reset                                 | Stop Mode Recovery                                                   |

|                | Watchdog Timer time-out when configured for interrupt                             | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO Port<br>pin enabled as a Stop Mode<br>Recovery source | Stop Mode Recovery                                                   |

|                | Assertion of external RESET Pin                                                   | System Reset                                                         |

|                | Debug Pin driven Low                                                              | System Reset                                                         |

#### Table 10. Stop Mode Recovery Sources and Resulting Action

## Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

## Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO Port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

**Note:** The SMR pulses shorter than specified does not trigger a recovery (see Table 131 on page 229). When this happens, the STOP bit in the Reset Status (RSTSTAT) register is set to 1.

**Caution:** In STOP mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can

**z**ilog<sup>°</sup>

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. See Timers on page 69 for more details.

**Caution:** For pin with multiple alternate functions, it is recommended to write to the AFS1 and AFS2 sub-registers before enabling the alternate function via the AF sub-register. This prevents spurious transitions through unwanted alternate function modes.

# **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the Alternate Function sub-register AFS1 and is programmable through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See Electrical Characteristics on page 221 for the maximum total current for the applicable package.

# **Shared Reset Pin**

On the 20- and 28-pin devices, the PD0 pin shares function with a bi-directional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bi-directional reset until the software re-configures it. The PD0 pin is output-only when in GPIO mode.

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

PS022825-0908

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus drives the pin low during any reset sequence. Since PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

# **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer func-

Zilog <sub>42</sub>

| Port   | Pin | Mnemonic    | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|--------------------------------|-----------------------------------------|

| Port B | PB0 | Reserved    |                                | AFS1[0]: 0                              |

|        |     | ANA0/AMPOUT | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|        | PB1 | Reserved    | AFS1[1]: 0                     |                                         |

|        |     | ANA1/AMPINN | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|        | PB2 | Reserved    |                                | AFS1[2]: 0                              |

|        |     | ANA2/AMPINP | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|        | PB3 | CLKIN       | External Clock Input           | AFS1[3]: 0                              |

|        |     | ANA3        | ADC Analog Input               | AFS1[3]: 1                              |

|        | PB4 | Reserved    |                                | AFS1[4]: 0                              |

|        |     | ANA7        | ADC Analog Input               | AFS1[4]: 1                              |

|        | PB5 | Reserved    |                                | AFS1[5]: 0                              |

|        |     | VREF*       | ADC Voltage Reference          | AFS1[5]: 1                              |

|        | PB6 | Reserved    |                                | AFS1[6]: 0                              |

|        |     | Reserved    |                                | AFS1[6]: 1                              |

|        | PB7 | Reserved    |                                | AFS1[7]: 0                              |

|        |     | Reserved    |                                | AFS1[7]: 1                              |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Note: Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A-D Alternate Function Sub-Registers on page 47 must also be enabled.

\* VREF is available on PB5 in 28-pin products only.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

### **Timer Pin Signal Operation**

Timer Output is a GPIO Port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The Timer Input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

## Operation

#### **Data Format**

The UART always transmits and receives data in an 8-bit data format, least-significant bit first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low START bit and ends with either 1 or 2 active High STOP bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

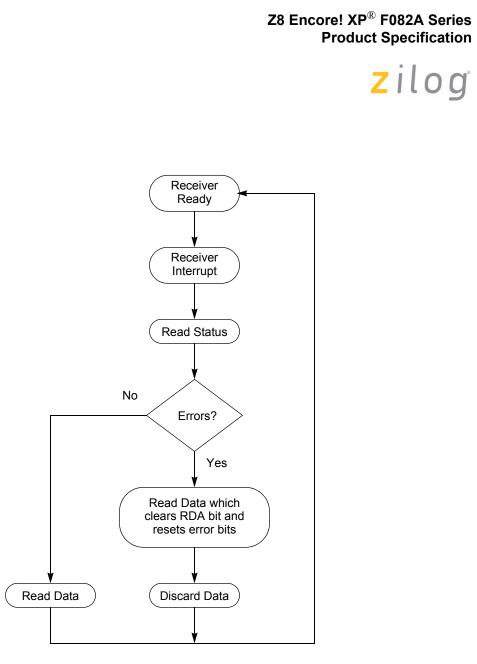

Figure 15. UART Receiver Interrupt Service Routine Flow

### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

# **Analog-to-Digital Converter**

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL mode.

- 10-bit resolution in SINGLE-ENDED mode.

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports.

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral.

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports.

- Low-power operational amplifier (LPO).

- Interrupt on conversion complete.

- Bandgap generated internal voltage reference with two selectable levels.

- Manual in-circuit calibration is possible employing user code (offset calibration).

- Factory calibrated for in-circuit error compensation.

## Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes).

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes).

- LPO output with full pin access to the feedback path.

Zilog 14

the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

## **Byte Programming**

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully completed, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming can be accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the *eZ8 CPU User Manual* (available for download at <u>www.zilog.com</u>) for a description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

#### Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### Mass Erase

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the

159

# Trim Bit Address 0001H

### Table 89. Trim Option Bits at 0001H

| BITS      | 7                             | 6            | 5            | 4          | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|-------------------------------|--------------|--------------|------------|-----|-----|-----|-----|--|--|--|--|

| FIELD     | Reserved                      |              |              |            |     |     |     |     |  |  |  |  |

| RESET     | U                             | U            | U            | U          | U   | U   | U   | U   |  |  |  |  |

| R/W       | R/W                           | R/W          | R/W          | R/W        | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR      | Information Page Memory 0021H |              |              |            |     |     |     |     |  |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | = Read/Write | <b>)</b> . |     |     |     |     |  |  |  |  |

Reserved—Altering this register may result in incorrect device operation.

# Trim Bit Address 0002H

## Table 90. Trim Option Bits at 0002H (TIPO)

| BITS      | 7                                               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-----------|-------------------------------------------------|---|---|---|---|---|---|---|--|--|--|--|--|

| FIELD     | IPO_TRIM                                        |   |   |   |   |   |   |   |  |  |  |  |  |

| RESET     |                                                 | U |   |   |   |   |   |   |  |  |  |  |  |

| R/W       |                                                 |   |   | R | W |   |   |   |  |  |  |  |  |

| ADDR      | Information Page Memory 0022H                   |   |   |   |   |   |   |   |  |  |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |   |   |   |   |   |   |   |  |  |  |  |  |

IPO\_TRIM—Internal Precision Oscillator Trim Byte Contains trimming bits for Internal Precision Oscillator.

# Trim Bit Address 0003H

**Note:** *The LVD is available on 8-pin devices only.*

## Table 91. Trim Option Bits at Address 0003H (TLVD)

| BITS      | 7                             | 6            | 5            | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|-------------------------------|--------------|--------------|-----|-----|-----|-----|-----|--|--|--|--|

| FIELD     | Reserved LVD_TRIM             |              |              |     |     |     |     |     |  |  |  |  |

| RESET     | U                             | U            | U            | U   |     |     |     |     |  |  |  |  |

| R/W       | R/W                           | R/W          | R/W          | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR      | Information Page Memory 0023H |              |              |     |     |     |     |     |  |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | = Read/Write | ).  |     |     |     |     |  |  |  |  |

PS022825-0908

186

#### 200

# Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1**: If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 112. Assembly Language Syntax Example 1

| Assembly Language<br>Code | ADD | 43H, | 08H | (ADD dst, src) |

|---------------------------|-----|------|-----|----------------|

| Object Code               | 04  | 08   | 43  | (OPC src, dst) |

**Example 2**: In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 113. Assembly Language Syntax Example 2

| Assembly Language<br>Code | ADD | 43H, | R8 | (ADD dst, src) |

|---------------------------|-----|------|----|----------------|

| Object Code               | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 114.

**z**ilog<sup>°</sup>

# 210

| Assembly        | Symbolic                                                                                                          | Addres        | s Mode   | Opcode(s) |   |              | Fla | ags |   |   | _ Fetch | Instr. |

|-----------------|-------------------------------------------------------------------------------------------------------------------|---------------|----------|-----------|---|--------------|-----|-----|---|---|---------|--------|

| Mnemonic        | Operation                                                                                                         | dst           | src      | (Hex)     | С | Ζ            | S   | ۷   | D | Н | Cycles  |        |

| HALT            | Halt Mode                                                                                                         |               |          | 7F        | - | -            | -   | -   | - | - | 1       | 2      |

| INC dst         | $dst \gets dst + 1$                                                                                               | R             |          | 20        | _ | *            | *   | _   | - | _ | 2       | 2      |

|                 |                                                                                                                   | IR            |          | 21        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | r             |          | 0E-FE     | - |              |     |     |   |   | 1       | 2      |

| INCW dst        | $dst \gets dst + 1$                                                                                               | RR            |          | A0        | - | *            | *   | *   | - | - | 2       | 5      |

|                 |                                                                                                                   | IRR           |          | A1        | - |              |     |     |   |   | 2       | 6      |

| IRET            | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |               |          | BF        | * | *            | *   | *   | * | * | 1       | 5      |

| JP dst          | $PC \gets dst$                                                                                                    | DA            |          | 8D        | - | _            | _   | _   | - | - | 3       | 2      |

|                 |                                                                                                                   | IRR           |          | C4        | - |              |     |     |   |   | 2       | 3      |

| JP cc, dst      | if cc is true $PC \leftarrow dst$                                                                                 | DA            |          | 0D-FD     | - | -            | _   | -   | - | - | 3       | 2      |

| JR dst          | $PC \gets PC + X$                                                                                                 | DA            |          | 8B        | - | -            | -   | -   | - | - | 2       | 2      |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                           | DA            |          | 0B-FB     | _ | _            | _   | _   | _ | _ | 2       | 2      |

| LD dst, rc      | $dst \gets src$                                                                                                   | r             | IM       | 0C-FC     | - | _            | _   | _   | - | - | 2       | 2      |

|                 |                                                                                                                   | r             | X(r)     | C7        | - |              |     |     |   |   | 3       | 3      |

|                 |                                                                                                                   | X(r)          | r        | D7        | - |              |     |     |   |   | 3       | 4      |

|                 |                                                                                                                   | r             | lr       | E3        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | R             | R        | E4        | - |              |     |     |   |   | 3       | 2      |

|                 |                                                                                                                   | R             | IR       | E5        | - |              |     |     |   |   | 3       | 4      |

|                 |                                                                                                                   | R             | IM       | E6        | - |              |     |     |   |   | 3       | 2      |

|                 |                                                                                                                   | IR            | IM       | E7        | - |              |     |     |   |   | 3       | 3      |

|                 |                                                                                                                   | lr            | r        | F3        | - |              |     |     |   |   | 2       | 3      |

|                 |                                                                                                                   | IR            | R        | F5        | - |              |     |     |   |   | 3       | 3      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                                        | of the result | of the o | peration. |   | ⊧ Re<br>⊧ Se |     |     | ) |   |         |        |

## Table 124. eZ8 CPU Instruction Summary (Continued)

**z**ilog<sup>°</sup>

|   |             |             |                     |                     |                     |                 | Lo           | ower Ni       | bble (He        | x)             |              |            |             |             |           |           |

|---|-------------|-------------|---------------------|---------------------|---------------------|-----------------|--------------|---------------|-----------------|----------------|--------------|------------|-------------|-------------|-----------|-----------|

|   | 0           | 1           | 2                   | 3                   | 4                   | 5               | 6            | 7             | 8               | 9              | А            | В          | С           | D           | Е         | F         |

| ~ | 1.1         | 2.2         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2       |

| 0 | BRK         | SRP<br>IM   | <b>ADD</b><br>r1,r2 | ADD<br>r1,lr2       | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1   | ADD<br>R1,IM | ADD<br>IR1,IM | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1 | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NO        |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            | ,            |            | ,           | 00,271      | 1         | See       |

| 1 | RLC         | RLC         | ADC                 | ADC                 | ADC                 | ADC             | ADC          | ADC           | ADCX            | ADCX           |              |            |             |             |           | Орсо      |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           | Ma        |

| 2 | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1,        |

| 2 | INC<br>R1   | INC<br>IR1  | <b>SUB</b><br>r1,r2 | SUB<br>r1,lr2       | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1   | SUB<br>R1,IM | SUB<br>IR1,IM | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1 |              |            |             |             |           | AT        |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 3 | DEC         | DEC         | SBC                 | SBC                 | SBC                 | SBC             | SBC          | SBC           | SBCX            | SBCX           |              |            |             |             |           |           |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           |           |

| 4 | DA          | DA          | OR                  | OR                  | OR                  | OR              | OR           | OR            | ORX             | ORX            |              |            |             |             |           |           |

|   | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| 5 | 2.2<br>POP  | 2.3<br>POP  | 2.3<br>AND          | 2.4<br>AND          | 3.3<br>AND          | 3.4<br>AND      | 3.3<br>AND   | 3.4<br>AND    | 4.3<br>ANDX     | 4.3<br>ANDX    |              |            |             |             |           | 1.<br>WE  |

| Ŭ | R1          | IR1         | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.        |

| 6 | СОМ         | COM         | тсм                 | тсм                 | тсм                 | тсм             | тсм          | тсм           | тсмх            | тсмх           |              |            |             |             |           | STO       |

|   | R1          | IR1         | r1,r2               | r1,Ir2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| - | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.1       |

| 7 | PUSH<br>R2  | PUSH<br>IR2 | <b>TM</b><br>r1,r2  | <b>TM</b><br>r1,lr2 | <b>TM</b><br>R2,R1  | TM<br>IR2,R1    | TM<br>R1,IM  | TM<br>IR1,IM  | TMX<br>ER2,ER1  | TMX<br>IM,ER1  |              |            |             |             |           | HA        |

|   | 2.5         | 2.6         | 2.5                 | 2.9                 | 3.2                 | 3.3             | 3.4          | 3.5           | 3.4             | 3.4            |              |            |             |             |           | 1.:       |

| 8 | DECW        |             | LDE                 | LDEI                | LDX                 | LDX             | LDX          | LDX           | LDX             | LDX            |              |            |             |             |           | D         |

|   | RR1         | IRR1        | r1,Irr2             | lr1,lrr2            | r1,ER2              | lr1,ER2         | IRR2,R1      | IRR2,IR1      | r1,rr2,X        | rr1,r2,X       |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.5                 | 2.9                 | 3.2                 | 3.3             | 3.4          | 3.5           | 3.3             | 3.5            |              |            |             |             |           | 1.2       |

| 9 | RL          | RL          | LDE                 | LDEI                | LDX                 | LDX             | LDX          | LDX           | LEA             | LEA            |              |            |             |             |           | E         |

|   | R1          | IR1         | r2,Irr1             | lr2,lrr1            | r2,ER1              | Ir2,ER1         |              | IR2,IRR1      | r1,r2,X         | rr1,rr2,X      |              |            |             |             |           | <u> </u>  |

| А | 2.5<br>INCW | 2.6<br>INCW | 2.3<br>CP           | 2.4<br>CP           | 3.3<br>CP           | 3.4<br>CP       | 3.3<br>CP    | 3.4<br>CP     | 4.3<br>CPX      | 4.3<br>CPX     |              |            |             |             |           | 1.4<br>RE |

| ~ | RR1         | IRR1        | r1,r2               | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.3                 | 2.4                 | 3.3                 | 3.4             | 3.3          | 3.4           | 4.3             | 4.3            |              |            |             |             |           | 1.        |

| В | CLR         | CLR         | XOR                 | XOR                 | XOR                 | XOR             | XOR          | XOR           | XORX            | XORX           |              |            |             |             |           | IRE       |

|   | R1          | IR1         | r1,r2               | r1,Ir2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| ~ | 2.2         | 2.3         | 2.5                 | 2.9                 | 2.3                 | 2.9             |              | 3.4           | 3.2             |                |              |            |             |             |           | 1.1       |

| С | RRC<br>R1   | IR1         | LDC<br>r1,Irr2      | LDCI<br>Ir1,Irr2    | JP<br>IRR1          | LDC<br>Ir1,Irr2 |              | LD<br>r1,r2,X | PUSHX<br>ER2    |                |              |            |             |             |           | RC        |

|   | 2.2         | 2.3         | 2.5                 | 2.9                 | 2.6                 | 2.2             | 3.3          | 3.4           | 3.2             |                |              |            |             |             |           | 1.:       |

| D | SRA         | SRA         | LDC                 | LDCI                | -                   | BSWAP           |              | LD            | POPX            |                |              |            |             |             |           | SC        |

|   | R1          | IR1         | r2,Irr1             | lr2,Irr1            | IRR1                | R1              | DA           | r2,r1,X       | ER1             |                |              |            |             |             |           |           |

|   | 2.2         | 2.3         | 2.2                 | 2.3                 | 3.2                 | 3.3             | 3.2          | 3.3           | 4.2             | 4.2            |              |            |             |             |           | 1.:       |

| E | RR          | RR          | BIT                 | LD                  | LD                  | LD              | LD           | LD            | LDX             | LDX            |              |            |             |             |           | cc        |

|   | R1          | IR1         | p,b,r1              | r1,lr2              | R2,R1               | IR2,R1          | R1,IM        | IR1,IM        | ER2,ER1         | IM,ER1         |              |            |             |             |           |           |

| F | 2.2<br>SWAP | 2.3<br>SWAP | 2.6<br><b>TRAP</b>  | 2.3<br>LD           | 2.8<br>MULT         | 3.3<br>LD       | 3.3<br>BTJ   | 3.4<br>BTJ    |                 |                |              | 4          |             |             |           |           |

|   | R1          | IR1         | Vector              | Ir1,r2              | RR1                 | R2,IR1          | p,b,r1,X     |               |                 |                | V            | V          |             |             |           |           |

Figure 31. First Opcode Map

Upper Nibble (Hex)

218

zilog <sub>238</sub>

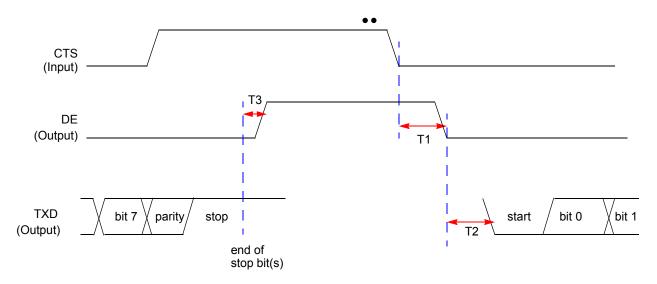

## **UART** Timing

Figure 37 and Table 142 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

|                |                                                    | Delay (ns)        |                                |  |  |  |  |

|----------------|----------------------------------------------------|-------------------|--------------------------------|--|--|--|--|

| Parameter      | Abbreviation                                       | Minimum           | Maximum                        |  |  |  |  |

| UART           |                                                    |                   |                                |  |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * XIN<br>period | 2 * XIN period<br>+ 1 bit time |  |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | / ± 5             |                                |  |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ± 5               |                                |  |  |  |  |

#### Table 142. UART Timing With CTS

Zilog <sub>243</sub>

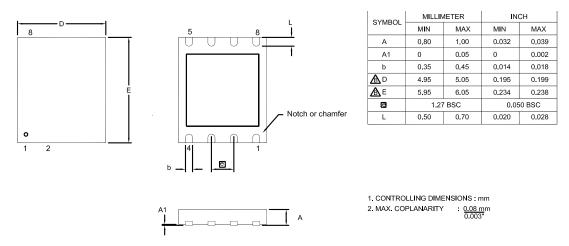

Figure 41 displays the 8-pin Quad Flat No-Lead package (QFN)/MLF-S available for the Z8 Encore! XP F082A Series devices. This package has a footprint identical to that of the 8-pin SOIC, but with a lower profile.

Figure 41. 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S

| Part Number                     | Flash      | RAM     | SUVD  | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------|------------|---------|-------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 |            |         |       | sh        |            |                     |                     |                |            |                    |                     |

| Standard Temperatur             | re: 0 °C 1 |         |       |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020SC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020SC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020SC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020SC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020SC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020SC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020SC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020SC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020SC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu              | re: -40 °  | C to 10 | 5 °C  |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020EC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020EC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020EC                  | 4 KB       | 1 KB    | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020EC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020EC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020EC                  | 4 KB       | 1 KB    | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020EC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020EC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020EC                  | 4 KB       | 1 KB    | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Replace C with G for Lea        | ad-Free P  | ackagin | g     |           |            |                     |                     |                |            |                    |                     |

zilog 257

| Part Number                     | Flash     | RAM      | SUVN   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------|-----------|----------|--------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP <sup>®</sup> F082 | A Serie   | s with 1 | KB Fla | ish, 1    | 0-Bit      | Ana                 | log-t               | o-Dig          | jital C    | Conv               | verter              |

| Standard Temperatu              | re: 0 °C  | to 70 °C | ;      |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu              | re: -40 ° | C to 10  | 5 °C   |           |            |                     |                     |                |            |                    |                     |

| Z8F012APB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EC                  | 1 KB      | 256 B    | 16 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EC                  | 1 KB      | 256 B    | 16 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EC                  | 1 KB      | 256 B    | 16 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

266

timing 237 OCD commands execute instruction (12H) 183 read data memory (0DH) 183 read OCD control register (05H) 181 read OCD revision (00H) 180 read OCD status register (02H) 180 read program counter (07H) 181 read program memory (0BH) 182 read program memory CRC (0EH) 183 read register (09H) 182 read runtime counter (03H) 180 step instruction (10H) 183 stuff instruction (11H) 183 write data memory (0CH) 182 write OCD control register (04H) 181 write program counter (06H) 181 write program memory (0AH) 182 write register (08H) 181 on-chip debugger (OCD) 173 on-chip debugger signals 12 on-chip oscillator 193 **ONE-SHOT** mode 84 opcode map abbreviations 217 cell description 216 first 218 second after 1FH 219 Operational Description 23, 33, 37, 55, 69, 91, 97, 117, 121, 134, 135, 139, 141, 153, 169, 173, 187, 193, 197 OR 205 ordering information 251 **ORX 206** oscillator signals 12

### Ρ

p 201 packaging 20-pin PDIP 244, 245 20-pin SSOP 246, 249 28-pin PDIP 247 28-pin SOIC 248

8-pin PDIP 241 8-pin SOIC 242 PDIP 248, 249 part selection guide 2 PC 202 PDIP 248, 249 peripheral AC and DC electrical characteristics 229 pin characteristics 13 **Pin Descriptions 9** polarity 201 POP 205 pop using extended addressing 205 **POPX 205** port availability, device 37 port input timing (GPIO) 235 port output timing, GPIO 236 power supply signals 13 power-down, automatic (ADC) 122 Power-on and Voltage Brownout electrical characteristics and timing 229 Power-On Reset (POR) 25 program control instructions 206 program counter 202 program memory 15 **PUSH 205** push using extended addressing 205 PUSHX 205 PWM mode 85 PxADDR register 46 PxCTL register 47

## R

R 201 r 201 RA register address 201 RCF 204 receive IrDA data 119 receiving UART data-interrupt-driven method 102 receiving UART data-polled method 101