Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082ahj020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Watchdog Timer Time-Out Response       92         Watchdog Timer Reload Unlock Sequence       93         Watchdog Timer Calibration       93         Watchdog Timer Calibration       93                                                                                       | 3<br>3                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Watchdog Timer Control Register Definitions       94         Watchdog Timer Control Register       94         Watchdog Timer Reload Upper, High and Low Byte Registers       94                                                                                                | 4                               |

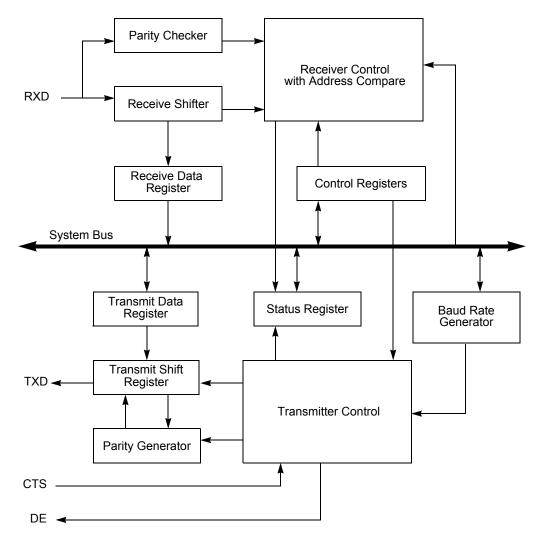

| Universal Asynchronous Receiver/Transmitter                                                                                                                                                                                                                                    | 7                               |

| Architecture       97         Operation       98         Data Format       98         Transmitting Data using the Polled Method       98                                                                                                                                       | 8<br>8                          |

| Transmitting Data using the Interrupt-Driven Method       100         Receiving Data using the Polled Method       100                                                                                                                                                         | 0<br>1                          |

| Receiving Data using the Interrupt-Driven Method       102         Clear To Send (CTS) Operation       103         MULTIPROCESSOR (9-bit) Mode       103         External Driver Enable       104         UART Interrupts       104         UART Baud Rate Generator       105 | 3<br>3<br>4<br>5                |

| UART Control Register Definitions108UART Control 0 and Control 1 Registers108UART Status 0 Register112UART Status 1 Register112UART Transmit Data Register113UART Receive Data Register113UART Address Compare Register114UART Baud Rate High and Low Byte Registers114        | 8<br>8<br>1<br>2<br>3<br>3<br>4 |

| Infrared Encoder/Decoder 112                                                                                                                                                                                                                                                   | 7                               |

| Architecture       117         Operation       117         Transmitting IrDA Data       118         Receiving IrDA Data       119         Infrared Encoder Control Decistor Definitions       120                                                                              | 7<br>8<br>9                     |

| Infrared Encoder/Decoder Control Register Definitions                                                                                                                                                                                                                          |                                 |

| Analog-to-Digital Converter                                                                                                                                                                                                                                                    |                                 |

| Architecture         12           Operation         122           Data Format         122                                                                                                                                                                                      | 2                               |

vii

- Up to thirteen 5 V-tolerant input pins

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brownout (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO, and LVD

- Power-On Reset (POR)

- 2.7 V to 3.6 V operating voltage

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

# **Part Selection Guide**

Table 1 on page 3 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F082A Series product line.

# Table 2. Signal Descriptions (Continued)

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Analog              |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| ANA[7:0]            | I       | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                       |  |  |  |  |  |

| VREF                | I/O     | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                               |  |  |  |  |  |

| Low-Power Operation | onal An | nplifier (LPO)                                                                                                                                                                                                                                                                |  |  |  |  |  |

| AMPINP/AMPINN       | Ι       | LPO inputs. If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                                                                                                                                             |  |  |  |  |  |

| AMPOUT              | 0       | LPO output. If enabled, this pin is driven by the on-chip LPO.                                                                                                                                                                                                                |  |  |  |  |  |

| Oscillators         |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| XIN                 | I       | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the <b>XOUT</b> pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |  |  |  |  |  |

| XOUT                | 0       | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                               |  |  |  |  |  |

| Clock Input         |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| CLKIN               | I       | Clock Input Signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                          |  |  |  |  |  |

| LED Drivers         |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| LED                 | 0       | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                                                                                   |  |  |  |  |  |

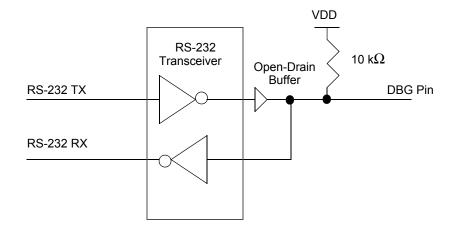

| On-Chip Debugger    |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| DBG                 | I/O     | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                                 |  |  |  |  |  |

|                     |         | <b>Caution:</b> The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                         |  |  |  |  |  |

| Reset               |         |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| RESET               | I/O     | RESET. Generates a Reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin low when in reset. This pin is open-drain and features an enabled internal pull-up resistor.                                                         |  |  |  |  |  |

12

zilog

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted Low, the Z8 Encore! XP<sup>®</sup> F082A Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the System Reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a System Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–D Control Registers on page 46), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

# **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) register is set.

# Stop Mode Recovery

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. See Low-Power Modes on page 33 for detailed STOP mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see Table 131 on page 229)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

# zilog <sub>37</sub>

# **General-Purpose Input/Output**

The Z8 Encore! XP<sup>®</sup> F082A Series products support a maximum of 25 port pins (Ports A– D) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality, and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

# **GPIO Port Availability By Device**

Table 13 lists the port pins available with each device and package type.

| Devices                         | Package | ADC | Port A | Port B | Port C | Port D | Total I/O |

|---------------------------------|---------|-----|--------|--------|--------|--------|-----------|

| Z8F082ASB, Z8F082APB, Z8F082AQB | 8-pin   | Yes | [5:0]  | No     | No     | No     | 6         |

| Z8F042ASB, Z8F042APB, Z8F042AQB |         |     |        |        |        |        |           |

| Z8F022ASB, Z8F022APB, Z8F022AQB |         |     |        |        |        |        |           |

| Z8F012ASB, Z8F012APB, Z8F012AQB |         |     |        |        |        |        |           |

| Z8F081ASB, Z8F081APB, Z8F081AQB | 8-pin   | No  | [5:0]  | No     | No     | No     | 6         |

| Z8F041ASB, Z8F041APB, Z8F041AQB |         |     |        |        |        |        |           |

| Z8F021ASB, Z8F021APB, Z8F021AQB |         |     |        |        |        |        |           |

| Z8F011ASB, Z8F011APB, Z8F011AQB |         |     |        |        |        |        |           |

| Z8F082APH, Z8F082AHH, Z8F082ASH | 20-pin  | Yes | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F042APH, Z8F042AHH, Z8F042ASH |         |     |        |        |        |        |           |

| Z8F022APH, Z8F022AHH, Z8F022ASH |         |     |        |        |        |        |           |

| Z8F012APH, Z8F012AHH, Z8F012ASH |         |     |        |        |        |        |           |

| Z8F081APH, Z8F081AHH, Z8F081ASH | 20-pin  | No  | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F041APH, Z8F041AHH, Z8F041ASH | •       |     |        |        |        |        |           |

| Z8F021APH, Z8F021AHH, Z8F021ASH |         |     |        |        |        |        |           |

| Z8F011APH, Z8F011AHH, Z8F011ASH |         |     |        |        |        |        |           |

| Z8F082APJ, Z8F082ASJ, Z8F082AHJ | 28-pin  | Yes | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F042APJ, Z8F042ASJ, Z8F042AHJ | •       |     |        |        |        |        |           |

| Z8F022APJ, Z8F022ASJ, Z8F022AHJ |         |     |        |        |        |        |           |

| Z8F012APJ, Z8F012ASJ, Z8F012AHJ |         |     |        |        |        |        |           |

| Z8F081APJ, Z8F081ASJ, Z8F081AHJ | 28-pin  | No  | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

| Z8F041APJ, Z8F041ASJ, Z8F041AHJ | •       |     |        |        |        |        |           |

| Z8F021APJ, Z8F021ASJ, Z8F021AHJ |         |     |        |        |        |        |           |

| Z8F011APJ, Z8F011ASJ, Z8F011AHJ |         |     |        |        |        |        |           |

#### Table 13. Port Availability by Device and Package Type

Zilog <sub>42</sub>

| Port   | Pin | Mnemonic    | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|--------------------------------|-----------------------------------------|

| Port B | PB0 | Reserved    |                                | AFS1[0]: 0                              |

|        |     | ANA0/AMPOUT | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|        | PB1 | Reserved    |                                | AFS1[1]: 0                              |

|        |     | ANA1/AMPINN | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|        | PB2 | Reserved    |                                | AFS1[2]: 0                              |

|        |     | ANA2/AMPINP | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|        | PB3 | CLKIN       | External Clock Input           | AFS1[3]: 0                              |

|        |     | ANA3        | ADC Analog Input               | AFS1[3]: 1                              |

|        | PB4 | Reserved    |                                | AFS1[4]: 0                              |

|        |     | ANA7        | ADC Analog Input               | AFS1[4]: 1                              |

|        | PB5 | Reserved    |                                | AFS1[5]: 0                              |

|        |     | VREF*       | ADC Voltage Reference          | AFS1[5]: 1                              |

|        | PB6 | Reserved    |                                | AFS1[6]: 0                              |

|        |     | Reserved    |                                | AFS1[6]: 1                              |

|        | PB7 | Reserved    |                                | AFS1[7]: 0                              |

|        |     | Reserved    |                                | AFS1[7]: 1                              |

#### Table 14. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Note: Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is not used to select the function. Also, alternate function selection as described in Port A-D Alternate Function Sub-Registers on page 47 must also be enabled.

\* VREF is available on PB5 in 28-pin products only.

# Operation

#### **Data Format**

The UART always transmits and receives data in an 8-bit data format, least-significant bit first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low START bit and ends with either 1 or 2 active High STOP bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

zilog

send. This action provides 7 bit periods of latency to load the Transmit Data register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

- A data byte is received and is available in the UART Receive Data register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

- · |

**Note:** In MULTIPROCESSOR mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data register must be read again to clear the error bits is the UART Status 0 register. Updates to the Receive Data register occur only when the next data word is received.

#### **UART Data and Error Handling Procedure**

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is Low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled.

1 = Transmitter enabled.

REN—Receive Enable

This bit enables or disables the receiver.

0 = Receiver disabled.

1 =Receiver enabled.

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter.

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter.

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled.

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data.

1 = Odd parity is transmitted and expected on all received data.

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit. 0 = No break is sent.

0 = No break is sent.

1 = Forces a break condition by setting the output of the transmitter to zero.

STOP—Stop Bit Select

0 = The transmitter sends one stop bit.

1 = The transmitter sends two stop bits.

LBEN—Loop Back Enable

0 = Normal operation.

1 = All transmitted data is looped back to the receiver.

### Table 62. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6                       | 5       | 4    | 3     | 2      | 1      | 0    |  |  |

|-------|---------|-------------------------|---------|------|-------|--------|--------|------|--|--|

| FIELD | MPMD[1] | MPEN                    | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |  |

| RESET | 0       | 0                       | 0       | 0    | 0     | 0      | 0      | 0    |  |  |

| R/W   | R/W     | R/W R/W R/W R/W R/W R/W |         |      |       |        |        |      |  |  |

| ADDR  |         |                         |         | F4   | 3H    |        |        |      |  |  |

zilog<sup>°</sup>

#### ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all Port pins in this list are available in all packages for the Z8 Encore! XP<sup>®</sup> F082A Series. For information on port pins available with each package style, see Pin Description on page 9. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

SINGLE-ENDED:

- 0000 = ANA0 (transimpedance amp output when enabled)

- 0001 = ANA1 (transimpedance amp inverting input)

- 0010 = ANA2 (transimpedance amp non-inverting input)

- 0011 = ANA3

- 0100 = ANA4

- 0101 = ANA5

- 0110 = ANA6

- 0111 = ANA7

- 1000 = Reserved

- 1001 = Reserved

- 1010 = Reserved

- 1011 = Reserved

- 1100 = Hold transimpedance input nodes (ANA1 and ANA2) to ground.

- 1101 = Reserved

- 1110 = Temperature Sensor.

- 1111 = Reserved.

DIFFERENTIAL (non-inverting input and inverting input respectively):

- 0000 = ANA0 and ANA10001 = ANA2 and ANA30010 = ANA4 and ANA50011 = ANA1 and ANA00100 = ANA3 and ANA20101 = ANA5 and ANA40110 = ANA6 and ANA50111 = ANA0 and ANA50111 = ANA0 and ANA21000 = ANA0 and ANA31001 = ANA0 and ANA41010 = ANA0 and ANA51011 = Reserved1100 = Reserved1101 = Reserved1101 = Reserved1110 = Reserved

- 1111 = Manual Offset Calibration Mode

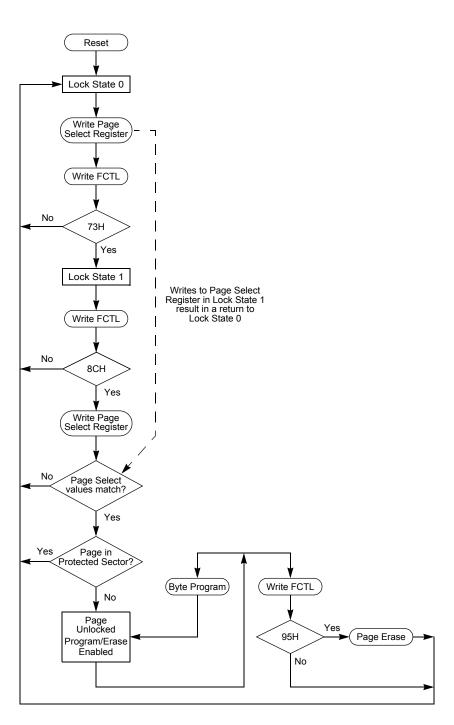

Figure 22. Flash Controller Operation Flow Chart

Zilog 14

the OCD or via the Flash Controller Bypass mode are unaffected. After a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

# **Byte Programming**

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully completed, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming can be accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. Refer to the *eZ8 CPU User Manual* (available for download at <u>www.zilog.com</u>) for a description of the LDC and LDCI instructions. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

#### Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### Mass Erase

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the

# Trim Bit Address 0004H

# Table 92. Trim Option Bits at 0004H

| BITS      | 7                               | 6            | 5            | 4          | 3   | 2   | 1   | 0   |  |  |  |

|-----------|---------------------------------|--------------|--------------|------------|-----|-----|-----|-----|--|--|--|

| FIELD     | Reserved                        |              |              |            |     |     |     |     |  |  |  |

| RESET     | U                               | U            | U            | U          | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                             | R/W          | R/W          | R/W        | R/W | R/W | R/W | R/W |  |  |  |

| ADDR      | R Information Page Memory 0024H |              |              |            |     |     |     |     |  |  |  |

| Note: U = | Jnchanged b                     | y Reset. R/W | = Read/Write | <b>)</b> . |     |     |     |     |  |  |  |

Reserved—Altering this register may result in incorrect device operation.

# Zilog Calibration Data

# ADC Calibration Data

# Table 93. ADC Calibration Bits

| BITS      | 7                                   | 6                       | 5            | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------|-------------------------------------|-------------------------|--------------|---|---|---|---|---|--|--|--|

| FIELD     | ADC_CAL                             |                         |              |   |   |   |   |   |  |  |  |

| RESET     | U                                   | U                       | U            | U | U | U | U | U |  |  |  |

| R/W       | R/W                                 | R/W R/W R/W R/W R/W R/W |              |   |   |   |   |   |  |  |  |

| ADDR      | Information Page Memory 0060H–007DH |                         |              |   |   |   |   |   |  |  |  |

| Note: U = | Unchanged b                         | y Reset. R/W            | = Read/Write |   |   |   |   |   |  |  |  |

ADC\_CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as described in Software Compensation Procedure Using Factory Calibration Data on page 126. The location of each calibration byte is provided in Table 94 on page 162.

#### Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

# **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions.

- The system clock operates unless in STOP mode.

- All enabled on-chip peripherals operate unless in STOP mode.

- Automatically exits HALT mode.

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG mode are:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (Breakpoint) instruction.

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG mode immediately (20-/28-pin products only).

- **Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 176).

**z**ilog<sup>®</sup>

203

Table 116 through Table 123 lists the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| СР       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| CPX      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### **Table 116. Arithmetic Instructions**

**z**ilog<sup>°</sup>

| 2 | n | 0 |

|---|---|---|

| 4 | υ | 3 |

| Assembly        | Symbolic                                                                                         | Addres        | s Mode   | Opcode(s) |   |          | Fla | ags |   |   | Fetch  | Instr. |

|-----------------|--------------------------------------------------------------------------------------------------|---------------|----------|-----------|---|----------|-----|-----|---|---|--------|--------|

| Mnemonic        | Operation                                                                                        | dst           | src      | (Hex)     | С | Ζ        | S   | ۷   | D | Н | Cycles |        |

| COM dst         | $dst \gets \simdst$                                                                              | R             |          | 60        | - | *        | *   | 0   | - | - | 2      | 2      |

|                 |                                                                                                  | IR            |          | 61        | - |          |     |     |   |   | 2      | 3      |

| CP dst, src     | dst - src                                                                                        | r             | r        | A2        | * | *        | *   | *   | - | - | 2      | 3      |

|                 |                                                                                                  | r             | lr       | A3        | - |          |     |     |   |   | 2      | 4      |

|                 |                                                                                                  | R             | R        | A4        | - |          |     |     |   |   | 3      | 3      |

|                 |                                                                                                  | R             | IR       | A5        | - |          |     |     |   |   | 3      | 4      |

|                 |                                                                                                  | R             | IM       | A6        | - |          |     |     |   |   | 3      | 3      |

|                 |                                                                                                  | IR            | IM       | A7        | - |          |     |     |   |   | 3      | 4      |

| CPC dst, src    | dst - src - C                                                                                    | r             | r        | 1F A2     | * | *        | *   | *   | - | - | 3      | 3      |

|                 |                                                                                                  | r             | lr       | 1F A3     | - |          |     |     |   |   | 3      | 4      |

|                 |                                                                                                  | R             | R        | 1F A4     | - |          |     |     |   |   | 4      | 3      |

|                 |                                                                                                  | R             | IR       | 1F A5     | - |          |     |     |   |   | 4      | 4      |

|                 |                                                                                                  | R             | IM       | 1F A6     | - |          |     |     |   |   | 4      | 3      |

|                 |                                                                                                  | IR            | IM       | 1F A7     | - |          |     |     |   |   | 4      | 4      |

| CPCX dst, src   | dst - src - C                                                                                    | ER            | ER       | 1F A8     | * | *        | *   | *   | _ | _ | 5      | 3      |

|                 |                                                                                                  | ER            | IM       | 1F A9     | - |          |     |     |   |   | 5      | 3      |

| CPX dst, src    | dst - src                                                                                        | ER            | ER       | A8        | * | *        | *   | *   | _ | _ | 4      | 3      |

|                 |                                                                                                  | ER            | IM       | A9        | - |          |     |     |   |   | 4      | 3      |

| DA dst          | $dst \gets DA(dst)$                                                                              | R             |          | 40        | * | *        | *   | Х   | _ | _ | 2      | 2      |

|                 |                                                                                                  | IR            |          | 41        | - |          |     |     |   |   | 2      | 3      |

| DEC dst         | $dst \gets dst \text{ - } 1$                                                                     | R             |          | 30        | _ | *        | *   | *   | _ | _ | 2      | 2      |

|                 |                                                                                                  | IR            |          | 31        | - |          |     |     |   |   | 2      | 3      |

| DECW dst        | $dst \gets dst \text{ - } 1$                                                                     | RR            |          | 80        | _ | *        | *   | *   | _ | _ | 2      | 5      |

|                 |                                                                                                  | IRR           |          | 81        | - |          |     |     |   |   | 2      | 6      |

| DI              | $IRQCTL[7] \leftarrow 0$                                                                         |               |          | 8F        | _ | _        | _   | _   | _ | _ | 1      | 2      |

| DJNZ dst, RA    | $\begin{array}{l} dst \leftarrow dst - 1 \\ if \ dst \neq 0 \\ PC \leftarrow PC + X \end{array}$ | r             |          | 0A-FA     | _ | _        | _   | _   | _ | _ | 2      | 3      |

| EI              | $IRQCTL[7] \leftarrow 1$                                                                         |               |          | 9F        | _ | -        | -   | _   | - | - | 1      | 2      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined                                       | of the result | of the o | peration. |   | Re<br>Se |     |     | ) |   |        |        |

# Table 124. eZ8 CPU Instruction Summary (Continued)

zilog <sub>217</sub>

| Abbreviation | Description                           | Abbreviation                                   | Description            |

|--------------|---------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |

| сс           | Condition code                        | р                                              | Polarity (0 or 1)      |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                   | R                                              | 8-bit register         |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register             | RA                                             | Relative               |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |

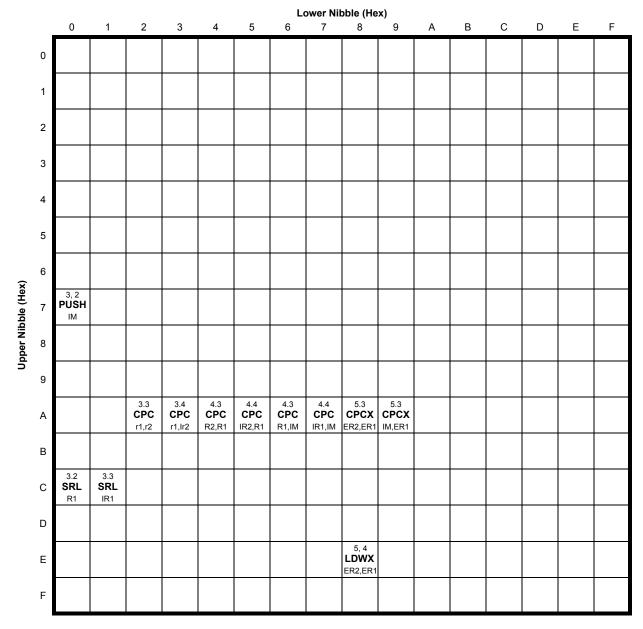

# Table 125. Opcode Map Abbreviations

223

|                   |                               | T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise specified) |                  |            |       |                                                                                 |  |

|-------------------|-------------------------------|--------------------------------------------------------------------|------------------|------------|-------|---------------------------------------------------------------------------------|--|

| Symbol            | Parameter                     | Minimum                                                            | Typical          | Maximum    | Units | Conditions                                                                      |  |

| V <sub>OL2</sub>  | Low Level Output<br>Voltage   | -                                                                  | -                | 0.6        | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.  |  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4                                                                | _                | -          | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |  |

| I <sub>IH</sub>   | Input Leakage<br>Current      | -                                                                  | <u>+</u> 0.002   | <u>+</u> 5 | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |  |

| IIL               | Input Leakage<br>Current      | -                                                                  | <u>+</u> 0.007   | <u>+</u> 5 | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -                                                                  | _                | <u>+</u> 5 | μA    |                                                                                 |  |

| I <sub>LED</sub>  | Controlled Current<br>Drive   | 1.8                                                                | 3                | 4.5        | mA    | {AFS2,AFS1} = {0,0}                                                             |  |

|                   |                               | 2.8                                                                | 7                | 10.5       | mA    | {AFS2,AFS1} = {0,1}                                                             |  |

|                   |                               | 7.8                                                                | 13               | 19.5       | mA    | {AFS2,AFS1} = {1,0}                                                             |  |

|                   |                               | 12                                                                 | 20               | 30         | mA    | {AFS2,AFS1} = {1,1}                                                             |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -                                                                  | 8.0 <sup>2</sup> | -          | pF    |                                                                                 |  |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -                                                                  | 8.0 <sup>2</sup> | _          | pF    |                                                                                 |  |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -                                                                  | 9.5 <sup>2</sup> | -          | pF    |                                                                                 |  |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30                                                                 | 100              | 350        | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |  |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD                                                                |                  |            | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |  |

|                   |                               |                                                                    | -                |            | -     |                                                                                 |  |

### Table 127. DC Characteristics (Continued)

#### Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

| V <sub>DD</sub> = 2.7 V to 3.6 V |                                                                               |              |                      |          |       |                                                                  |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------|--------------|----------------------|----------|-------|------------------------------------------------------------------|--|--|--|

|                                  |                                                                               |              | Maximum <sup>2</sup> | _        |       |                                                                  |  |  |  |

| Symbol                           | Parameter                                                                     | Typical $^1$ | Std Temp             | Ext Temp | Units | Conditions                                                       |  |  |  |

| I <sub>DD</sub> Stop             | Supply Current in STOP<br>Mode                                                | 0.1          |                      |          | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |  |  |  |

| I <sub>DD</sub> Halt             | Supply Current in HALT                                                        | 35           | 55                   | 65       | μA    | 32 kHz                                                           |  |  |  |

|                                  | Mode (with all peripherals disabled)                                          | 520          |                      |          | μA    | 5.5 MHz                                                          |  |  |  |

|                                  |                                                                               | 2.1          | 2.85                 | 2.85     | mA    | 20 MHz                                                           |  |  |  |

| I <sub>DD</sub>                  | Supply Current in<br>ACTIVE Mode (with all<br>peripherals disabled)           | 2.8          |                      |          | mA    | 32 kHz                                                           |  |  |  |

|                                  |                                                                               | 4.5          | 5.2                  | 5.2      | mA    | 5.5 MHz                                                          |  |  |  |

|                                  |                                                                               | 5.5          | 6.5                  | 6.5      | mA    | 10 MHz                                                           |  |  |  |

|                                  | -                                                                             | 7.9          | 11.5                 | 11.5     | mA    | 20 MHz                                                           |  |  |  |

| I <sub>DD</sub> WDT              | Watchdog Timer Supply<br>Current                                              | 0.9          | 1.0                  | 1.1      | μA    |                                                                  |  |  |  |

| I <sub>DD</sub><br>XTAL          | Crystal Oscillator<br>Supply Current                                          | 40           |                      |          | μA    | 32 kHz                                                           |  |  |  |

|                                  |                                                                               | 230          |                      |          | μA    | 4 MHz                                                            |  |  |  |

|                                  | -                                                                             | 760          |                      |          | μA    | 20 MHz                                                           |  |  |  |

| I <sub>DD</sub> IPO              | Internal Precision<br>Oscillator Supply<br>Current                            | 350          | 500                  | 550      | μA    |                                                                  |  |  |  |

| I <sub>DD</sub> VBO              | Low-Voltage Detect                                                            | 50           |                      |          | μA    | For 20-/28-pin devices<br>(VBO only); See Notes 4                |  |  |  |

|                                  | Supply Current                                                                |              |                      |          |       | For 8-pin devices; See<br>Notes 4                                |  |  |  |

| I <sub>DD</sub> ADC              | Analog to Digital<br>Converter Supply<br>Current (with External<br>Reference) | 2.8          | 3.1                  | 3.2      | mA    | 32 kHz                                                           |  |  |  |

|                                  |                                                                               | 3.1          | 3.6                  | 3.7      | mA    | 5.5 MHz                                                          |  |  |  |

|                                  |                                                                               | 3.3          | 3.7                  | 3.8      | mA    | 10 MHz                                                           |  |  |  |

|                                  | -                                                                             | 3.7          | 4.2                  | 4.3      | mA    | 20 MHz                                                           |  |  |  |

| I <sub>DD</sub><br>ADCRef        | ADC Internal Reference<br>Supply Current                                      | 0            |                      |          | μA    | See Notes 4                                                      |  |  |  |

| I <sub>DD</sub> CMP              | Comparator supply<br>Current                                                  | 150          | 180                  | 190      | μA    | See Notes 4                                                      |  |  |  |

# Table 128. Power Consumption