Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                       |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082apb020ec    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Reset, Stop Mode Recovery, and Low Voltage Detection | 23 |

|------------------------------------------------------|----|

| Reset Types                                          | 23 |

| Reset Sources                                        |    |

| Power-On Reset                                       |    |

| Voltage Brownout Reset                               |    |

| Watchdog Timer Reset       External Reset Input      |    |

| External Reset Indicator                             |    |

| On-Chip Debugger Initiated Reset                     |    |

| Stop Mode Recovery                                   | 28 |

| Stop Mode Recovery Using Watchdog Timer Time-Out     | 29 |

| Stop Mode Recovery Using a GPIO Port Pin Transition  |    |

| Stop Mode Recovery Using the External RESET Pin      |    |

| Low Voltage Detection                                |    |

| Reset Register Definitions                           | 30 |

| Low-Power Modes                                      | 33 |

| STOP Mode                                            | 33 |

| HALT Mode                                            | 34 |

| Peripheral-Level Power Control                       | 34 |

| Power Control Register Definitions                   | 34 |

| General-Purpose Input/Output                         | 37 |

| GPIO Port Availability By Device                     | 37 |

| Architecture                                         | 38 |

| GPIO Alternate Functions                             | 38 |

| Direct LED Drive                                     | 39 |

| Shared Reset Pin                                     | 39 |

| Shared Debug Pin                                     | 39 |

| Crystal Oscillator Override                          | 40 |

| 5 V Tolerance                                        | 40 |

| External Clock Setup                                 | 40 |

| GPIO Interrupts                                      | 45 |

| GPIO Control Register Definitions                    | 45 |

| Port A–D Address Registers                           |    |

| Port A–D Control Registers                           |    |

| Port A D Data Direction Sub-Registers                |    |

| Port A–D Alternate Function Sub-Registers            | 41 |

#### **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

#### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

#### General-Purpose Input/Output

The Z8 Encore! XP F082A Series features 6 to 25 port pins (Ports A–D) for general- purpose input/output (GPIO). The number of GPIO pins available is a function of package, and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

#### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

#### **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, as well as factory serialization and read protection.

#### Non-Volatile Data Storage

The non-volatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8 KB Flash memory do not include the NVDS feature.

zilog

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the  $\overline{\text{RESET}}$  input pin is asserted Low, the Z8 Encore! XP<sup>®</sup> F082A Series devices remain in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the System Reset time-out, the device exits the Reset state on the system clock rising edge following  $\overline{\text{RESET}}$  pin deassertion. Following a System Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Reset Status (RSTSTAT) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–D Control Registers on page 46), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) register is set.

#### Stop Mode Recovery

STOP mode is entered by execution of a STOP instruction by the eZ8 CPU. See Low-Power Modes on page 33 for detailed STOP mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see Table 131 on page 229)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

# **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

#### **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

<mark>z</mark>ilog<sup>°</sup>

#### 44

| Port   | Pin | Mnemonic          | Alternate Function Description            | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select Register<br>AFS2 |

|--------|-----|-------------------|-------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| Port A | PA0 | TOIN              | Timer 0 Input                             | AFS1[0]: 0                                    | AFS2[0]: 0                                       |

|        |     | Reserved          |                                           | AFS1[0]: 0                                    | AFS2[0]: 1                                       |

|        |     | Reserved          |                                           | AFS1[0]: 1                                    | AFS2[0]: 0                                       |

|        |     | TOOUT             | Timer 0 Output Complement                 | AFS1[0]: 1                                    | AFS2[0]: 1                                       |

|        | PA1 | TOOUT             | Timer 0 Output                            | AFS1[1]: 0                                    | AFS2[1]: 0                                       |

|        |     | Reserved          |                                           | AFS1[1]: 0                                    | AFS2[1]: 1                                       |

|        |     | CLKIN             | External Clock Input                      | AFS1[1]: 1                                    | AFS2[1]: 0                                       |

|        |     | Analog Functions* | ADC Analog Input/VREF                     | AFS1[1]: 1                                    | AFS2[1]: 1                                       |

|        | PA2 | DE0               | UART 0 Driver Enable                      | AFS1[2]: 0                                    | AFS2[2]: 0                                       |

|        |     | RESET             | External Reset                            | AFS1[2]: 0                                    | AFS2[2]: 1                                       |

|        |     | T1OUT             | Timer 1 Output                            | AFS1[2]: 1                                    | AFS2[2]: 0                                       |

|        |     | Reserved          |                                           | AFS1[2]: 1                                    | AFS2[2]: 1                                       |

|        | PA3 | CTS0              | UART 0 Clear to Send                      | AFS1[3]: 0                                    | AFS2[3]: 0                                       |

|        |     | COUT              | Comparator Output                         | AFS1[3]: 0                                    | AFS2[3]: 1                                       |

|        |     | T1IN              | Timer 1 Input                             | AFS1[3]: 1                                    | AFS2[3]: 0                                       |

|        |     | Analog Functions* | ADC Analog Input/LPO Input (P)            | AFS1[3]: 1                                    | AFS2[3]: 1                                       |

|        | PA4 | RXD0              | UART 0 Receive Data                       | AFS1[4]: 0                                    | AFS2[4]: 0                                       |

|        |     | Reserved          |                                           | AFS1[4]: 0                                    | AFS2[4]: 1                                       |

|        |     | Reserved          |                                           | AFS1[4]: 1                                    | AFS2[4]: 0                                       |

|        |     | Analog Functions* | ADC/Comparator Input (N)/LPO<br>Input (N) | AFS1[4]: 1                                    | AFS2[4]: 1                                       |

|        | PA5 | TXD0              | UART 0 Transmit Data                      | AFS1[5]: 0                                    | AFS2[5]: 0                                       |

|        |     | T10UT             | Timer 1 Output Complement                 | AFS1[5]: 0                                    | AFS2[5]: 1                                       |

|        |     | Reserved          |                                           | AFS1[5]: 1                                    | AFS2[5]: 0                                       |

|        |     | Analog Functions* | ADC/Comparator Input (P) LPO<br>Output    | AFS1[5]: 1                                    | AFS2[5]: 1                                       |

|        |     |                   |                                           |                                               |                                                  |

#### Table 15. Port Alternate Function Mapping (8-Pin Parts)

\*Analog Functions include ADC inputs, ADC reference, comparator inputs and LPO ports.

**Note:** Also, alternate function selection as described in Port A–D Alternate Function Sub-Registers on page 47 must be enabled.

function). (Push-pull output)

1 = The source current for the associated pin is disabled (open-drain mode).

#### Port A–D High Drive Enable Sub-Registers

The Port A–D High Drive Enable sub-register (Table 22) is accessed through the Port A–D Control register by writing 04H to the Port A–D Address register. Setting the bits in the Port A–D High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

Table 22. Port A–D High Drive Enable Sub-Registers (PxHDE)

| BITS  | 7        | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| FIELD | PHDE7    | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET | 0        | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W   | R/W      | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| ADDR  | lf 04H i | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |

PHDE[7:0]—Port High Drive Enabled

0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

#### Port A–D Stop Mode Recovery Source Enable Sub-Registers

The Port A–D Stop Mode Recovery Source Enable sub-register (Table 23) is accessed through the Port A–D Control register by writing 05H to the Port A–D Address register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable sub-registers to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

| BITS  | 7        | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| FIELD | PSMRE7   | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |

| RESET | 0        | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W   | R/W      | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| ADDR  | lf 05H i | If 05H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin

62

#### Interrupt Request 2 Register

The Interrupt Request 2 (IRQ2) register (Table 35) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

#### Table 35. Interrupt Request 2 Register (IRQ2)

| BITS  | 7   | 6        | 5   | 4   | 3    | 2    | 1    | 0    |

|-------|-----|----------|-----|-----|------|------|------|------|

| FIELD |     | Reserved |     |     | PC3I | PC2I | PC1I | PC0I |

| RESET | 0   | 0        | 0   | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W      | R/W | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     | FC6H     |     |     |      |      |      |      |

Reserved—Must be 0.

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x.

1 = An interrupt request from GPIO Port C pin x is awaiting service.

where x indicates the specific GPIO Port C pin number (0-3).

#### **IRQ0 Enable High and Low Bit Registers**

Table 36 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 37 and Table 38) form a priority encoded enabling for interrupts in the Interrupt Request 0 register.

#### Table 36. IRQ0 Enable and Priority Encoding

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Medium      |

| 1          | 1          | Level 3  | High        |

where x indicates the register bits from 0–7.

Zilog

Endec, and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

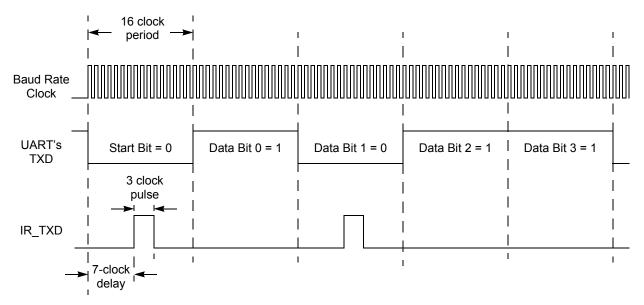

#### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP<sup>®</sup> F082A Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

Zilog

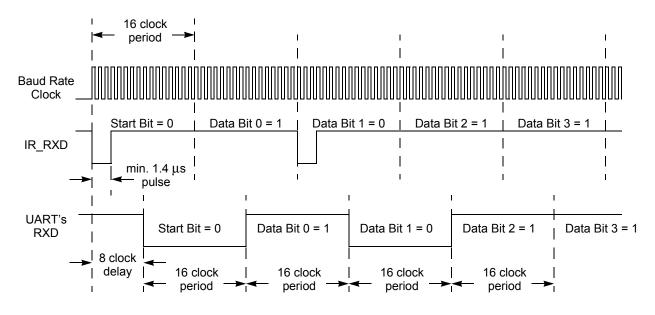

#### **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F082A Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the  $1.4 \,\mu s$  minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

# zilog

180

| Debug Command           | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by<br>Flash Read Protect Option Bit                                                                                                                              |

|-------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Register          | 08H             | -                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register           | 09H             | _                                     | Disabled                                                                                                                                                                  |

| Write Program Memory    | 0AH             | _                                     | Disabled                                                                                                                                                                  |

| Read Program Memory     | 0BH             | _                                     | Disabled                                                                                                                                                                  |

| Write Data Memory       | 0CH             | _                                     | Yes                                                                                                                                                                       |

| Read Data Memory        | 0DH             | _                                     | -                                                                                                                                                                         |

| Read Program Memory CRC | 0EH             | _                                     | -                                                                                                                                                                         |

| Reserved                | 0FH             | _                                     | -                                                                                                                                                                         |

| Step Instruction        | 10H             | _                                     | Disabled                                                                                                                                                                  |

| Stuff Instruction       | 11H             | _                                     | Disabled                                                                                                                                                                  |

| Execute Instruction     | 12H             | _                                     | Disabled                                                                                                                                                                  |

| Reserved                | 13H–FFH         | _                                     | _                                                                                                                                                                         |

In the following bulleted list of OCD Commands, data and commands sent from the host to the On-Chip Debugger are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the On-Chip Debugger back to the host is identified by 'DBG  $\rightarrow$  Data'

• **Read OCD Revision (00H)**—The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

• **Read OCD Status Register (02H)**—The Read OCD Status Register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

• **Read Runtime Counter (03H)**—The Runtime Counter counts system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the

zilog

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F082A Series device ceases functioning and can only be recovered by Power-On-Reset.

### **Oscillator Control Register Definitions**

#### **Oscillator Control Register**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

| BITS  | 7     | 6     | 5     | 4     | 3     | 2   | 1      | 0   |

|-------|-------|-------|-------|-------|-------|-----|--------|-----|

| FIELD | INTEN | XTLEN | WDTEN | SOFEN | WDFEN |     | SCKSEL |     |

| RESET | 1     | 0     | 1     | 0     | 0     | 0   | 0      | 0   |

| R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W | R/W    | R/W |

| ADDR  |       |       |       | F8    | 6H    |     |        |     |

#### Table 109. Oscillator Control Register (OSCCTL)

INTEN—Internal Precision Oscillator Enable

1 = Internal precision oscillator is enabled

0 = Internal precision oscillator is disabled

XTLEN-Crystal Oscillator Enable; this setting overrides the GPIO register control for PA0 and PA1

1 = Crystal oscillator is enabled

0 = Crystal oscillator is disabled

WDTEN—Watchdog Timer Oscillator Enable

1 = Watchdog Timer oscillator is enabled

0 = Watchdog Timer oscillator is disabled

SOFEN—System Clock Oscillator Failure Detection Enable

1 = Failure detection and recovery of system clock oscillator is enabled

0 = Failure detection and recovery of system clock oscillator is disabled

204

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 118. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses       |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

#### Table 119. CPU Control Instructions

| Mnemonic | Operands | Instruction           |  |  |  |

|----------|----------|-----------------------|--|--|--|

| ATM      | _        | Atomic Execution      |  |  |  |

| CCF      | _        | Complement Carry Flag |  |  |  |

| DI       | _        | Disable Interrupts    |  |  |  |

| EI       | _        | Enable Interrupts     |  |  |  |

| HALT     | _        | Halt Mode             |  |  |  |

| NOP      | _        | No Operation          |  |  |  |

| RCF      | _        | Reset Carry Flag      |  |  |  |

zilog

207

#### Table 123. Rotate and Shift Instructions (Continued)

| Mnemonic | Operands | Instruction            |  |  |  |

|----------|----------|------------------------|--|--|--|

| SRA      | dst      | Shift Right Arithmetic |  |  |  |

| SRL      | dst      | Shift Right Logical    |  |  |  |

| SWAP     | dst      | Swap Nibbles           |  |  |  |

### eZ8 CPU Instruction Summary

Table 124 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly<br>Mnemonic | Symbolic<br>Operation                                      | Addres        | Address Mode |                    | Flags |          |   |           |   | Fetch | Instr. |   |

|----------------------|------------------------------------------------------------|---------------|--------------|--------------------|-------|----------|---|-----------|---|-------|--------|---|

|                      |                                                            | dst           | src          | Opcode(s)<br>(Hex) | С     | Ζ        | S | ۷         | D | Н     |        |   |

| ADC dst, src         | $dst \gets dst + src + C$                                  | r             | r            | 12                 | *     | *        | * | *         | 0 | *     | 2      | 3 |

|                      |                                                            | r             | lr           | 13                 | -     |          |   |           |   |       | 2      | 4 |

|                      |                                                            | R             | R            | 14                 | -     |          |   |           |   |       | 3      | 3 |

|                      |                                                            | R             | IR           | 15                 | -     |          |   |           |   |       | 3      | 4 |

|                      |                                                            | R             | IM           | 16                 | -     |          |   |           |   |       | 3      | 3 |

|                      |                                                            | IR            | IM           | 17                 | -     |          |   |           |   |       | 3      | 4 |

| ADCX dst, src        | $dst \gets dst + src + C$                                  | ER            | ER           | 18                 | *     | *        | * | *         | 0 | *     | 4      | 3 |

|                      |                                                            | ER            | IM           | 19                 | -     |          |   |           |   |       | 4      | 3 |

| ADD dst, src         | $dst \gets dst + src$                                      | r             | r            | 02                 | *     | *        | * | *         | 0 | *     | 2      | 3 |

|                      |                                                            | r             | lr           | 03                 | -     |          |   |           |   |       | 2      | 4 |

|                      |                                                            | R             | R            | 04                 | -     |          |   |           |   |       | 3      | 3 |

|                      |                                                            | R             | IR           | 05                 | -     |          |   |           |   |       | 3      | 4 |

|                      |                                                            | R             | IM           | 06                 | -     |          |   |           |   |       | 3      | 3 |

|                      |                                                            | IR            | IM           | 07                 | -     |          |   |           |   |       | 3      | 4 |

| ADDX dst, src        | $dst \gets dst + src$                                      | ER            | ER           | 08                 | *     | *        | * | *         | 0 | *     | 4      | 3 |

|                      |                                                            | ER            | IM           | 09                 | -     |          |   |           |   |       | 4      | 3 |

| Flags Notation:      | * = Value is a function<br>– = Unaffected<br>X = Undefined | of the result | of the o     | peration.          |       | Re<br>Se |   | to (<br>1 | ) |       |        |   |

Table 124. eZ8 CPU Instruction Summary

zilog <sub>217</sub>

| Abbreviation | Description                           | Abbreviation                                   | Description            |  |  |

|--------------|---------------------------------------|------------------------------------------------|------------------------|--|--|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |  |  |

| сс           | Condition code                        | р                                              | Polarity (0 or 1)      |  |  |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |  |  |

| DA           | Destination address                   | R                                              | 8-bit register         |  |  |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |  |  |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |  |  |

| Ir           | Indirect Working Register             | RA                                             | Relative               |  |  |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |  |  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |  |  |

#### Table 125. Opcode Map Abbreviations

<mark>z</mark>ilog<sup>°</sup>

### **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

#### Table 129. AC Characteristics

|                     |                              | T <sub>A</sub> = -40 °C<br>(unless o | V to 3.6 V<br>to +105 °C<br>otherwise<br>ted) |       |                                                                                                         |  |  |

|---------------------|------------------------------|--------------------------------------|-----------------------------------------------|-------|---------------------------------------------------------------------------------------------------------|--|--|

| Symbol              | Parameter                    | Minimum Maximum                      |                                               | Units | Conditions                                                                                              |  |  |

| F <sub>SYSCLK</sub> | System Clock Frequency       | _                                    | 20.0                                          | MHz   | Read-only from Flash memory                                                                             |  |  |

|                     |                              | 0.032768                             | 20.0                                          | MHz   | Program or erasure of the<br>Flash memory                                                               |  |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | -                                    | 20.0                                          | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an external<br>clock driver |  |  |

| T <sub>XIN</sub>    | System Clock Period          | 50                                   | _                                             | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                |  |  |

| T <sub>XINH</sub>   | System Clock High Time       | 20                                   | 30                                            | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |  |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                                   | 30                                            | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |  |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                    | 3                                             | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |  |

| T <sub>XINF</sub>   | System Clock Fall Time       | -                                    | 3                                             | ns    | T <sub>CLK</sub> = 50 ns                                                                                |  |  |

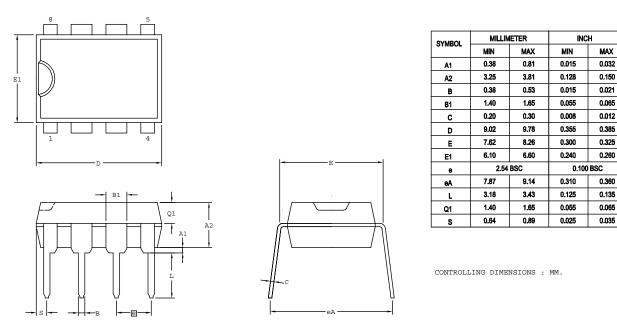

# Packaging

Figure 39 displays the 8-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore!  $XP^{\textcircled{R}}$  F082A Series devices.

Figure 39. 8-Pin Plastic Dual Inline Package (PDIP)

264

**DJNZ 206** EI 204 **HALT 204 INC 203 INCW 203 IRET 206** JP 206 LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204 LDX 205 LEA 205 logical 205 **MULT 203** NOP 204 OR 205 **ORX 206** POP 205 **POPX 205** program control 206 **PUSH 205** PUSHX 205 **RCF 204 RET 206** RL 206 **RLC 206** rotate and shift 206 RR 206 **RRC 206** SBC 203 SCF 204, 205 SRA 207 SRL 207 **SRP 205 STOP 205** SUB 203 SUBX 203 **SWAP 207** TCM 204 **TCMX 204** TM 204 TMX 204

**TRAP 206** Watchdog Timer refresh 205 XOR 206 **XORX 206** instructions, eZ8 classes of 202 interrupt control register 67 interrupt controller 55 architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 66 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 206 interrupt vector listing 55 interrupts **UART 105** IR 201 lr 201 IrDA architecture 117 block diagram 117 control register definitions 120 operation 117 receiving data 119 transmitting data 118 **IRET 206** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 63 IRQ2 enable high and low bit registers 65 **IRR 201** Irr 201

#### J

JP 206 jump, conditional, relative, and relative conditional 206

265

L LD 205 LDC 205 LDCI 204, 205 LDE 205 LDEI 204, 205 LDX 205 LEA 205 load 205 load constant 204 load constant to/from program memory 205 load constant with auto-increment addresses 205 load effective address 205 load external data 205 load external data to/from data memory and auto-increment addresses 204 load external to/from data memory and auto-increment addresses 205 load using extended addressing 205 logical AND 205 logical AND/extended addressing 205 logical exclusive OR 206 logical exclusive OR/extended addressing 206 logical instructions 205 logical OR 205 logical OR/extended addressing 206 low power modes 33

#### Μ

master interrupt enable 57 memory data 17 program 15 mode CAPTURE 85, 86 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 85 ONE-SHOT 84 PWM 85 modes 85 MULT 203 multiply 203 multiprocessor mode, UART 103

#### Ν

NOP (no operation) 204 notation b 201 cc 201 DA 201 ER 201 IM 201 IR 201 Ir 201 IRR 201 Irr 201 p 201 R 201 r 201 RA 201 RR 201 rr 201 vector 201 X 201 notational shorthand 201

#### O OCD

architecture 173 auto-baud detector/generator 176 baud rate limits 177 block diagram 173 breakpoints 178 commands 179 control register 184 data format 176 DBG pin to RS-232 Interface 174 debug mode 175 debugger break 206 interface 174 serial errors 177 status register 185