#### Zilog - Z8F082APB020SC Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                |                                                              |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                       |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082apb020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

viii

| Hardware Overflow         Automatic Powerdown         Single-Shot Conversion         Continuous Conversion         Interrupts         Calibration and Compensation         ADC Compensation Details         Input Buffer Stage         ADC Control Register Definitions         ADC Control Register 1         ADC Control/Status Register 1         ADC Data High Byte Register         ADC Data Low Byte Register | 123<br>124<br>125<br>125<br>127<br>129<br>130<br>130<br>132<br>132 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Low Power Operational Amplifier                                                                                                                                                                                                                                                                                                                                                                                     | 134                                                                |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                            | 134                                                                |

| Comparator                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| Temperature Sensor                                                                                                                                                                                                                                                                                                                                                                                                  | 139                                                                |

| Temperature Sensor Operation                                                                                                                                                                                                                                                                                                                                                                                        | 139                                                                |

| Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                        | 141                                                                |

| Architecture                                                                                                                                                                                                                                                                                                                                                                                                        | 141                                                                |

| Flash Information Area                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| Flash Operation Timing Using the Flash Frequency Registers                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| Flash Code Protection Against External Access                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

| 6 6                                                                                                                                                                                                                                                                                                                                                                                                                 | 147                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                     | 147                                                                |

| Mass Erase                                                                                                                                                                                                                                                                                                                                                                                                          | 147                                                                |

| Flash Controller Bypass                                                                                                                                                                                                                                                                                                                                                                                             | 148                                                                |

| Flash Controller Behavior in DEBUG Mode                                                                                                                                                                                                                                                                                                                                                                             | 148                                                                |

| Flash Control Register Definitions                                                                                                                                                                                                                                                                                                                                                                                  | 149                                                                |

| Flash Control Register                                                                                                                                                                                                                                                                                                                                                                                              | 149                                                                |

| Flash Status Register                                                                                                                                                                                                                                                                                                                                                                                               | 150                                                                |

| Flash Page Select Register                                                                                                                                                                                                                                                                                                                                                                                          | 150                                                                |

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See Interrupt Controller on page 55 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 16 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register Mnemonic     | Port Register Name                                              |

|----------------------------|-----------------------------------------------------------------|

| PxADDR                     | Port A–D Address Register<br>(Selects sub-registers)            |

| PxCTL                      | Port A–D Control Register<br>(Provides access to sub-registers) |

| PxIN                       | Port A–D Input Data Register                                    |

| PxOUT                      | Port A–D Output Data Register                                   |

| Port Sub-Register Mnemonic | Port Register Name                                              |

| PxDD                       | Data Direction                                                  |

| PxAF                       | Alternate Function                                              |

| PxOC                       | Output Control (Open-Drain)                                     |

| PxHDE                      | High Drive Enable                                               |

| PxSMRE                     | Stop Mode Recovery Source Enable                                |

| PxPUE                      | Pull-up Enable                                                  |

| PxAFS1                     | Alternate Function Set 1                                        |

| PxAFS2                     | Alternate Function Set 2                                        |

|                            |                                                                 |

| Table 16. | <b>GPIO Por</b> | t Registers | and Sub-Registers |

|-----------|-----------------|-------------|-------------------|

|-----------|-----------------|-------------|-------------------|

## Table 18. Port A–D Control Registers (PxCTL)

| BITS  | 7   | 6                      | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|------------------------|-----|-----|-----|-----|-----|-----|

| FIELD |     | PCTL                   |     |     |     |     |     |     |

| RESET |     | 00H                    |     |     |     |     |     |     |

| R/W   | R/W | R/W                    | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     | FD1H, FD5H, FD9H, FDDH |     |     |     |     |     |     |

PCTL[7:0]—Port Control

The Port Control register provides access to all sub-registers that configure the GPIO Port operation.

# Port A–D Data Direction Sub-Registers

The Port A–D Data Direction sub-register is accessed through the Port A–D Control register by writing 01H to the Port A–D Address register (Table 19).

| BITS  | 7        | 6            | 5           | 4             | 3            | 2             | 1            | 0        |

|-------|----------|--------------|-------------|---------------|--------------|---------------|--------------|----------|

| FIELD | DD7      | DD6          | DD5         | DD4           | DD3          | DD2           | DD1          | DD0      |

| RESET | 1        | 1            | 1           | 1             | 1            | 1             | 1            | 1        |

| R/W   | R/W      | R/W          | R/W         | R/W           | R/W          | R/W           | R/W          | R/W      |

| ADDR  | lf 01H i | n Port A–D / | Address Reg | gister, acces | sible throug | n the Port A- | -D Control F | Register |

## Table 19. Port A–D Data Direction Sub-Registers (PxDD)

## DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 = Output. Data in the Port A–D Output Data register is driven onto the port pin.

1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register. The output driver is tristated.

# Port A–D Alternate Function Sub-Registers

The Port A–D Alternate Function sub-register (Table 20) is accessed through the Port A–D Control register by writing 02H to the Port A–D Address register. The Port A–D Alternate Function sub-registers enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the Port A–D Alternate Function

Follow the steps below for configuring a timer for COMPARATOR COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER mode. After the first timer Reload in COMPARATOR COUNTER mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer.

In COMPARATOR COUNTER mode, the number of comparator output transitions since the timer start is given by the following equation:

Comparator Output Transitions = Current Count Value – Start Value

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO Port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for CAPTURE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE mode.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to

zilog',

0001H and counting resumes. The INPCAP bit in TxCTL0 register is cleared to indicate the timer interrupt is not caused by an input capture event.

Follow the steps below for configuring a timer for CAPTURE RESTART mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE RESTART mode by writing the TMODE bits in the TxCTL1 register and the TMODEHI bit in TxCTL0 register.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **COMPARE Mode**

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

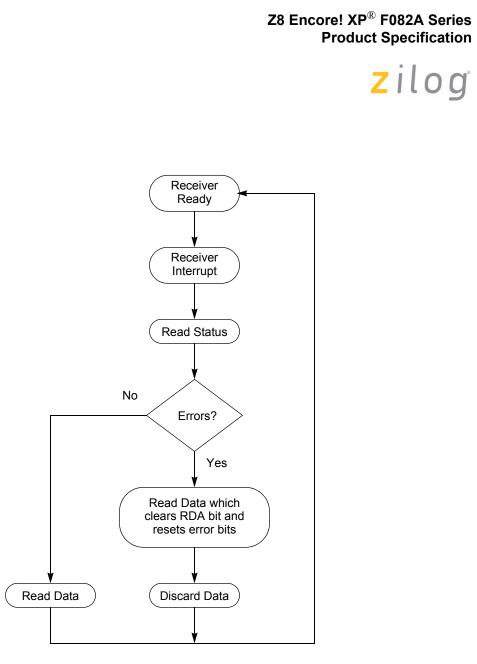

Figure 15. UART Receiver Interrupt Service Routine Flow

## **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is Low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled.

1 = Transmitter enabled.

REN—Receive Enable

This bit enables or disables the receiver.

0 = Receiver disabled.

1 =Receiver enabled.

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter.

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter.

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled.

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit.

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data.

1 = Odd parity is transmitted and expected on all received data.

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit. 0 = No break is sent.

0 = No break is sent.

1 = Forces a break condition by setting the output of the transmitter to zero.

STOP—Stop Bit Select

0 = The transmitter sends one stop bit.

1 = The transmitter sends two stop bits.

LBEN—Loop Back Enable

0 = Normal operation.

1 = All transmitted data is looped back to the receiver.

### Table 62. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |

|-------|---------|------|---------|------|-------|--------|--------|------|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |

| RESET | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |

| ADDR  |         |      |         | F4   | 3H    |        |        |      |

# zilog | 11

## **UART Address Compare Register**

The UART Address Compare (UxADDR) register stores the multi-node network address of the UART (see Table 67). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

#### Table 67. UART Address Compare Register (U0ADDR)

| BITS  | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----------|-----|-----|-----|-----|-----|-----|

| FIELD |     | COMP_ADDR |     |     |     |     |     |     |

| RESET | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     | F45H      |     |     |     |     |     |     |

COMP\_ADDR—Compare Address

This 8-bit value is compared to incoming address bytes.

## UART Baud Rate High and Low Byte Registers

The UART Baud Rate High (UxBRH) and Low Byte (UxBRL) registers (Table 68 and Table 69) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

### Table 68. UART Baud Rate High Byte Register (U0BRH)

| BITS  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| FIELD |     | BRH |     |     |     |     |     |     |

| RESET | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     |     |     | F4  | 6H  |     |     |     |

#### Table 69. UART Baud Rate Low Byte Register (U0BRL)

| BITS  | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|------|-----|-----|-----|-----|-----|-----|

| FIELD |     | BRL  |     |     |     |     |     |     |

| RESET | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     | F47H |     |     |     |     |     |     |

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register may be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1.

- Set CEN to 1 to start the conversions.

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete.

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD L[7:3]}.

- Sends an interrupt request to the Interrupt Controller denoting conversion complete.

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

### Interrupts

The ADC is able to interrupt the CPU when a conversion has been completed. When the ADC is disabled, no new interrupts are asserted; however, an interrupt pending when the ADC is disabled is not cleared.

## **Calibration and Compensation**

The Z8 Encore! XP<sup>®</sup> F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, you can perform your own calibration, storing the values into Flash themselves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL mode operation.

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The Flow Chart in Figure 22 displays basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select, Page Erase, and Mass Erase) displayed in Figure 22.

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

## Table 102. Randomized Lot ID Locations (Continued)

# zilog

#### 199

# eZ8 CPU Instruction Set

# **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                          |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4. |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data                                    |

|               | ; value 01H, is the source. The value 01H is written into the ; Register at address 234H.                                                                                                                              |

zilog

| ) g | 213 |

|-----|-----|

|     |     |

| Assembly                   | Symbolic<br>Operation                                           | Address Mode |          | Opcode(s) | Flags |          |   |           |   |   | Fetch  | Instr. |

|----------------------------|-----------------------------------------------------------------|--------------|----------|-----------|-------|----------|---|-----------|---|---|--------|--------|

| Mnemonic                   |                                                                 | dst          | src      | (Hex)     | С     | Ζ        | S | V         | D | Н | Cycles |        |

| RR dst                     |                                                                 | R            |          | E0        | *     | *        | * | *         | _ | _ | 2      | 2      |

| ► D7 D6 D5 D4 D3 D2<br>dst |                                                                 | IR           |          | E1        |       |          |   |           |   |   | 2      | 3      |

|                            |                                                                 |              |          |           |       |          |   |           |   |   |        |        |

| RRC dst                    |                                                                 | R            |          | C0        | *     | *        | * | *         | - | - | 2      | 2      |

|                            | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                            | IR           |          | C1        |       |          |   |           |   |   | 2      | 3      |

| SBC dst, src               | $dst \gets dst - src - C$                                       | r            | r        | 32        | *     | *        | * | *         | 1 | * | 2      | 3      |

|                            |                                                                 | r            | lr       | 33        |       |          |   |           |   |   | 2      | 4      |

|                            |                                                                 | R            | R        | 34        |       |          |   |           |   |   | 3      | 3      |

|                            |                                                                 | R            | IR       | 35        | •     |          |   |           |   |   | 3      | 4      |

|                            |                                                                 | R            | IM       | 36        | •     |          |   |           |   |   | 3      | 3      |

|                            |                                                                 | IR           | IM       | 37        | •     |          |   |           |   |   | 3      | 4      |

| SBCX dst, src              | $dst \gets dst - src - C$                                       | ER           | ER       | 38        | *     | *        | * | *         | 1 | * | 4      | 3      |

|                            |                                                                 | ER           | IM       | 39        | •     |          |   |           |   |   | 4      | 3      |

| SCF                        | C ← 1                                                           |              |          | DF        | 1     | -        | _ | _         | _ | _ | 1      | 2      |

| SRA dst                    |                                                                 | R            |          | D0        | *     | *        | * | 0         | - | _ | 2      | 2      |

|                            | D7D6D5D4D3D2D1D0 C                                              | IR           |          | D1        |       |          |   |           |   |   | 2      | 3      |

| SRL dst 0                  | 0 - <b>▶</b> D7D6D5D4D3D2D1D0- <b>▶</b> C                       | R            |          | 1F C0     | *     | *        | 0 | *         | _ | _ | 3      | 2      |

|                            | dst                                                             | IR           |          | 1F C1     | -     |          |   |           |   |   | 3      | 3      |

| SRP src                    | $RP \gets src$                                                  |              | IM       | 01        | _     | _        | _ | -         | _ | _ | 2      | 2      |

| STOP                       | STOP Mode                                                       |              |          | 6F        | _     | _        | _ | _         | _ | _ | 1      | 2      |

| SUB dst, src               | $dst \gets dst - src$                                           | r            | r        | 22        | *     | *        | * | *         | 1 | * | 2      | 3      |

|                            |                                                                 | r            | lr       | 23        | •     |          |   |           |   |   | 2      | 4      |

|                            |                                                                 | R            | R        | 24        | •     |          |   |           |   |   | 3      | 3      |

|                            |                                                                 | R            | IR       | 25        |       |          |   |           |   |   | 3      | 4      |

|                            |                                                                 | R            | IM       | 26        | •     |          |   |           |   |   | 3      | 3      |

|                            |                                                                 | IR           | IM       | 27        |       |          |   |           |   |   | 3      | 4      |

| Flags Notation:            | * = Value is a function of t<br>– = Unaffected<br>X = Undefined | he result    | of the o | peration. |       | Re<br>Se |   | to (<br>1 | ) |   |        |        |

## Table 124. eZ8 CPU Instruction Summary (Continued)

zilog 226

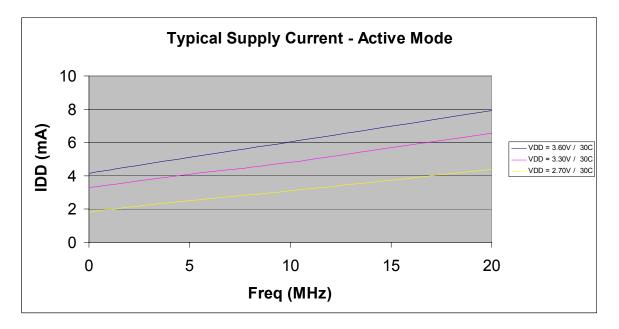

Figure 33 displays the typical current consumption while operating with all peripherals disabled, at 30 °C, versus the system clock frequency.

Figure 33. Typical Active Mode I<sub>DD</sub> Versus System Clock Frequency

zilog <sub>238</sub>

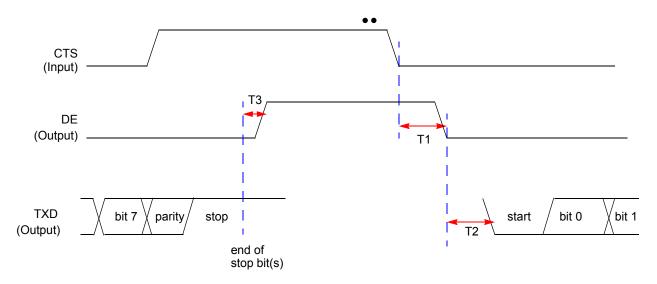

## **UART** Timing

Figure 37 and Table 142 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

|                |                                                    | Delay (ns)        |                                |  |  |  |  |

|----------------|----------------------------------------------------|-------------------|--------------------------------|--|--|--|--|

| Parameter      | Abbreviation                                       | Minimum           | Maximum                        |  |  |  |  |

| UART           |                                                    |                   |                                |  |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * XIN<br>period | 2 * XIN period<br>+ 1 bit time |  |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | / ± 5             |                                |  |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ± 5               |                                |  |  |  |  |

#### Table 142. UART Timing With CTS

zilog

245

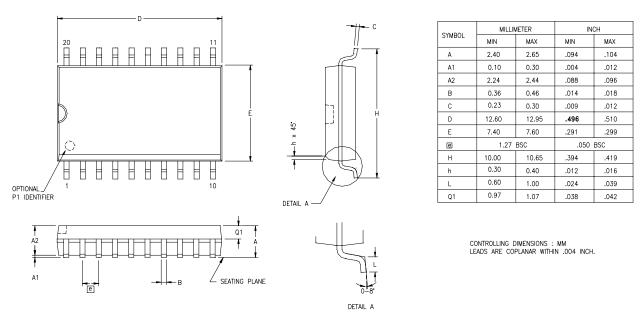

Figure 43 displays the 20-pin Small Outline Integrated Circuit Package (SOIC) available for the Z8 Encore! XP F082A Series devices.

Figure 43. 20-Pin Small Outline Integrated Circuit Package (SOIC)

263

page erase 147 page select register 150, 151 FPS register 150, 151 FSTAT register 150

# G

GATED mode 85 general-purpose I/O 37 GPIO 7, 37 alternate functions 38 architecture 38 control register definitions 45 input data sample timing 234 interrupts 45 port A-C pull-up enable sub-registers 50, 51 port A-H address registers 46 port A-H alternate function sub-registers 47 port A-H control registers 46 port A-H data direction sub-registers 47 port A-H high drive enable sub-registers 49 port A-H input data registers 51 port A-H output control sub-registers 48 port A-H output data registers 52 port A-H stop mode recovery sub-registers 49 port availability by device 37 port input timing 235 port output timing 236

# Η

H 202 HALT 204 halt mode 34, 204 hexadecimal number prefix/suffix 202

# I

I2C 7 IM 201 immediate data 201 immediate operand prefix 202 **INC 203** increment 203 increment word 203 **INCW 203** indexed 201 indirect address prefix 202 indirect register 201 indirect register pair 201 indirect working register 201 indirect working register pair 201 infrared encoder/decoder (IrDA) 117 Instruction Set 199 instruction set. eZ8 CPU 199 instructions ADC 203 ADCX 203 ADD 203 **ADDX 203** AND 205 **ANDX 205** arithmetic 203 **BCLR 204** BIT 204 bit manipulation 204 block transfer 204 **BRK 206 BSET 204** BSWAP 204, 206 **BTJ 206 BTJNZ 206 BTJZ 206 CALL 206** CCF 204 CLR 205 COM 205 CP 203 CPC 203 **CPCX 203** CPU control 204 **CPX 203** DA 203 **DEC 203 DECW 203**

DI 204