Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 1K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Through Hole                                                 |

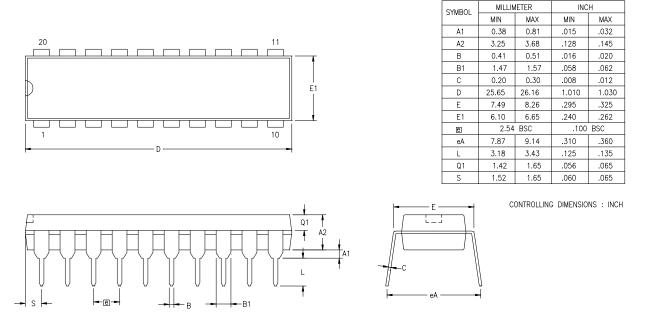

| Package / Case             | 28-DIP (0.600", 15.24mm)                                     |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f082apj020sc    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to thirteen 5 V-tolerant input pins

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brownout (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO, and LVD

- Power-On Reset (POR)

- 2.7 V to 3.6 V operating voltage

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

# **Part Selection Guide**

Table 1 on page 3 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F082A Series product line.

### **Interrupt Controller**

The Z8 Encore! XP<sup>®</sup> F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

#### **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the  $\overline{\text{RESET}}$  pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP mode exit, or Voltage Brownout (VBO) warning signal. The  $\overline{\text{RESET}}$  pin is bi-directional, that is, it functions as reset source as well as a reset indicator.

# **Low-Power Modes**

The Z8 Encore! XP F082A Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in Active mode (defined as being in neither STOP nor HALT mode).

# **STOP Mode**

Executing the eZ8 CPU's STOP instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, the Low-power Operational Amplifier and the Watchdog Timer. These three blocks may also be disabled for additional power savings. Specifically, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- Low-power operational amplifier continues to operate if enabled by the Power Control register to do so.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset, Stop Mode Recovery, and Low Voltage Detection on page 23.

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low).

1 = Input data is logical 1 (High).

### Port A–D Output Data Register

The Port A–D Output Data register (Table 28) controls the output data to the pins.

| BITS  | 7     | 6     | 5     | 4          | 3         | 2     | 1     | 0     |

|-------|-------|-------|-------|------------|-----------|-------|-------|-------|

| FIELD | POUT7 | POUT6 | POUT5 | POUT4      | POUT3     | POUT2 | POUT1 | POUT0 |

| RESET | 0     | 0     | 0     | 0          | 0         | 0     | 0     | 0     |

| R/W   | R/W   | R/W   | R/W   | R/W        | R/W       | R/W   | R/W   | R/W   |

| ADDR  |       |       | FI    | D3H, FD7H, | FDBH, FDF | Ή     |       |       |

#### Table 28. Port A–D Output Data Register (PxOUT)

POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 = Drive a logical 0 (Low).

1= Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

# LED Drive Enable Register

The LED Drive Enable register (Table 29) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

| BITS  | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | LEDEN[7:0] |     |     |     |     |     |     |     |

| RESET | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |            |     |     | F8  | 2H  |     |     |     |

#### Table 29. LED Drive Enable (LEDEN)

Interrupts are globally enabled by any of the following actions:

- Execution of an EI (Enable Interrupt) instruction

- Execution of an IRET (Return from Interrupt) instruction

- Writing a 1 to the IRQE bit in the Interrupt Control register

Interrupts are globally disabled by any of the following actions:

- Execution of a DI (Disable Interrupt) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Oscillator Fail Trap

#### **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as Level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in Table 32 on page 56. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 32, above. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Oscillator Fail Trap, and Illegal Instruction Trap always have highest (level 3) priority.

#### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Pin Signal Operation**

Timer Output is a GPIO Port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The Timer Input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

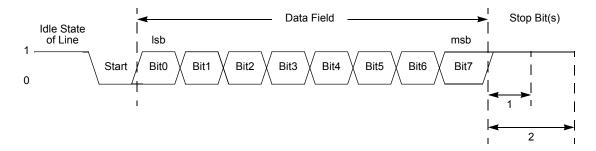

Figure 11. UART Asynchronous Data Format without Parity

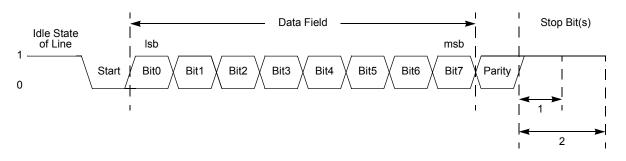

Figure 12. UART Asynchronous Data Format with Parity

#### Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO Port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

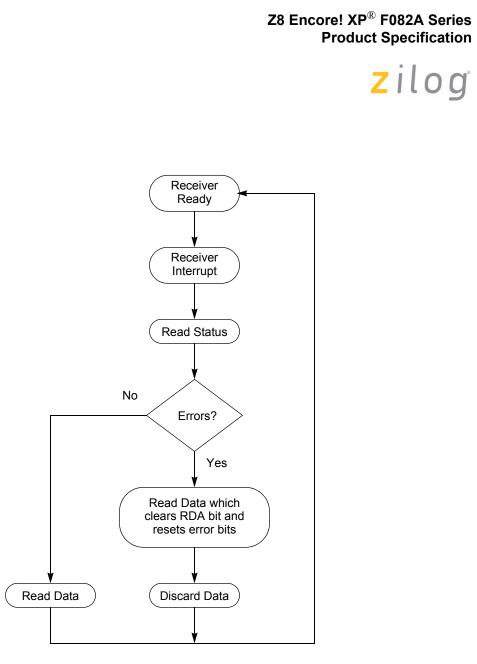

Figure 15. UART Receiver Interrupt Service Routine Flow

#### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

# **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

107

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 =Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

#### **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers (Table 63 and Table 64) identify the current UART operating configuration and status.

Table 63. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6  | 5  | 4  | 3    | 2    | 1   | 0   |

|-------|-----|----|----|----|------|------|-----|-----|

| FIELD | RDA | PE | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET | 0   | 0  | 0  | 0  | 0    | 1    | 1   | Х   |

| R/W   | R   | R  | R  | R  | R    | R    | R   | R   |

| ADDR  |     |    |    | F4 | 1H   |      |     |     |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty.

1 = There is a byte in the UART Receive Data register.

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred.

1 = A parity error has occurred.

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data register clears this bit.

- 0 = No overrun error occurred.

- 1 = An overrun error occurred.

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

Compensation Steps:

1. Correct for Offset

#3

| ADC MSB     | ADC LSB    |

|-------------|------------|

| -           |            |

| Offset MSB  | Offset LSB |

| Oliset widd | Oliser LOD |

| =           |            |

| #1 MSB      | #1 LSB     |

2. Take absolute value of the offset corrected ADC value *if negative*—the gain correction factor is computed assuming positive numbers, with sign restoration afterward.

| #2 MSB #2 LS |

|--------------|

|--------------|

Also take absolute value of the gain correction word *if negative*.

| AGain MSB | AGain LSB |

|-----------|-----------|

|-----------|-----------|

3. Multiply by Gain Correction Word. If in DIFFERENTIAL mode, there are two gain correction values: one for positive ADC values, another for negative ADC values. Based on the sign of #2, use the appropriate Gain Correction Word.

|   | #2 MSB    | #2 LSB    |

|---|-----------|-----------|

| * |           |           |

| Γ | AGain MSB | AGain LSB |

|   |           |           |

| = |           |           |

#3

4. Round the result and discard the least significant two bytes (this is equivalent to dividing by  $2^{16}$ ).

#3

| #3   | #3   | #3   | #3   |

|------|------|------|------|

| -    |      |      |      |

| 0x00 | 0x00 | 0x80 | 0x00 |

| =    |      |      |      |

|      |      | 7    |      |

|--|

5. Determine sign of the gain correction factor using the sign bits from Step 2. If the offset corrected ADC value AND the gain correction word have the same sign, then the factor is positive and is left unchanged. If they have differing signs, then the factor is negative and must be multiplied by -1.

#3

zilog

value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

#### **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore!<sup>®</sup> MCU Application Note (AN0117) available for download at <u>www.zilog.com</u>.

#### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select register.

- Bits in the Flash Sector Protect register can be written to one or zero.

- The second write of the Page Select register to unlock the Flash Controller is not necessary.

- The Page Select register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control register.

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/erase. When writing multiple Flash pages, the flash controller must go through the unlock sequence again to select another page.

zilog

163

| Info Page<br>Address | Memory<br>Address | Compensation Usage      | ADC Mode                 | Reference<br>Type |

|----------------------|-------------------|-------------------------|--------------------------|-------------------|

| 34                   | FE34              | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V    |

| 35                   | FE35              | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V    |

| 78                   | FE78              | Offset                  | Differential 1x Buffered | Internal 2.0 V    |

| 18                   | FE18              | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 19                   | FE19              | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 36                   | FE36              | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V    |

| 37                   | FE37              | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V    |

| 7B                   | FE7B              | Offset                  | Differential 1x Buffered | External 2.0 V    |

| 1A                   | FE1A              | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 1B                   | FE1B              | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

| 38                   | FE38              | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V    |

| 39                   | FE39              | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V    |

#### Table 94. ADC Calibration Data Location (Continued)

zilog | 17

read operations to illegal addresses. Also, the user code must pop the address byte off the stack.

The read routine uses 9 bytes of stack space in addition to the one byte of address pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a non-uniform execution time. A read operation takes between 44  $\mu$ s and 489  $\mu$ s (assuming a 20 MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a 2  $\mu$ s execution time.

The status byte returned by the NVDS read routine is zero for successful read, as determined by a CRC check. If the status byte is non-zero, there was a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have a CRC error.

#### **Power Failure Protection**

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. Bytes previously written to the array are not perturbed.

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

#### Optimizing NVDS Memory Usage for Execution Speed

The NVDS read time varies drastically, this discrepancy being a trade-off for minimizing the frequency of writes that require post-write page erases (see Table 104). The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, as well as the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by 1  $\mu$ s, up to a maximum of (511-NVDS SIZE)  $\mu$ s.

| Operation            | Minimum<br>Latency | Maximum<br>Latency |

|----------------------|--------------------|--------------------|

| Read (16 byte array) | 875                | 9961               |

| Read (64 byte array) | 876                | 8952               |

#### Table 104. NVDS Read Time

# zilog <sub>172</sub>

#### Table 104. NVDS Read Time (Continued)

| Operation              | Minimum<br>Latency | Maximum<br>Latency |

|------------------------|--------------------|--------------------|

| Read (128 byte array)  | 883                | 7609               |

| Write (16 byte array)  | 4973               | 5009               |

| Write (64 byte array)  | 4971               | 5013               |

| Write (128 byte array) | 4984               | 5023               |

| Illegal Read           | 43                 | 43                 |

| Illegal Write          | 31                 | 31                 |

If NVDS read performance is critical to your software architecture, there are some things you can do to optimize your code for speed, listed in order from most helpful to least helpful:

- Periodically refresh all addresses that are used. The optimal use of NVDS in terms of speed is to rotate the writes evenly among all addresses planned to use, bringing all reads closer to the minimum read time. Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

- Use as few unique addresses as possible: this helps to optimize the impact of refreshing as well as minimize the requirement for it.

# **Oscillator Control**

The Z8 Encore!  $XP^{\mathbb{R}}$  F082A Series devices uses five possible clocking schemes, each user-selectable:

- Internal precision trimmed RC oscillator (IPO).

- On-chip oscillator using off-chip crystal or resonator.

- On-chip oscillator using external RC network.

- External clock drive.

- On-chip low power Watchdog Timer oscillator.

- Clock failure detection circuitry.

In addition, Z8 Encore! XP F082A Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the system clock oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures.

#### **System Clock Selection**

The oscillator control block selects from the available clocks. Table 108 details each clock source and its usage.

zilog

189

When selecting a new clock source, the system clock oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If SOFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the OSCCTL register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

#### **Clock Failure Detection and Recovery**

#### System Clock Oscillator Failure

The Z8F04xA family devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function (see Watchdog Timer on page 91).

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (SOFEN must be deasserted in the OSCCTL register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the system clock oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

Zilog 244

Figure 42 displays the 20-pin Plastic Dual Inline Package (PDIP) available for the Z8 Encore! XP F082A Series devices.

Figure 42. 20-Pin Plastic Dual Inline Package (PDIP)

266

timing 237 OCD commands execute instruction (12H) 183 read data memory (0DH) 183 read OCD control register (05H) 181 read OCD revision (00H) 180 read OCD status register (02H) 180 read program counter (07H) 181 read program memory (0BH) 182 read program memory CRC (0EH) 183 read register (09H) 182 read runtime counter (03H) 180 step instruction (10H) 183 stuff instruction (11H) 183 write data memory (0CH) 182 write OCD control register (04H) 181 write program counter (06H) 181 write program memory (0AH) 182 write register (08H) 181 on-chip debugger (OCD) 173 on-chip debugger signals 12 on-chip oscillator 193 **ONE-SHOT** mode 84 opcode map abbreviations 217 cell description 216 first 218 second after 1FH 219 Operational Description 23, 33, 37, 55, 69, 91, 97, 117, 121, 134, 135, 139, 141, 153, 169, 173, 187, 193, 197 OR 205 ordering information 251 **ORX 206** oscillator signals 12

#### Ρ

p 201 packaging 20-pin PDIP 244, 245 20-pin SSOP 246, 249 28-pin PDIP 247 28-pin SOIC 248

8-pin PDIP 241 8-pin SOIC 242 PDIP 248, 249 part selection guide 2 PC 202 PDIP 248, 249 peripheral AC and DC electrical characteristics 229 pin characteristics 13 **Pin Descriptions 9** polarity 201 POP 205 pop using extended addressing 205 **POPX 205** port availability, device 37 port input timing (GPIO) 235 port output timing, GPIO 236 power supply signals 13 power-down, automatic (ADC) 122 Power-on and Voltage Brownout electrical characteristics and timing 229 Power-On Reset (POR) 25 program control instructions 206 program counter 202 program memory 15 **PUSH 205** push using extended addressing 205 PUSHX 205 PWM mode 85 PxADDR register 46 PxCTL register 47

#### R

R 201 r 201 RA register address 201 RCF 204 receive IrDA data 119 receiving UART data-interrupt-driven method 102 receiving UART data-polled method 101

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <a href="http://www.zilog.com/kb">http://www.zilog.com/kb</a>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.