Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | LVD, PWM, WDT                                                         |

| Number of I/O              | 58                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x6b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mke04z128vlh4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Ordering parts

## 1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to **nxp.com** and perform a part number search for the following device numbers: KE06Z.

#### 2 Part identification

## 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

#### 2.2 Format

Part numbers for this device have the following format:

Q KE## A FFF R T PP CC N

#### 2.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description               | Values                                                                                     |

|-------|---------------------------|--------------------------------------------------------------------------------------------|

| Q     | Qualification status      | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul> |

| KE##  | Kinetis family            | • KE04                                                                                     |

| А     | Key attribute             | • Z = M0+ core                                                                             |

| FFF   | Program flash memory size | • 128 = 128 KB                                                                             |

| R     | Silicon revision          | (Blank) = Main     A = Revision after main                                                 |

| Т     | Temperature range (°C)    | • V = -40 to 105                                                                           |

| PP    | Package identifier        | • LD = 44 LQFP (10 mm x 10 mm)                                                             |

Table continues on the next page...

## 4 Ratings

## 4.1 Thermal handling ratings

| Symbol           | Description                   | Min.        | Max. | Unit | Notes |

|------------------|-------------------------------|-------------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | <b>-</b> 55 | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _           | 260  | °C   | 2     |

- 1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

- Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

## 4.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level |      | 3    | _    | 1     |

Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

## 4.3 ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | -6000 | +6000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 125°C      | -100  | +100  | mA   | 3     |

- Determined according to JEDEC Standard JESD22-A114, Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM).

- 2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

- 3. Determined according to JEDEC Standard JESD78D, IC Latch-up Test.

- Test was performed at 125 °C case temperature (Class II).

- I/O pins pass ±100 mA I-test with I<sub>DD</sub> current limit at 400 mA.

- I/O pins pass +50/-100 mA I-test with I<sub>DD</sub> current limit at 1000 mA.

- Supply groups pass 1.5 V<sub>ccmax</sub>.

- RESET pin was only tested with negative I-test due to product conditioning requirement.

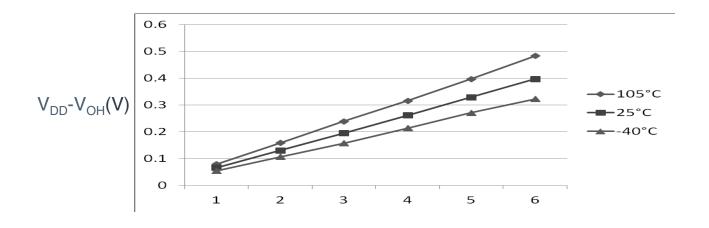

$I_{OH}(mA)$

Figure 1. Typical  $V_{DD}$ - $V_{OH}$  Vs.  $I_{OH}$  (standard drive strength) ( $V_{DD}$  = 5 V)

$I_{OH}(mA)$

Figure 2. Typical  $V_{DD}$ - $V_{OH}$  Vs.  $I_{OH}$  (standard drive strength) ( $V_{DD}$  = 3 V)

## 5.1.2 Supply current characteristics

This section includes information about power supply current in various operating modes.

Table 5. Supply current characteristics

| С | Parameter                                           | Symbol           | Core/Bus<br>Freq | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Max <sup>2</sup> | Unit | Temp          |

|---|-----------------------------------------------------|------------------|------------------|---------------------|----------------------|------------------|------|---------------|

| С | Run supply current FEI                              | RI <sub>DD</sub> | 48/24 MHz        | 5                   | 11.1                 | _                | mA   | -40 to 105 °C |

| С | mode, all modules clocks<br>enabled; run from flash |                  | 24/24 MHz        |                     | 8                    | _                |      |               |

| С | enabled, full from flash                            |                  | 12/12 MHz        |                     | 5                    | _                |      |               |

| С |                                                     |                  | 1/1 MHz          |                     | 2.4                  |                  |      |               |

| С |                                                     |                  | 48/24 MHz        | 3                   | 11                   | _                |      |               |

| С |                                                     |                  | 24/24 MHz        |                     | 7.9                  |                  |      |               |

| С |                                                     |                  | 12/12 MHz        |                     | 4.9                  |                  |      |               |

|   |                                                     |                  | 1/1 MHz          |                     | 2.3                  | _                |      |               |

| С | Run supply current FEI                              | RI <sub>DD</sub> | 48/24 MHz        | 5                   | 7.8                  | _                | mA   | -40 to 105 °C |

| С | mode, all modules clocks disabled and gated; run    |                  | 24/24 MHz        |                     | 5.5                  | _                |      |               |

| С | from flash                                          |                  | 12/12 MHz        |                     | 3.8                  | _                |      |               |

| С |                                                     |                  | 1/1 MHz          |                     | 2.3                  |                  |      |               |

| С |                                                     |                  | 48/24 MHz        | 3                   | 7.7                  | _                |      |               |

| С |                                                     |                  | 24/24 MHz        |                     | 5.4                  | _                |      |               |

| С |                                                     |                  | 12/12 MHz        |                     | 3.7                  | _                |      |               |

| С |                                                     |                  | 1/1 MHz          |                     | 2.2                  | _                |      |               |

| С | Run supply current FBE                              | $RI_{DD}$        | 48/24 MHz        | 5                   | 14.7                 |                  | mA   | -40 to 105 °C |

| Р | mode, all modules clocks<br>enabled; run from RAM   |                  | 24/24 MHz        |                     | 9.8                  | 14.9             |      |               |

| С |                                                     |                  | 12/12 MHz        |                     | 6                    |                  |      |               |

| С |                                                     |                  | 1/1 MHz          |                     | 2.4                  |                  |      |               |

| С |                                                     |                  | 48/24 MHz        | 3                   | 14.6                 |                  |      |               |

| Р |                                                     |                  | 24/24 MHz        |                     | 9.6                  | 12.8             |      |               |

| С |                                                     |                  | 12/12 MHz        |                     | 5.9                  |                  |      |               |

| С |                                                     |                  | 1/1 MHz          |                     | 2.3                  |                  |      |               |

| С | Run supply current FBE                              | RI <sub>DD</sub> | 48/24 MHz        | 5                   | 11.4                 | _                | mA   | -40 to 105 °C |

| Р | mode, all modules clocks<br>disabled and gated; run |                  | 24/24 MHz        |                     | 7.7                  | 12.5             |      |               |

| С | from RAM                                            |                  | 12/12 MHz        |                     | 4.7                  |                  |      |               |

| С |                                                     |                  | 1/1 MHz          |                     | 2.3                  |                  |      |               |

| С |                                                     |                  | 48/24 MHz        | 3                   | 11.3                 | _                |      |               |

| Р |                                                     |                  | 24/24 MHz        |                     | 7.6                  | 9.5              |      |               |

| С |                                                     |                  | 12/12 MHz        |                     | 4.6                  | 1                |      |               |

|   |                                                     |                  | 1/1 MHz          |                     | 2.2                  | _                |      |               |

Table continues on the next page...

| Table 5. | Supply current | t characteristics | (continued) |

|----------|----------------|-------------------|-------------|

|----------|----------------|-------------------|-------------|

| С | Parameter                                              | Symbol           | Core/Bus<br>Freq | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Max <sup>2</sup> | Unit | Temp          |

|---|--------------------------------------------------------|------------------|------------------|---------------------|----------------------|------------------|------|---------------|

| С | Wait mode current FEI                                  | WI <sub>DD</sub> | 48/24 MHz        | 5                   | 8.4                  | _                | mA   | -40 to 105 °C |

| Р | mode, all modules clocks<br>enabled                    |                  | 24/24 MHz        |                     | 6.5                  | 7.2              |      |               |

| С | enabled                                                |                  | 12/12 MHz        |                     | 4.3                  | _                |      |               |

| С |                                                        |                  | 1/1 MHz          |                     | 2.4                  | _                |      |               |

| С |                                                        |                  | 48/24 MHz        | 3                   | 8.3                  | _                |      |               |

| Р |                                                        |                  | 24/24 MHz        |                     | 6.4                  | 7                |      |               |

| С |                                                        |                  | 12/12 MHz        |                     | 4.2                  | _                |      |               |

| С |                                                        |                  | 1/1 MHz          |                     | 2.3                  | _                |      |               |

| Р | Stop mode supply current                               | SI <sub>DD</sub> | _                | 5                   | 2                    | 105              | μA   | -40 to 105 °C |

| Р | no clocks active (except 1 kHz LPO clock) <sup>3</sup> |                  | _                | 3                   | 1.9                  | 95               |      | -40 to 105 °C |

| С | ADC adder to Stop                                      | _                | _                | 5                   | 86                   | _                | μA   | -40 to 105 °C |

| С | ADLPC = 1                                              |                  |                  | 3                   | 82                   | _                |      |               |

|   | ADLSMP = 1                                             |                  |                  |                     |                      |                  |      |               |

|   | ADCO = 1                                               |                  |                  |                     |                      |                  |      |               |

|   | MODE = 10B                                             |                  |                  |                     |                      |                  |      |               |

|   | ADICLK = 11B                                           |                  |                  |                     |                      |                  |      |               |

| С | ACMP adder to Stop                                     | _                | _                | 5                   | 12                   | _                | μΑ   | -40 to 105 °C |

| С |                                                        |                  |                  | 3                   | 12                   | _                |      |               |

| С | LVD adder to Stop <sup>4</sup>                         | _                | _                | 5                   | 130                  | _                | μA   | -40 to 105 °C |

| С |                                                        |                  |                  | 3                   | 125                  | _                |      |               |

- 1. Data in Typical column was characterized at 5.0 V, 25 °C or is typical recommended value.

- 2. The Max current is observed at high temperature of 105 °C.

- 3. RTC adder cause <1 µA I<sub>DD</sub> increase typically, RTC clock source is 1 kHz LPO clock.

- 4. LVD is periodically woken up from Stop by 5% duty cycle. The period is equal to or less than 2 ms.

### 5.1.3 EMC performance

Electromagnetic compatibility (EMC) performance is highly dependent on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation play a significant role in EMC performance. The system designer must consult the following applications notes, available on nxp.com for advice and guidance specifically targeted at optimizing EMC performance.

- AN2321: Designing for Board Level Electromagnetic Compatibility

- AN1050: Designing for Electromagnetic Compatibility (EMC) with HCMOS Microcontrollers

- AN1263: Designing for Electromagnetic Compatibility with Single-Chip Microcontrollers

KE04 Sub-Family Data Sheet, Rev. 4, 07/2016

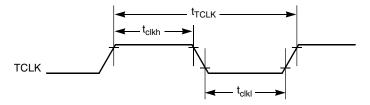

Table 8. FTM input timing (continued)

| С | Function                  | Symbol            | Min | Max | Unit                   |

|---|---------------------------|-------------------|-----|-----|------------------------|

| D | External clock period     | t <sub>TCLK</sub> | 4   | _   | t <sub>Timer</sub> , 1 |

| D | External clock high time  | t <sub>clkh</sub> | 1.5 | _   | t <sub>Timer</sub> 1   |

| D | External clock low time   | t <sub>cikl</sub> | 1.5 | _   | t <sub>Timer</sub> 1   |

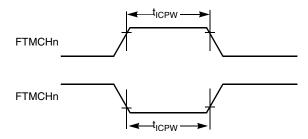

| D | Input capture pulse width | t <sub>ICPW</sub> | 1.5 | _   | t <sub>Timer</sub> 1   |

1.  $t_{Timer} = 1/f_{Timer}$

Figure 11. Timer external clock

Figure 12. Timer input capture pulse

# 5.3 Thermal specifications

## 5.3.1 Thermal operating requirements

Table 9. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| T <sub>J</sub> | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed maximum  $T_J$ . The simplest method to determine  $T_J$  is:  $T_J = T_A + \theta_{JA} x$  chip power dissipation

#### 5.3.2 Thermal characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

| Board type        | Symbol                                                           | Description                                                                                     | 64<br>LQFP | 64 QFP | 44<br>LQFP | 80<br>LQFP | Unit | Notes |

|-------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|--------|------------|------------|------|-------|

| Single-layer (1S) | $R_{\theta JA}$                                                  | Thermal resistance, junction to ambient (natural convection)                                    | 71         | 61     | 75         | 57         | °C/W | 1, 2  |

| Four-layer (2s2p) | $R_{\theta JA}$                                                  | Thermal resistance, junction to ambient (natural convection)                                    | 53         | 47     | 53         | 44         | °C/W | 1, 3  |

| Single-layer (1S) | R <sub>θJMA</sub>                                                | Thermal resistance, junction to ambient (200 ft./min. air speed)                                | 59         | 50     | 62         | 47         | °C/W | 1, 3  |

| Four-layer (2s2p) | Thermal resistance, junction to ambient (200 ft./min. air speed) |                                                                                                 | 46         | 41     | 47         | 38         | °C/W | 1, 3  |

| _                 | R <sub>eJB</sub>                                                 | Thermal resistance, junction to board                                                           | 35         | 32     | 34         | 28         | °C/W | 4     |

| _                 | R <sub>eJC</sub>                                                 | Thermal resistance, junction to case                                                            | 20         | 23     | 20         | 15         | °C/W | 5     |

| _                 | $\Psi_{ m JT}$                                                   | Thermal characterization parameter, junction to package top outside center (natural convection) | 5          | 8      | 5          | 3          | °C/W | 6     |

Table 10. Thermal attributes

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board (JESD51-3) horizontal.

- 3. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the solder pad on the bottom of the package. Interface resistance is ignored.

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization.

The average chip-junction temperature (T<sub>J</sub>) in °C can be obtained from:

$$T_J = T_A + (P_D \times \theta_{JA})$$

KE04 Sub-Family Data Sheet, Rev. 4, 07/2016

Peripheral operating requirements and behaviors

Where:

$T_A = Ambient temperature, °C$

$\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W

$$P_D = P_{int} + P_{I/O}$$

$P_{int} = I_{DD} \times V_{DD}$ , Watts - chip internal power

$P_{I/O}$  = Power dissipation on input and output pins - user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_I$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_I + 273 \, ^{\circ}C)$$

Solving the equations above for K gives:

$$K = P_D \times (T_A + 273 \text{ }^{\circ}C) + \theta_{JA} \times (P_D)^2$$

where K is a constant pertaining to the particular part. K can be determined by measuring  $P_D$  (at equilibrium) for an known  $T_A$ . Using this value of K, the values of  $P_D$  and  $P_D$  and  $P_D$  and  $P_D$  are obtained by solving the above equations iteratively for any value of  $P_D$ .

# 6 Peripheral operating requirements and behaviors

#### 6.1 Core modules

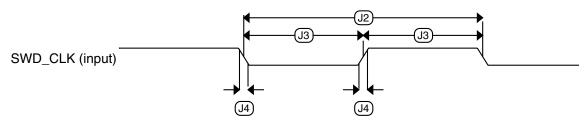

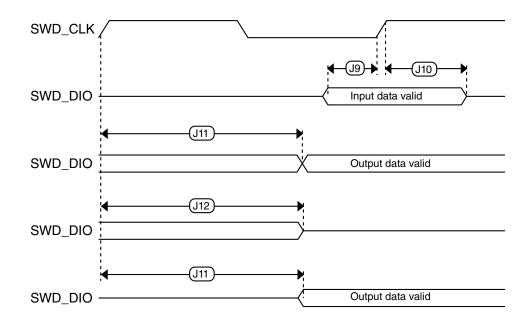

#### 6.1.1 SWD electricals

Table 11. SWD full voltage range electricals

| Symbol | Description                                     | Min. | Max. | Unit |

|--------|-------------------------------------------------|------|------|------|

|        | Operating voltage                               | 2.7  | 5.5  | V    |

| J1     | SWD_CLK frequency of operation                  |      |      |      |

|        | Serial wire debug                               | 0    | 24   | MHz  |

| J2     | SWD_CLK cycle period                            | 1/J1 | _    | ns   |

| J3     | SWD_CLK clock pulse width                       |      |      |      |

|        | Serial wire debug                               | 20   | _    | ns   |

| J4     | SWD_CLK rise and fall times                     | _    | 3    | ns   |

| J9     | SWD_DIO input data setup time to SWD_CLK rise   | 10   | _    | ns   |

| J10    | SWD_DIO input data hold time after SWD_CLK rise | 3    | _    | ns   |

Table continues on the next page...

Table 11. SWD full voltage range electricals (continued)

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| J11    | SWD_CLK high to SWD_DIO data valid | _    | 35   | ns   |

| J12    | SWD_CLK high to SWD_DIO high-Z     | 5    | _    | ns   |

Figure 13. Serial wire clock input timing

Figure 14. Serial wire data timing

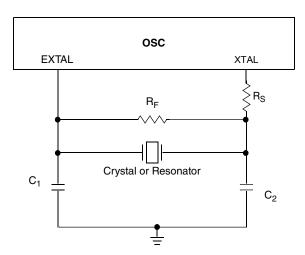

## 6.2 External oscillator (OSC) and ICS characteristics

Table 12. OSC and ICS specifications (temperature range = -40 to 105 °C ambient)

| Num | С | Characteristic         |                        | Symbol          | Min   | Typical <sup>1</sup> | Max     | Unit |

|-----|---|------------------------|------------------------|-----------------|-------|----------------------|---------|------|

| 1   | С | Crystal or             | Low range (RANGE = 0)  | f <sub>lo</sub> | 31.25 | 32.768               | 39.0625 | kHz  |

|     | С | resonator<br>frequency | High range (RANGE = 1) | f <sub>hi</sub> | 4     |                      | 24      | MHz  |

Table continues on the next page...

Peripheral operating requirements and behaviors

Table 12. OSC and ICS specifications (temperature range = -40 to 105 °C ambient) (continued)

| Num | С | C                                                            | haracteristic                                | Symbol               | Min   | Typical <sup>1</sup>  | Max     | Unit |

|-----|---|--------------------------------------------------------------|----------------------------------------------|----------------------|-------|-----------------------|---------|------|

| 2   | D | Lo                                                           | oad capacitors                               | C1, C2               |       | See Note <sup>2</sup> |         |      |

| 3   | D | Feedback<br>resistor                                         | Low Frequency, Low-Power Mode <sup>3</sup>   | R <sub>F</sub>       | _     | _                     | _       | ΜΩ   |

|     |   |                                                              | Low Frequency, High-Gain<br>Mode             |                      | _     | 10                    | _       | ΜΩ   |

|     |   |                                                              | High Frequency, Low-<br>Power Mode           |                      | _     | 1                     | _       | ΜΩ   |

|     |   |                                                              | High Frequency, High-Gain<br>Mode            |                      | _     | 1                     | _       | ΜΩ   |

| 4   | D | Series resistor -                                            | Low-Power Mode <sup>3</sup>                  | R <sub>S</sub>       | _     | 0                     | _       | kΩ   |

|     |   | Low Frequency                                                | High-Gain Mode                               |                      | _     | 200                   | _       | kΩ   |

| 5   | D | Series resistor -<br>High Frequency                          | Low-Power Mode <sup>3</sup>                  | R <sub>S</sub>       | _     | 0                     | _       | kΩ   |

|     | D | Series resistor -                                            | 4 MHz                                        |                      | _     | 0                     | _       | kΩ   |

|     | D | High<br>Frequency,                                           | 8 MHz                                        |                      | _     | 0                     | _       | kΩ   |

|     | D | High-Gain Mode                                               | 16 MHz                                       |                      | _     | 0                     | _       | kΩ   |

| 6   | С | Crystal start-up                                             | Low range, low power                         | t <sub>CSTL</sub>    | _     | 1000                  | _       | ms   |

|     | С | time low range<br>= 32.768 kHz                               | Low range, high gain                         |                      | _     | 800                   | _       | ms   |

|     | С | crystal; High                                                | High range, low power                        | t <sub>CSTH</sub>    | _     | 3                     | _       | ms   |

|     | С | range = 20 MHz<br>crystal <sup>4,5</sup>                     | High range, high gain                        |                      | _     | 1.5                   | _       | ms   |

| 7   | Т | Internal re                                                  | eference start-up time                       | t <sub>IRST</sub>    | _     | 20                    | 50      | μs   |

| 8   | Р | Internal reference                                           | e clock (IRC) frequency trim range           | f <sub>int_t</sub>   | 31.25 | _                     | 39.0625 | kHz  |

| 9   | Р | Internal<br>reference clock<br>frequency,<br>factory trimmed | T = 25 °C, V <sub>DD</sub> = 5 V             | f <sub>int_ft</sub>  | _     | 37.5                  | _       | kHz  |

| 10  | Р | DCO output frequency range                                   | FLL reference = fint_t, flo, or fhi/RDIV     | f <sub>dco</sub>     | 40    | _                     | 50      | MHz  |

| 11  | Р | Factory trimmed internal oscillator accuracy                 | T = 25 °C, V <sub>DD</sub> = 5 V             | Δf <sub>int_ft</sub> | -0.5  | _                     | 0.5     | %    |

| 12  | С | Deviation of IRC over                                        | Over temperature range from -40 °C to 105°C  | $\Delta f_{int\_t}$  | -1    | _                     | 0.5     | %    |

|     |   | temperature when trimmed at T = 25 °C, V <sub>DD</sub> = 5 V | Over temperature range<br>from 0 °C to 105°C | Δf <sub>int_t</sub>  | -0.5  | _                     | 0.5     |      |

| 13  | С | Frequency accuracy of                                        | Over temperature range from -40 °C to 105°C  | $\Delta f_{dco\_ft}$ | -1.5  | _                     | 1       | %    |

|     |   | DCO output<br>using factory<br>trim value                    | Over temperature range from 0 °C to 105°C    | $\Delta f_{dco\_ft}$ | -1    | _                     | 1       |      |

Table continues on the next page...

Table 12. OSC and ICS specifications (temperature range = -40 to 105 °C ambient) (continued)

| Num | С | Characteristic                                                                  | Symbol               | Min | Typical <sup>1</sup> | Max | Unit              |

|-----|---|---------------------------------------------------------------------------------|----------------------|-----|----------------------|-----|-------------------|

| 14  | С | FLL acquisition time <sup>4,6</sup>                                             | t <sub>Acquire</sub> |     |                      | 2   | ms                |

| 15  | С | Long term jitter of DCO output clock (averaged over 2 ms interval) <sup>7</sup> | C <sub>Jitter</sub>  | ı   | 0.02                 | 0.2 | %f <sub>dco</sub> |

- 1. Data in Typical column was characterized at 5.0 V, 25 °C or is typical recommended value.

- 2. See crystal or resonator manufacturer's recommendation.

- 3. Load capacitors (C<sub>1</sub>,C<sub>2</sub>), feedback resistor (R<sub>F</sub>) and series resistor (R<sub>S</sub>) are incorporated internally when RANGE = HGO =

- 4. This parameter is characterized and not tested on each device.

- 5. Proper PC board layout procedures must be followed to achieve specifications.

- 6. This specification applies to any time the FLL reference source or reference divider is changed, trim value changed, or changing from FLL disabled (FBELP, FBILP) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>Bus</sub>.

Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval.

Figure 15. Typical crystal or resonator circuit

### 6.3 NVM specifications

This section provides details about program/erase times and program/erase endurance for the flash memories.

Table 13. Flash characteristics

| С | Characteristic                                    | Symbol                  | Min <sup>1</sup> | Typical <sup>2</sup> | Max <sup>3</sup> | Unit <sup>4</sup> |

|---|---------------------------------------------------|-------------------------|------------------|----------------------|------------------|-------------------|

| D | Supply voltage for program/erase -40 °C to 105 °C | V <sub>prog/erase</sub> | 2.7              | _                    | 5.5              | V                 |

| D | Supply voltage for read operation                 | V <sub>Read</sub>       | 2.7              |                      | 5.5              | V                 |

Table continues on the next page...

KE04 Sub-Family Data Sheet, Rev. 4, 07/2016

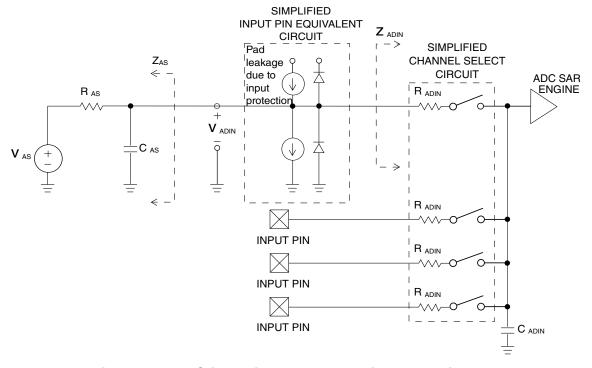

Table 14. 5 V 12-bit ADC operating conditions (continued)

| Characteri<br>stic               | Conditions                                                    | Symbol            | Min        | Typ <sup>1</sup> | Max               | Unit | Comment         |

|----------------------------------|---------------------------------------------------------------|-------------------|------------|------------------|-------------------|------|-----------------|

| Supply                           | Absolute                                                      | V <sub>DDA</sub>  | 2.7        | _                | 5.5               | V    | _               |

| voltage                          | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDA</sub> ) | $\Delta V_{DDA}$  | -100       | 0                | +100              | mV   | _               |

| Input<br>voltage                 |                                                               | V <sub>ADIN</sub> | $V_{REFL}$ | _                | V <sub>REFH</sub> | V    | _               |

| Input capacitance                |                                                               | C <sub>ADIN</sub> | _          | 4.5              | 5.5               | pF   | _               |

| Input resistance                 |                                                               | R <sub>ADIN</sub> | _          | 3                | 5                 | kΩ   | _               |

| Analog<br>source                 | 12-bit mode<br>• f <sub>ADCK</sub> > 4 MHz                    | R <sub>AS</sub>   | _          | _                | 2                 | kΩ   | External to MCU |

| resistance                       | • f <sub>ADCK</sub> < 4 MHz                                   |                   | _          | _                | 5                 |      |                 |

|                                  | 10-bit mode<br>• f <sub>ADCK</sub> > 4 MHz                    |                   | <u> </u>   | _                | 5                 |      |                 |

|                                  | • f <sub>ADCK</sub> < 4 MHz                                   |                   | _          | _                | 10                |      |                 |

|                                  | 8-bit mode                                                    |                   | _          | _                | 10                |      |                 |

|                                  | (all valid f <sub>ADCK</sub> )                                |                   |            |                  |                   |      |                 |

| ADC                              | High speed (ADLPC=0)                                          | f <sub>ADCK</sub> | 0.4        | _                | 8.0               | MHz  | _               |

| conversion<br>clock<br>frequency | Low power (ADLPC=1)                                           |                   | 0.4        | _                | 4.0               |      |                 |

1. Typical values assume  $V_{DDA} = 5.0 \text{ V}$ , Temp = 25°C,  $f_{ADCK} = 1.0 \text{ MHz}$  unless otherwise stated. Typical values are for reference only and are not tested in production.

Figure 16. ADC input impedance equivalency diagram

#### Peripheral operating requirements and behaviors

Table 15. 12-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ )

| Characteristic                    | Conditions                  | C | Symbol             | Min  | Typ <sup>1</sup> | Max | Unit             |

|-----------------------------------|-----------------------------|---|--------------------|------|------------------|-----|------------------|

| Supply current                    |                             | Т | I <sub>DDA</sub>   | _    | 133              | _   | μΑ               |

| ADLPC = 1                         |                             |   |                    |      |                  |     |                  |

| ADLSMP = 1                        |                             |   |                    |      |                  |     |                  |

| ADCO = 1                          |                             |   |                    |      |                  |     |                  |

| Supply current                    |                             | Т | I <sub>DDA</sub>   | _    | 218              | _   | μA               |

| ADLPC = 1                         |                             |   |                    |      |                  |     |                  |

| ADLSMP = 0                        |                             |   |                    |      |                  |     |                  |

| ADCO = 1                          |                             |   |                    |      |                  |     |                  |

| Supply current                    |                             | Т | I <sub>DDA</sub>   | _    | 327              | _   | μA               |

| ADLPC = 0                         |                             |   |                    |      |                  |     |                  |

| ADLSMP = 1                        |                             |   |                    |      |                  |     |                  |

| ADCO = 1                          |                             |   |                    |      |                  |     |                  |

| Supply current                    |                             | Т | I <sub>DDA</sub>   | _    | 582              | 990 | μA               |

| ADLPC = 0                         |                             |   |                    |      |                  |     |                  |

| ADLSMP = 0                        |                             |   |                    |      |                  |     |                  |

| ADCO = 1                          |                             |   |                    |      |                  |     |                  |

| Supply current                    | Stop, reset, module off     | Т | I <sub>DDA</sub>   | _    | 0.011            | 1   | μА               |

| ADC asynchronous clock source     | High speed (ADLPC = 0)      | Р | f <sub>ADACK</sub> | 2    | 3.3              | 5   | MHz              |

|                                   | Low power (ADLPC = 1)       |   |                    | 1.25 | 2                | 3.3 |                  |

| Conversion time (including sample | Short sample (ADLSMP = 0)   | Т | t <sub>ADC</sub>   | _    | 20               | _   | ADCK cycles      |

| time)                             | Long sample<br>(ADLSMP = 1) |   |                    | _    | 40               | _   |                  |

| Sample time                       | Short sample (ADLSMP = 0)   | Т | t <sub>ADS</sub>   | _    | 3.5              | _   | ADCK cycles      |

|                                   | Long sample (ADLSMP = 1)    |   |                    | _    | 23.5             | _   |                  |

| Total unadjusted                  | 12-bit mode                 | С | E <sub>TUE</sub>   | _    | ±5.0             | _   | LSB <sup>3</sup> |

| Error <sup>2</sup>                | 10-bit mode                 | С |                    | _    | ±1.5             | _   |                  |

|                                   | 8-bit mode                  | С |                    | _    | ±0.8             | _   |                  |

| Differential Non-                 | 12-bit mode                 | С | DNL                | _    | ±1.5             | _   | LSB <sup>3</sup> |

| Liniarity                         | 10-bit mode                 | С |                    | _    | ±0.4             | _   |                  |

|                                   | 8-bit mode                  | С |                    | _    | ±0.15            | _   |                  |

| Integral Non-Linearity            |                             | С | INL                | _    | ±1.5             | _   | LSB <sup>3</sup> |

|                                   | 10-bit mode                 | С |                    | _    | ±0.4             | _   |                  |

|                                   | 8-bit mode                  | С |                    | _    | ±0.15            | _   |                  |

| Zero-scale error <sup>4</sup>     | 12-bit mode                 | С | E <sub>ZS</sub>    | _    | ±1.0             | _   | LSB <sup>3</sup> |

|                                   | 10-bit mode                 | С |                    | _    | ±0.2             | _   |                  |

Table continues on the next page...

Table 15. 12-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

| Characteristic                   | Conditions    | С | Symbol              | Min | Typ <sup>1</sup>                  | Max  | Unit             |

|----------------------------------|---------------|---|---------------------|-----|-----------------------------------|------|------------------|

|                                  | 8-bit mode    | С |                     | _   | ±0.35                             | _    |                  |

| Full-scale error <sup>5</sup>    | 12-bit mode   | С | E <sub>FS</sub>     | _   | ±2.5                              | _    | LSB <sup>3</sup> |

|                                  | 10-bit mode   | С |                     | _   | ±0.3                              | _    |                  |

|                                  | 8-bit mode    | С |                     | _   | ±0.25                             | _    |                  |

| Quantization error               | ≤12 bit modes | D | EQ                  | _   | _                                 | ±0.5 | LSB <sup>3</sup> |

| Input leakage error <sup>6</sup> | all modes     | D | E <sub>IL</sub>     |     | I <sub>In</sub> * R <sub>AS</sub> |      | mV               |

| Temp sensor slope                | -40 °C–25 °C  | D | m                   | _   | 3.266                             | _    | mV/°C            |

|                                  | 25 °C–125 °C  |   |                     | _   | 3.638                             | _    |                  |

| Temp sensor voltage              | 25 °C         | D | V <sub>TEMP25</sub> | _   | 1.396                             | _    | V                |

Typical values assume V<sub>DDA</sub> = 5.0 V, Temp = 25 °C, f<sub>ADCK</sub>=1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

## 6.4.2 Analog comparator (ACMP) electricals

Table 16. Comparator electrical specifications

| С | Characteristic                                   | Symbol              | Min                   | Typical | Max       | Unit |

|---|--------------------------------------------------|---------------------|-----------------------|---------|-----------|------|

| D | Supply voltage                                   | $V_{DDA}$           | 2.7                   | _       | 5.5       | V    |

| Т | Supply current (Operation mode) I <sub>DDA</sub> |                     | _                     | 10      | 20        | μΑ   |

| D | Analog input voltage                             | V <sub>AIN</sub>    | V <sub>SS</sub> - 0.3 | _       | $V_{DDA}$ | V    |

| Р | Analog input offset voltage                      | V <sub>AIO</sub>    | _                     | _       | 40        | mV   |

| С | Analog comparator hysteresis (HYST=0)            | $V_{H}$             | _                     | 15      | 20        | mV   |

| С | Analog comparator hysteresis (HYST=1)            | V <sub>H</sub>      | _                     | 20      | 30        | mV   |

| Т | Supply current (Off mode)                        | I <sub>DDAOFF</sub> | _                     | 60      | _         | nA   |

| С | Propagation Delay                                | t <sub>D</sub>      | _                     | 0.4     | 1         | μs   |

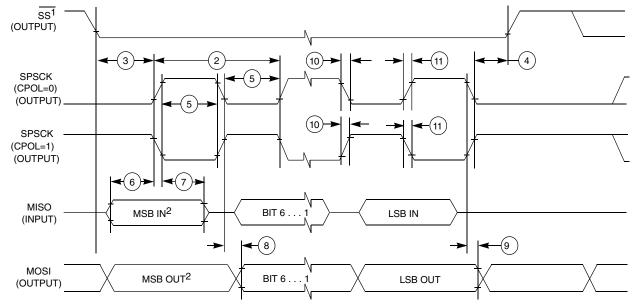

#### 6.5 Communication interfaces

## 6.5.1 SPI switching specifications

The serial peripheral interface (SPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic SPI timing modes. See the SPI chapter of the

<sup>2.</sup> Includes quantization

<sup>3.</sup>  $1 LSB = (V_{REFH} - V_{REFL})/2^{N}$

<sup>4.</sup>  $V_{ADIN} = V_{SSA}$

<sup>5.</sup>  $V_{ADIN} = V_{DDA}$

<sup>6.</sup> I<sub>In</sub> = leakage current (refer to DC characteristics)

#### Peripheral operating requirements and behaviors

chip's reference manual for information about the modified transfer formats used for communicating with slower peripheral devices. All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$ , unless noted, and 25 pF load on all SPI pins. All timing assumes slew rate control is disabled and high-drive strength is enabled for SPI output pins.

| Table 17. SPI master m | node timing |

|------------------------|-------------|

|------------------------|-------------|

| Nu<br>m. | Symbol              | Description                    | Min.                   | Max.                    | Unit               | Comment                              |

|----------|---------------------|--------------------------------|------------------------|-------------------------|--------------------|--------------------------------------|

| 1        | f <sub>op</sub>     | Frequency of operation         | f <sub>Bus</sub> /2048 | f <sub>Bus</sub> /2     | Hz                 | f <sub>Bus</sub> is the bus<br>clock |

| 2        | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>Bus</sub>   | 2048 x t <sub>Bus</sub> | ns                 | $t_{Bus} = 1/f_{Bus}$                |

| 3        | t <sub>Lead</sub>   | Enable lead time               | 1/2                    | _                       | t <sub>SPSCK</sub> | _                                    |

| 4        | t <sub>Lag</sub>    | Enable lag time                | 1/2                    | _                       | t <sub>SPSCK</sub> | _                                    |

| 5        | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>Bus</sub> – 30  | 1024 x t <sub>Bus</sub> | ns                 | _                                    |

| 6        | t <sub>SU</sub>     | Data setup time (inputs)       | 8                      | _                       | ns                 | _                                    |

| 7        | t <sub>HI</sub>     | Data hold time (inputs)        | 8                      | _                       | ns                 | _                                    |

| 8        | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                      | 25                      | ns                 | _                                    |

| 9        | t <sub>HO</sub>     | Data hold time (outputs)       | 20                     | _                       | ns                 | _                                    |

| 10       | t <sub>RI</sub>     | Rise time input                | _                      | t <sub>Bus</sub> – 25   | ns                 | _                                    |

|          | t <sub>FI</sub>     | Fall time input                |                        |                         |                    |                                      |

| 11       | t <sub>RO</sub>     | Rise time output               | _                      | 25                      | ns                 | _                                    |

|          | t <sub>FO</sub>     | Fall time output               |                        |                         |                    |                                      |

<sup>1.</sup> If configured as an output.

Figure 17. SPI master mode timing (CPHA=0)

<sup>2.</sup> LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

To find a package drawing, go to **nxp.com** and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| 32-pin QFN                               | 98ASA00473D                   |

| 44-pin LQFP                              | 98ASS23225W                   |

| 64-pin QFP                               | 98ASB42844B                   |

| 64-pin LQFP                              | 98ASS23234W                   |

| 80-pin LQFP                              | 98ASS23237W                   |

#### 8 Pinout

## 8.1 Signal multiplexing and pin assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

#### **NOTE**

VSS and VSSA are internally connected.

VREFH and VDDA are internally connected in 64-pin packages.

PTB4, PTB5, PTD0, PTD1, PTE0, PTE1, PTH0, and PTH1 are high-current drive pins when operated as output.

PTA2 and PTA3 are true open-drain pins when operated as output.

| 80<br>LQFP | 64<br>LQFP<br>/QFP | 44<br>LQFP | Pin Name | Default  | ALT0 | ALT1     | ALT2     | ALT3      | ALT4     | ALT5 | ALT6 | ALT7 |

|------------|--------------------|------------|----------|----------|------|----------|----------|-----------|----------|------|------|------|

| 1          | 1                  | 1          | PTD1     | DISABLED | PTD1 | KBI0_P25 | FTM2_CH3 | SPI1_MOSI |          |      |      |      |

| 2          | 2                  | 2          | PTD0     | DISABLED | PTD0 | KBI0_P24 | FTM2_CH2 | SPI1_SCK  |          |      |      |      |

| 3          | 3                  | _          | PTH7     | DISABLED | PTH7 | KBI1_P31 | PWT_IN1  |           |          |      |      |      |

| 4          | 4                  | _          | PTH6     | DISABLED | PTH6 | KBI1_P30 |          |           |          |      |      |      |

| 5          | -                  | 1          | PTH5     | DISABLED | PTH5 | KBI1_P29 |          |           |          |      |      |      |

| 6          | 5                  | 3          | PTE7     | DISABLED | PTE7 | KBI1_P7  | TCLK2    |           | FTM1_CH1 |      |      |      |

| 7          | 6                  | 4          | PTH2     | DISABLED | PTH2 | KBI1_P26 | BUSOUT   |           | FTM1_CH0 |      |      |      |

| 8          | 7                  | 5          | VDD      | VDD      |      |          |          |           |          |      | VDD  |      |

| 80<br>LQFP | 64<br>LQFP<br>/QFP | 44<br>LQFP | Pin Name | Default  | ALT0 | ALT1     | ALT2           | ALT3              | ALT4      | ALT5           | ALT6 | ALT7 |

|------------|--------------------|------------|----------|----------|------|----------|----------------|-------------------|-----------|----------------|------|------|

| 49         | 41                 | 28         | VDD      | VDD      |      |          |                |                   |           |                | VDD  |      |

| 50         | _                  | _          | PTG7     | DISABLED | PTG7 | KBI1_P23 | FTM2_CH5       | SPI1_PCS          |           |                |      |      |

| 51         | _                  | -          | PTG6     | DISABLED | PTG6 | KBI1_P22 | FTM2_CH4       | SPI1_MISO         |           |                |      |      |

| 52         | _                  | _          | PTG5     | DISABLED | PTG5 | KBI1_P21 | FTM2_CH3       | SPI1_MOSI         |           |                |      |      |

| 53         | _                  | _          | PTG4     | DISABLED | PTG4 | KBI1_P20 | FTM2_CH2       | SPI1_SCK          |           |                |      |      |

| 54         | 42                 | _          | PTF1     | DISABLED | PTF1 | KBI1_P9  | FTM2_CH1       |                   |           |                |      |      |

| 55         | 43                 | -          | PTF0     | DISABLED | PTF0 | KBI1_P8  | FTM2_CH0       |                   |           |                |      |      |

| 56         | 44                 | 29         | PTD4     | DISABLED | PTD4 | KBI0_P28 |                |                   |           |                |      |      |

| 57         | 45                 | 30         | PTD3     | DISABLED | PTD3 | KBI0_P27 | SPI1_PCS       |                   |           |                |      |      |

| 58         | 46                 | 31         | PTD2     | DISABLED | PTD2 | KBI0_P26 | SPI1_MISO      |                   |           |                |      |      |

| 59         | 47                 | 32         | PTA3     | DISABLED | PTA3 | KBI0_P3  | UART0_TX       | I2C0_SCL          |           |                |      |      |

| 60         | 48                 | 33         | PTA2     | DISABLED | PTA2 | KBI0_P2  | UART0_RX       | I2C0_SDA          |           |                |      |      |

| 61         | 49                 | 34         | PTA1     | ADC0_SE1 | PTA1 | KBI0_P1  | FTM0_CH1       | I2CO_<br>4WSDAOUT | ACMP0_IN1 | ADC0_SE1       |      |      |

| 62         | 50                 | 35         | PTA0     | ADC0_SE0 | PTA0 | KBI0_P0  | FTM0_CH0       | I2C0_<br>4WSCLOUT | ACMP0_IN0 | ADC0_SE0       |      |      |

| 63         | 51                 | 36         | PTC7     | DISABLED | PTC7 | KBI0_P23 | UART1_TX       |                   |           |                |      |      |

| 64         | 52                 | 37         | PTC6     | DISABLED | PTC6 | KBI0_P22 | UART1_RX       |                   |           |                |      |      |

| 65         | _                  | _          | PTI3     | DISABLED | PTI3 | IRQ      |                |                   |           |                |      |      |

| 66         | _                  | _          | PTI2     | DISABLED | PTI2 | IRQ      |                |                   |           |                |      |      |

| 67         | 53                 | 1          | PTE3     | DISABLED | PTE3 | KBI1_P3  | SPI0_PCS       |                   |           |                |      |      |

| 68         | 54                 | 38         | PTE2     | DISABLED | PTE2 | KBI1_P2  | SPI0_MISO      | PWT_IN0           |           |                |      |      |

| 69         | _                  | 1          | VSS      | VSS      |      |          |                |                   |           |                | VSS  |      |

| 70         | _                  | 1          | VDD      | VDD      |      |          |                |                   |           |                | VDD  |      |

| 71         | 55                 | ı          | PTG3     | DISABLED | PTG3 | KBI1_P19 |                |                   |           |                |      |      |

| 72         | 56                 | _          | PTG2     | DISABLED | PTG2 | KBI1_P18 |                |                   |           |                |      |      |

| 73         | 57                 | -          | PTG1     | DISABLED | PTG1 | KBI1_P17 |                |                   |           |                |      |      |

| 74         | 58                 | _          | PTG0     | DISABLED | PTG0 | KBI1_P16 |                |                   |           |                |      |      |

| 75         | 59                 | 39         | PTE1     | DISABLED | PTE1 | KBI1_P1  | SPI0_MOSI      |                   | I2C1_SCL  |                |      |      |

| 76         | 60                 | 40         | PTE0     | DISABLED | PTE0 | KBI1_P0  | SPI0_SCK       | TCLK1             | I2C1_SDA  |                |      |      |

| 77         | 61                 | 41         | PTC5     | DISABLED | PTC5 | KBI0_P21 |                | FTM1_CH1          |           | RTC_<br>CLKOUT |      |      |

| 78         | 62                 | 42         | PTC4     | SWD_CLK  | PTC4 | KBI0_P20 | RTC_<br>CLKOUT | FTM1_CH0          | ACMP0_IN2 | SWD_CLK        |      |      |

| 79         | 63                 | 43         | PTA5     | RESET_b  | PTA5 | KBI0_P5  | IRQ            | TCLK0             | RESET_b   |                |      |      |

| 80         | 64                 | 44         | PTA4     | SWD_DIO  | PTA4 | KBI0_P4  |                | ACMP0_OUT         | SWD_DIO   |                |      |      |

# 8.2 Device pin assignment

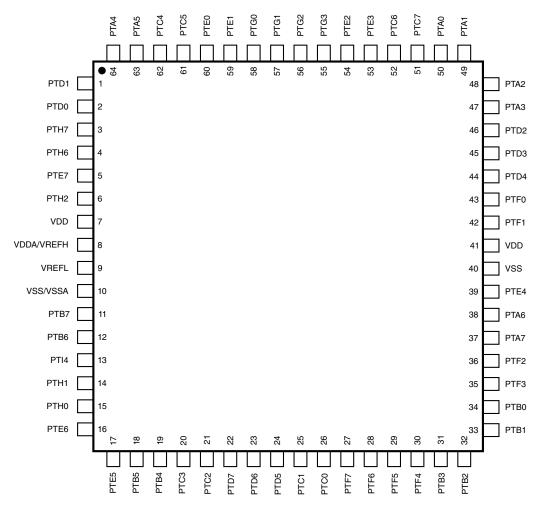

Figure 22. 64-pin QFP/LQFP packages

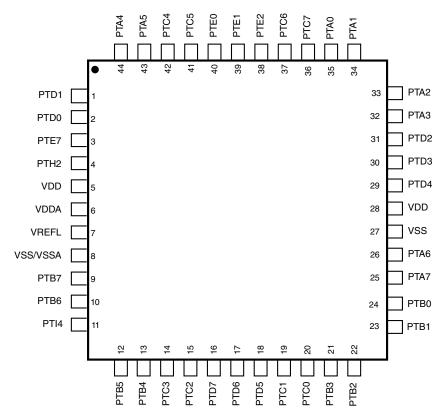

Figure 23. 44-pin LQFP package

# 9 Revision history

The following table provides a revision history for this document.

Table 19. Revision history

| Rev. No. | Date    | Substantial Changes                                                                                                                                              |  |  |  |  |  |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1        | 12/2013 | Initial NDA release.                                                                                                                                             |  |  |  |  |  |

| 2        | 3/2014  | Initial public release.                                                                                                                                          |  |  |  |  |  |

| 3        | 5/2014  | <ul> <li>Updated the Max. of SI<sub>DD</sub>.</li> <li>Updated footnote to the V<sub>OH</sub>.</li> <li>Corrected Unit in the FTM input timing table.</li> </ul> |  |  |  |  |  |

| 4        | 07/2016 | <ul> <li>Added a new section of Thermal operating requirements.</li> <li>Corrected pinout diagram for 44-pin LQFP in the Device pin assignment.</li> </ul>       |  |  |  |  |  |

How to Reach Us:

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, Freescale, the Freescale logo, and Kinetis are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, the ARM powered logo, and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

©2013-2016 NXP B.V.

Document Number MKE04P80M48SF0 Revision 4, 07/2016