#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                     |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                                    |

| Core Size                  | 8-Bit                                                                                   |

| Speed                      | 20MHz                                                                                   |

| Connectivity               | -                                                                                       |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                         |

| Number of I/O              | 18                                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | 128 x 8                                                                                 |

| RAM Size                   | 128 x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x10b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Through Hole                                                                            |

| Package / Case             | 20-DIP Module                                                                           |

| Supplier Device Package    | -                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w79e8213akg |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### nuvoTon

### 2. FEATURES

- Fully static design 8-bit 4T-8051 CMOS microcontroller:

- VDD = 4.5V to 5.5V @20MHz

- VDD = 2.7V to 5.5V @12MHz

- VDD = 2.4V to 5.5V @4MHz

- Instruction-set compatible with MSC-51.

- Flexible CPU clock source configurable by config bit and software:

- High speed external oscillator: upto 20MHz Crystal and resonator (enabled by config bit).

- Internal RC oscillator: 20/10MHz selectable by config bit, only W79E8213R supports ±2% accuracy internal RC oscillator at fixed voltage and temperature condition.

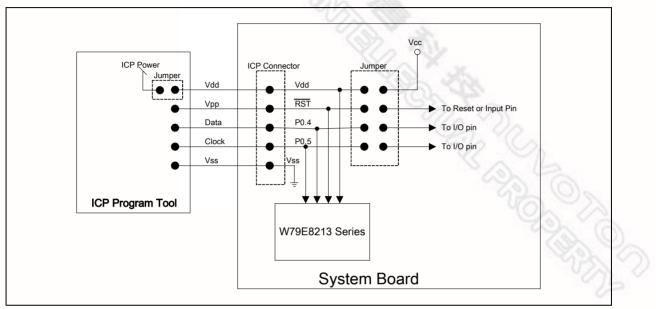

- 4K bytes of AP Flash EPROM, with ICP and external writer programmable mode.

- 128 bytes of on-chip RAM.

- W79E8213 series supports 128 bytes NVM Data Flash EPROM for customer data storage used and 10K writer cycles.

- 8 pages. Page size is 16 bytes.

- Two 16-bit timer/counters.

- Ten interrupts source with four levels of priority.

- Three-edge detect interrupt inputs.

- Programmable Watchdog Timer.

- Four-channel 10-bit PWM (Pulse Width Modulator).

- Internal square wave generator for buzzer.

- Up to 18 I/O pins.

- The 4 outputs mode and TTL/Schmitt trigger selectable Port.

- ▶ LED drive capability on all port pins. Sink 20mA; Drive: -15~-20mA @push-pull mode.

- Eight high sink capability (40mA) port pins.

- Eight-channel multiplexed with 10-bits A/D convert.

- Low Voltage Detect interrupt and reset.

- Development Tools:

- ICP(In Circuit Programming) writer

- Packages:

| - Lead Free (RoHS) DIP 20: | W79E8213AKG |

|----------------------------|-------------|

|                            |             |

| - Leau Fiee ( | RUNS) SOF 20. | W/9E0213A3G  |

|---------------|---------------|--------------|

| - Lead Free ( | RoHS) DIP 20: | W79E8213RAKG |

- Lead Free (RoHS) SOP 20: W79E8213RASG

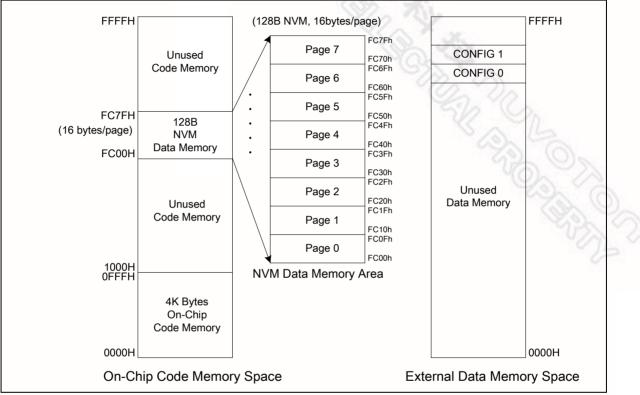

### 7. MEMORY ORGANIZATION

The W79E8213 series separate the memory into two separate sections, the Program Memory and the Data Memory. The Program Memory is used to store the instruction op-codes, while the Data Memory is used to store data or for memory mapped devices.

Figure 7-1: W79E8213 series memory map

#### 7.1 Program Memory (on-chip Flash)

The Program Memory on the W79E8213 series can be up to 4K bytes long. All instructions are fetched for execution from this memory area. The MOVC instruction can also access this memory region.

#### 7.2 Data Flash Memory

The NVM Data Memory of Flash EPROM on the W79E8213 series is 128 bytes long, with page size of 16 bytes, respectively. The W79E8213 series' NVM size is controllable through CONFIG1 register. The W79E8213 series read the content of data memory by using "MOVC A, @A+DPTR". To write data is by NVMADDRL, NVMDATA and NVMCON SFR's registers.

#### 7.3 Data Memory (accessed by MOVX)

Not available in this product series.

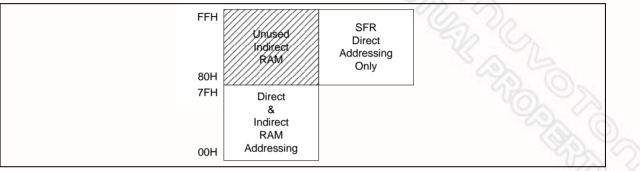

### 7.4 Scratch-pad RAM and Register Map

As mentioned before the W79E8213 series have separate Program and Data Memory areas. The onchip 128 bytes scratch pad RAM is in addition to the external memory. There are also several Special Function Registers (SFRs) which can be accessed by software. The SFRs can be accessed only by direct addressing, while the on-chip RAM can be accessed by either direct or indirect addressing.

Figure 7-2: W79E8213 RAM and SFR memory map

Since the scratch-pad RAM is only 128 bytes it can be used only when data contents are small. There are several other special purpose areas within the scratch-pad RAM. These are described as following.

#### 8. SPECIAL FUNCTION REGISTERS

The W79E8213 series uses Special Function Registers (SFRs) to control and monitor peripherals and their Modes. The SFRs reside in the register locations 80-FFh and are accessed by direct addressing only. Some of the SFRs are bit addressable. This is very useful in cases where users wish to modify a particular bit without changing the others. The SFRs that are bit addressable are those whose addresses end in 0 or 8. The W79E8213 series contain all the SFRs present in the standard 8052. However some additional SFRs are added. In some cases the unused bits in the original 8052, have been given new functions. The list of the SFRs is as following.

| F8 | IP1   | BUZCON |              |         |         | Corto | 0        |         |

|----|-------|--------|--------------|---------|---------|-------|----------|---------|

| F0 | В     |        |              |         |         | Y     | PADIDS   | IP1H    |

| E8 | EIE   |        |              |         |         |       | SAN A    | 2       |

| E0 | ACC   | ADCCON | ADCH         | ADCCON1 |         |       | No.      | 0       |

| D8 | WDCON | PWMPL  | <b>PWM0L</b> | PWM1L   | PWMCON1 | PWM2L | PWM3L    | PWMCON2 |

| D0 | PSW   | PWMPH  | PWM0H        | PWM1H   |         | PWM2H | PWM3H    | PWMCON3 |

| C8 |       |        |              |         |         |       | NVMCON   | NVMDATA |

| C0 |       |        |              |         |         |       | NVMADDRL | ТА      |

| B8 | IP0   |        |              |         |         |       |          |         |

| B0 |       | P0M1   | P0M2         | P1M1    | P1M2    | P2M1  | P2M2     | IP0H    |

| A8 | IE    |        |              |         |         |       |          |         |

| A0 | P2    |        | AUXR1        | EDIC    |         |       |          |         |

| 98 |       |        |              |         |         |       |          |         |

| 90 | P1    |        |              |         |         |       |          |         |

| 88 | TCON  | TMOD   | TL0          | TL1     | TH0     | TH1   | CKCON    |         |

| 80 | P0    | SP     | DPL          | DPH     |         |       |          | PCON    |

Table 8-1: Special Function Register Location Table

Note: 1. The SFRs in the column with dark borders are bit-addressable

2. The table is condensed with eight locations per row. Empty locations indicate that these are no registers at these addresses. When a bit or register is not implemented, it will read high.

# nuvoTon

| SYMBOL   | DEFINITION                            | DN ADD MSB BIT_ADDRESS, SYMBOL<br>RESS LSB |               |                    |               |               |               |               |               | RESET         |                                                                                                      |

|----------|---------------------------------------|--------------------------------------------|---------------|--------------------|---------------|---------------|---------------|---------------|---------------|---------------|------------------------------------------------------------------------------------------------------|

| BUZCON   | Square wave control register          | F9H                                        | -             | -                  | BUZDIV.<br>5  | BUZDIV.<br>4  | BUZDIV.<br>3  | BUZDIV.<br>2  | BUZDIV.<br>1  | BUZDIV.<br>0  | xx00 0000                                                                                            |

| IP1      | Interrupt priority 1                  | F8H                                        | (FF)<br>PED   | (FE)<br>PPWM       | (FD)<br>PBK   | (FC)<br>PWDI  | (FB)<br>-     | (FA)<br>-     | (F9)<br>-     | (F8)<br>-     | 0000xxxxB                                                                                            |

| IP1H     | Interrupt high priority 1             | F7H                                        | PEDH          | PPWMH              | PBKH          | PWDIH         | - 20          | 1             | -             | -             | 0000xxxxB                                                                                            |

| PADIDS   | Port ADC digital input disable        | F6H                                        |               |                    |               | Y             |               | 1. 11         |               |               | 00000000                                                                                             |

| В        | B register                            | F0H                                        | (F7)          | (F6)               | (F5)          | (F4)          | (F3)          | (F2)          | (F1)          | (F0)          | 0000000E                                                                                             |

| EIE      | Interrupt enable 1                    | E8H                                        | (EF)<br>EED   | (EE)<br>EPWMU<br>F | (ED)<br>EPWM  | (EC)<br>EWDI  | (EB)<br>-     | (EA)<br>-     | (E9)<br>-     | (E8)<br>-     | 0000xxxxB                                                                                            |

| ADCCON1  | ADC control register 1                | E3H                                        | ADCLK.<br>1   | ADCLK.<br>0        | -             | -             | -             | AADR2         | 5             | Co.           | 10xxx0xxB                                                                                            |

| ADCH     | ADC converter result high<br>register | E2H                                        | ADC.9         | ADC.8              | ADC.7         | ADC.6         | ADC.5         | ADC.4         | ADC.3         | ADC.2         | 00000000                                                                                             |

| ADCCON   | ADC control register                  | E1H                                        | ADC.1         | ADC.0              | ADCEX         | ADCI          | ADCS          | RCCLK         | AADR1         | AADR0         | 00000000                                                                                             |

| ACC      | Accumulator                           | E0H                                        | (E7)          | (E6)               | (E5)          | (E4)          | (E3)          | (E2)          | (E1)          | (E0)          | 00000000                                                                                             |

| PWMCON2  | PWM control register 2                | DFH                                        | вксн          | BKPS               | BPEN          | BKEN          | PWM3B         | PWM2B         | PWM1B         | <b>PWM0B</b>  | 00000000                                                                                             |

| PWM3L    | PWM 3 low bits register               | DEH                                        | PWM3.7        | PWM3.6             | PWM3.5        | PWM3.4        | PWM3.3        | PWM3.2        | PWM3.1        | PWM3.0        | 00000000                                                                                             |

| PWM2L    | PWM 2 low bits register               | DDH                                        | PWM2.7        | PWM2.6             | PWM2.5        | PWM2.4        | PWM2.3        | PWM2.2        | PWM2.1        | PWM2.0        | 00000000                                                                                             |

| PWMCON1  | PWM control register 1                | DCH                                        | PWMRU<br>N    | load               | PWMF          | CLRPW<br>M    | PWM3I         | PWM2I         | PWM1I         | PWM0I         | 00000000                                                                                             |

| PWM1L    | PWM 1 low bits register               | DBH                                        | PWM1.7        | PWM1.6             | PWM1.5        | PWM1.4        | PWM1.3        | PWM1.2        | PWM1.1        | PWM1.0        | 00000000                                                                                             |

| PWM0L    | PWM 0 low bits register               | DAH                                        | PWM0.7        | PWM0.6             | PWM0.5        | PWM0.4        | PWM0.3        | PWM0.2        | PWM0.1        | PWM0.0        | 0000000                                                                                              |

| PWMPL    | PWM counter low register              | D9H                                        | PWMP0.<br>7   | PWMP0.<br>6        | PWMP0.<br>5   | PWMP0.<br>4   | PWMP0.<br>3   | PWMP0.<br>2   | PWMP0.<br>1   | PWMP0.<br>0   | 00000000                                                                                             |

| WDCON    | Watch-Dog control                     | D8H                                        | (DF)<br>WDRUN | (DE)<br>-          | (DD)<br>WD1   | (DC)<br>WD0   | (DB)<br>WDIF  | (DA)<br>WTRF  | (D9)<br>EWRST | (D8)<br>WDCLR | External<br>reset:<br>0x00 0000<br>Watchdog<br>reset:<br>0x00 0100<br>Power on<br>reset<br>0x0000000 |

| PWMCON3  | PWM control register 3                | D7H                                        | -             | -                  | -             | -             | FP1           | FP0           | -             | BKF           | xxxx00x0E                                                                                            |

| РШМЗН    | PWM 3 high bits register              | D6H                                        | -             | -                  | -             | -             | -             | -             | PWM3.9        | PWM3.8        | xxxxxx00E                                                                                            |

| PWM2H    | PWM 2 high bits register              | D5H                                        | _             | _                  | _             | -             | _             | _             | PWM2.9        | PWM2.8        | xxxxxx00E                                                                                            |

| PWM1H    | PWM 1 high bits register              | D3H                                        |               |                    | _             | _             |               | _             | PWM1.9        | PWM1.8        |                                                                                                      |

| PWM0H    | PWM 0 high bits register              | D2H                                        | -             | -                  | -             | -             | -             | -             | -             | -             | xxxxxx00E                                                                                            |

| PWMPH    | PWM counter high register             | D1H                                        | -             | -                  | -             | -             | -             | -             | PWMP0.        | PWMP0.        | 00000000                                                                                             |

| PSW      | Program status word                   | D0H                                        | (D7)          | (D6)               | (D5)          | (D4)          | (D3)          | (D2)          | (D1)          | (D0)          | 00000000                                                                                             |

| NVMDATA  | NIV/M Data                            | CFH                                        | CY            | AC                 | F0            | RS1           | RS0           | OV            | F1            | Р             | 00000000                                                                                             |

| NVMCON   | NVM Data<br>NVM Control               |                                            | EER           | EWR                |               |               |               |               |               |               | 00000000                                                                                             |

| TA       | Timed Access Protection               |                                            | TA.7          | TA.6               | -<br>TA.5     | -<br>TA.4     | -<br>TA.3     | -<br>TA.2     | -<br>TA.1     | -<br>TA.0     | 111111111                                                                                            |

| NVMADDRL | NVM low byte address                  | С6Н                                        | -             | NVMAD<br>DR.6      | NVMAD<br>DR.5 | NVMAD<br>DR.4 | NVMAD<br>DR.3 | NVMAD<br>DR.2 | NVMAD<br>DR.1 | NVMAD<br>DR.0 | 00000000                                                                                             |

| IP0      | Interrupt priority                    | B8H                                        | (BF)          | (BE)<br>PADC       | (BD)<br>PBO   | (BC)          | (BB)<br>PT1   | (BA)<br>PX1   | (B9)<br>PT0   | (B8)<br>PX0   | x00x0000                                                                                             |

# nuvoTon

| BIT | NAME | FUNCTION                                                                                                                                                                                       |  |  |  |  |  |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | TF1  | Timer 1 Overflow Flag. This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. Software can also set or clear this bit. |  |  |  |  |  |

| 6   | TR1  | Timer 1 Run Control. This bit is set or cleared by software to turn timer/counter on or off.                                                                                                   |  |  |  |  |  |

| 5   | TF0  | Timer 0 Overflow Flag. This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit. |  |  |  |  |  |

| 4   | TR0  | Timer 0 Run Control. This bit is set or cleared by software to turn timer/counter on or off.                                                                                                   |  |  |  |  |  |

|     |      | Interrupt 1 Edge Detect Flag: Set by hardware when an edge/level is detected on                                                                                                                |  |  |  |  |  |

| 3   | IE1  | INT1. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the inverse of the pin.                           |  |  |  |  |  |

| 2   | IT1  | Interrupt 1 Type Control. Set/cleared by software to specify falling edge/ low level triggered external inputs.                                                                                |  |  |  |  |  |

|     |      | Interrupt 0 Edge Detect Flag. Set by hardware when an edge/level is detected on                                                                                                                |  |  |  |  |  |

| 1   | IE0  | INT0. This bit is cleared by hardware when the service routine is vectored to only if the interrupt was edge triggered. Otherwise it follows the inverse of the pin.                           |  |  |  |  |  |

| 0   | IT0  | Interrupt 0 Type Control: Set/cleared by software to specify falling edge/ low level triggered external inputs.                                                                                |  |  |  |  |  |

#### TIMER MODE CONTROL

| Bit: | 7      | 6                | 5  | 4  | 3      | 2                | 1  | 0  |

|------|--------|------------------|----|----|--------|------------------|----|----|

|      | GATE   | $C/\overline{T}$ | M1 | MO | GATE   | $C/\overline{T}$ | M1 | M0 |

|      | TIMER1 |                  |    |    | TIMER0 |                  |    |    |

Mnemonic: TMOD

Address: 89h

| BIT | NAME                      | FUNCTION                                                                                                                                      |  |  |  |  |

|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     |                           | Gating control: When this bit is set, Timer/counter 1 is enabled only while the $\overline{INT1}$                                             |  |  |  |  |

| 7   | GATE                      | pin is high and the TR1 control bit is set. When cleared, the INT1 pin has no effect, and Timer 1 is enabled whenever TR1 control bit is set. |  |  |  |  |

| 6   | C/T                       | Timer or Counter Select: When clear, Timer 1 is incremented by the internal clock.                                                            |  |  |  |  |

|     | 0/1                       | When set, the timer counts falling edges on the T1 pin.                                                                                       |  |  |  |  |

| 5   | M1                        | Timer 1 mode select bit 1. See table below.                                                                                                   |  |  |  |  |

| 4   | M0                        | Timer 1 mode select bit 0. See table below.                                                                                                   |  |  |  |  |

| NC  | 3.4                       | Gating control: When this bit is set, Timer/counter 0 is enabled only while the $\overline{INT0}$                                             |  |  |  |  |

| 3   | GATE                      | pin is high and the TR0 control bit is set. When cleared, the INT0 pin has no effect, and Timer 0 is enabled whenever TR0 control bit is set. |  |  |  |  |

| 2   | C/T                       | Timer or Counter Select: When clear, Timer 0 is incremented by the internal clock. When set, the timer counts falling edges on the T0 pin.    |  |  |  |  |

| 1   | M1                        | Timer 0 mode select bit 1. See table below.                                                                                                   |  |  |  |  |

| 0   | M0                        | Timer 0 mode select bit 0. See table below.                                                                                                   |  |  |  |  |

|     | M1, M0: Mode Select bits: |                                                                                                                                               |  |  |  |  |

| -  |    |                                                                                     |  |  |  |  |  |  |

|----|----|-------------------------------------------------------------------------------------|--|--|--|--|--|--|

| M1 | MO | MODE                                                                                |  |  |  |  |  |  |

| 0  | 0  | Mode 0: 13-bits timer/counter; THx 8 bits and TLx 5 bits which serve as pre-scalar. |  |  |  |  |  |  |

# nuvoTon

| 1 | P2.1 | XTAL1 clock input pin.              |

|---|------|-------------------------------------|

| 0 | P2.0 | XTAL2 or CLKOUT pin by alternative. |

Note: During power-on-reset, the port pins are tri-stated. After power-on-reset, the value of the port is set by CONFIG0.PRHI bit. The default setting for CONFIG0.PRHI =1 which the alternative function output is turned on upon reset. If CONFIG0.PRHI is set to 0, the user has to write a 1 to port SFR to turn on the alternative function output.

#### **AUX FUNCTION REGISTER 1**

| Bit: | 7           | 6   | 5   | 4     | 3    | 2     | 1    | 0           |

|------|-------------|-----|-----|-------|------|-------|------|-------------|

|      | EDF         | BOD | BOI | LPBOV | SRST | ADCEN | BUZE | -           |

| Mnem | onic: AUXR1 | l   |     |       |      | - m   | A    | ddress: A2h |

| BI  | NAME  | FUNCTION                                                                                                                                                                                                                                         |  |  |  |  |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     |       | Edge detect Interrupt Flag:                                                                                                                                                                                                                      |  |  |  |  |

| 7   | EDF   | 1: When any pin of port 1.0-1.2 that is enabled for the Edge Detect Interrupt function trigger (falling/rising edge trigger configurable). Must be cleared by software.                                                                          |  |  |  |  |

|     |       | Brown Out Disable:                                                                                                                                                                                                                               |  |  |  |  |

| 6   | BOD   | 0: Enable Brownout Detect function.                                                                                                                                                                                                              |  |  |  |  |

|     |       | 1: Disable Brownout Detect function and save power.                                                                                                                                                                                              |  |  |  |  |

|     |       | Brown Out Interrupt:                                                                                                                                                                                                                             |  |  |  |  |

| 5   | BOI   | 0: Disable Brownout Detect Interrupt function and it will cause chip reset when BOF is set.                                                                                                                                                      |  |  |  |  |

|     |       | 1: This prevents Brownout Detection from causing a chip reset and allows the Brownout Detect function to be used as an interrupt.                                                                                                                |  |  |  |  |

|     |       | Low Power Brown Out Detect control:                                                                                                                                                                                                              |  |  |  |  |

|     |       | 0: When BOD is enable, the Brown Out detect is always turned on by normal run<br>or Power-down mode.                                                                                                                                             |  |  |  |  |

| 4   | LPBOV | 1: When BOD is enable, the Brown Out detect circuit is turned on by Power-<br>down mode. This control can help save 15/16 of the Brownout circuit power<br>When uC is in Power-down mode, the BOD will enable internal RC OSC<br>(600KHz+/- 50%) |  |  |  |  |

| 3   | ODOT  | Software reset:                                                                                                                                                                                                                                  |  |  |  |  |

| 3   | SRST  | 1: reset the chip as if a hardware reset occurred.                                                                                                                                                                                               |  |  |  |  |

| 200 |       | 0: Disable ADC circuit.                                                                                                                                                                                                                          |  |  |  |  |

| 2   | ADCEN | 1: Enable ADC circuit.                                                                                                                                                                                                                           |  |  |  |  |

| 1   | ave   | Square-wave enable bit:                                                                                                                                                                                                                          |  |  |  |  |

| 1   | BUZE  | 0: Disable square wave output.                                                                                                                                                                                                                   |  |  |  |  |

|     | 2     | 1: The square wave is output to the BUZ (P1.0) pin.                                                                                                                                                                                              |  |  |  |  |

| 0   | - 70  | Reserved.                                                                                                                                                                                                                                        |  |  |  |  |

#### EDGE DETECT CONTROL REGISTER

| Bit: | 7          | 6        | 5      | 4     | 3      | 2     | 1      | 0           |

|------|------------|----------|--------|-------|--------|-------|--------|-------------|

|      | EDFILT.1   | EDFILT.0 | ED2TRG | ED2EN | ED1TRG | ED1EN | ED0TRG | ED0EN       |

| Mnem | onic: EDIC | 1        | 200    | 2     |        |       | Ac     | ldress: A3h |

# ηυνοτοη

| BIT          | NAME                           |                    |                          |               | FUNCTIO       | N           |             |             |  |  |

|--------------|--------------------------------|--------------------|--------------------------|---------------|---------------|-------------|-------------|-------------|--|--|

| 7            | EA                             | Global en          | able. Enable             | e/Disable all | interrupts.   |             |             |             |  |  |

| 6            | EADC                           | Enable A           | DC interrupt             | . Q           | 12 as         |             |             |             |  |  |

| 5            | EBO                            | Enable Br          | own Out int              | errupt.       | VID N         | 1.5         |             |             |  |  |

| 4            | -                              | Reserved           |                          |               | - SZ          | N.          |             |             |  |  |

| 3            | ET1                            | Enable Ti          | nable Timer 1 interrupt. |               |               |             |             |             |  |  |

| 2            | EX1                            | Enable ex          | ternal interr            | upt 1.        |               | Va. S       | 22          |             |  |  |

| 1            | ET0                            | Enable Ti          | mer 0 interru            | upt.          |               | -Un         | 0           |             |  |  |

| 0            | EX0                            | Enable ex          | ternal interr            | upt 0.        |               | Ŷ           | 2240        |             |  |  |

| PORT         | 0 OUTPUT                       | MODE 1             |                          |               |               |             |             |             |  |  |

| Bit:         | 7                              | 6                  | 5                        | 4             | 3             | 2           | 1 20        | 0           |  |  |

|              | P0M1.7                         | P0M1.6             | P0M1.5                   | P0M1.4        | P0M1.3        | P0M1.2      | P0M1.1      | P0M1.0      |  |  |

| Mnem         | onic: P0M1                     |                    |                          |               |               |             |             | Address: B  |  |  |

| BIT          | NAME                           |                    |                          |               | FUNCTIO       | N           |             | (Se)        |  |  |

| 7-0          | P0M1.[7:0]                     | To contro          | I the output             | configuratio  | on of P0 bits | [7:0]       |             | 20          |  |  |

| PORT         |                                | MODE 2             |                          |               |               |             |             |             |  |  |

| Bit:         | 7                              | 6                  | 5                        | 4             | 3             | 2           | 1           | 0           |  |  |

|              | P0M2.7                         | P0M2.6             | P0M2.5                   | P0M2.4        | P0M2.3        | P0M2.2      | P0M2.1      | P0M2.0      |  |  |

| Mnem         | onic: P0M2                     |                    |                          |               |               |             |             | Address: B  |  |  |

| BIT          | NAME                           |                    |                          |               | FUNCTIO       | N           |             |             |  |  |

| 7-0          | P0M2.[7:0]                     | To contro          | I the output             | configuratio  | on of P0 bits |             |             |             |  |  |

|              |                                |                    | <u> </u>                 |               |               |             |             |             |  |  |

| Bit:         | 7                              |                    | 5                        | 4             | 3             | 2           | 1           | 0           |  |  |

| Dit.         | ,<br>P1M1.7                    | 0<br>P1M1.6        | -                        | P1M1.4        | 9<br>P1M1.3   | P1M1.2      | P1M1.1      | P1M1.0      |  |  |

| Mnom         | onic: P1M1                     | 1 1111.0           |                          |               | 1 1111.0      | 1 11011.2   |             | Address: B  |  |  |

| -            |                                |                    |                          |               | EUNCTIO       |             |             |             |  |  |

| BIT          |                                |                    | I the output             | configuration | FUNCTIO       |             |             |             |  |  |

| 70           |                                |                    | i the output             | coniguratio   |               | 17.01       |             |             |  |  |

| 7-0          | P1M1.[7:0]                     |                    | •                        | -             |               |             |             |             |  |  |

| 500          |                                |                    | •                        |               |               |             |             |             |  |  |

| 200          | 1 OUTPUT                       | <b>MODE 2</b><br>6 | 5                        | 4             | 3             | 2           | 1           | 0           |  |  |

| PORT         |                                | MODE 2             |                          | 4<br>P1M2.4   |               |             | 1<br>P1M2.1 | 0<br>P1M2.0 |  |  |

| PORT<br>Bit: | 1 OUTPUT                       | <b>MODE 2</b><br>6 |                          |               | 3             | 2           | P1M2.1      | 1           |  |  |

| PORT<br>Bit: | <b>1 OUTPUT</b><br>7<br>P1M2.7 | <b>MODE 2</b><br>6 |                          |               | 3             | 2<br>P1M2.2 | P1M2.1      | P1M2.0      |  |  |

# ηυνοτοη

| 7~0  | PWM1.[7:0] PWM 1 Low Bits Register. |                                                             |                                                                                                                                                                                                                                                                                    |                        |          |                 |                |              |  |

|------|-------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|-----------------|----------------|--------------|--|

| PWM  |                                     |                                                             | 1                                                                                                                                                                                                                                                                                  |                        | 3        |                 |                |              |  |

| Bit: | 7                                   | 6                                                           | 5                                                                                                                                                                                                                                                                                  | 4                      | 3        | 2               | 1              | 0            |  |

|      | PWMRUN                              | Load                                                        | PWMF                                                                                                                                                                                                                                                                               | CLRPWM                 | 1/2      | N - 34          | PWM1I          | PWM0I        |  |

| Inem | onic: PWMC                          | ON1                                                         |                                                                                                                                                                                                                                                                                    |                        | ×.       | S W             | ŀ              | Address: DCh |  |

| BIT  | NAME                                |                                                             |                                                                                                                                                                                                                                                                                    |                        | FUNCT    | ION             | Xs.            |              |  |

| 7    | PWMRUN                              |                                                             | /M is not ru<br>/M counter                                                                                                                                                                                                                                                         | inning.<br>is running. |          | NG3             | 10             |              |  |

| 6    | Load                                | Compa<br>1: The PV                                          | <ul> <li>D: The registers value of PWMP and PWMn are never loaded to counter and Comparator registers.</li> <li>I: The PWMP and PWMn registers load value to counter and compare registers at the counter underflow. This bit is auto cleared by hardware at next clock</li> </ul> |                        |          |                 |                |              |  |

| 5    | PWMF                                | 0: The 10-<br>1: The 10<br>PWM inte                         | PWM underflow flag:<br>0: The 10-bit counter down count is not underflow.<br>1: The 10-bit counter down count is underflow. (PWM interrupt is requested if<br>PWM interrupt is enabled).<br>This bit is Software clear.                                                            |                        |          |                 |                |              |  |

| 4    | CLRPWM                              | 1: Clear 1                                                  | 0-bit PWM                                                                                                                                                                                                                                                                          | counter to 00          | 00H. Thi | s bit is auto c | leared by hard | lware.       |  |

| 3    | PWM3I                               |                                                             | out is non-i<br>output is in                                                                                                                                                                                                                                                       |                        |          |                 |                |              |  |

| 2    | PWM2I                               | ••••                                                        | out is non-i<br>output is in                                                                                                                                                                                                                                                       |                        |          |                 |                |              |  |

| 1    | PWM1I                               |                                                             | out is non-i<br>output is in                                                                                                                                                                                                                                                       |                        |          |                 |                |              |  |

| 0    | PWM0I                               | 0: PWM0 out is non-inverted.<br>1: PWM0 output is inverted. |                                                                                                                                                                                                                                                                                    |                        |          |                 |                |              |  |

| Bit: | 7          | 6      | 5      | 4      | 3      | 2      | 1      | 0          |

|------|------------|--------|--------|--------|--------|--------|--------|------------|

|      | PWM2.7     | PWM2.6 | PWM2.5 | PWM2.4 | PWM2.3 | PWM2.2 | PWM2.1 | PWM2.0     |

| Mnem | onic: PWM2 | 2      |        |        |        |        | Ac     | dress: DDh |

| BIT |            | FUNCTION                 | Address. DDi |

|-----|------------|--------------------------|--------------|

| 7~0 | PWM2.[7:0] | PWM 2 Low Bits Register. |              |

|     | 20         | Sh .                     |              |

|     |            |                          |              |

|     |            |                          |              |

|     |            |                          |              |

|     |            |                          |              |

|     |            |                          |              |

|     |            | -32-                     |              |

| Brake | Condition  | Table <sup>.</sup> |

|-------|------------|--------------------|

| Diane | Contaition | I abie.            |

| BPEN | BKCH | BRAKE CONDITION                                                                                                                                                                                                                                                                                                                                                                          |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | Brake On (software brake and keeping brake).<br>Software brake condition. When active (BPEN=BKCH=0, and BKEN=1), PWM<br>output follows PWMnB setting. This brake has no effect on PWMRUN bit,<br>therefore, internal PWM generator continues to run. When the brake is released,<br>the state of PWM output depends on the current state of PWM generator output<br>during the release.  |

| 0    | 1    | Brake On;<br>This condition is when BKEN set (BKEN=1) and PWM is not running<br>(PWMRUN=0), the PWMn output follows PWMnB setting. When the brake is<br>released (by disabling BKEN = 0), the PWMn output resumes to the state when<br>PWM generator stop running prior to enabling the brake.<br>Brake Off;<br>This condition is when PWM is running (PWMRUN=1).                        |

| 1    | 0    | Brake On, when Brake Pin asserted.<br>External pin brake condition. When active (by external pin), PWM output follows<br>PWMnB setting, PWMRUN will be cleared by hardware, and BKF flag will be set.<br>When the brake is released (by de-asserting the external pin and disabling<br>BKEN = 0), the PWM output resumes to the state of the PWM generator output<br>prior to the brake. |

| 1    | 1    | This is another brake condition (by Brake Pin) which causes BKF to be set, but PWM generator continues to run. The PWM output does not follow PWMnB, instead it output continuously as per normal.                                                                                                                                                                                       |

#### ACCUMULATOR

| Bit: | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

|      | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

Mnemonic: ACC

Address: E0h

| BIT | NAME      | FUNCTION                                               |

|-----|-----------|--------------------------------------------------------|

| 7-0 | ACC.[7:0] | The A or ACC register is the standard 8052 accumulator |

#### ADC CONTROL REGISTER

| Bit: | 7     | 6     | 5     | 4    | 3    | 2     | 1     | 0     |

|------|-------|-------|-------|------|------|-------|-------|-------|

|      | ADC.1 | ADC.0 | ADCEX | ADCI | ADCS | RCCLK | AADR1 | AADR0 |

Mnemonic: ADCCON

Address: E1h

# nuvoTon

| BIT | NAME | FUNCTION                                                                       |

|-----|------|--------------------------------------------------------------------------------|

| 7   | PED  | 1: To set interrupt priority of Edge Detect is higher priority level.          |

| 6   | PPWM | 1: To set interrupt priority of PWM underflow is higher priority level.        |

| 5   | PBK  | 1: To set interrupt priority of PWM's external brake is higher priority level. |

| 4   | PWDI | 1: To set interrupt priority of Watchdog is higher priority level.             |

| 3-0 | -    | Reserved.                                                                      |

#### **BUZZER CONTROL REGISTER**

| Bit:             | 7 | 6 | 5        | 4        | 3        | 2        | 1 Cs     | 0          |

|------------------|---|---|----------|----------|----------|----------|----------|------------|

|                  | - | - | BUZDIV.5 | BUZDIV.4 | BUZDIV.3 | BUZDIV.2 | BUZDIV.1 | BUZDIV.0   |

| Mnemonic: BUZCON |   |   |          |          |          |          | Ac       | dress: F9h |

| BIT | NAME   | FUNCTION                                                                                                                                                                                                                                                                                             |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6 | -      | Reserved.                                                                                                                                                                                                                                                                                            |

| 5-0 | BUZDIV | Buzzer division select bits:<br>These bits are division selector. User may configure these bits to further divide<br>the cpu clock in order to generate the desired buzzer output frequency.<br>The following shows the equation for the buzzer output rate;<br>Fbuz = Fcpu x 1/[(256)x(BUZDIV + 1)] |

#### **INSTRUCTION SET** 9.

The W79E8213 series execute all the instructions of the standard 8052 family. The operations of these instructions, as well as their effects on flag and status bits, are exactly the same. However, the timing of these instructions is different in two ways. Firstly, the machine cycle is four clock periods, while the standard-8051/52 machine cycle is twelve clock periods. Secondly, it can fetch only once per machine cycle (i.e., four clocks per fetch), while the standard 8051/52 can fetch twice per machine cycle (i.e., six clocks per fetch).

The timing differences create an advantage for the W79E8213 series. There is only one fetch per machine cycle, so the number of machine cycles is usually equal to the number of operands in the instruction. (Jumps and calls do require an additional cycle to calculate the new address.) As a result, the W79E8213 series reduces the number of dummy fetches and wasted cycles, and therefore improves overall efficiency, compared to the standard 8051/52.

| Op-code        | HEX Code | Bytes | W79E8213<br>series<br>Machine<br>Cycle | W79E8213<br>series<br>Clock<br>cycles | 8032<br>Clock<br>cycles | W79E8213<br>series v.s.<br>8032 Speed<br>Ratio |

|----------------|----------|-------|----------------------------------------|---------------------------------------|-------------------------|------------------------------------------------|

| NOP            | 00       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, R0      | 28       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, R1      | 29       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, R2      | 2A       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, R3      | 2B       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, R4      | 2C       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, R5      | 2D       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, R6      | 2E       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, R7      | 2F       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, @R0     | 26       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, @R1     | 27       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADD A, direct  | 25       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| ADD A, #data   | 24       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| ADDC A, R0     | 38       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, R1     | 39       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, R2     | 3A       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, R3     | 3B       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, R4     | 3C       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, R5     | 3D       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, R6     | 3E       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, R7     | 3F       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, @R0    | 36       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, @R1    | 37       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| ADDC A, direct | 35       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

#### INSTRUCTION SET, continued

| Op-code        | HEX Code | Bytes | W79E8213<br>series<br>Machine<br>Cycle | W79E8213<br>series<br>Clock<br>cycles | 8032<br>Clock<br>cycles | W79E8213<br>series v.s.<br>8032 Speed<br>Ratio |

|----------------|----------|-------|----------------------------------------|---------------------------------------|-------------------------|------------------------------------------------|

| ADDC A, #data  | 34       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| SUBB A, R0     | 98       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R1     | 99       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R2     | 9A       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R3     | 9B       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R4     | 9C       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R5     | 9D       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R6     | 9E       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R7     | 9F       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, @R0    | 96       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, @R1    | 97       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, direct | 95       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| SUBB A, #data  | 94       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| INC A          | 04       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R0         | 08       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R1         | 09       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R2         | 0A       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R3         | 0B       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R4         | 0C       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R5         | 0D       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R6         | 0E       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R7         | 0F       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC @R0        | 06       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC @R1        | 07       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC direct     | 05       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| INC DPTR       | A3       | 1     | 2                                      | 8                                     | 24                      | 3                                              |

| DEC A          | 14       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R0         | 18       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R1         | 19       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R2         | 1A       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R3         | 1B       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R4         | 1C       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R5         | 1D       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R6         | IE S     | 1     | 1                                      | 4                                     | 12                      | 3                                              |

#### **10. POWER MANAGEMENT**

The W79E8213 series has several features that help the user to control the power consumption of the device. These modes are discussed in the next two sections.

#### 10.1 Idle Mode

The user can put the device into idle mode by writing 1 to the bit PCON.0. The instruction that sets the idle bit is the last instruction that will be executed before the device goes into Idle Mode. In the Idle mode, the clock to the CPU is halted, but not to the Interrupt, Timer, PWM and Watchdog timer blocks. This forces the CPU state to be frozen; the Program counter, the Stack Pointer, the Program Status Word, the Accumulator and the other registers hold their contents. The port pins hold the logical states they had at the time Idle was activated. The Idle mode can be terminated in two ways. Since the interrupt controller is still active, the activation of any enabled interrupt can wake up the processor. This will automatically clear the Idle bit, terminate the Idle mode, and the Interrupt Service Routine (ISR) will be executed. After the ISR, execution of the program will continue from the instruction which put the device into Idle Mode.

The Idle mode can also be exited by activating the reset. The device can put into reset either by applying a low on the external /RST pin, a Power on reset condition or a Watchdog timer reset. The external reset pin has to be held low for at least two machine cycles i.e. 8 clock periods to be recognized as a valid reset. In the reset condition the program counter is reset to 0000h and all the SFRs are set to the reset condition. Since the clock is already running there is no delay and execution starts immediately. In the Idle mode, the Watchdog timer continues to run, and if enabled, a time-out will cause a watchdog timer interrupt which will wake up the device. The software must reset the Watchdog timer in order to preempt the reset which will occur after 512 clock periods of the time-out. When the W79E8213 series are exiting from an Idle Mode with a reset, the instruction following the one which put the device into Idle Mode is not executed. So there is no danger of unexpected writes.

#### 10.2 Power-down Mode

The device can be put into Power-down mode by writing 1 to bit PCON.1. The instruction that does this will be the last instruction to be executed before the device goes into Power-down mode. In the Power-down mode, all the clocks are stopped and the device comes to a halt. All activity is completely stopped and the power consumption is reduced to the lowest possible value. The port pins output the values held by their respective SFRs.

The W79E8213 series will exit the Power-down mode with a reset or by an external interrupt pin enabled as level detected. An external reset can be used to exit the Power down state. The low on /RST pin terminates the Power-down mode, and restarts the clock. The program execution will restart from 0000h. In the Power-down mode, the clock is stopped, so the Watchdog timer cannot be used to provide the reset to exit Power-down mode when its clock source is external OSC or crystal.

The sources that can wake up from the power-down mode are external interrupts, brownout reset (BOR) and ADC. Note that for ADC waking up from powerdown, the device need to run on internal rc and software perform start ADC prior to powerdown.

The W79E8213 series can be waken up from the Power-down mode by forcing an external interrupt pin activation, provided the corresponding interrupt is enabled, while the global enable (EA) bit is set. If these conditions are met, then either a low-level or a falling-edge at external interrupt pin will re-start the oscillator. The device will then execute the interrupt service routine for the corresponding external interrupt. After the interrupt service routine is completed, the program execution returns to the instruction after one which put the device into Power-down mode and continues from there. During Power-down mode, if AUXR1.LPBOV = 1 and AUXR1.BOD = 0, the internal RC clock will be enabled and hence save power.

### **12. INTERRUPTS**

The W79E8213 series have four priority level interrupts structure with 10 interrupt sources. Each of the interrupt sources has an individual priority bit, flag, interrupt vector and enable bit. In addition, the interrupts can be globally enabled or disabled.

### **12.1 Interrupt Sources**

The External Interrupts INT0 and INT1 can be either edge triggered or level triggered, programmable through bits IT0 and IT1. The bits IE0 and IE1 in the TCON register are the flags which are checked to generate the interrupt. In the edge triggered mode, the INTx inputs are sampled in every machine cycle. If the sample is high in one cycle and low in the next, then a high to low transition is detected and the interrupts request flag IEx in TCON is set. The flag bit requests the interrupt. Since the external interrupts are sampled every machine cycle, they have to be held high or low for at least one complete machine cycle. The IEx flag is automatically cleared when the service routine is called. If the level triggered mode is selected, then the requesting source has to hold the pin low till the interrupt is serviced. The IEx flag will not be cleared by the hardware on entering the service routine. If the interrupt continues to be held low even after the service routine is completed, then the processor may acknowledge another interrupt request from the same source.

The Timer 0 and 1 Interrupts are generated by the TF0 and TF1 flags. These flags are set by the overflow in the Timer 0 and Timer 1. The TF0 and TF1 flags are automatically cleared by the hardware when the timer interrupt is serviced.

The Watchdog timer can be used as a system monitor or a simple timer. In either case, when the timeout count is reached, the Watchdog Timer interrupt flag WDIF (WDCON.3) is set. If the interrupt is enabled by the enable bit EIE.4, then an interrupt will occur.

PWM interrupt is generated when its' 10-bit down counter underflows. PWMF flag is set and PWM interrupt is generated if enabled. PWMF is set by hardware and can only be cleared by software. Alternatively, PWM function can also generate interrupt by BKF flag, after external brake pin has brake occurred. This bit will be cleared by software.

The ADC can generate interrupt after finished ADC converter. There is one interrupt source, which is obtained by the ADCI bit in the ADCCON SFR. This bit is not automatically cleared by the hardware, and the user will have to clear this bit using software.

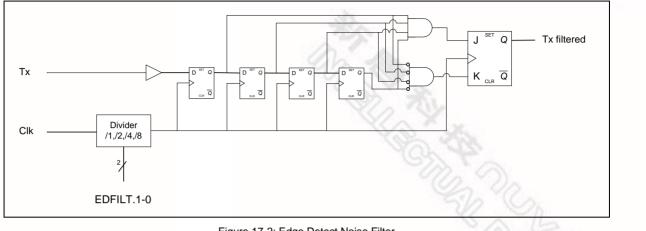

Edge detect interrupt is generated when any of the keypad connected to P1.0-P1.2 pins is pressed. Each edge detect interrupt can be individually enabled/disabled. User will have to software clear the flag bit. The ED pins have edge type and filter type control, configurable through EDIC SFR.

Brownout detect can cause brownout flag, BOF, to be asserted if power voltage drop below brownout voltage level. Interrupt will occur if BOI (AUXR1.5), EBO (IE.5) and global interrupt enable are set.

All the bits that generate interrupts can be set or reset by software, and thereby software initiated interrupts can be generated. Each of the individual interrupts can be enabled or disabled by setting or clearing a bit in the IE SFR. IE also has a global enable/disable bit EA, which can be cleared to disable all interrupts.

The interrupt flags are sampled every machine cycle. In the same machine cycle, the sampled interrupts are polled and their priority is resolved. If certain conditions are met then the hardware will execute an internally generated LCALL instruction which will vector the process to the appropriate interrupt vector address. The conditions for generating the LCALL are;

1. An interrupt of equal or higher priority is not currently being serviced.

2. The current polling cycle is the last machine cycle of the instruction currently being execute.

3. The current instruction does not involve a write to IE, EIE, IP0, IP0H, IP1 or IPH1 registers and is not a RETI.

If any of these conditions are not met, then the LCALL will not be generated. The polling cycle is repeated every machine cycle, with the interrupts sampled in the same machine cycle. If an interrupt

## nuvoTon

flag is active in one cycle but not responded to, and is not active when the above conditions are met, the denied interrupt will not be serviced. This means that active interrupts are not remembered; every polling cycle is new.

The processor responds to a valid interrupt by executing an LCALL instruction to the appropriate service routine. This may or may not clear the flag which caused the interrupt. In case of Timer interrupts, the TF0 or TF1 flags are cleared by hardware whenever the processor vectors to the appropriate timer service routine. In case of external interrupt, INT0 and INT1, the flags are cleared only if they are edge triggered. In case of Serial interrupts, the flags are not cleared by hardware. The Watchdog timer interrupt flag WDIF has to be cleared by software. The hardware LCALL behaves exactly like the software LCALL instruction. This instruction saves the Program Counter contents onto the Stack, but does not save the Program Status Word PSW. The PC is reloaded with the vector address of that interrupt which caused the LCALL. These address of vector for the different sources are as following:

| SOURCE                  | VECTOR<br>ADDRESS                    | SOURCE                | VECTOR<br>ADDRESS |  |  |

|-------------------------|--------------------------------------|-----------------------|-------------------|--|--|

| External Interrupt 0    | External Interrupt 0 0003h Timer 0 O |                       | 000Bh             |  |  |

| External Interrupt 1    | 0013h                                | Timer 1 Overflow      | 001Bh             |  |  |

| -                       | 0023h                                | Brownout Interrupt    | 002Bh             |  |  |

| -                       | 0033h                                | Edge Detect Interrupt | 003Bh             |  |  |

| -                       | 0043h                                | -                     | 004Bh             |  |  |

| Watchdog Timer          | 0053h                                | ADC Interrupt         | 005Bh             |  |  |

| -                       | 0063h                                | PWM Brake Interrupt   | 0073h             |  |  |

| PWM Underflow Interrupt | 006Bh                                | -                     | 007Bh             |  |  |

#### VECTOR LOCATIONS FOR INTERRUPT SOURCES

Table 12-1: Vector locations for interrupt sources