Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                  |

| Core Processor             | 8051                                                                                    |

| Core Size                  | 8-Bit                                                                                   |

| Speed                      | 20MHz                                                                                   |

| Connectivity               | -                                                                                       |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT                                         |

| Number of I/O              | 18                                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | 128 x 8                                                                                 |

| RAM Size                   | 128 x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x10b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                                          |

| Supplier Device Package    | -                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w79e8213asg |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3. PARTS INFORMATION LIST

#### 3.1 Lead Free (RoHS) Parts information list

| PART NO.     | EPROM<br>FLASH SIZE | RAM  | NVM FLASH<br>EPROM | INTERNAL RC <sup>1</sup><br>OSCILLATOR<br>ACCURACY | PACKAGE    |

|--------------|---------------------|------|--------------------|----------------------------------------------------|------------|

| W79E8213AKG  | 4KB                 | 128B | 128B               | ±30%                                               | DIP-20 Pin |

| W79E8213ASG  | 4KB                 | 128B | 128B               | ±30%                                               | SOP-20 Pin |

| W79E8213RAKG | 4KB                 | 128B | 128B               | ±2%                                                | DIP-20 Pin |

| W79E8213RASG | 4KB                 | 128B | 128B               | ±2%                                                | SOP-20 Pin |

Note: 1. Test conditions are  $V_{DD}$  = 3.3V, TA = 25°C

Table 3-1: Lead Free (RoHS) Parts information list

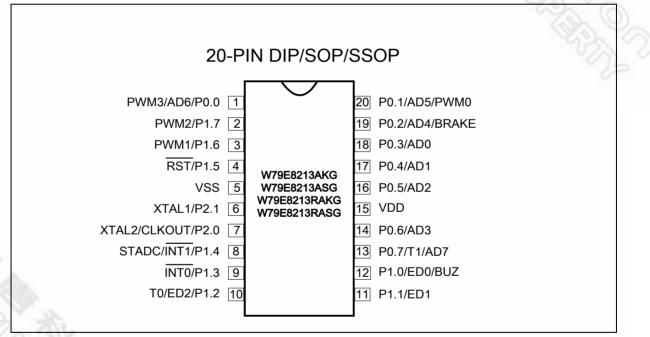

### 4. PIN CONFIGURATION

Figure 4-1: Pin Configuration

| PWM3.0<br>dress: DE |

|---------------------|

|                     |

| 0                   |

| 0                   |

| 0                   |

| 0                   |

|                     |

| PWM0B               |

| dress: DF           |

| 0.                  |

| ~0                  |

| 201                 |

| Roy                 |

| 00                  |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

| Brake | Condition  | Table <sup>.</sup> |

|-------|------------|--------------------|

| Diane | Contaition | I abie.            |

| BPEN | BKCH | BRAKE CONDITION                                                                                                                                                                                                                                                                                                                                                                          |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | Brake On (software brake and keeping brake).<br>Software brake condition. When active (BPEN=BKCH=0, and BKEN=1), PWM<br>output follows PWMnB setting. This brake has no effect on PWMRUN bit,<br>therefore, internal PWM generator continues to run. When the brake is released,<br>the state of PWM output depends on the current state of PWM generator output<br>during the release.  |

| 0    | 1    | Brake On;<br>This condition is when BKEN set (BKEN=1) and PWM is not running<br>(PWMRUN=0), the PWMn output follows PWMnB setting. When the brake is<br>released (by disabling BKEN = 0), the PWMn output resumes to the state when<br>PWM generator stop running prior to enabling the brake.<br>Brake Off;<br>This condition is when PWM is running (PWMRUN=1).                        |

| 1    | 0    | Brake On, when Brake Pin asserted.<br>External pin brake condition. When active (by external pin), PWM output follows<br>PWMnB setting, PWMRUN will be cleared by hardware, and BKF flag will be set.<br>When the brake is released (by de-asserting the external pin and disabling<br>BKEN = 0), the PWM output resumes to the state of the PWM generator output<br>prior to the brake. |

| 1    | 1    | This is another brake condition (by Brake Pin) which causes BKF to be set, but<br>PWM generator continues to run. The PWM output does not follow PWMnB,<br>instead it output continuously as per normal.                                                                                                                                                                                 |

#### ACCUMULATOR

| Bit: | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------|-------|-------|-------|-------|-------|-------|-------|-------|

|      | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

Mnemonic: ACC

Address: E0h

| BIT | NAME      | FUNCTION                                               |

|-----|-----------|--------------------------------------------------------|

| 7-0 | ACC.[7:0] | The A or ACC register is the standard 8052 accumulator |

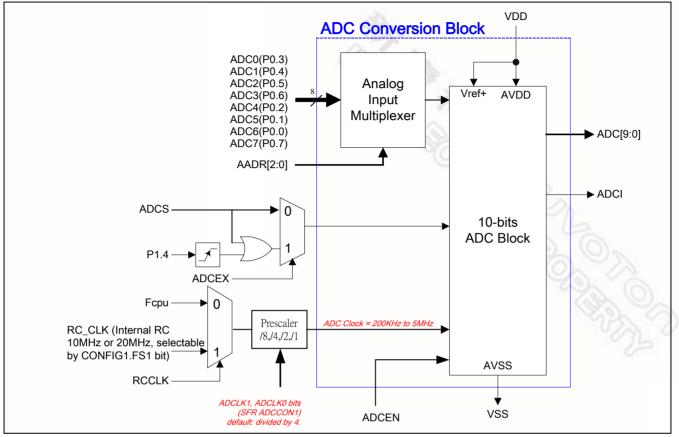

#### ADC CONTROL REGISTER

| Bit: | 7     | 6     | 5     | 4    | 3    | 2     | 1     | 0     |

|------|-------|-------|-------|------|------|-------|-------|-------|

|      | ADC.1 | ADC.0 | ADCEX | ADCI | ADCS | RCCLK | AADR1 | AADR0 |

Mnemonic: ADCCON

Address: E1h

# nuvoTon

| ·   | 1    |       | 1                            |                                                                                                                                                                                                                                                                    |  |  |  |  |

|-----|------|-------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIT | N/   | AME   |                              | FUNCTION                                                                                                                                                                                                                                                           |  |  |  |  |

| 7-6 | ADC  | 0.1-0 | 2 LS                         | B of 10-bit A/D conversion result.                                                                                                                                                                                                                                 |  |  |  |  |

| 5   | ADC  | EX    | 0: C<br>1: C                 | <ul> <li>Enable STADC-triggered conversion</li> <li>D: Conversion can only be started by software (i.e., by setting ADCS).</li> <li>1: Conversion can be started by software or by a rising edge on STADC (pin P1.4).</li> </ul>                                   |  |  |  |  |

| 4   | ADC  | :     | ADC<br>This<br>ADC           | C Interrupt flag:<br>flag is set when the result of an A/D conversion is ready. This generates an<br>C interrupt, if it is enabled. The flag may be cleared by the ISR. While this flag<br>the ADC cannot start a new conversion. ADCI can not be set by software. |  |  |  |  |

| 3   | ADC  | s     | by S<br>rese                 | <ul> <li>is cleared and ADCS is set at the same time, a new A/D conversion may start on the same channel.</li> <li>2. Software clearing of ADCS will abort conversion in progress.</li> </ul>                                                                      |  |  |  |  |

| 2   | RCC  | PR1   | 1: T<br>used<br><i>Not</i> e | <ol> <li>This bit can only be set/cleared when ADCEN=0.</li> <li>The ADC clock source will goes through pre-scalar of /1, /2, /4 or /8 selectable by ADCLK bits (SFR ADCCON1.6-7).</li> <li>ADC input select. See table below.</li> </ol>                          |  |  |  |  |

| 0   | AAD  | R0    | <u> </u>                     | ADC input select. See table below. ADCI and ADCS control the ADC conversion as below:                                                                                                                                                                              |  |  |  |  |

|     | IJCI | AD    | CS                           | ADC STATUS                                                                                                                                                                                                                                                         |  |  |  |  |

| 8   | 0    | C     | )                            | ADC not busy; A conversion can be started.                                                                                                                                                                                                                         |  |  |  |  |

| -   |      |       |                              |                                                                                                                                                                                                                                                                    |  |  |  |  |

#### The ADCI and ADCS control the ADC conversion as below:

| ADCI | ADCS | ADC STATUS                                                         |

|------|------|--------------------------------------------------------------------|

| 0    | 0    | ADC not busy; A conversion can be started.                         |

| 0    | 1    | ADC busy; Start of a new conversion is blocked.                    |

| 10   | 0    | Conversion completed; Start of a new conversion requires ADCI = 0. |

| 1    | 10   | This is an internal temporary state that user can ignore it.       |

# nuvoTon

| BIT | NAME | FUNCTION                                                                       |  |  |  |

|-----|------|--------------------------------------------------------------------------------|--|--|--|

| 7   | PED  | 1: To set interrupt priority of Edge Detect is higher priority level.          |  |  |  |

| 6   | PPWM | I: To set interrupt priority of PWM underflow is higher priority level.        |  |  |  |

| 5   | PBK  | 1: To set interrupt priority of PWM's external brake is higher priority level. |  |  |  |

| 4   | PWDI | 1: To set interrupt priority of Watchdog is higher priority level.             |  |  |  |

| 3-0 | -    | Reserved.                                                                      |  |  |  |

#### **BUZZER CONTROL REGISTER**

| Bit:             | 7 | 6 | 5        | 4        | 3        | 2        | 1 Cs     | 0          |

|------------------|---|---|----------|----------|----------|----------|----------|------------|

|                  | - | - | BUZDIV.5 | BUZDIV.4 | BUZDIV.3 | BUZDIV.2 | BUZDIV.1 | BUZDIV.0   |

| Mnemonic: BUZCON |   |   |          |          |          |          | Ac       | dress: F9h |

| BIT | NAME   | FUNCTION                                                                                                                                                                                                                                                                                             |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-6 | -      | Reserved.                                                                                                                                                                                                                                                                                            |

| 5-0 | BUZDIV | Buzzer division select bits:<br>These bits are division selector. User may configure these bits to further divide<br>the cpu clock in order to generate the desired buzzer output frequency.<br>The following shows the equation for the buzzer output rate;<br>Fbuz = Fcpu x 1/[(256)x(BUZDIV + 1)] |

#### INSTRUCTION SET, continued

| Op-code        | HEX Code | Bytes | W79E8213<br>series<br>Machine<br>Cycle | W79E8213<br>series<br>Clock<br>cycles | 8032<br>Clock<br>cycles | W79E8213<br>series v.s.<br>8032 Speec<br>Ratio |

|----------------|----------|-------|----------------------------------------|---------------------------------------|-------------------------|------------------------------------------------|

| ADDC A, #data  | 34       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| SUBB A, R0     | 98       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R1     | 99       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R2     | 9A       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R3     | 9B       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R4     | 9C       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R5     | 9D       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R6     | 9E       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, R7     | 9F       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, @R0    | 96       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, @R1    | 97       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| SUBB A, direct | 95       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| SUBB A, #data  | 94       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| INC A          | 04       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R0         | 08       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R1         | 09       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R2         | 0A       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R3         | 0B       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R4         | 0C       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R5         | 0D       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R6         | 0E       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC R7         | 0F       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC @R0        | 06       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC @R1        | 07       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| INC direct     | 05       | 2     | 2                                      | 8                                     | 12                      | 1.5                                            |

| INC DPTR       | A3       | 1     | 2                                      | 8                                     | 24                      | 3                                              |

| DEC A          | 14       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R0         | 18       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R1         | 19       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R2         | 1A       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R3         | 1B       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R4         | 1C       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R5         | 1D       | 1     | 1                                      | 4                                     | 12                      | 3                                              |

| DEC R6         | 1E S     | 1     | 1                                      | 4                                     | 12                      | 3                                              |

#### INSTRUCTION SET, continued

| Op-code            | HEX Code | Bytes | W79E8213<br>series<br>Machine<br>Cycle | W79E8213<br>series<br>Clock<br>cycles | 8032<br>Clock<br>cycles | W79E8213<br>series v.s 8032<br>Speed Ratio |

|--------------------|----------|-------|----------------------------------------|---------------------------------------|-------------------------|--------------------------------------------|

| MOV direct, R2     | 8A       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

| MOV direct, R3     | 8B       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

| MOV direct, R4     | 8C       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

| MOV direct, R5     | 8D       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

| MOV direct, R6     | 8E       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

| MOV direct, R7     | 8F       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

| MOV direct, @R0    | 86       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

| MOV direct, @R1    | 87       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

| MOV direct, direct | 85       | 3     | 3                                      | 12                                    | 24                      | 2                                          |

| MOV direct, #data  | 75       | 3     | 3                                      | 12                                    | 24                      | 2                                          |

| MOV DPTR, #data 16 | 90       | 3     | 3                                      | 12                                    | 24                      | 2                                          |

| MOVC A, @A+DPTR    | 93       | 1     | 2                                      | 8                                     | 24                      | 3                                          |

| MOVC A, @A+PC      | 83       | 1     | 2                                      | 8                                     | 24                      | 3                                          |

| MOVX A, @R0        | E2       | 1     | 2 - 9                                  | 8 - 36                                | 24                      | 3 - 0.66                                   |

| MOVX A, @R1        | E3       | 1     | 2 - 9                                  | 8 - 36                                | 24                      | 3 - 0.66                                   |

| MOVX A, @DPTR      | E0       | 1     | 2 - 9                                  | 8 - 36                                | 24                      | 3 - 0.66                                   |

| MOVX @R0, A        | F2       | 1     | 2 - 9                                  | 8 - 36                                | 24                      | 3 - 0.66                                   |

| MOVX @R1, A        | F3       | 1     | 2 - 9                                  | 8 - 36                                | 24                      | 3 - 0.66                                   |

| MOVX @DPTR, A      | F0       | 1     | 2 - 9                                  | 8 - 36                                | 24                      | 3 - 0.66                                   |

| PUSH direct        | C0       | 2     | 2                                      | 8                                     | 24                      | 3                                          |

| POP direct         | D0       | 2     | 2                                      | 8                                     | 24                      | 3                                          |

| XCH A, R0          | C8       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, R1          | C9       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, R2          | CA       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, R3          | СВ       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, R4          | CC       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, R5          | CD       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, R6          | CE       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, R7          | CF       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, @R0         | C6       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, @R1         | C7       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCHD A, @R0        | D6       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCHD A, @R1        | D7       | 1     | 1                                      | 4                                     | 12                      | 3                                          |

| XCH A, direct      | C5       | 2     | 2                                      | 8                                     | 12                      | 1.5                                        |

## nuvoTon

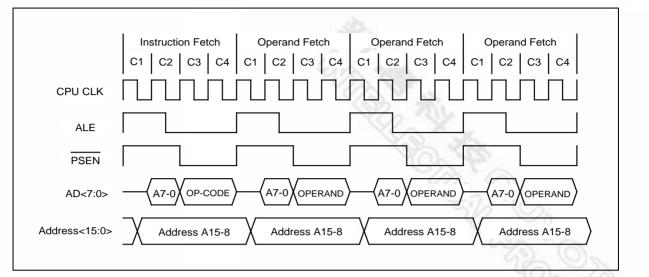

Figure 9-4: Four Cycles Instruction Timing

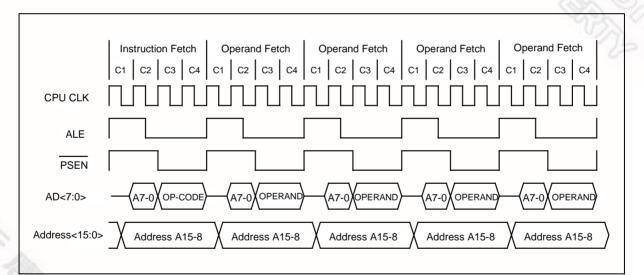

Figure 9-5: Five Cycles Instruction Timing

# nuvoTon

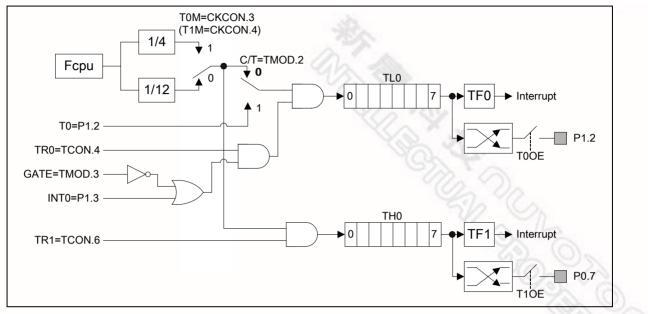

Figure 13-4: Timer/Counter Mode 3

#### **14. NVM MEMORY**

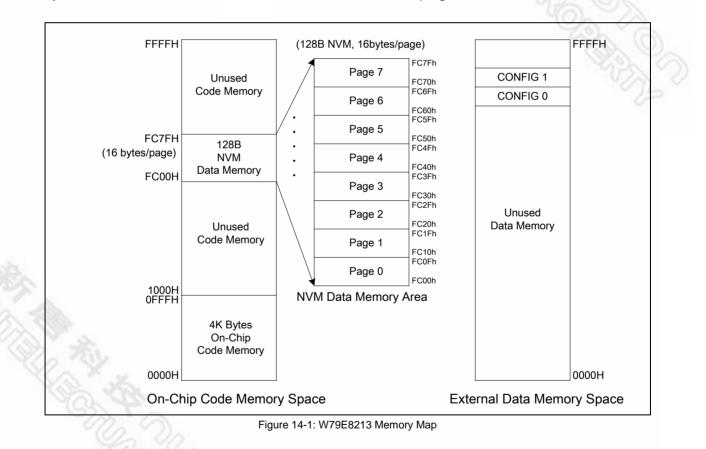

The W79E8213 series have NVM data memory of 128 bytes for customer's data store used. The NVM data memory has 8 pages area and each page of 16 bytes.

The NVM memory can be read/write by customer program to access. Read NVM data is by MOVC A,@A+DPTR instruction, and write data is by SFR of NVMADDRL, NVMDATA and NVMCON. Before write data to NVM memory, the page must be erased by providing page address on NVMADDRL, which address of On-Chip Code Memory space will decode, then set EER of NVMCON.7. This will automatically hold fetch program code and PC Counter, and execute page erase. After finished, this bit will be cleared by hardware. The erase time is ~ 5ms.

For writing data to NVM memory, user must set address and data to NVMADDRL and NVMDATA, then set EWR of NVMCON.6 to initiate nvm data write. The uC will hold program code and PC Counter, and then write data to mapping address. Upon write completion, the EWR bit will be cleared by hardware, the uC will continue execute next instruction. The program time is ~50us.

#### **15. WATCHDOG TIMER**

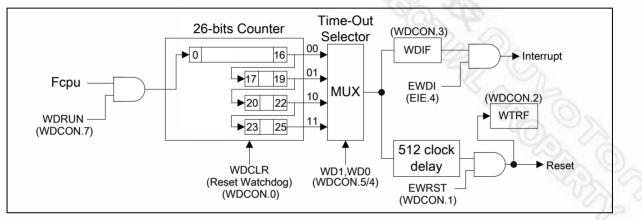

The Watchdog Timer is a free-running Timer which can be programmed by the user to serve as a system monitor, a time-base generator or an event timer. It is basically a set of dividers that divide the system clock. The divider output is selectable and determines the time-out interval. When the time-out occurs a flag is set, which can cause an interrupt if enabled, and a system reset can also be caused if it is enabled. The interrupt will occur if the individual interrupt enable and the global enable are set. The interrupt and reset functions are independent of each other and may be used separately or together depending on the user's software.

Figure 15-1: Watchdog Timer

The Watchdog Timer should first be restarted by using WDCLR. This ensures that the timer starts from a known state. The WDCLR bit is used to restart the Watchdog Timer. This bit is self clearing, i.e. after writing a 1 to this bit the software will automatically clear it. The Watchdog Timer will now count clock cycles. The time-out interval is selected by the two bits WD1 and WD0 (WDCON.5 and WDCON.4). When the selected time-out occurs, the Watchdog interrupt flag WDIF (WDCON.3) is set. After the time-out has occurred, the Watchdog Timer waits for an additional 512 clock cycles. If the Watchdog Reset EWRST (WDCON.1) is enabled, then 512 clocks after the time-out, if there is no WDCLR, a system reset due to Watchdog Timer will occur. This will last for two machine cycles, and the Watchdog Timer reset flag WTRF (WDCON.2) will be set. This indicates to the software that the Watchdog was the cause of the reset.

When used as a simple timer, the reset and interrupt functions are disabled. The timer will set the WDIF flag each time the timer completes the selected time interval. The WDIF flag is polled to detect a time-out and the WDCLR allows software to restart the timer. The Watchdog Timer can also be used as a very long timer. The interrupt feature is enabled in this case. Every time the time-out occurs an interrupt will occur if the global interrupt enable EA is set.

The main use of the Watchdog Timer is as a system monitor. This is important in real-time control applications. In case of some power glitches or electro-magnetic interference, the processor may begin to execute errant code. If this is left unchecked the entire system may crash. Using the watchdog timer interrupt during software development will allow the user to select ideal watchdog reset locations. The code is first written without the watchdog interrupt or reset. Then the Watchdog interrupt is enabled to identify code locations where interrupt occurs. The user can now insert instructions to reset the Watchdog Timer, which will allow the code to run without any Watchdog Timer interrupts. Now the Watchdog Timer reset is enabled and the Watchdog interrupt may be disabled. If any errant code is executed now, then the reset Watchdog Timer instructions will not be executed at the required instants and Watchdog reset will occur.

The Watchdog Timer time-out selection will result in different time-out values depending on the clock

#### **19. OSCILLATOR**

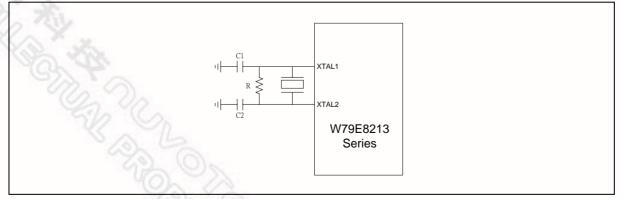

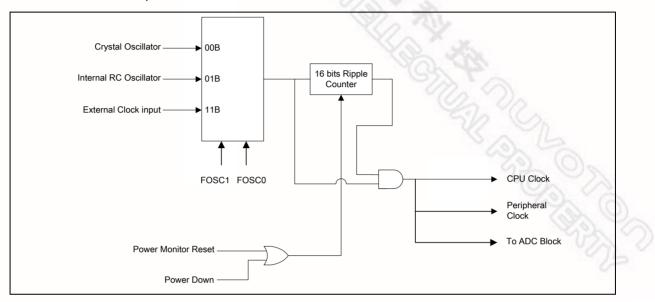

The W79E8213 series provides three oscillator input option. These are configured at CONFIG register (CONFIG0) that include Internal RC Oscillator Option, External Clock Input Option and Crystal Oscillator Input Option. The Crystal Oscillator Input frequency may be supported from 4MHz to 20MHz, and without capacitor or resister.

Figure 19-1: Oscillator

#### 19.1 Internal RC Oscillator Option

The internal RC Oscillator is configurable to 10MHz/20MHz (through CONFIG1.FS1 bit) frequency to support clock source. When FOSC1, FOSC0 = 01b, the internal RC oscillator is enabled. A clock output on P2.0 (XTAL2) may be enabled when internal RC oscillator is used.

#### **19.2 External Clock Input Option**

The clock source pin (XTAL1) is from External Clock Input by FOSC1, FOSC0 = 11b, and frequency range is form 4MHz up to 20MHz. A clock output on P2.0 (XTAL2) may be enabled when External Clock Input is used.

The W79E8213 series supports a clock output function when either the internal RC oscillator or the external clock input options is selected. This allows external devices to synchronize to the W79E8213 serial. When enabled, via the ENCLK bit in the P2M1 register, the clock output appears on the XTAL2/CLKOUT pin whenever the internal RC oscillator is running, including in Idle Mode. The frequency of the clock output is 1/4 of the CPU clock rate. If the clock output is not needed in Idle Mode, it may be turned off prior to entering Idle mode, saving additional power. The clock output may also be enabled when the external clock input option is selected.

## nuvoTon

For supporting active low buzzer, this buzzer output is implemented with an off-state of high. The following pseudo code shows the operating procedure when working with active high and low buzzer;

(Assume PRHI=1):

1) During power on, P1.0/BUZ will be high;

| <for active="" buzzer:<="" high="" p=""></for> |                                                       |

|------------------------------------------------|-------------------------------------------------------|

| Clear SFR P1.0                                 | ; user has to take care to output this pin low        |

|                                                | ; at the top of s/w code to avoid initial beep sound. |

| <for active="" buzzer="" low=""></for>         |                                                       |

| No action needed.                              |                                                       |

|                                                |                                                       |

| To turn-on buzzer;                             |                                                       |

- 2) To turn-on buzzer;

<u><For active high buzzer></u> Set BUZE bit

Set SFR P1.0 bit

; to push out the buzout.

<u><For active low buzzer></u> Set BUZE bit

- 3) To turn-off buzzer;

<For active high buzzer>

Clear SFR P1.0

; user has to take care to output this pin low.

Clear BUZE bit

<For active low buzzer>

Set BUZE bit

### ηυνοτοη

#### **21. POWER MONITORING FUNCTION**

Power-On Detect and Brownout are two additional power monitoring functions implemented in W79E8213 series to prevent incorrect operation during power up and power drop or loss.

#### 21.1 Power On Detect

The Power–On Detect function is a designed to detect power up after power voltage reaches to a level where Brownout Detect can work. After power on detect, the POR (PCON.4) will be set to "1" to indicate an initial power up condition. The POR flag will be cleared by software.

#### 21.2 Brownout Detect

The Brownout Detect function is detect power voltage is drops to brownout voltage level, and allows preventing some process work or indicate power warming. The W79E8213 series have two brownout voltage levels to select by BOV (CONFIG0.4). If BOV =0 that brownout voltage level is 3.8V, If BOV = 1 that brownout voltage level is 2.5V. When the Brownout voltage is drop to select level, the brownout detector will detect and keeps this active until VDD is returns to above brownout Detect voltage. The Brownout Detect block is as follow.

Figure 21-1: Brownout Detect Block

When Brownout Detect is enabled by BOD (AUXR1.6), the BOF (PCON.5) flag will be set and brownout reset will occur. If BOI (AUXR1.5) is set to "1", the brownout detect will cause interrupt via the EA (IE.7) and EBO (IE.5) bits is set. BOF is cleared by software.

In order to guarantee a correct detection of Brownout, The VDD fail time must be slower than 50mV/us, and rise time is slower than 2mV/us to ensure a proper reset.

## nuvoton

#### 22. PULSE-WIDTH-MODULATED (PWM) OUTPUTS

The W79E8213 series have 4 Pulse Width Modulated (PWM) channels, and the PWM outputs are PWM0(P0.1), PWM1(P1.6), PWM2(P1.7), PWM3(P0.0). The initial PWM outputs level correspondingly depend on the PRHI level set prior to the chip reset. When PRHI set to high, PWM output will initialize to high after chip reset; if PRHI set to low, PWM output will be initialize to low after chip reset.

The W79E8213 series support 10-bits down counter with cpu clock as its input. The PWM counter clock, has the frequency as  $F_{CPWM} = F_{OSC}/Prescaler$ . The two pre-scaler selectable bits FP[1:0] are located at PWMCON3[3:2].

When the counter reaches underflow it will automatic reloaded from counter register. The PWM frequency is given by: f<sub>PWM</sub> = F<sub>CPWM</sub> / (PWMP+1), where PWMP is 10-bits register of PWMPH.1, PWMPH.0 and PWMPL.7~PWMPL.0.

The counter register will be loaded with the PWMP register value when PWMRUN, load and PWMF are equal to 1; the load bit will be automatically cleared to zero on the next clock cycle, and at the same time the counter register value will be loaded to the 10 bits down counter. PWMF flag is set when 10-bits down counter underflow, the PWMF flag can only be cleared by software.

The pulse width of each PWM output is determined by the Compare registers of PWM0L through PWM3L and PWM0H through PWM3H. When PWM compare register is greater than 10-bits counter register, the PWM output is low. Load bit has to be set to 1 for alteration of PWMn width. After the new values are written to the PWMn registers, and if load bit is set to 1, the new PWMn values will be loaded to the PWMn registers upon the next underflow. The PWM output high pulses width is given by:

$t_{HI} = (PWMP - PWMn+1).$

The following equations show the formula for period and duty:

Period = (pwmp +1) \* ioclock period \* 1/prescaler = duty \* ioclock period Duty

#### Note:

- 1. If compare register is set to 000H, the PWMn output will stay at high, and if compare register is set to 3FFH, the PWMn output will stuck at low until there is a change in the compare register. [n = 0-3].

- 2. During ICP mode, PWM pins will be tri-stated. PWM operation will be stop. When exit from ICP mode, the PWM pins will follow the last SFR port values. Contraction of the second seco

### nuvoTon

#### Note:

Figure 23-2: ADC block diagram

As Port 0 is multi-function port, when configuring Port0 for ADC application, user should configure Input Only (High Impedance) and Disable Digital Input on port 0. This is done using P1Mx and PADIDS SFRs.

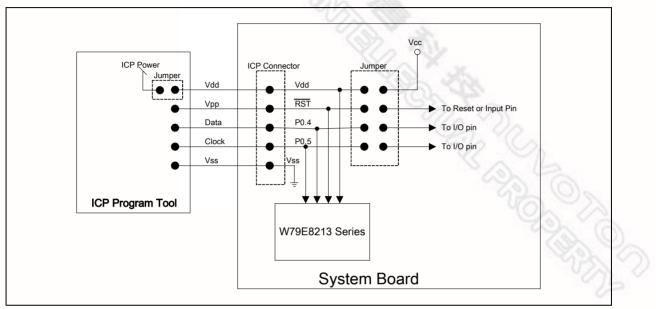

#### 24. ICP (IN-CIRCUIT PROGRAM) FLASH PROGRAM

The contexts of flash in W79E8213 series are empty by default. At the first use, you must program the flash EPROM by external Writer device or by ICP (In-Circuit Program) tool.

Note:

- 1. When using ICP to upgrade code, the P1.5, P0.4 and P0.5 must be taken within design system board.

- 2. After program finished by ICP, to suggest system power must power off and remove ICP connector then power on.

- 3. It is recommended that user performs erase function and programming configure bits continuously without any interruption.

- 4. During ICP mode, all PWM pins will be tri-stated.

### **26. ELECTRICAL CHARACTERISTICS**

### 26.1 Absolute Maximum Ratings

| PARAMETER             | SYMBOL  | MIN     | MAX     | UNIT |

|-----------------------|---------|---------|---------|------|

| DC Power Supply       | VDD-VSS | -0.3    | +7.0    | V    |

| Input Voltage         | VIN     | VSS-0.3 | VDD+0.3 | V    |

| Operating Temperature | ТА      | -40     | +85     | ٥C   |

| Storage Temperature   | Tst     | -55     | +150    | ٥C   |

| P1 Sink current       | ISK     | -       | 90      | mA   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the lift and reliability of the device.

#### DAOTEDIO 2

|                            | 0.44               |      | SPECIFI | CATION |      | ~~~~                                                                                                                |  |

|----------------------------|--------------------|------|---------|--------|------|---------------------------------------------------------------------------------------------------------------------|--|

| PARAMETER                  | SYM.               | MIN. | TYP.    | MAX.   | UNIT | TEST CONDITIONS                                                                                                     |  |

| Operating Voltage          | V <sub>DD1</sub>   | 2.4  | -       | 5.5    | V    | V <sub>DD</sub> =4.5V ~ 5.5V @ 20MHz<br>V <sub>DD</sub> =2.7V ~ 5.5V @ 12MHz<br>V <sub>DD</sub> =2.4V ~ 5.5V @ 4MHz |  |

|                            | V <sub>DD2</sub>   | 3.0  | -       | 5.5    |      | NVM program and erase operation.                                                                                    |  |

|                            | I <sub>DD1</sub>   | -    | 8.30    | 12     |      | No load, /RST = VSS, V <sub>DD</sub> =<br>5.0V @ 20MHz                                                              |  |

| Operating Current (20MHz)  | I <sub>DD2</sub>   | -    | 4.20    | 6      | - mA | No load, /RST = VSS, V <sub>DD</sub> =<br>3.0V @ 20MHz                                                              |  |

| Operating Current (200012) | I <sub>DD3</sub>   | -    | 14.50   | 20     | IIIA | No load, /RST = $V_{DD}$ , $V_{DD}$ = 5.0V @ 20MHz, RUN NOP                                                         |  |

|                            | I <sub>DD4</sub>   | -    | 5.20    | 7      |      | No load, /RST = $V_{DD}$ , $V_{DD}$ = 3.0V @ 20MHz, RUN NOP                                                         |  |

|                            | I <sub>DD5</sub>   | -    | 3.60    | 5      |      | No load, /RST = VSS, V <sub>DD</sub> =<br>5.0V @ 4MHz                                                               |  |

| Operating Current (4MUs)   | I <sub>DD6</sub>   | -    | 1.86    | 3      |      | No load, /RST = VSS, V <sub>DD</sub> =<br>3.0V @ 4MHz                                                               |  |

| Operating Current (4MHz)   | I <sub>DD7</sub>   | -    | 8.60    | 12     | - mA | No load, /RST = V <sub>DD</sub> , V <sub>DD</sub> =<br>5.0V @ 4MHz, RUN NOP                                         |  |

| C. Tr                      | I <sub>DD8</sub>   | -    | 2.20    | 3.5    |      | No load, /RST = V <sub>DD</sub> , V <sub>DD</sub> =<br>3.0V @ 4MHz, RUN NOP                                         |  |

| Idle Current               | I <sub>IDLE1</sub> | -    | 5.70    | 8      |      | No load, V <sub>DD</sub> = 5.0V<br>@ 20MHz                                                                          |  |

|                            | I <sub>IDLE2</sub> | -    | 2.48    | 3.5    | - mA | No load, V <sub>DD</sub> = 3.0V<br>@ 20MHz                                                                          |  |

|                                | OVM                | SPECIFICATION |      |           |    | TEST CONDITIONS                 |  |

|--------------------------------|--------------------|---------------|------|-----------|----|---------------------------------|--|

| PARAMETER                      | SYM.               | MIN. TYP.     |      | MAX. UNIT |    | TEST CONDITIONS                 |  |

| Brownout voltage with<br>BOV=1 | $V_{BO2.5}$        | 2.4           | -9   | 2.7       | V  | TA = -0 to 70°C                 |  |

| Brownout voltage with<br>BOV=0 | V <sub>BO3.8</sub> | 3.5           | -    | 4         | V  | TA = -0 to 70°C                 |  |

|                                |                    | -             | 0.4  | 0.8       | mA | $V_{DD} = 5.0V$ , ADCCLK = 4MHz |  |

| ADC current consumption        | ADC                | -             | 0.25 | 0.5       | mA | $V_{DD} = 3.0V$ , ADCCLK = 4MHz |  |

| Brownout voltage detect        | I <sub>BOD</sub>   | -             | 1.2  | 1.8       | mA | $V_{DD} = 5.0 V$                |  |

| current                        | IBOD               | -             | 0.8  | 1.2       |    | $V_{DD} = 3.0V$                 |  |

#### DC ELECTRICAL CHARACTERISTICS, continued

\*1. /RST pin is a Schmitt trigger input.

\*2. XTAL1 is a CMOS input.

\*3. Pins of P0, P1 and P2 can source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when Vin approximates to 2V.

\*4. Only one of the 8 pins sinks high current at a time.

### 26.3 The ADC Converter DC ELECTRICAL CHARACTERISTICS

$(V_{DD}-V_{SS} = 3.0 - 5V, TA = -40 - 85^{\circ}C, Fosc = 4MHz, unless otherwise specified.)$

| PARAMETER                  | SYMBOL         |                      | SPECIFIC                        | TEST                 |      |                                  |

|----------------------------|----------------|----------------------|---------------------------------|----------------------|------|----------------------------------|

| PARAMETER                  | STIVIDOL       | MIN.                 | TYP.                            | MAX.                 | UNIT | CONDITIONS                       |

| Analog input               | AVin           | V <sub>SS</sub> -0.2 |                                 | V <sub>DD</sub> +0.2 | V    |                                  |

| ADC clock                  | ADCCLK         | 200KHz               | -                               | 5MHz                 | Hz   | ADC block circuit<br>input clock |

| Conversion time            | t <sub>C</sub> |                      | 52t <sub>ADC</sub> <sup>1</sup> |                      | us   |                                  |

| Differential non-linearity | DNL            | -1                   | -                               | +1                   | LSB  |                                  |

| Integral non-linearity     | INL            | -2                   | -                               | +2                   | LSB  |                                  |

| Offset error               | Ofe            | -1                   | -                               | +1                   | LSB  |                                  |

| Gain error                 | Ge             | -1                   | -                               | +1                   | %    |                                  |

| Absolute voltage error     | Ae             | -3                   | -                               | +3                   | LSB  |                                  |

Notes:

1. tADC: The period time of ADC input clock.

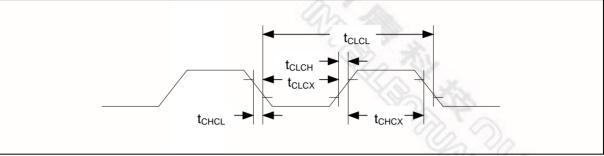

### 26.5 AC ELECTRICAL CHARACTERISTICS

Note: Duty cycle is 50%.

### 26.6 EXTERNAL CLOCK CHARACTERISTICS

| PARAMETER       | SYMBOL            | MIN. | TYP. | MAX. | UNITS | NOTES |

|-----------------|-------------------|------|------|------|-------|-------|

| Clock High Time | t <sub>CHCX</sub> | 12.5 | -    | -    | nS    | 30 (0 |

| Clock Low Time  | t <sub>CLCX</sub> | 12.5 | -    | -    | nS    | Roy.  |

| Clock Rise Time | t <sub>CLCH</sub> | -    | -    | 10   | nS    | 022   |

| Clock Fall Time | t <sub>CHCL</sub> | -    | -    | 10   | nS    | -0    |

### 26.7 AC SPECIFICATION

| PARAMETER            | SYMBOL              | VARIABLE CLOCK<br>MIN. | VARIABLE CLOCK<br>MAX. | UNITS |

|----------------------|---------------------|------------------------|------------------------|-------|

| Oscillator Frequency | 1/t <sub>CLCL</sub> | 0                      | 20                     | MHz   |

### 26.8 TYPICAL APPLICATION CIRCUITS

| CRYSTAL       | C1      | C2      | R       |

|---------------|---------|---------|---------|

| 4MHz ~ 20 MHz | without | without | without |

The above table shows the reference values for crystal applications.