Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

#### Details

·XF

| Details                 |                                                                                       |

|-------------------------|---------------------------------------------------------------------------------------|

| Product Status          | Active                                                                                |

| Applications            | Audio Record/Playback                                                                 |

| Core Processor          | ARM® Cortex®-M0                                                                       |

| Program Memory Type     | FLASH (145kB)                                                                         |

| Controller Series       | -                                                                                     |

| RAM Size                | 12K x 8                                                                               |

| Interface               | I <sup>2</sup> C, IrDA, LIN, SPI, UART/USART                                          |

| Number of I/O           | 8                                                                                     |

| Voltage - Supply        | 2.5V ~ 5.5V                                                                           |

| Operating Temperature   | -40°C ~ 85°C                                                                          |

| Mounting Type           | Surface Mount                                                                         |

| Package / Case          | 48-LQFP                                                                               |

| Supplier Device Package | 48-LQFP (7x7)                                                                         |

| Purchase URL            | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/isd9160fi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### IRQ16 ~ IRQ19 Interrupt Priority Register (NVIC\_IPR4)

| Register  | Offset       | R/W | Description                             | Reset Value |

|-----------|--------------|-----|-----------------------------------------|-------------|

| NVIC_IPR4 | SCS_BA+0x410 | R/W | IRQ16 ~ IRQ19 Priority Control Register | 0x0000_0000 |

| 31     | 30  | 29       | 28       | 27   | 26    | 25 | 24 |

|--------|-----|----------|----------|------|-------|----|----|

| PRI    | _19 | Reserved |          |      |       |    |    |

| 23     | 22  | 21       | 20       | 19   | 18    | 17 | 16 |

| PRI_18 |     |          | Reserved |      |       |    |    |

| 15     | 14  | 13       | 12       | 11   | 10    | 9  | 8  |

| PRI    | _17 |          |          | Rese | erved |    |    |

| 7      | 6   | 5        | 4        | 3    | 2     | 1  | 0  |

| PRI    | _16 | Reserved |          |      |       |    |    |

Table 5-26 Interrupt Priority Register (IPR4, address 0xE000\_E410)

| Bits    | Description | Description                                                                           |  |  |  |  |

|---------|-------------|---------------------------------------------------------------------------------------|--|--|--|--|

| [31:30] | PRI_19      | Priority of IRQ19<br>"0" denotes the highest priority and "3" denotes lowest priority |  |  |  |  |

| [23:22] | PRI_18      | Priority of IRQ18<br>"0" denotes the highest priority and "3" denotes lowest priority |  |  |  |  |

| [15:14] | PRI_17      | Priority of IRQ17<br>"0" denotes the highest priority and "3" denotes lowest priority |  |  |  |  |

| [7:6]   | PRI_16      | Priority of IRQ16<br>"0" denotes the highest priority and "3" denotes lowest priority |  |  |  |  |

## IRQ26(PDMA) Interrupt Source Identify Register (IRQ26\_SRC)

| Register  | Offset      | R/W | Description                                     | Reset Value |

|-----------|-------------|-----|-------------------------------------------------|-------------|

| IRQ26_SRC | INT_BA+0x68 | R   | IRQ26 (PDMA) Interrupt Source Identity Register | 0xXXXX_XXXX |

| 31       | 30 | 29 | 28 | 27 | 26 | 25           | 24 |  |  |

|----------|----|----|----|----|----|--------------|----|--|--|

| Reserved |    |    |    |    |    |              |    |  |  |

| 23       | 22 | 21 | 20 | 19 | 18 | 17           | 16 |  |  |

| Reserved |    |    |    |    |    |              |    |  |  |

| 15       | 14 | 13 | 12 | 11 | 10 | 9            | 8  |  |  |

| Reserved |    |    |    |    |    |              |    |  |  |

| 7        | 6  | 5  | 4  | 3  | 2  | 1            | 0  |  |  |

| Reserved |    |    |    |    |    | INT_SRC[2:0] |    |  |  |

| Bits          | Description               |                |  |  |  |

|---------------|---------------------------|----------------|--|--|--|

| [2:0] INT_SRC | Interrupt Source Identity |                |  |  |  |

|               | INT_SRC                   | Bit2: 0        |  |  |  |

| [=:0]         |                           | Bit1: 0        |  |  |  |

|               |                           | Bit0: PDMA_INT |  |  |  |

|               |                           |                |  |  |  |

nuvoTon

## **ISD9160 Technical Reference Manual**

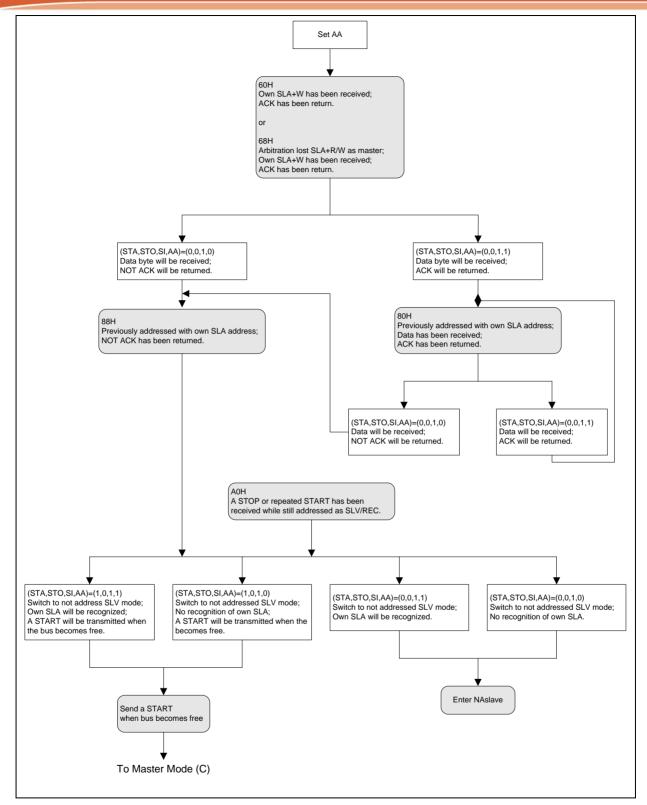

Figure 5-22 Slave Receiver Mode

## **NUVOTON** ISD9160 Technical Reference Manual

| PWM Interrupt Enable Register (PWM_INTEN) |              |     |                               |             |  |  |  |

|-------------------------------------------|--------------|-----|-------------------------------|-------------|--|--|--|

| Register                                  | Offset       | R/W | Description                   | Reset Value |  |  |  |

| PWM_INTEN                                 | PWM_BA+0x040 | R/W | PWM Interrupt Enable Register | 0x0000_0000 |  |  |  |

|                                           | •            |     |                               |             |  |  |  |

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0     |

|---|----------|---|---|---|---|---|-------|

|   | Reserved |   |   |   |   |   | PIEN0 |

### Table 5-63 PWM Interrupt Enable Register (PWM\_INTEN, address 0x4004\_0040).

| Bits | Description |                              |  |  |

|------|-------------|------------------------------|--|--|

|      |             | PWM Timer 1 Interrupt Enable |  |  |

| [1]  | PIEN1       | 0 = Disable                  |  |  |

|      |             | 1 = Enable                   |  |  |

|      |             | PWM Timer 0 Interrupt Enable |  |  |

| [0]  | PIEN0       | 0 = Disable                  |  |  |

|      |             | 1 = Enable                   |  |  |

| RTC Time-Tick Register (RTC_TICK) |              |     |                        |             |  |  |

|-----------------------------------|--------------|-----|------------------------|-------------|--|--|

| Register                          | Offset       | R/W | Description            | Reset Value |  |  |

| RTC_TICK                          | RTC_BA+0x030 | R/W | RTC Time Tick Register | 0x0000_0000 |  |  |

| 7        | 6 | 5 | 4 | 3     | 2 | 1       | 0 |

|----------|---|---|---|-------|---|---------|---|

| Reserved |   |   |   | TWKEN |   | TICKSEL |   |

#### Table 5-83 RTC Time-Tick Register (RTC\_TICK, address 0x4000\_8030).

| Bits  | Description |                                                                                                                 |  |  |  |  |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       |             | RTC Timer Wakeup CPU Function Enable Bit                                                                        |  |  |  |  |

| [3]   | TWKEN       | If TWKEN is set before CPU is in power-down mode, when a RTC Time-Tick or Alarm Match occurs, CPU will wake up. |  |  |  |  |

|       |             | 0= Disable Wakeup CPU function.                                                                                 |  |  |  |  |

|       |             | 1= Enable the Wakeup function.                                                                                  |  |  |  |  |

|       |             | Time Tick Register                                                                                              |  |  |  |  |

| [2:0] | TICKSEL     | The RTC time tick period for Periodic Time-Tick Interrupt request.                                              |  |  |  |  |

| [2:0] |             | Time Tick (second) : 1 / (2^TICKSEL)                                                                            |  |  |  |  |

|       |             | Note: This register can be read back after the RTC is active.                                                   |  |  |  |  |

#### LSB First

nuvoTon

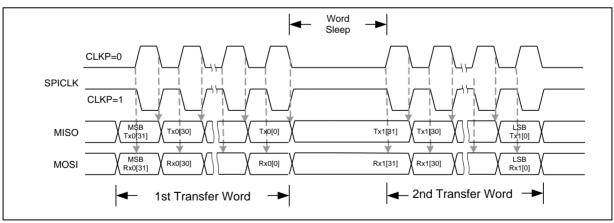

The SPI\_CTL.LSB bit defines the **bit** order of data transmission. If LSB=0 then MSB of transfer word is sent first in time. If LSB=1 then LSB of transfer word is sent first in time.

#### Transmit Edge

The SPI\_CTL.TXNEG bit determines whether transmit data is changed on the positive or negative edge of the SPI\_SCLK serial clock. If TXNEG=0 then transmitted data will change state on the rising edge of SPI\_SCLK. If TXNEG=1 then transmitted data will change state on the falling edge of SPI\_SCLK.

#### **Receive Edge**

The SPI\_CTL.RXNET bit determines whether data is received at either the negative edge or positive edge of serial clock SPI\_SCLK. If RXNET=1 then data is clocked in on the falling edge of SPI\_SCLK. If RXNET=0 data is clocked in on the rising edge of SPI\_SCLK. Note that RXNET should be the inverse of TXNEG for standard SPI operation.

#### Word Sleep Suspend

The bit field SPI\_CTL.SUSPITV provides a configurable suspend interval of SUSPITV+2 serial clock periods between successive word transfers in master mode. The suspend interval is from the last falling clock edge of the preceding transfer word to the first rising clock edge of the following transfer word if CLKPOL = 0. If CLKPOL = 1, the interval is from the rising clock edge of the preceding transfer word to the falling clock edge of the following transfer word. The default value of SUSPITV is 0x0 (2 serial clock cycles). Word Sleep only occurs when TXCNT=1. For TXCNT=0, this parameter will determine a Byte Sleep condition if the BYTEITV bit is set.

Figure 5-38 Word Sleep Suspend Mode

words. Now consider if this data were to be sent to the SPI port; the user could:

**UVOTON**

- 1. Set DWIDTH=8 and send data byte-by-byte SPI\_TX0 = ucSPI\_DATA[i++]

- 2. Set DWIDTH=32 and send word-by-word SPI\_TX0 = uiSPI\_DATA[i++]

Both of these would result in the byte stream {0x01, 0x02, 0x03, 0x04, 0x05, 0x06, 0x07, 0x08} being sent.

It would be common that a byte array of data is constructed but user, for efficiency, wishes to transfer data to SPI via word transfers. Consider the situation of Figure 5-41 where a int pointer points to the byte data array.

| unsigned char ucSPI_DATA[]={0x01, 0x02, 0x03, 0x04, 0x05, 0x06, 0x07, 0x08};<br>unsigned int *uiSPI_DATA = (unsigned int *)ucSPI_DATA[]; |                          |       |         |         |         |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|---------|---------|---------|--|--|

|                                                                                                                                          | RAM Address              | RAM   | Content | S       |         |  |  |

|                                                                                                                                          | 0x20000014               | Byte0 | Byte1   | Byte2   | Byte3   |  |  |

|                                                                                                                                          | 0x20000010               | Byte0 | Byte1   | Byte2   | Byte3   |  |  |

|                                                                                                                                          | 0x200000c                | 0x08  | 0x07    | 0x06    | 0x05    |  |  |

|                                                                                                                                          | 0x2000008                | 0x04  | 0x03    | 0x02    | 0x01    |  |  |

|                                                                                                                                          | 0x20000004               | 0x05  | 0x06    | 0x07    | 0x08    |  |  |

| uiSPI_DATA[]→                                                                                                                            | ucSPI_DATA[]→ 0x20000000 | 0x01  | 0x02    | 0x03    | 0x04    |  |  |

|                                                                                                                                          | APB Data Bus             | [7:0] | [15:8]  | [23:16] | [31:24] |  |  |

Figure 5-41 Byte Order in Memory

Now if we set DWIDTH=32 and sent word-by-word SPI\_TX0 =  $uiSPI_DATA[i++]$ , the order transmitted would be {0x04, 0x03, 0x02, 0x01, 0x08, 0x07, 0x06, 0x05}. However if we set REORDER=1, we would reverse this order to the desired stream: {0x01, 0x02, 0x03, 0x04, 0x05, 0x06, 0x07, 0x08}.

| SPI Divider Register (SPI_CLKDIV) |                |     |                                      |             |  |  |  |  |

|-----------------------------------|----------------|-----|--------------------------------------|-------------|--|--|--|--|

| Register                          | Offset         | R/W | Description                          | Reset Value |  |  |  |  |

| SPI_CLKDIV                        | SPI0_BA + 0x04 | R/W | Clock Divider Register (Master Only) | 0x0000_0000 |  |  |  |  |

| 31 | 30             | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|----|----------------|----|----|----|----|----|----|--|--|

|    | DIVIDER1[15:8] |    |    |    |    |    |    |  |  |

| 23 | 22             | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|    | DIVIDER1[7:0]  |    |    |    |    |    |    |  |  |

| 15 | 14             | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

|    | DIVIDER0[15:8] |    |    |    |    |    |    |  |  |

| 7  | 6              | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|    | DIVIDER0[7:0]  |    |    |    |    |    |    |  |  |

### Table 5-85 SPI Clock Divider Register (SPI\_CLKDIV, address 0x4003\_0004)

| Bits    | Description |                                                                                                                                                                                                                     |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |             | Clock Divider 2 Register (master only)                                                                                                                                                                              |

| [31:16] | DIVIDER1    | The value in this field is the 2 <sup>nd</sup> frequency divider of the system clock, PCLK, to generate the serial clock on the output SCLK. The desired frequency is obtained according to the following equation: |

|         |             | Fsclk aaa Fpclk / ((DIVIDER1+1) * 2)                                                                                                                                                                                |

|         |             | Clock Divider Register (master only)                                                                                                                                                                                |

|         |             | The value in this field is the frequency division of the system clock, PCLK, to generate the serial clock on the output SCLK. The desired frequency is obtained according to the following equation:                |

| [15:0]  | DIVIDER0    | Fsclk aaa Fpclk / ((DIVIDER0+1) * 2)                                                                                                                                                                                |

|         |             | In slave mode, the period of SPI clock driven by a master shall satisfy                                                                                                                                             |

|         |             | Fsclk < aaa (Fpclk / 5)                                                                                                                                                                                             |

|         |             | In other words, the maximum frequency of SCLK clock is one fifth of the SPI peripheral clock.                                                                                                                       |

### 5.10.4 Timer Controller Register Map

nuvoTon

R: read only, W: write only, R/W: both read and write

| Register          | Offset                       | R/W | Description                       | Reset Value |  |  |  |

|-------------------|------------------------------|-----|-----------------------------------|-------------|--|--|--|

| TMR Base Address: |                              |     |                                   |             |  |  |  |

| TMRn_BA=0x4001_   | TMRn_BA=0x4001_0000+(0x20*n) |     |                                   |             |  |  |  |

| n=0,1             |                              |     |                                   |             |  |  |  |

| TIMERx_CTL        | TMRn_BA+0x00                 | R/W | Timer Control and Status Register | 0x0000_0005 |  |  |  |

| TIMERx_CMP        | TMRn_BA+0x04                 | R/W | Timer Compare Register            | 0x0000_0000 |  |  |  |

| TIMERx_INTSTS     | TMRn_BA+0x08                 | R/W | Timer Interrupt Status Register   | 0x0000_0000 |  |  |  |

| TIMERx_CNT        | TMRn_BA+0x0C                 | R/W | Timer Data Register               | 0x0000_0000 |  |  |  |

#### 5.12.2 Features of UART controller

- UART supports 8 byte FIFO for receive and transmit data payloads.

- PDMA access support.

nuvoTon

- Auto flow control function (/CTS, /RTS) supported.

- Programmable baud-rate generator.

- Fully programmable serial-interface characteristics:

- 5-, 6-, 7-, or 8-bit character.

- Even, odd, or no-parity bit generation and detection.

- 1-, 1&1/2, or 2-stop bit generation.

- Baud rate generation.

- False start bit detection.

- IrDA SIR Function.

- LIN master mode.

| [8]   | LINIEN    | LIN RX Break Field Detected Interrupt Enable<br>0 = Mask off Lin bus Rx break field interrupt.<br>1 = Enable Lin bus Rx break field interrupt. |

|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | Reserved  | Reserved                                                                                                                                       |

| [5]   | BUFERRIEN | Buffer Error Interrupt Enable<br>0 = Mask off BUFERRINT<br>1 = Enable IBUFERRINT                                                               |

| [4]   | RXTOIEN   | Receive Time out Interrupt Enable<br>0 = Mask off RXTOINT<br>1 = Enable RXTOINT                                                                |

| [3]   | MODEMIEN  | Modem Status Interrupt Enable<br>0 = Mask off MODEMINT<br>1 = Enable MODEMINT                                                                  |

| [2]   | RLSIEN    | Receive Line Status Interrupt Enable<br>0 = Mask off RLSINT<br>1 = Enable RLSINT                                                               |

| [1]   | THREIEN   | Transmit FIFO Register Empty Interrupt Enable<br>0 = Mask off THERINT<br>1 = Enable THERINT                                                    |

| [0]   | RDAIEN    | Receive Data Available Interrupt Enable.0 = Mask off RDAINT1 = Enable RDAINT                                                                   |

## 5.13.5 FIFO operation

| , |                       |            |     |       |          |    |       |   |         |

|---|-----------------------|------------|-----|-------|----------|----|-------|---|---------|

|   | Mono 8-bit data mode  | )          |     |       |          |    |       |   | -       |

|   | N+3<br>7 0            | N+2<br>7 0 | 7   | N+1   | 0        | 7  | N     | 0 |         |

|   | Stereo 8-bit data mod |            | ·   |       | <u> </u> |    |       |   | I       |

|   | LEFT+1                | RIGHT+1    |     | LEFT  |          |    | RIGHT |   |         |

|   | 7 0                   | 7 0        | 7   |       | 0        | 7  |       | 0 | ]       |

|   | Mono 16-bit data mod  |            | T   |       |          |    |       |   | 1       |

|   | N+                    | +10        | 15  |       | N        |    |       | 0 |         |

|   | Stereo 16-bit data mo | de         |     |       |          |    |       |   |         |

|   | LE<br>15              | FT 0       | 15  |       | RIGI     | ΗТ |       | 0 |         |

|   | Mono 24-bit data mod  |            |     |       |          |    |       |   | I       |

|   |                       |            |     | N     |          |    |       |   |         |

|   |                       | 23         |     | ••    |          |    |       | 0 | ]       |

|   | Stereo 24-bit data mo | de<br>T    |     |       |          |    |       |   | 1       |

|   |                       | 23         |     | LEFT  |          |    |       | 0 | N       |

|   |                       | 1          |     | RIGHT |          |    |       |   | N+1     |

|   |                       | 23         |     | RIGHT |          |    |       | 0 | N+1<br> |

|   | Mono 32-bit data mod  | le         |     |       |          |    |       |   | _       |

|   | 31                    |            | N   |       |          |    |       | 0 |         |

|   | Stereo 32-bit data mo | de         |     |       |          |    |       |   | I       |

|   |                       |            | EFT |       |          |    |       |   | N       |

|   | 31                    |            |     |       |          |    |       | 0 |         |

|   | 31                    | RI         | GHT |       |          |    |       | 0 | N+1     |

|   | 31                    |            |     |       |          |    |       |   | ]       |

Figure 5-63 FIFO contents for various I2S modes

### 5.13.6 I2S Control Register Map

nuvoTon

R: read only, W: write only, R/W: both read and write

| Register              | Offset            | R/W | Description                   | Reset Value |  |  |  |

|-----------------------|-------------------|-----|-------------------------------|-------------|--|--|--|

| I2S Base Address:     | I2S Base Address: |     |                               |             |  |  |  |

| $12S\_BA = 0x400A\_0$ | 0000              |     |                               |             |  |  |  |

| I2S_CTL               | I2S_BA + 0x00     | R/W | I2S Control Register          | 0x0000_0000 |  |  |  |

| I2S_CLKDIV            | I2S_BA + 0x04     | R/W | I2S Clock Divider Register    | 0x0000_0000 |  |  |  |

| I2S_IEN               | I2S_BA + 0x08     | R/W | I2S Interrupt Enable Register | 0x0000_0000 |  |  |  |

| I2S_STATUS            | I2S_BA + 0x0C     | R/W | I2S Status Register           | 0x0014_1000 |  |  |  |

| I2S_TX                | I2S_BA + 0x10     | W   | I2S Transmit FIFO Register    | 0x0000_0000 |  |  |  |

| I2S_RX                | I2S_BA + 0x14     | R   | I2S Receive FIFO Register     | 0x0000_0000 |  |  |  |

# **NUVOTON** ISD9160 Technical Reference Manual

| I2S Interrupt Enable Register (I2S_IEN) |               |     |                               |             |  |  |  |

|-----------------------------------------|---------------|-----|-------------------------------|-------------|--|--|--|

| Register                                | Offset        | R/W | Description                   | Reset Value |  |  |  |

| I2S_IEN                                 | I2S_BA + 0x08 | R/W | I2S Interrupt Enable Register | 0x0000_0000 |  |  |  |

| 15 | 14       | 13       | 12      | 11      | 10      | 9       | 8       |

|----|----------|----------|---------|---------|---------|---------|---------|

|    | Reserved |          |         | RZCIEN  | TXTHIEN | TXOVIEN | TXUDIEN |

| 7  | 6        | 5        | 4       | 3       | 2       | 1       | 0       |

|    | -        | Reserved | RXTHIEN | RXOVIEN | RXUDIEN |         |         |

Table 5-116 I2S Interrupt Enable Register (I2S\_IEN, address 0x400A\_0008)

| Bits | Description |                                                                                                                                                                                                     |

|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [12] | LZCIEN      | Left Channel Zero Cross Interrupt Enable<br>Interrupt will occur if this bit is set to 1 and left channel has zero cross event<br>0 = Disable interrupt<br>1 = Enable interrupt                     |

| [11] | RZCIEN      | Right Channel Zero Cross Interrupt EnableInterrupt will occur if this bit is set to 1 and right channel has zero cross event0 = Disable interrupt1 = Enable interrupt                               |

| [10] | TXTHIEN     | Transmit FIFO Threshold Level Interrupt Enable<br>Interrupt occurs if this bit is set to 1 and data words in transmit FIFO is less than TXTH[2:0].<br>0 = Disable interrupt<br>1 = Enable interrupt |

| [9]  | TXOVIEN     | Transmit FIFO Overflow Interrupt Enable<br>Interrupt occurs if this bit is set to 1 and transmit FIFO overflow flag is set to 1<br>0 = Disable interrupt<br>1 = Enable interrupt                    |

| [8]  | TXUDIEN     | Transmit FIFO Underflow Interrupt Enable<br>Interrupt occur if this bit is set to 1 and transmit FIFO underflow flag is set to 1.<br>0 = Disable interrupt<br>1 = Enable interrupt                  |

| [2]  | RXTHIEN     | Receive FIFO Threshold Level Interrupt Interrupt occurs if this bit is set to 1 and data words in receive FIFO is greater than or equal to RXTH[2:0]. 0 = Disable interrupt 1 = Enable interrupt    |

## nuvoTon

| CRC Output   |             |     |                     |             |  |  |

|--------------|-------------|-----|---------------------|-------------|--|--|

| Register     | Offset      | R/W | Description         | Reset Value |  |  |

| CRC_CHECKSUM | CRC_BA+0x08 | R   | CRC Output Register | 0x0000_FFFF |  |  |

## Table 5-122 CRC Output Register

| 31 | 30            | 29 | 28     | 27       | 26 | 25 | 24 |  |  |

|----|---------------|----|--------|----------|----|----|----|--|--|

|    | Reserved      |    |        |          |    |    |    |  |  |

| 23 | 22            | 21 | 20     | 19       | 18 | 17 | 16 |  |  |

|    | Reserved      |    |        |          |    |    |    |  |  |

| 15 | 14            | 13 | 12     | 11       | 10 | 9  | 8  |  |  |

|    |               |    | CHECKS | UM[15:8] |    |    |    |  |  |

| 7  | 6             | 5  | 4      | 3        | 2  | 1  | 0  |  |  |

|    | CHECKSUM[7:0] |    |        |          |    |    |    |  |  |

| Bits   | Description |                                                                                                                                                      |

|--------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:0] | CHECKSUM    | <b>CRC Output</b><br>The result of CRC computation. The result is valid four clock cycles after last CRC_DAT input data is written to CRC generator. |

| Register         | Offset        | R/W | Description                                        | Reset Value |

|------------------|---------------|-----|----------------------------------------------------|-------------|

| PDMA_DSCT0_ENDSA | PDMA_BA+0x04  | R/W | PDMA Transfer Source Address Register of Channel 0 | 0x0000_0000 |

| PDMA_DSCT1_ENDSA | PDMA_BA+0x104 | R/W | PDMA Transfer Source Address Register of Channel 1 | 0x0000_0000 |

| PDMA_DSCT2_ENDSA | PDMA_BA+0x204 | R/W | PDMA Transfer Source Address Register of Channel 2 | 0x0000_0000 |

| PDMA_DSCT3_ENDSA | PDMA_BA+0x304 | R/W | PDMA Transfer Source Address Register of Channel 3 | 0x0000_0000 |

#### PDMA Transfer Source Address Register (PDMA\_DSCTn\_ENDSA)(n=0~3)

#### Table 5-124 PDMA Source Address Register (PDMA\_DSCTn\_ENDSA, address 0x5000\_8004 + *n*\*0x100)

| Bits   | Description |                                                                  |  |  |  |  |

|--------|-------------|------------------------------------------------------------------|--|--|--|--|

|        |             | PDMA Transfer Source Address Register                            |  |  |  |  |

| [31:0] | ENDSA       | This register holds the initial Source Address of PDMA transfer. |  |  |  |  |

|        |             | Note: The source address must be word aligned.                   |  |  |  |  |

### PDMA Current Byte Count Register (PDMA\_CURBCCHn) (n=0~3)

| Register      | Offset        | R/W | Description                                   | Reset Value |

|---------------|---------------|-----|-----------------------------------------------|-------------|

| PDMA_CURBCCH0 | PDMA_BA+0x1C  | R   | PDMA Current Byte Count Register of Channel 0 | 0x0000_0000 |

| PDMA_CURBCCH1 | PDMA_BA+0x11C | R   | PDMA Current Byte Count Register of Channel 1 | 0x0000_0000 |

| PDMA_CURBCCH2 | PDMA_BA+0x21C | R   | PDMA Current Byte Count Register of Channel 2 | 0x0000_0000 |

| PDMA_CURBCCH3 | PDMA_BA+0x31C | R   | PDMA Current Byte Count Register of Channel 3 | 0x0000_0000 |

#### Table 5-130 PDMA Current Byte Count Register (PDMA\_CURBCCHn, address 0x5000\_801C + *n*\*0x100)

| Bits    | Description       |                                                                                                                                                                                                                                           |  |  |  |  |

|---------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| [31:16] | Reserved Reserved |                                                                                                                                                                                                                                           |  |  |  |  |

| [15:0]  | CURBC             | <b>PDMA Current Byte Count Register (Read Only)</b><br>This field indicates the current remaining byte count of PDMA transfer. This register is initialized with PDMA_TXBCCHn register when PDMA is triggered or when a wraparound occurs |  |  |  |  |

## PDMA Interrupt Status Register (PDMA\_CHnIF) (n=0~3)

| Register   | Offset        | R/W | Description                                 | Reset Value |

|------------|---------------|-----|---------------------------------------------|-------------|

| PDMA_CH0IF | PDMA_BA+0x24  | R/W | PDMA Interrupt Status Register of Channel 0 | 0x0000_0000 |

| PDMA_CH1IF | PDMA_BA+0x124 | R/W | PDMA Interrupt Status Register of Channel 1 | 0x0000_0000 |

| PDMA_CH2IF | PDMA_BA+0x224 | R/W | PDMA Interrupt Status Register of Channel 2 | 0x0000_0000 |

| PDMA_CH3IF | PDMA_BA+0x324 | R/W | PDMA Interrupt Status Register of Channel 3 | 0x0000_0000 |

| 31     | 30       | 29       | 28      | 27   | 26 | 25 | 24 |  |  |  |  |

|--------|----------|----------|---------|------|----|----|----|--|--|--|--|

| INTSTS |          | Reserved |         |      |    |    |    |  |  |  |  |

| 23     | 22       | 21       | 20      | 19   | 18 | 17 | 16 |  |  |  |  |

|        | Reserved |          |         |      |    |    |    |  |  |  |  |

| 15     | 14       | 13       | 12      | 11   | 10 | 9  | 8  |  |  |  |  |

|        | Rese     | erved    |         | WAIF |    |    |    |  |  |  |  |

| 7      | 6        | 5        | 4       | 3    | 2  | 1  | 0  |  |  |  |  |

|        |          | TXOKIF   | TXABTIF |      |    |    |    |  |  |  |  |

## Table 5-132 PDMA Interrupt Enable Status Register (PDMA\_CHnIF, address 0x5000\_8024 +

*n*\*0x100)

| Bits    | Description |                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|---------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [31]    | INTSTS      | Interrupt Pin Status (Read Only)<br>This bit is the Interrupt pin status of PDMA channel.                                                                                                                                                                                                                                                                                               |  |  |  |

| [30:12] | Reserved    | Reserved                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| [11:8]  | WAIF        | <ul> <li>Wrap Around Transfer Byte Count Interrupt Flag</li> <li>These flags are set whenever the conditions for a wraparound interrupt (complete or half complete) are met. They are cleared by writing one to the bits.</li> <li>0001 aaa Current transfer finished flag (CURBC aaaaaa 0).</li> <li>0100 aaa Current transfer half complete flag (CURBC aaaaaa BYTECNT/2).</li> </ul> |  |  |  |

| [1]     | TXOKIF      | <ul> <li>Block Transfer Done Interrupt Flag</li> <li>This bit indicates that PDMA block transfer complete interrupt has been generated. It is cleared by writing 1 to the bit.</li> <li>0 = Transfer ongoing or Idle.</li> <li>1 = Transfer Complete.</li> </ul>                                                                                                                        |  |  |  |

## nuvoTon

## **ISD9160 Technical Reference Manual**

|                                      | I <sub>DD13</sub>  | 12.5 | mA | V <sub>DD</sub> = 5.5V,<br>Enable all IP.          |

|--------------------------------------|--------------------|------|----|----------------------------------------------------|

| Operating Current                    | I <sub>DD14</sub>  | 10.3 | mA | V <sub>DD</sub> = 5.5V,<br>Disable all IP.         |

| Normal Run Mode<br>@ 12.288Mhz       | I <sub>DD15</sub>  | 11.4 | mA | V <sub>DD</sub> = 3V,<br>Enable all IP.            |

|                                      | I <sub>DD16</sub>  | 9    | mA | V <sub>DD</sub> = 3V,<br>Disable all IP.           |

|                                      | I <sub>DD9</sub>   | 9.7  | mA | $V_{DD} = 5.5V$ ,<br>Enable all IP.                |

| Operating Current<br>Normal Run Mode | I <sub>DD10</sub>  | 8.1  | mA | V <sub>DD</sub> = 5.5V,<br>Disable all IP.         |

| @ 4.9152Mhz                          | I <sub>DD11</sub>  | 8.7  | mA | V <sub>DD</sub> = 3V,<br>Enable all IP.            |

|                                      | I <sub>DD12</sub>  | 7.0  | mA | V <sub>DD</sub> = 3V,<br>Disable all IP.           |

| Operating Current<br>Sleep Mode      | I <sub>IDLE1</sub> | 10   | mA | V <sub>DD</sub> = 5.5V                             |

| Sleep wode                           | I <sub>IDLE1</sub> | 9    | mA | V <sub>DD</sub> = 3.3V                             |

| Operating Current                    | I <sub>IDLE1</sub> | 10   | mA | V <sub>DD</sub> =5.5V                              |

| Deep Sleep Mode                      | I <sub>IDLE1</sub> | 8    | mA | V <sub>DD</sub> = 3.3V                             |

| Standby Power down                   | I <sub>IDLE1</sub> | 3    | uA | $V_{DD}$ =3.3V 32K running with RTC                |

| mode(SPD)                            | I <sub>IDLE1</sub> | 1    | uA | V <sub>DD</sub> = 3.3V 16K running                 |

| Operating Current                    | I <sub>IDLE1</sub> | 500  | nA | V <sub>DD</sub> =3.3V Wakeup with16K               |

| Deep Power down mode(DPD)            | I <sub>IDLE1</sub> |      | nA | $V_{\text{DD}}\text{=}3.3V$ wakeup with wakeup pin |

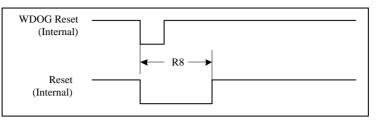

9.5.1.4 Watchdog Reset Timing