#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HCS08                                                                  |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 48MHz                                                                  |

| Connectivity               | FIFO, I <sup>2</sup> C, SCI, SPI, USB                                  |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 46                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 12K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 8x12b SAR                                                          |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-LQFP                                                                |

| Supplier Device Package    | 80-LQFP (12x12)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08je128clk |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 Devices in the MC9S08JE128 series                          | 3  |

|--------------------------------------------------------------|----|

| 2 Preliminary Electrical Characteristics                     | 12 |

| 2.1 Parameter Classification                                 | 12 |

| 2.2 Absolute Maximum Ratings                                 | 13 |

| 2.3 Thermal Characteristics                                  | 14 |

| 2.4 Electrostatic Discharge (ESD) Protection Characteristics |    |

| 2.5 DC Characteristics                                       | 16 |

| 2.6 Supply Current Characteristics                           | 19 |

| 2.7 Comparator (PRACMP) Electricals                          | 21 |

| 2.8 12-Bit Digital-to-Analog Converter (DAC12LV) Electricals | 22 |

| 2.9 ADC Characteristics                                      | 23 |

| 2.10 MCG and External Oscillator (XOSC) Characteristics      | 28 |

| 2.11 AC Characteristics                                      | 31 |

| 2.12 SPI Characteristics                                     | 32 |

| 2.13 Flash Specifications                                    | 35 |

| 2.14 USB Electricals                                         | 36 |

|                                                              |    |

| 2.15 | VREF | Specifications | 35 |

|------|------|----------------|----|

|------|------|----------------|----|

| 3 Ordering Information      | 41 |

|-----------------------------|----|

| 3.1 Device Numbering System | 42 |

| 3.2 Package Information     |    |

| 3.3 Mechanical Drawings     | 42 |

| 4 Revision History          | 43 |

# **Related Documentation**

Find the most current versions of all documents at: http://www.freescale.com.

#### Reference Manual —MC9S08JE128RM

Contains extensive product information including modes of operation, memory, resets and interrupts, register definition, port pins, CPU, and all module information.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2009-2010. All rights reserved.

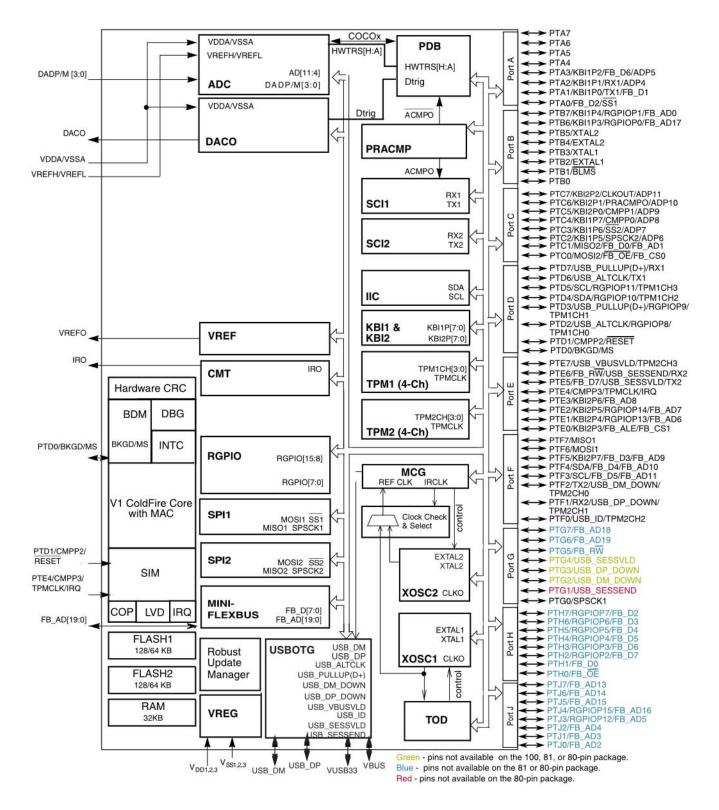

Figure 1. MC9S08JE128 series Block Diagram

Devices in the MC9S08JE128 series

### 1.1 Pin Assignments

This section shows the pin assignments for the MC9S08JE128 series devices.

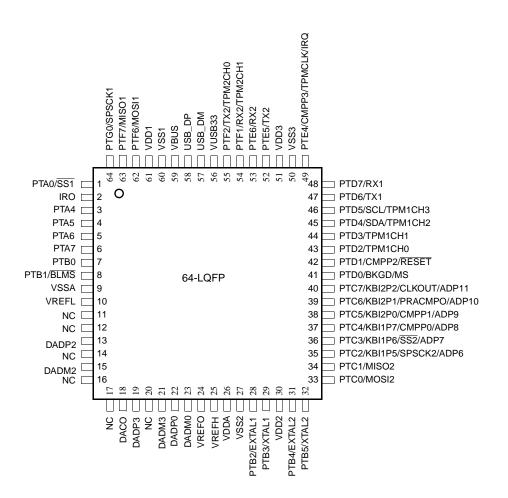

### 1.1.1 64-Pin LQFP

The following two figures show the 64-pin LQFP pinout configuration.

Figure 2. 64-Pin LQFP

# 1.2 Pin Assignments by Packages

| Pa        | ackag   | е       |                     |        |      |      |                      |

|-----------|---------|---------|---------------------|--------|------|------|----------------------|

| 81 MAPBGA | 80 LQFP | 64 LQFP | Default<br>Function | ALT1   | ALT2 | ALT3 | Composite Pin Name   |

| B2        | 1       | 1       | PTA0                | SS1    | _    | _    | PTA0/SS1             |

| A1        | 2       | 2       | IRO                 | _      | _    | -    | IRO                  |

| C4        | 3       |         | PTA1                | KBI1P0 | TX1  | _    | PTA1/KBI1P0/TX1      |

| D5        | 4       |         | PTA2                | KBI1P1 | RX1  | ADP4 | PTA2/KBI1P1/RX1/ADP4 |

| D6        | 5       |         | PTA3                | KBI1P2 | ADP5 | _    | PTA3/KBI1P2/ADP5     |

| C1        | 6       | 3       | PTA4                | _      |      | _    | PTA4                 |

| C2        | 7       | 4       | PTA5                | _      | _    |      | PTA5                 |

| C3        | 8       | 5       | PTA6                | _      | _    | _    | PTA6                 |

| D2        | 9       | 6       | PTA7                | _      | _    |      | PTA7                 |

| D3        | 10      | 7       | PTB0                | _      |      |      | PTB0                 |

| D4        | 11      | 8       | PTB1                | BLMS   | _    | _    | PTB1/BLMS            |

| J1        | 12      | 9       | VSSA                | _      | _    | _    | VSSA                 |

| J2        | 13      | 10      | VREFL               | _      | _    | _    | VREFL                |

| D1        | 14      | 11      | NC                  |        | _    | _    | NC                   |

| E1        | 15      | 12      | NC                  | _      | _    | _    | NC                   |

| F2        | 16      | 13      | DADP2               | _      | _    | _    | DADP2                |

| F1        | 17      | 14      | NC                  | _      |      |      | NC                   |

| E2        | 18      | 15      | DADM2               | _      | _    | _    | DADM2                |

| F3        | 19      | 16      | NC                  | _      | _    | _    | NC                   |

| E3        | 20      | 17      | NC                  | _      |      | _    | NC                   |

| G2        | 21      | 18      | DACO                | _      | _    | _    | DACO                 |

| G3        | 22      | 19      | DADP3               | _      | _    | _    | DADP3                |

| H4        | 23      | 20      | NC                  | —      | _    | _    | NC                   |

| G4        | 24      | 21      | DADM3               | _      | _    | _    | DADM3                |

| G1        | 25      | 22      | DADP0               |        |      | _    | DADP0                |

| H1        | 26      | 23      | DADM0               | _      | _    | _    | DADM0                |

| G5        | 27      | 24      | VREFO               | _      | _    | _    | VREFO                |

| H3        | 28      |         | DADP1               | _      | _    | _    | DADP1                |

| H2        | 29      | —       | DADM1               | _      | _    | _    | DADM1                |

| Table 3 | 8. Package | Pin Assigr | ments |  |  |

|---------|------------|------------|-------|--|--|

|         |            |            |       |  |  |

### 2.3 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

| # | Symbol            |                                     | Value                                   | Unit       |      |

|---|-------------------|-------------------------------------|-----------------------------------------|------------|------|

| 1 | T <sub>A</sub>    | Operating temperature               | range (packaged):                       |            | °C   |

|   |                   |                                     | MC9S08JE128                             | -40 to 105 | -    |

|   |                   |                                     | MC9S08JE64                              | -40 to 105 |      |

| 2 | T <sub>JMAX</sub> | Maximum junction tem                | perature                                | 135        | °C   |

| 3 | $\theta_{JA}$     | Thermal resistance <sup>1,2,3</sup> | <sup>3,4</sup> Single-layer board — 1s  |            | °C/W |

|   |                   |                                     | 81-pin MBGA                             | 77         |      |

|   |                   |                                     | 80-pin LQFP                             | 55         |      |

|   |                   |                                     | 64-pin LQFP                             | 68         |      |

| 4 | $\theta_{JA}$     | Thermal resistance <sup>1, 2,</sup> | <sup>3, 4</sup> Four-layer board — 2s2p |            | °C/W |

|   |                   |                                     | 81-pin MBGA                             | 47         |      |

|   |                   |                                     | 80-pin LQFP                             | 40         |      |

|   |                   |                                     | 64-pin LQFP                             | 49         |      |

| 0        | . 22   |                   |   |

|----------|--------|-------------------|---|

| Table 6. | Therma | I Characteristics | 5 |

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- <sup>2</sup> Junction to Ambient Natural Convection

- <sup>3</sup> 1s Single layer board, one signal layer

- <sup>4</sup> 2s2p Four layer board, 2 signal and 2 power layers

The average chip-junction temperature  $(T_J)$  in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$T_A = Ambient temperature, °C$

$\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W

$P_D = P_{int} + P_{I/O}$

$P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

$P_{I/O}$  = Power dissipation on input and output pins — user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K \div (T_{J} + 273^{\circ}C)$$

Eqn. 2

| Num | Symbol           |                                                               | teristic                            | Condition                                                  | Min                       | ,<br>Typ <sup>1</sup> | Мах                       | Unit | С |

|-----|------------------|---------------------------------------------------------------|-------------------------------------|------------------------------------------------------------|---------------------------|-----------------------|---------------------------|------|---|

| 7   | V <sub>IL</sub>  | Input low voltage all digital inputs                          |                                     |                                                            |                           |                       |                           |      |   |

|     |                  |                                                               |                                     | all digital inputs, $V_{DD} > 2.7 V$                       | —                         | _                     | 0.35 x<br>V <sub>DD</sub> | V    | Р |

|     |                  |                                                               |                                     | all digital inputs, $2.7 > V_{DD} \ge \\ 1.8 \text{ V}$    | _                         | _                     | 0.30 x<br>V <sub>DD</sub> | V    | Р |

| 8   | V <sub>hys</sub> | Input hysteresis                                              | all digital inputs                  | —                                                          | 0.06 x<br>V <sub>DD</sub> |                       |                           | mV   | С |

| 9   | I <sub>In </sub> | Input leakage<br>current                                      | all input only<br>pins<br>(Per pin) | $V_{In} = V_{DD}$ or $V_{SS}$                              | —                         | _                     | 0.25<br>(TBD)             | μΑ   | Р |

| 10  | I <sub>OZ </sub> | Hi-Z (off-state)<br>leakage current                           | all input/output<br>(per pin)       | $V_{ln} = V_{DD} \text{ or } V_{SS}$                       | _                         |                       | 1(TBD)                    | μΑ   | Р |

| 11  | I <sub>OZ</sub>  | Leakage current<br>for analog output<br>pins (DACO,<br>VREFO) | all input/output<br>(per pin)       | V <sub>In</sub> = V <sub>DD</sub> or<br>V <sub>SS</sub>    | _                         | _                     | (TBD)                     | μΑ   | Ρ |

| 12  | I <sub>InT</sub> | Total Leakage<br>Current <sup>3</sup>                         | For all pins                        |                                                            | —                         | —                     | 2                         | μΑ   | D |

| 13  | R <sub>PU</sub>  | Pull-up resistors                                             |                                     |                                                            | 17.5                      | _                     | 52.5                      | kΩ   | Р |

| 14  | R <sub>PD</sub>  | Internal<br>pull-down<br>resistors <sup>4</sup>               |                                     | _                                                          | 17.5                      | —                     | 52.5                      | kΩ   | Р |

| 15  | Ι <sub>IC</sub>  | DC injection<br>current <sup>5, 6, 7</sup>                    | Single pin limit                    |                                                            | <u></u>                   |                       |                           |      |   |

|     |                  |                                                               |                                     | $\begin{array}{c} V_{SS} > V_{IN} > \\ V_{DD} \end{array}$ | -0.2                      | —                     | 0.2                       | mA   | D |

|     |                  | Total MCU limit, includes sum of all stressed pins            |                                     |                                                            |                           |                       |                           |      |   |

|     |                  |                                                               |                                     | $V_{SS} > V_{IN} > V_{DD}$                                 | -5                        | _                     | 5                         | mA   | D |

| 16  | C <sub>In</sub>  | Input Capacitance                                             | e, all pins                         | _                                                          | —                         | _                     | 8                         | pF   | С |

| 17  | V <sub>RAM</sub> | RAM retention vo                                              | tage                                |                                                            | —                         | 0.6                   | 1.0                       | V    | С |

| 18  | V <sub>POR</sub> | POR re-arm volta                                              | ge <sup>8</sup>                     |                                                            | 0.9                       | 1.4                   | 1.79                      | V    | С |

| 19  | t <sub>POR</sub> | POR re-arm time                                               |                                     | _                                                          | 10                        | _                     | _                         | μS   | D |

| Num | Symbol              | Chara                                                             | Condition                 | Min | Typ <sup>1</sup> | Мах  | Unit | С  |   |

|-----|---------------------|-------------------------------------------------------------------|---------------------------|-----|------------------|------|------|----|---|

| 20  | V <sub>LVDH</sub> 9 | Low-voltage<br>detection<br>threshold —<br>high range             | V <sub>DD</sub> falling   | 1   | I                |      |      |    |   |

|     |                     |                                                                   |                           |     | 2.11             | 2.16 | 2.22 | V  | Р |

|     |                     |                                                                   | V <sub>DD</sub> rising    |     |                  |      |      |    |   |

|     |                     |                                                                   |                           | _   | 2.16             | 2.23 | 2.27 | V  | Р |

| 21  | V <sub>LVDL</sub>   | Low-voltage<br>detection<br>threshold —<br>low range <sup>9</sup> | V <sub>DD</sub> falling   |     |                  |      |      |    |   |

|     |                     |                                                                   |                           |     | 1.80             | 1.84 | 1.88 | V  | Ρ |

|     |                     |                                                                   | $V_{DD}$ rising           |     |                  |      |      |    |   |

|     |                     |                                                                   |                           |     | 1.88             | 1.93 | 1.96 | V  | Р |

| 22  | V <sub>LVWH</sub>   | Low-voltage<br>warning<br>threshold —<br>high range <sup>9</sup>  | V <sub>DD</sub> falling   |     |                  |      |      |    |   |

|     |                     |                                                                   |                           | _   | 2.36             | 2.46 | 2.56 | V  | Р |

|     |                     |                                                                   | $V_{DD}$ rising           |     |                  |      |      |    |   |

|     |                     |                                                                   |                           | _   | 2.36             | 2.46 | 2.56 | V  | Р |

| 23  | V <sub>LVWL</sub>   | Low-voltage<br>warning<br>threshold —<br>low range <sup>9</sup>   | V <sub>DD</sub> falling   |     |                  |      |      |    |   |

|     |                     |                                                                   |                           | _   | 2.11             | 2.16 | 2.22 | V  | Р |

|     |                     |                                                                   | V <sub>DD</sub> rising    |     | •                |      |      |    |   |

|     |                     |                                                                   |                           |     | 2.16             | 2.23 | 2.27 | V  | Р |

| 24  | V <sub>hys</sub>    | Low-voltage inhi<br>hysteresis <sup>10</sup>                      | bit reset/recover         | _   | _                | 50   | —    | mV | С |

| 25  | $V_{BG}$            | Bandgap Voltag                                                    | e Reference <sup>11</sup> | —   | 1.15             | 1.17 | 1.18 | V  | Р |

#### Table 9. DC Characteristics (Continued)

<sup>1</sup> Typical values are measured at 25°C. Characterized, not tested

<sup>2</sup> As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above V<sub>LVDL</sub>.

<sup>3</sup> Total Leakage current is the sum value for all GPIO pins; this leakage current is not distributed evenly across all pins but characterization data shows that individual pin leakage current maximums are less than 250 nA.

<sup>4</sup> Measured with  $V_{In} = V_{DD}$ .

$^5\,$  All functional non-supply pins are internally clamped to V\_{SS} and V\_{DD}.

<sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>7</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

- <sup>8</sup> Maximum is highest voltage that POR is guaranteed.

- <sup>9</sup> Run at 1 MHz bus frequency

- <sup>10</sup> Low voltage detection and warning limits measured at 1 MHz bus frequency.

- <sup>11</sup> Factory trimmed at  $V_{DD} = 3.0$  V, Temp = 25°C

### Supply Current Characteristics Table 10. Supply Current Characteristics 2.6

| # | Symbol           | Para                     | ameter                 | Bus<br>Freq     | V <sub>DD</sub> (V) | Typ <sup>1</sup> | Мах | Unit | Temp<br>(°C)  | С |

|---|------------------|--------------------------|------------------------|-----------------|---------------------|------------------|-----|------|---------------|---|

| 1 | RI <sub>DD</sub> | Run<br>supply<br>current | FEI mode<br>All module | s ON            | L                   | I                | 1   | I    | 1 1           |   |

|   |                  |                          |                        | 24 MHz          | 3                   | 20               | 24  | mA   | -40 to<br>25  | Ρ |

|   |                  |                          |                        | 24 MHz          | 3                   | 20               | TBD | mA   | 105           | Р |

|   |                  |                          |                        | 20 MHz          | 3                   | 18               | _   | mA   | -40 to<br>105 | Т |

|   |                  |                          |                        | 8 MHz           | 3                   | 8                | _   | mA   | -40 to<br>105 | Т |

|   |                  |                          |                        | 1 MHz           | 3                   | 1.8              | _   | mA   | -40 to<br>105 | Т |

| 2 | RI <sub>DD</sub> | Run<br>supply<br>current | FEI mode;              | All modules     | OFF                 |                  |     |      | · · ·         |   |

|   |                  |                          |                        | 24 MHz          | 3                   | 12.3             | TBD | mA   | -40 to<br>105 | С |

|   |                  |                          |                        | 20 MHz          | 3                   | 10.5             | _   | mA   | -40 to<br>105 | Т |

|   |                  |                          |                        | 8 MHz           | 3                   | 4.8              | _   | mA   | -40 to<br>105 | Т |

|   |                  |                          |                        | 1 MHz           | 3                   | 1.3              | _   | mA   | -40 to<br>105 | Т |

| 3 | RI <sub>DD</sub> | Run<br>supply<br>current | LPS=0; All             | modules OF      | F                   |                  |     |      |               |   |

|   |                  |                          |                        | 16 kHz<br>FBILP | 3                   | TBD              | _   | μΑ   | -40 to<br>105 | Т |

|   |                  |                          |                        | 16 kHz<br>FBELP | 3                   | TBD              | _   | μA   | -40 to<br>105 | Т |

| 4 | RI <sub>DD</sub> | Run supply current       | LPS=1, all             | modules OF      | F                   | ·                | •   |      | · · ·         |   |

|   |                  |                          |                        | 16 kHz<br>FBELP | 3                   | TBD              | _   | μΑ   | 0 to 70       | Т |

|   |                  |                          |                        | 16 kHz<br>FBELP | 3                   | TBD              | —   | μA   | -40 to<br>105 | Т |

| # | Parameter             | Condition                                                 |              | Tem          | perature     | (°C)         |               | Units | с |

|---|-----------------------|-----------------------------------------------------------|--------------|--------------|--------------|--------------|---------------|-------|---|

| # | Farameter             | Condition                                                 | -40          | 25           | 70           | 85           | 105           | Units | C |

| 1 | LPO                   | _                                                         | 50           | 75           | 100          | 150          | 250           | nA    | D |

| 2 | EREFSTEN              | RANGE = HGO = 0                                           | 600<br>(TBD) | 650<br>(TBD) | 750<br>(TBD) | 850<br>(TBD) | 1000<br>(TBD) | nA    | D |

| 3 | IREFSTEN <sup>1</sup> | —                                                         | 68           | 70           | 77           | 86           | 120           | μA    | Т |

| 4 | TOD                   | Does not include clock source<br>current                  | 50           | 75           | 100          | 150          | 250           | nA    | D |

| 5 | LVD <sup>1</sup>      | LVDSE = 1                                                 | 114          | 115          | 123          | 135          | 170           | μA    | Т |

| 6 | ACMP <sup>1</sup>     | Not using the bandgap<br>(BGBE = 0)                       | 18           | 20           | 23           | 33           | 65            | μA    | Т |

| 7 | ADC <sup>1</sup>      | ADLPC = ADLSMP = 1<br>Not using the bandgap<br>(BGBE = 0) | 75           | 85           | 100          | 115          | 165           | μA    | Т |

| 8 | DAC <sup>1</sup>      | High power mode; no load on<br>DACO                       | 500          | 500          | 500          | 500          | 500           | μA    | Т |

Table 11. Typical Stop Mode Adders

<sup>1</sup> Not available in stop2 mode.

# 2.7 PRACMP Electricals

| # | Characteristic                             | Symbol              | Min            | Typical | Max             | Unit | С |

|---|--------------------------------------------|---------------------|----------------|---------|-----------------|------|---|

| 1 | Supply voltage                             | V <sub>PWR</sub>    | 1.8            |         | 3.6             | V    | Ρ |

| 2 | Supply current (active) (PRG enabled)      | I <sub>DDACT1</sub> | —              | -       | 60              | μΑ   | С |

| 3 | Supply current (active) (PRG disabled)     | I <sub>DDACT2</sub> | —              | _       | 40              | μΑ   | С |

| 4 | Supply current (ACMP and PRG all disabled) | I <sub>DDDIS</sub>  | -              | _       | 2               | nA   | D |

| 5 | Analog input voltage                       | VAIN                | $V_{SS} - 0.3$ | _       | V <sub>DD</sub> | V    |   |

| 6 | Analog input offset voltage                | VAIO                | —              | 5       | 40              | mV   | Т |

| 7 | Analog comparator hysteresis               | V <sub>H</sub>      | 3.0            |         | 20.0            | mV   | Т |

| 8 | Analog input leakage current               | I <sub>ALKG</sub>   | —              | _       | 1               | nA   | D |

| 9 | Analog comparator initialization delay     | tAINIT              | _              | _       | 1.0             | μS   | Т |

#### Table 12. PRACMP Electrical Specifications

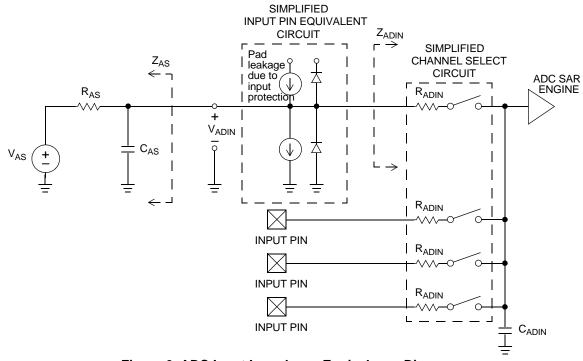

Figure 6. ADC Input Impedance Equivalency Diagram

| Table 16. 12-bit SAR ADC Characteristics full operating range                                                   |

|-----------------------------------------------------------------------------------------------------------------|

| (V <sub>REFH</sub> = V <sub>DDAD</sub> , > 1.8, V <sub>REFL</sub> = V <sub>SSAD</sub> $\leq$ 8 MHz) (Continued) |

| Characterist<br>ic        | Conditions <sup>1</sup>                              | Symb                    | Min | Typ <sup>2</sup>                  | Max          | Unit             | с | Comment                                                                      |

|---------------------------|------------------------------------------------------|-------------------------|-----|-----------------------------------|--------------|------------------|---|------------------------------------------------------------------------------|

| Zero-Scale<br>Error       | 12-bit single-ended mode                             | E <sub>ZS</sub>         |     | ±0.7                              | ±2.0         | LSB <sup>2</sup> | Т | V <sub>ADIN</sub> =<br>V <sub>SSAD</sub>                                     |

|                           | 11-bit differential mode<br>10-bit single-ended mode |                         |     | ±0.4<br>±0.4                      | ±1.0<br>±1.0 |                  | Т |                                                                              |

|                           | 9-bit differential mode<br>8-bit single-ended mode   |                         |     | ±0.2<br>±0.2                      | ±0.5<br>±0.5 |                  | Т |                                                                              |

| Full-Scale<br>Error       | 12-bit single-ended mode                             | E <sub>FS</sub>         |     | ±1.0                              | ±3.5         | LSB <sup>2</sup> | Т | V <sub>ADIN</sub> =<br>V <sub>DDAD</sub>                                     |

|                           | 11-bit differential mode<br>10-bit single-ended mode |                         |     | ±0.4<br>±0.4                      | ±1.5<br>±1.5 |                  | Т |                                                                              |

|                           | 9-bit differential mode<br>8-bit single-ended mode   |                         |     | ±0.2<br>±0.2                      | ±0.5<br>±0.5 |                  | Т |                                                                              |

| Quantization<br>Error     | All modes                                            | E <sub>Q</sub>          | _   | _                                 | ±0.5         | LSB <sup>2</sup> | D |                                                                              |

| Input<br>Leakage<br>Error | all modes                                            | E <sub>IL</sub>         |     | I <sub>In</sub> * R <sub>AS</sub> |              | mV               | D | I <sub>In</sub> = leakage<br>current<br>(refer to DC<br>characteristi<br>cs) |

| Temp Sensor<br>Slope      | −40°C − 25°C                                         | m                       | _   | 1.646                             | —            | mV/×<br>C        | С |                                                                              |

|                           | 25°C – 125°C                                         |                         | —   | 1.769                             | —            |                  |   |                                                                              |

| Temp Sensor<br>Voltage    | 25°C                                                 | V <sub>TEMP2</sub><br>5 | _   | 701.2                             | _            | mV               | С |                                                                              |

<sup>1</sup> All accuracy numbers assume the ADC is calibrated with V<sub>REFH</sub>=V<sub>DDAD</sub>

<sup>2</sup> Typical values assume V<sub>DDAD</sub> = 3.0V, Temp = 25°C, f<sub>ADCK</sub>=2.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>3</sup> 1 LSB = (V<sub>REFH</sub> - V<sub>REFL</sub>)/2<sup>N</sup>

- <sup>3</sup> This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- <sup>4</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>BUS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval.

- <sup>5</sup> 625 ns represents 5 time quanta for CAN applications, under worst-case conditions of 8 MHz CAN bus clock, 1 Mbps CAN Bus speed, and 8 time quanta per bit for bit time settings. 5 time quanta is the minimum time between a synchronization edge and the sample point of a bit using 8 time quanta per bit.

- <sup>6</sup> Below D<sub>lock</sub> minimum, the MCG is guaranteed to enter lock. Above D<sub>lock</sub> maximum, the MCG will not enter lock. But if the MCG is already in lock, then the MCG may stay in lock.

- <sup>7</sup> Below D<sub>unl</sub> minimum, the MCG will not exit lock if already in lock. Above D<sub>unl</sub> maximum, the MCG is guaranteed to exit lock.

| # | Char                                                        | acteristic                                                                                    | Symbol                           | Min                   | Typ <sup>1</sup> | Мах  | Unit  |

|---|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------|-----------------------|------------------|------|-------|

|   | Oscillator crystal or resonator<br>(EREFS = 1, ERCLKEN = 1) | • Low range (RANGE = 0)                                                                       | f <sub>lo</sub>                  | 32                    | _                | 38.4 | kHz   |

|   |                                                             | <ul> <li>High range (RANGE = 1),</li> <li>FEE or FBE mode <sup>2</sup></li> </ul>             | fhi                              | 1                     | —                | 5    | MHz   |

| 1 |                                                             | <ul> <li>High range (RANGE = 1),</li> <li>High gain (HGO = 1),</li> <li>FBELP mode</li> </ul> | fhi                              | 1                     | _                | 16   | MHz   |

|   |                                                             | <ul> <li>High range (RANGE = 1),</li> <li>Low power (HGO = 0),</li> <li>FBELP mode</li> </ul> | fhi                              | 1                     | _                | 8    | MHz   |

| 2 | Load capacitors                                             |                                                                                               | C <sub>1</sub><br>C <sub>2</sub> | See Note <sup>3</sup> |                  |      |       |

| 3 | Feedback resistor                                           | Low range<br>(32 kHz to 38.4 kHz)                                                             | R <sub>F</sub>                   | _                     | 10               | _    | ΜΩ    |

| 3 |                                                             | High range<br>(1 MHz to 16 MHz)                                                               | —                                | _                     | 1                | —    | 10122 |

| 4 | Series resistor — Low range                                 | Low Gain (HGO = 0)                                                                            | R <sub>S</sub>                   |                       | 0                | _    | kΩ    |

| 4 |                                                             | High Gain (HGO = 1)                                                                           |                                  |                       | 100              |      |       |

|   | Series resistor — High range                                | • Low Gain (HGO = 0)                                                                          |                                  |                       |                  |      |       |

|   |                                                             | <ul> <li>High Gain (HGO = 1)</li> </ul>                                                       |                                  |                       |                  |      |       |

| 5 |                                                             | ≥ 8 MHz                                                                                       | R <sub>S</sub>                   | —                     | 0                | 0    | kΩ    |

|   |                                                             | 4 MHz                                                                                         |                                  | —                     | 0                | 10   |       |

|   |                                                             | 1 MHz                                                                                         |                                  | _                     | 0                | 20   |       |

#### Table 18. XOSC (Temperature Range = -40 to 105°C Ambient)

| # | Ch                                    | Characteristic                               |                   |   | Typ <sup>1</sup> | Max | Unit |

|---|---------------------------------------|----------------------------------------------|-------------------|---|------------------|-----|------|

|   | Crystal start-up time <sup>4, 5</sup> | Low range, low gain (RANGE = 0,<br>HGO = 0)  | t<br>CSTL         | _ | 200              | _   |      |

| 6 |                                       | Low range, high gain (RANGE = 0, HGO = 1)    |                   | _ | 400              | _   |      |

| 0 |                                       | High range, low gain (RANGE = 1,<br>HGO = 0) | t <sub>CSTH</sub> | _ | 5                | _   | ms   |

|   |                                       | High range, high gain (RANGE = 1, HGO = 1)   |                   |   | 15               |     |      |

#### Table 18. XOSC (Temperature Range = -40 to 105°C Ambient)

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25°C or is typical recommended value.

<sup>2</sup> When MCG is configured for FEE or FBE mode, input clock source must be divisible using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

<sup>3</sup> See crystal or resonator manufacturer's recommendation.

<sup>4</sup> This parameter is characterized and not tested on each device.

<sup>5</sup> Proper PC board layout procedures must be followed to achieve specifications.

| # | Symbol                                | Parameter                                                      |                                                 | Min | Typical <sup>1</sup> | Max | С | Unit |  |

|---|---------------------------------------|----------------------------------------------------------------|-------------------------------------------------|-----|----------------------|-----|---|------|--|

| 9 | t <sub>Rise</sub> , t <sub>Fall</sub> | Port rise and fall time $(load = 50 \text{ pF})^4$ , Low Drive |                                                 |     |                      |     |   |      |  |

|   |                                       |                                                                | Slew rate<br>control<br>disabled<br>(PTxSE = 0) | _   | 11                   | _   | D |      |  |

|   |                                       |                                                                | Slew rate<br>control<br>enabled<br>(PTxSE = 1)  | _   | 35                   |     | D |      |  |

|   |                                       |                                                                | Slew rate<br>control<br>disabled<br>(PTxSE = 0) | _   | 40                   | _   | D |      |  |

|   |                                       |                                                                | Slew rate<br>control<br>enabled<br>(PTxSE = 1)  | _   | 75                   |     | D |      |  |

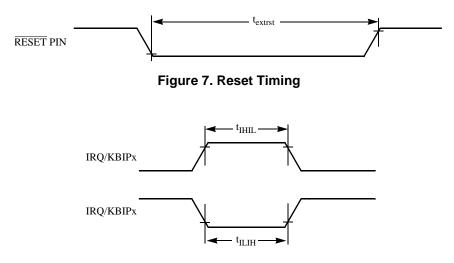

#### Table 19. Control Timing

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0 V, 25 °C unless otherwise stated.

<sup>2</sup> This is the shortest pulse that is guaranteed to be recognized as a reset pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

<sup>3</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^4$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40 °C to 105 °C.

Figure 8. IRQ/KBIPx Timing

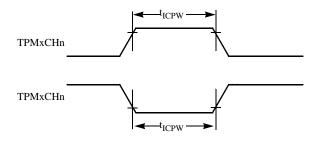

### 2.11.2 TPM Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

Table 20. TPM Input Timing

| # | С | Function                  | Symbol              | Min | Мах                 | Unit             |

|---|---|---------------------------|---------------------|-----|---------------------|------------------|

| 1 | — | External clock frequency  | f <sub>TPMext</sub> | dc  | f <sub>Bus</sub> /4 | MHz              |

| 2 | — | External clock period     | t <sub>TPMext</sub> | 4   | —                   | t <sub>cyc</sub> |

| 3 | D | External clock high time  | t <sub>clkh</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| 4 | D | External clock low time   | t <sub>clkl</sub>   | 1.5 | —                   | t <sub>cyc</sub> |

| 5 | D | Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

Figure 9. Timer External Clock

Figure 10. Timer Input Capture Pulse

## 2.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal V<sub>DD</sub> supply. For more detailed information about program/erase operations, see the Memory chapter in the Reference Manual for this device (MC9S08JE128RM).

| #  | Characteristic                                                                                        | Symbol                                                            | Min    | Typical | Мах               | Unit              | С |

|----|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------|---------|-------------------|-------------------|---|

| 1  | Supply voltage for program/erase<br>-40°C to 105°C                                                    | V <sub>prog/erase</sub>                                           | 1.8    | _       | 3.6               | V                 | D |

| 2  | Supply voltage for read operation                                                                     | V <sub>Read</sub>                                                 | 1.8    | —       | 3.6               | V                 | D |

| 3  | Internal FCLK frequency <sup>1</sup>                                                                  | f <sub>FCLK</sub>                                                 | 150    | —       | 200               | kHz               | D |

| 4  | Internal FCLK period (1/FCLK)                                                                         | t <sub>Fcyc</sub>                                                 | 5      | —       | 6.67              | μS                | D |

| 5  | Byte program time (random location) <sup>2</sup>                                                      | e program time (random location) <sup>2</sup> t <sub>prog</sub> 9 |        |         | t <sub>Fcyc</sub> | Р                 |   |

| 6  | Byte program time (burst mode) <sup>2</sup>                                                           | t <sub>Burst</sub>                                                |        | 4       |                   |                   | Р |

| 7  | Page erase time <sup>2</sup>                                                                          | t <sub>Page</sub>                                                 |        | 4000    |                   | t <sub>Fcyc</sub> | Р |

| 8  | Mass erase time <sup>2</sup>                                                                          | t <sub>Mass</sub>                                                 |        | 20,000  |                   | t <sub>Fcyc</sub> | Р |

| 9  | Program/erase endurance <sup>3</sup><br>$T_L$ to $T_H = -40^{\circ}C$ to + 105°C<br>$T = 25^{\circ}C$ |                                                                   | 10,000 |         | _                 | cycles            | С |

| 10 | Data retention <sup>4</sup>                                                                           | t <sub>D_ret</sub>                                                | 15     | 100     |                   | years             | С |

#### Table 22. Flash Characteristics

<sup>1</sup> The frequency of this clock is controlled by a software setting.

<sup>2</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>3</sup> **Typical endurance for flash** was evaluated for this product family on the HC9S12Dx64. For additional information on how Freescale defines typical endurance, please refer to Engineering Bulletin EB619, *Typical Endurance for Nonvolatile Memory*.

<sup>4</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines typical data retention, please refer to Engineering Bulletin EB618, *Typical Data Retention for Nonvolatile Memory.*

## 2.14 USB Electricals

The USB electricals for the USB On-the-Go module conform to the standards documented by the Universal Serial Bus Implementers Forum. For the most up-to-date standards, visit http://www.usb.org.

If the Freescale USB On-the-Go implementation has electrical characteristics that deviate from the standard or require additional information, this space would be used to communicate that information.

| # | Characteristic                                       | Symbol               | Min | Тур | Max | Unit | С |

|---|------------------------------------------------------|----------------------|-----|-----|-----|------|---|

| 1 | Regulator operating voltage                          | V <sub>regin</sub>   | 3.9 | —   | 5.5 | V    | С |

| 2 | VREG output                                          | V <sub>regout</sub>  | 3   | 3.3 | 3.6 | V    | Р |

| 3 | V <sub>USB33</sub> input with internal VREG disabled | V <sub>usb33in</sub> | 3   | 3.3 | 3.6 | V    | С |

| 4 | VREG Quiescent Current                               | I <sub>VRQ</sub>     |     | 0.5 |     | mA   | С |

#### Table 23. Internal USB 3.3 V Voltage Regulator Characteristics

# 2.15 VREF Electrical Specifications

Table 24. VREF Electrical Specifications

| Num | Characteristic                                                    | Symbol           | Min   | Мах         | Unit            | С |

|-----|-------------------------------------------------------------------|------------------|-------|-------------|-----------------|---|

| 1   | Supply voltage                                                    | V <sub>DDA</sub> | 1.80  | 3.6         | V               | С |

| 2   | Temperature                                                       | T <sub>A</sub>   | -40   | 105         | °C              | С |

| 3   | Output Load Capacitance                                           | CL               | _     | 100         | nf              | D |

| 4   | Maximum Load                                                      |                  | _     | 10          | mA              | — |

| 5   | Voltage Reference Output with Factory Trim. $V_{DD} = 3 V$ .      | Vout             | 1.140 | 1.160       | V               | Р |

| 6   | Temperature Drift (Vmin - Vmax across the full temperature range) | Tdrift           | -     | 10<br>(TBD) | mV <sup>1</sup> | Т |

| 7   | Aging Coefficient                                                 | Ac               | _     | TBD         | ppm/year        | С |

| 8   | Powered down Current (Off Mode,<br>VREFEN=0, VRSTEN=0)            | I                | -     | 0.10        | μA              | С |

| 9   | Bandgap only (MODE_LV[1:0] = 00)                                  | I                | —     | 75          | μΑ              | Т |

| 10  | Low-Power buffer (MODE_LV[1:0] = 01)                              | I                | _     | 125         | μΑ              | Т |

| 11  | Tight-Regulation buffer (MODE_LV[1:0]<br>= 10)                    | I                | -     | 1.1         | mA              | Т |

| 12  | Load Regulation MODE_LV = 10                                      |                  | —     | 100         | μV/mA           | С |

| 13  | Line Regulation (Power Supply                                     | DC               | —     | TBD         | mV              | С |

| 14  | Rejection)                                                        | AC               | TBD   |             | dB              |   |

<sup>1</sup> See typical chart below.

#### Table 25. VREF Limited Range Operating Requirements

| # | Characteristic | Symbol         | Min | Мах | Unit | С | Notes |

|---|----------------|----------------|-----|-----|------|---|-------|

| 1 | Temperature    | T <sub>A</sub> | 0   | 50  | °C   | С |       |

#### Table 26. VREF Limited Range Operating Behaviors

| # | Characteristic                                | Symbol | Min | Мах | Unit | С | Notes |

|---|-----------------------------------------------|--------|-----|-----|------|---|-------|

| 1 | Voltage Reference Output with<br>Factory Trim | Vout   | TBD | TBD | μA   | С |       |

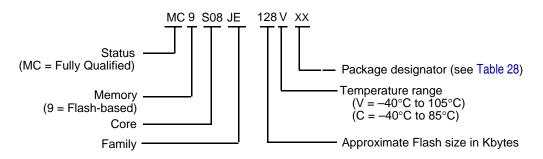

**Ordering Information**

### 3.1 Device Numbering System

Example of the device numbering system:

#### Table 27. Device Numbering System

| Device Number <sup>1</sup> | Men     | nory   | Available Packages <sup>2</sup> |  |

|----------------------------|---------|--------|---------------------------------|--|

| Device Number              | Flash   | RAM    | Available Fackages              |  |

|                            | 131,072 | 12,288 | 64 LQFP                         |  |

| MC9S08JE128                | 131,072 | 12,288 | 80 LQFP                         |  |

|                            | 131,072 | 12,288 | 81 MAPBGA                       |  |

| MC9S08JE64                 | 65,536  | 12,288 | 64 LQFP                         |  |

<sup>1</sup> See Table 2 for a complete description of modules included on each device.

<sup>2</sup> See Table 28 for package information.

### 3.2 Package Information

#### Table 28. Package Descriptions

| Pin Count | Package Type          | Abbreviation | Designator | Case No. | Document No. |

|-----------|-----------------------|--------------|------------|----------|--------------|

| 64        | Low Quad Flat Package | LQFP         | LH         | 840F-02  | 98ASS23234W  |

| 80        | Low Quad Flat Package | LQFP         | LK         | 917-01   | 98ASS23174W  |

| 81        | MAPBGA Package        | Map PBGA     | MB         | 1662-01  | 98ASA10670D  |

### 3.3 Mechanical Drawings

Table 28 provides the available package types and their document numbers. The latest package outline/mechanical drawings are available on the MC9S08JE128 series Product Summary pages at http://www.freescale.com.

To view the latest drawing, either:

- Click on the appropriate link in Table 28, or

- Open a browser to the Freescale<sup>®</sup> website (http://www.freescale.com), and enter the appropriate document number (from Table 28) in the "Enter Keyword" search box at the top of the page.