Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 48MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, USB                             |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 46                                                          |

| Program Memory Size        | 128KB (128K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | ·                                                           |

| RAM Size                   | 12K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                 |

| Data Converters            | A/D 8x12b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 80-LQFP                                                     |

| Supplier Device Package    | 80-LQFP (12x12)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08je128vlk |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Devices in the MC9S08JE128 series

The following table summarizes the feature set available in the MC9S08JE128 series of MCUs.

| Feature                                     | МС | 9S08JE | 128 | MC9S08JE64 |

|---------------------------------------------|----|--------|-----|------------|

| Pin quantity                                | 81 | 80     | 64  | 64         |

| FLASH size (bytes)                          |    | 131072 |     | 65535      |

| RAM size (bytes)                            |    | 12K    |     | 12K        |

| Programmable Analog Comparator (PRACMP)     |    | yes    |     | yes        |

| Debug Module (DBG)                          |    | yes    |     | yes        |

| Multipurpose Clock Generator (MCG)          |    | yes    |     | yes        |

| Inter-Integrated Communication (IIC)        |    | yes    |     | yes        |

| Interrupt Request Pin (IRQ)                 |    | yes    |     | yes        |

| Keyboard Interrupt (KBI)                    | 16 | 16     | 7   | 7          |

| Port I/O <sup>1</sup>                       | 47 | 46     | 33  | 33         |

| Dedicated Analog Input Pins                 |    | 12     |     | 12         |

| Power and Ground Pins                       |    | 8      |     | 8          |

| Time Of Day (TOD)                           |    | yes    |     | yes        |

| Serial Communications (SCI1)                |    | yes    |     | yes        |

| Serial Communications (SCI2)                |    | yes    |     | yes        |

| Serial Peripheral Interface 1 (SPI1 (FIFO)) |    | yes    |     | yes        |

| Serial Peripheral Interface 2 (SPI2)        |    | yes    |     | yes        |

| Carrier Modulator Timer pin (IRO)           |    | yes    |     | yes        |

| TPM input clock pin (TPMCLK)                |    | yes    |     | yes        |

| TPM1 channels                               |    | 4      |     | 4          |

| TPM2 channels                               | 4  | 4      | 2   | 2          |

| XOSC1                                       |    | yes    |     | yes        |

| XOSC2                                       |    | yes    |     | yes        |

| USB                                         |    | yes    |     | yes        |

| Programmable Delay Block (PDB)              |    | yes    |     | yes        |

| SAR ADC differential channels <sup>2</sup>  | 4  | 4      | 3   | 3          |

| SAR ADC single-ended channels               | 8  | 8      | 6   | 6          |

| Voltage reference output pin (VREFO)        |    | yes    |     | yes        |

### Table 1. MC9S08JE128 series Features by MCU and Package

<sup>1</sup> Port I/O count does not include two (2) output-only and one (1) input-only pins.

<sup>2</sup> Each differential channel is comprised of 2 pin inputs.

#### Devices in the MC9S08JE128 series

A complete description of the modules included on each device is provided in the following table.

| Module                                  | Version |

|-----------------------------------------|---------|

| Analog-to-Digital Converter (ADC12)     | 1       |

| Digital to Analog Converter (DAC)       | 1       |

| Programmable Delay Block                | 1       |

| Inter-Integrated Circuit (IIC)          | 3       |

| Central Processing Unit (CPU)           | 5       |

| On-Chip In-Circuit Debug/Emulator (DBG) | 3       |

| Multi-Purpose Clock Generator (MCG)     | 3       |

| Low Power Oscillator (XOSCVLP)          | 1       |

| Carrier Modulator Timer (CMT)           | 1       |

| Programable Analog Comparator (PRACMP)  | 1       |

| Serial Communications Interface (SCI)   | 4       |

| Serial Peripheral Interface (SPI)       | 5       |

| Time of Day (TOD)                       | 1       |

| Universal Serial Bus (USB)              | 1       |

| Timer Pulse-Width Modulator (TPM)       | 3       |

| System Integration Module (SIM)         | 1       |

| Cyclic Redundancy Check (CRC)           | 3       |

| Keyboard Interrupt (KBI)                | 2       |

| Voltage Reference (VREF)                | 1       |

| Voltage Regulator (VREG)                | 1       |

| Interrupt Request (IRQ)                 | 3       |

| Flash Wrapper                           | 1       |

| GPIO                                    | 2       |

| Port Control                            | 1       |

Table 2. Versions of On-Chip Modules

The block diagram in Figure 1 shows the structure of the MC9S08JE128 series MCU.

Devices in the MC9S08JE128 series

### 1.1 Pin Assignments

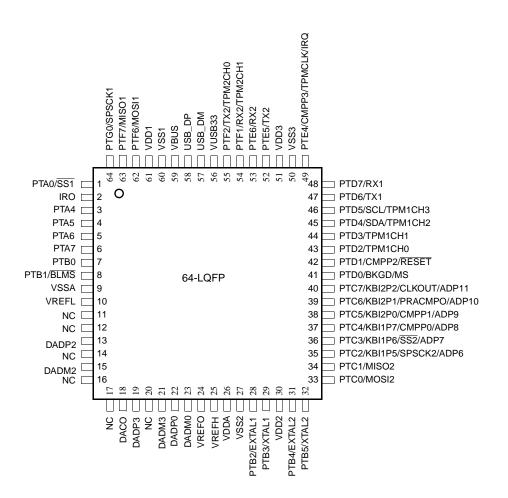

This section shows the pin assignments for the MC9S08JE128 series devices.

### 1.1.1 64-Pin LQFP

The following two figures show the 64-pin LQFP pinout configuration.

Figure 2. 64-Pin LQFP

# 1.2 Pin Assignments by Packages

| Pa        | ackag   | е       |                     |        |      |      |                      |

|-----------|---------|---------|---------------------|--------|------|------|----------------------|

| 81 MAPBGA | 80 LQFP | 64 LQFP | Default<br>Function | ALT1   | ALT2 | ALT3 | Composite Pin Name   |

| B2        | 1       | 1       | PTA0                | SS1    | _    | _    | PTA0/SS1             |

| A1        | 2       | 2       | IRO                 | _      | _    | -    | IRO                  |

| C4        | 3       |         | PTA1                | KBI1P0 | TX1  | _    | PTA1/KBI1P0/TX1      |

| D5        | 4       |         | PTA2                | KBI1P1 | RX1  | ADP4 | PTA2/KBI1P1/RX1/ADP4 |

| D6        | 5       |         | PTA3                | KBI1P2 | ADP5 | _    | PTA3/KBI1P2/ADP5     |

| C1        | 6       | 3       | PTA4                | _      |      | _    | PTA4                 |

| C2        | 7       | 4       | PTA5                | _      | _    |      | PTA5                 |

| C3        | 8       | 5       | PTA6                | _      | _    | _    | PTA6                 |

| D2        | 9       | 6       | PTA7                | _      | _    |      | PTA7                 |

| D3        | 10      | 7       | PTB0                | _      |      |      | PTB0                 |

| D4        | 11      | 8       | PTB1                | BLMS   | _    | _    | PTB1/BLMS            |

| J1        | 12      | 9       | VSSA                | _      | _    | _    | VSSA                 |

| J2        | 13      | 10      | VREFL               | _      | _    | _    | VREFL                |

| D1        | 14      | 11      | NC                  |        | _    | _    | NC                   |

| E1        | 15      | 12      | NC                  | _      | _    | _    | NC                   |

| F2        | 16      | 13      | DADP2               |        | _    | _    | DADP2                |

| F1        | 17      | 14      | NC                  | _      | _    |      | NC                   |

| E2        | 18      | 15      | DADM2               |        | _    | _    | DADM2                |

| F3        | 19      | 16      | NC                  | _      | _    | _    | NC                   |

| E3        | 20      | 17      | NC                  | _      | _    | _    | NC                   |

| G2        | 21      | 18      | DACO                | _      | _    | _    | DACO                 |

| G3        | 22      | 19      | DADP3               | _      | _    | _    | DADP3                |

| H4        | 23      | 20      | NC                  | —      | _    | _    | NC                   |

| G4        | 24      | 21      | DADM3               | _      | _    | _    | DADM3                |

| G1        | 25      | 22      | DADP0               |        |      | _    | DADP0                |

| H1        | 26      | 23      | DADM0               | _      | _    | _    | DADM0                |

| G5        | 27      | 24      | VREFO               | _      | _    | _    | VREFO                |

| H3        | 28      |         | DADP1               |        | _    | _    | DADP1                |

| H2        | 29      | —       | DADM1               | _      | _    | _    | DADM1                |

| Table 3 | Table 3. Package Pin Assignments |  |  |  |  |  |  |  |  |  |

|---------|----------------------------------|--|--|--|--|--|--|--|--|--|

|         |                                  |  |  |  |  |  |  |  |  |  |

# 2.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in the following table may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

| # | Rating                                                                                          | Symbol           | Value                         | Unit |

|---|-------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| 1 | Supply voltage                                                                                  | V <sub>DD</sub>  | -0.3 to +3.8                  | V    |

| 2 | Maximum current into V <sub>DD</sub>                                                            | I <sub>DD</sub>  | 120                           | mA   |

| 3 | Digital input voltage                                                                           | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| 4 | Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | ۱ <sub>D</sub>   | ± 25                          | mA   |

| 5 | Storage temperature range                                                                       | T <sub>stg</sub> | -55 to 150                    | °C   |

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}.$

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ).

# 2.5 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

| Num | Symbol           | Char                   | acteristic                                 | Condition                                                                        | Min                       | Typ <sup>1</sup> | Мах | Unit | С |

|-----|------------------|------------------------|--------------------------------------------|----------------------------------------------------------------------------------|---------------------------|------------------|-----|------|---|

| 1   | V <sub>DD</sub>  | Operating<br>Voltage   |                                            |                                                                                  | 1.8 <sup>2</sup>          | _                | 3.6 | V    | _ |

| 2   | V <sub>OH</sub>  | Output high<br>voltage | All I/O pins, low-o                        | drive strength                                                                   |                           |                  |     |      |   |

|     |                  |                        |                                            | 1.8 V, I <sub>Load</sub><br>= -600 μA                                            | V <sub>DD</sub> –<br>0.5  | _                | —   | V    | С |

|     |                  |                        | All I/O pins, high-                        | -drive strengtl                                                                  | h                         |                  |     |      |   |

|     |                  |                        |                                            | 2.7 V, I <sub>Load</sub><br>= -10 mA                                             | V <sub>DD</sub> –<br>0.5  | _                | _   | V    | Ρ |

|     |                  |                        |                                            | 1.8V, $I_{Load} =$<br>-3 mA                                                      | V <sub>DD</sub> –<br>0.5  | _                | _   | V    | С |

| 3   | I <sub>OHT</sub> | Output high<br>current | Max total I <sub>OH</sub> for              | all ports                                                                        |                           |                  |     |      |   |

|     |                  |                        |                                            | —                                                                                | —                         | _                | 100 | mA   | D |

| 4   | V <sub>OL</sub>  | Output low<br>voltage  | All I/O pins, low-o                        | All I/O pins, low-drive strength                                                 |                           |                  |     |      |   |

|     |                  |                        |                                            | 1.8 V, I <sub>Load</sub><br>= 600 μA                                             | _                         |                  | 0.5 | V    | С |

|     |                  |                        | All I/O pins, high-                        | -drive strengtl                                                                  | h                         |                  |     | J    |   |

|     |                  |                        |                                            | 2.7 V, I <sub>Load</sub><br>= 10 mA                                              | _                         |                  | 0.5 | V    | Ρ |

|     |                  |                        |                                            | 1.8 V, I <sub>Load</sub><br>= 3 mA                                               |                           | -                | 0.5 | V    | С |

| 5   | I <sub>OLT</sub> | Output low current     | Max total I <sub>OL</sub><br>for all ports | —                                                                                | _                         | _                | 100 | mA   | D |

| 6   | V <sub>IH</sub>  | Input high volta       | ge all digital inputs                      |                                                                                  |                           |                  |     |      |   |

|     |                  |                        |                                            | all digital<br>inputs,<br>V <sub>DD</sub> > 2.7 V                                | 0.70 x<br>V <sub>DD</sub> |                  | —   | V    | Ρ |

|     |                  |                        |                                            | all digital inputs, $2.7 \text{ V} > \text{V}_{\text{DD}} \\ \geq 1.8 \text{ V}$ | 0.85 x<br>V <sub>DD</sub> |                  | _   | V    | Ρ |

### **Table 9. DC Characteristics**

| Num | Symbol              | Chara                                                             | cteristic                 | Condition | Min  | Typ <sup>1</sup> | Мах  | Unit | С |

|-----|---------------------|-------------------------------------------------------------------|---------------------------|-----------|------|------------------|------|------|---|

| 20  | V <sub>LVDH</sub> 9 | Low-voltage<br>detection<br>threshold —<br>high range             | V <sub>DD</sub> falling   | 1         | L    |                  |      |      |   |

|     |                     |                                                                   |                           |           | 2.11 | 2.16             | 2.22 | V    | Р |

|     |                     |                                                                   | V <sub>DD</sub> rising    |           |      |                  |      |      |   |

|     |                     |                                                                   |                           | _         | 2.16 | 2.23             | 2.27 | V    | Р |

| 21  | V <sub>LVDL</sub>   | Low-voltage<br>detection<br>threshold —<br>low range <sup>9</sup> | V <sub>DD</sub> falling   |           |      |                  |      |      |   |

|     |                     |                                                                   |                           |           | 1.80 | 1.84             | 1.88 | V    | Ρ |

|     |                     |                                                                   | $V_{DD}$ rising           |           |      |                  |      |      |   |

|     |                     |                                                                   |                           |           | 1.88 | 1.93             | 1.96 | V    | Р |

| 22  | V <sub>LVWH</sub>   | Low-voltage<br>warning<br>threshold —<br>high range <sup>9</sup>  | V <sub>DD</sub> falling   |           |      |                  |      |      |   |

|     |                     |                                                                   |                           | _         | 2.36 | 2.46             | 2.56 | V    | Р |

|     |                     |                                                                   | $V_{DD}$ rising           |           |      |                  |      |      |   |

|     |                     |                                                                   |                           | _         | 2.36 | 2.46             | 2.56 | V    | Р |

| 23  | V <sub>LVWL</sub>   | Low-voltage<br>warning<br>threshold —<br>low range <sup>9</sup>   | V <sub>DD</sub> falling   |           |      |                  |      |      |   |

|     |                     |                                                                   |                           | _         | 2.11 | 2.16             | 2.22 | V    | Р |

|     |                     |                                                                   | V <sub>DD</sub> rising    |           | •    |                  |      | ·    |   |

|     |                     |                                                                   |                           |           | 2.16 | 2.23             | 2.27 | V    | Р |

| 24  | V <sub>hys</sub>    | Low-voltage inhi<br>hysteresis <sup>10</sup>                      | bit reset/recover         | _         | _    | 50               | —    | mV   | С |

| 25  | $V_{BG}$            | Bandgap Voltag                                                    | e Reference <sup>11</sup> | —         | 1.15 | 1.17             | 1.18 | V    | Р |

### Table 9. DC Characteristics (Continued)

<sup>1</sup> Typical values are measured at 25°C. Characterized, not tested

<sup>2</sup> As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above V<sub>LVDL</sub>.

<sup>3</sup> Total Leakage current is the sum value for all GPIO pins; this leakage current is not distributed evenly across all pins but characterization data shows that individual pin leakage current maximums are less than 250 nA.

<sup>4</sup> Measured with  $V_{In} = V_{DD}$ .

$^5\,$  All functional non-supply pins are internally clamped to V\_{SS} and V\_{DD}.

<sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>7</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

- <sup>8</sup> Maximum is highest voltage that POR is guaranteed.

- <sup>9</sup> Run at 1 MHz bus frequency

- <sup>10</sup> Low voltage detection and warning limits measured at 1 MHz bus frequency.

- <sup>11</sup> Factory trimmed at  $V_{DD} = 3.0$  V, Temp = 25°C

| # | Symbol            | Parameter                                    | Bus<br>Freq | V <sub>DD</sub> (V) | Typ <sup>1</sup> | Max | Unit | <b>Temp</b><br>(°C) | С |

|---|-------------------|----------------------------------------------|-------------|---------------------|------------------|-----|------|---------------------|---|

| 5 | WI <sub>DD</sub>  | Wait mode FEI mode,<br>supply cur-<br>rent   | all modules | OFF                 |                  | 1   | 1    | 1 1                 |   |

|   |                   |                                              | 24 MHz      | 3                   | TBD              | 6   | mA   | -40 to<br>105       | С |

|   |                   |                                              | 20 MHz      | 3                   | TBD              | _   | mA   | -40 to<br>105       | Т |

|   |                   |                                              | 8 MHz       | 3                   | TBD              | _   | mA   | -40 to<br>105       | Ţ |

|   |                   |                                              | 1 MHz       | 3                   | TBD              | _   | mA   | -40 to<br>105       | Т |

| 6 | S2I <sub>DD</sub> | Stop2mode<br>supply cur-<br>rent             |             |                     |                  |     |      |                     |   |

|   |                   |                                              | N/A         | 3                   | 0.39             | 0.6 | μA   | -40 to<br>25        | Р |

|   |                   |                                              | N/A         | 3                   | TBD              | TBD | μA   | 70                  | С |

|   |                   |                                              | N/A         | 3                   | 7                | TBD | μA   | 85                  | С |

|   |                   |                                              | N/A         | 3                   | 16               | TBD | μA   | 105                 | Р |

|   |                   |                                              | N/A         | 2                   | TBD              | TBD | μA   | -40 to<br>25        | С |

|   |                   |                                              | N/A         | 2                   | TBD              | TBD | μA   | 70                  | С |

|   |                   |                                              | N/A         | 2                   | TBD              | TBD | μA   | 85                  | С |

|   |                   |                                              | N/A         | 2                   | TBD              | TBD | μA   | 105                 | С |

| 7 | S3I <sub>DD</sub> | Stop3mode No clocks a<br>supply cur-<br>rent | active      |                     |                  |     |      |                     |   |

|   |                   |                                              | N/A         | 3                   | 0.55             | 0.9 | μA   | -40 to<br>25        | Р |

|   |                   |                                              | N/A         | 3                   | TBD              | TBD | μA   | 70                  | С |

|   |                   |                                              | N/A         | 3                   | 14               | TBD | μΑ   | 85                  | С |

|   |                   |                                              | N/A         | 3                   | 37               | TBD | μΑ   | 105                 | Р |

|   |                   |                                              | N/A         | 2                   | TBD              | TBD | μA   | -40 to<br>25        | С |

|   |                   |                                              | N/A         | 2                   | TBD              | TBD | μΑ   | 70                  | С |

|   |                   |                                              | N/A         | 2                   | 14               | TBD | μA   | 85                  | С |

|   |                   |                                              | N/A         | 2                   | TBD              | TBD | μA   | 105                 | С |

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25°C or is typical recommended value.

| # | Parameter             | rameter Condition                                         |              |              | Units        | с            |               |       |   |

|---|-----------------------|-----------------------------------------------------------|--------------|--------------|--------------|--------------|---------------|-------|---|

| # | Farameter             | Condition                                                 | -40          | 25           | 70           | 85           | 105           | Units | C |

| 1 | LPO                   | _                                                         | 50           | 75           | 100          | 150          | 250           | nA    | D |

| 2 | EREFSTEN              | RANGE = HGO = 0                                           | 600<br>(TBD) | 650<br>(TBD) | 750<br>(TBD) | 850<br>(TBD) | 1000<br>(TBD) | nA    | D |

| 3 | IREFSTEN <sup>1</sup> | —                                                         | 68           | 70           | 77           | 86           | 120           | μA    | Т |

| 4 | TOD                   | Does not include clock source<br>current                  | 50           | 75           | 100          | 150          | 250           | nA    | D |

| 5 | LVD <sup>1</sup>      | LVDSE = 1                                                 | 114          | 115          | 123          | 135          | 170           | μA    | Т |

| 6 | ACMP <sup>1</sup>     | Not using the bandgap<br>(BGBE = 0)                       | 18           | 20           | 23           | 33           | 65            | μA    | Т |

| 7 | ADC <sup>1</sup>      | ADLPC = ADLSMP = 1<br>Not using the bandgap<br>(BGBE = 0) | 75           | 85           | 100          | 115          | 165           | μA    | Т |

| 8 | DAC <sup>1</sup>      | High power mode; no load on<br>DACO                       | 500          | 500          | 500          | 500          | 500           | μA    | Т |

Table 11. Typical Stop Mode Adders

<sup>1</sup> Not available in stop2 mode.

# 2.7 PRACMP Electricals

| # | Characteristic                             | Symbol              | Min            | Typical | Max             | Unit | С |

|---|--------------------------------------------|---------------------|----------------|---------|-----------------|------|---|

| 1 | Supply voltage                             | V <sub>PWR</sub>    | 1.8            |         | 3.6             | V    | Ρ |

| 2 | Supply current (active) (PRG enabled)      | I <sub>DDACT1</sub> | —              | -       | 60              | μΑ   | С |

| 3 | Supply current (active) (PRG disabled)     | I <sub>DDACT2</sub> | —              | _       | 40              | μΑ   | С |

| 4 | Supply current (ACMP and PRG all disabled) | I <sub>DDDIS</sub>  | -              | _       | 2               | nA   | D |

| 5 | Analog input voltage                       | VAIN                | $V_{SS} - 0.3$ | _       | V <sub>DD</sub> | V    |   |

| 6 | Analog input offset voltage                | VAIO                | —              | 5       | 40              | mV   | Т |

| 7 | Analog comparator hysteresis               | V <sub>H</sub>      | 3.0            |         | 20.0            | mV   | Т |

| 8 | Analog input leakage current               | I <sub>ALKG</sub>   | —              | _       | 1               | nA   | D |

| 9 | Analog comparator initialization delay     | tAINIT              | _              | _       | 1.0             | μS   | Т |

### Table 12. PRACMP Electrical Specifications

| #  | Characteristic                                 | Symbol                                | Min                 | Typical | Max             | Unit | С |

|----|------------------------------------------------|---------------------------------------|---------------------|---------|-----------------|------|---|

| 10 | Programmable reference generator inputs        | V <sub>In2</sub> (V <sub>DD25</sub> ) | 1.8                 | —       | 2.75            | V    |   |

| 11 | Programmable reference generator setup delay   | t <sub>PRGST</sub>                    | —                   | 1       | —               | μs   | D |

| 12 | Programmable reference generator step size     | Vstep                                 | -0.25               | 1       | 0.25            | LSB  | D |

| 13 | Programmable reference generator voltage range | Vprgout                               | V <sub>In</sub> /32 |         | V <sub>in</sub> | V    | Р |

### Table 12. PRACMP Electrical Specifications

# 2.8 12-bit DAC Electricals

| # | Characteristic          | Symbol            | Min  | Max | Unit | С | Notes                                                                                       |

|---|-------------------------|-------------------|------|-----|------|---|---------------------------------------------------------------------------------------------|

| 1 | Supply voltage          | V <sub>DDA</sub>  | 1.8  | 3.6 | V    | Р |                                                                                             |

| 2 | Reference voltage       | V <sub>DACR</sub> | 1.15 | 3.6 | V    | С |                                                                                             |

| 3 | Temperature             | T <sub>A</sub>    | -40  | 105 | °C   | С |                                                                                             |

| 4 | Output load capacitance | CL                | _    | 100 | pF   | с | A small load capacitance<br>(47 pF) can improve the<br>bandwidth performance<br>of the DAC. |

| 5 | Output load current     | ΙL                | —    | 1   | mA   | С |                                                                                             |

### Table 13. DAC 12LV Operating Requirements

| Characterist<br>ic            | Conditions <sup>1</sup>                              | Symb               | Min | Typ <sup>2</sup> | Max            | Unit             | с | Comment                                                      |

|-------------------------------|------------------------------------------------------|--------------------|-----|------------------|----------------|------------------|---|--------------------------------------------------------------|

| Supply                        | ADLPC=1, ADHSC=0                                     |                    | —   | 215              | —              |                  |   |                                                              |

| Current                       | ADLPC=0, ADHSC=0                                     | I <sub>DDAD</sub>  | _   | 470              | —              | μA               | т | ADLSMP=0<br>ADCO=1                                           |

|                               | ADLPC=0, ADHSC=1                                     |                    | _   | 610              | —              |                  |   |                                                              |

| Supply<br>Current             | Stop, Reset, Module Off                              | I <sub>DDAD</sub>  | —   | 0.01             | _              | μΑ               | С |                                                              |

| ADC                           | ADLPC=1, ADHSC=0                                     |                    | —   | 2.4              | —              |                  |   |                                                              |

| Asynchronou<br>s Clock        | ADLPC=0, ADHSC=0                                     | f <sub>ADACK</sub> | _   | 5.2              | —              | MHz              | Р | t <sub>ADACK</sub> =                                         |

| Source                        | ADLPC=0, ADHSC=1                                     |                    |     | 6.2              | —              |                  |   | 1/f <sub>ADACK</sub>                                         |

| Sample Time                   | See Block Guide for sample t                         | imes               |     |                  |                |                  |   |                                                              |

| Conversion<br>Time            | See Block Guide for conversi                         | on times           |     |                  |                |                  |   |                                                              |

| Total<br>Unadjusted<br>Error  | 12-bit single-ended mode                             | TUE                | _   | ±1.75            | ±3.5           | LSB <sup>3</sup> | Т | 32x<br>Hardware<br>Averaging<br>(AVGE = %1<br>AVGS =<br>%11) |

|                               | 11-bit differential mode<br>10-bit single-ended mode | -                  |     | ±0.7<br>±0.8     | ±1.5<br>±1.5   |                  | Т |                                                              |

|                               | 9-bit differential mode<br>8-bit single-ended mode   |                    |     | ±0.5<br>±0.5     | ±1.0<br>±1.0   |                  | Т |                                                              |

| Differential<br>Non-Linearity | 12-bit single-ended mode                             | DNL                | _   | ±0.7             | ±1             | LSB <sup>2</sup> | Т |                                                              |

|                               | 11-bit differential mode<br>10-bit single-ended mode |                    |     | ±0.5<br>±0.5     | ±0.75<br>±0.75 |                  | Т |                                                              |

|                               | 9-bit differential mode<br>8-bit single-ended mode   |                    |     | ±0.2<br>±0.2     | ±0.5<br>±0.5   |                  | Т |                                                              |

| Integral<br>Non-Linearity     | 12-bit single-ended mode                             | INL                | _   | ±1.0             | ±2.5           | LSB <sup>2</sup> | Т |                                                              |

|                               | 11-bit differential mode<br>10-bit single-ended mode |                    |     | ±0.5<br>±0.5     | ±1.0<br>±1.0   |                  | Т |                                                              |

|                               | 9-bit differential mode<br>8-bit single-ended mode   |                    |     | ±0.3<br>±0.3     | ±0.5<br>±0.5   |                  | Т |                                                              |

# Table 16. 12-bit SAR ADC Characteristics full operating range (V\_{REFH} = V\_{DDAD}, > 1.8, V\_{REFL} = V\_{SSAD} $\leq$ 8 MHz)

| Table 16. 12-bit SAR ADC Characteristics full operating range                                                   |

|-----------------------------------------------------------------------------------------------------------------|

| (V <sub>REFH</sub> = V <sub>DDAD</sub> , > 1.8, V <sub>REFL</sub> = V <sub>SSAD</sub> $\leq$ 8 MHz) (Continued) |

| Characterist<br>ic        | Conditions <sup>1</sup>                              | Symb                    | Min                               | Typ <sup>2</sup> | Max          | Unit             | с                                                                            | Comment                                  |

|---------------------------|------------------------------------------------------|-------------------------|-----------------------------------|------------------|--------------|------------------|------------------------------------------------------------------------------|------------------------------------------|

| Zero-Scale<br>Error       | 12-bit single-ended mode                             | E <sub>ZS</sub>         |                                   | ±0.7             | ±2.0         | LSB <sup>2</sup> | Т                                                                            | V <sub>ADIN</sub> =<br>V <sub>SSAD</sub> |

|                           | 11-bit differential mode<br>10-bit single-ended mode |                         |                                   | ±0.4<br>±0.4     | ±1.0<br>±1.0 |                  | Т                                                                            |                                          |

|                           | 9-bit differential mode<br>8-bit single-ended mode   |                         |                                   | ±0.2<br>±0.2     | ±0.5<br>±0.5 |                  | Т                                                                            |                                          |

| Full-Scale<br>Error       | 12-bit single-ended mode                             | E <sub>FS</sub>         |                                   | ±1.0             | ±3.5         | LSB <sup>2</sup> | Т                                                                            | V <sub>ADIN</sub> =<br>V <sub>DDAD</sub> |

|                           | 11-bit differential mode<br>10-bit single-ended mode |                         |                                   | ±0.4<br>±0.4     | ±1.5<br>±1.5 |                  | Т                                                                            |                                          |

|                           | 9-bit differential mode<br>8-bit single-ended mode   |                         |                                   | ±0.2<br>±0.2     | ±0.5<br>±0.5 |                  | Т                                                                            |                                          |

| Quantization<br>Error     | All modes                                            | E <sub>Q</sub>          | _                                 | _                | ±0.5         | LSB <sup>2</sup> | D                                                                            |                                          |

| Input<br>Leakage<br>Error | all modes                                            | E <sub>IL</sub>         | I <sub>In</sub> * R <sub>AS</sub> |                  | mV           | D                | I <sub>In</sub> = leakage<br>current<br>(refer to DC<br>characteristi<br>cs) |                                          |

| Temp Sensor<br>Slope      | −40°C − 25°C                                         | m                       | _                                 | 1.646            | —            | mV/×<br>C        | С                                                                            |                                          |

|                           | 25°C – 125°C                                         |                         | —                                 | 1.769            | —            |                  |                                                                              |                                          |

| Temp Sensor<br>Voltage    | 25°C                                                 | V <sub>TEMP2</sub><br>5 | _                                 | 701.2            | _            | mV               | С                                                                            |                                          |

<sup>1</sup> All accuracy numbers assume the ADC is calibrated with V<sub>REFH</sub>=V<sub>DDAD</sub>

<sup>2</sup> Typical values assume V<sub>DDAD</sub> = 3.0V, Temp = 25°C, f<sub>ADCK</sub>=2.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>3</sup> 1 LSB = (V<sub>REFH</sub> - V<sub>REFL</sub>)/2<sup>N</sup>

### 2.10 MCG and External Oscillator (XOSC) Characteristics

| #   | Rating                                                                        |                                                      | Symbol                            | Min    | Typical            | Мах                                                                       | Unit                | С |

|-----|-------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------|--------|--------------------|---------------------------------------------------------------------------|---------------------|---|

| 1   | Internal reference startup time                                               |                                                      | t <sub>irefst</sub>               | —      | 55                 | 100                                                                       | μS                  | D |

| 2   | Average internal reference frequency                                          | factory trimmed at<br>VDD=3.0 V and<br>temp=25°C     | f <sub>int_ft</sub>               | _      | 31.25              | _                                                                         | kHz                 | С |

|     |                                                                               | user trimmed                                         |                                   | 31.25  | _                  | 39.0625                                                                   |                     | С |

| 3   | DCO output frequency range -                                                  | Low range<br>(DRS=00)                                | - f <sub>dco_t</sub>              | 16     | —                  | 20                                                                        | MHz                 | С |

| 5   | trimmed                                                                       | Mid range<br>(DRS=01)                                | 'dco_t                            | 32     | —                  | 40                                                                        |                     | С |

|     |                                                                               | High range <sup>1</sup><br>(DRS=10)                  |                                   | 40     | —                  | 60                                                                        |                     | С |

| 4   | Resolution of trimmed DCO output fre-<br>quency at fixed voltage and tempera- | with FTRIM                                           | ∆f <sub>dco_res_t</sub>           | _      | ± 0.1              | ± 0.2                                                                     | %f <sub>dco</sub>   | С |

| 4   | ture                                                                          | without FTRIM                                        | <sup>∆</sup> 'dco_res_t           | —      | ± 0.2              | ± 0.4                                                                     | /0 <sup>r</sup> dco | С |

|     | Total deviation of trimmed DCO output                                         | over voltage and temperature                         |                                   | _      | ±1.0               | ±2                                                                        |                     | р |

| 5 1 | requency over voltage and tempera-<br>ure                                     | over fixed voltage<br>and temp range<br>of 0 - 70 °C | Δf <sub>dco_t</sub>               | _      | ± 0.5              | ± 1                                                                       | %f <sub>dco</sub>   | С |

| ~   | Acquisition time                                                              | FLL <sup>2</sup>                                     | t <sub>fll_acquire</sub>          | —      | —                  | 1                                                                         |                     | С |

| 6   | · · · · · · · · · · · · · · · · · · ·                                         | PLL <sup>3</sup>                                     | t <sub>pll_acquire</sub>          | —      | —                  | 1                                                                         | ms                  | D |

| 7   | Long term Jitter of DCO output clock (a interval) $^4$                        | averaged over 2mS                                    | C <sub>Jitter</sub>               | _      | 0.02               | 0.2                                                                       | %f <sub>dco</sub>   | С |

| 8   | VCO operating frequency                                                       |                                                      | f <sub>vco</sub>                  | 7.0    | —                  | 55.0                                                                      | MHz                 | D |

| 9   | PLL reference frequency range                                                 |                                                      | f <sub>pll_ref</sub>              | 1.0    | —                  | 2.0                                                                       | MHz                 | D |

| 10  | Jitter of PLL output clock measured over 625ns 5                              | Long term                                            | f <sub>pll_jitter_625</sub><br>ns | _      | 0.566 <sup>4</sup> | _                                                                         | %f <sub>pll</sub>   | D |

| 44  |                                                                               | Entry <sup>6</sup>                                   | D <sub>lock</sub>                 | ± 1.49 | —                  | ± 2.98                                                                    | 0/                  | D |

| 11  | Lock frequency tolerance                                                      | Exit <sup>7</sup>                                    | D <sub>unl</sub>                  | ± 4.47 | _                  | ± 5.97                                                                    | %                   | D |

|     |                                                                               | FLL                                                  | t <sub>fll_lock</sub>             | _      | _                  | t <sub>fll_acquire+</sub><br>1075(1/fint_t)                               |                     | D |

| 12  | Lock time                                                                     | PLL                                                  | t <sub>pll_lock</sub>             | _      | _                  | t <sub>pll_acquire+</sub><br>1075(1/ <sup>f</sup> pll_re<br><sub>f)</sub> | S                   | D |

| 13  | Loss of external clock minimum freque                                         | f <sub>loc_low</sub>                                 | (3/5) x<br>f <sub>int_t</sub>     | _      | _                  | kHz                                                                       | D                   |   |

| 14  | Loss of external clock minimum freque                                         | f <sub>loc_high</sub>                                | (16/5) x<br>f <sub>int_t</sub>    | _      | _                  | kHz                                                                       | D                   |   |

Table 17. MCG (Temperature Range = -40 to 105°C Ambient)

<sup>1</sup> This should not exceed the maximum CPU frequency for this device.

<sup>2</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bit is changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

# 2.11 AC Characteristics

This section describes ac timing characteristics for each peripheral system.

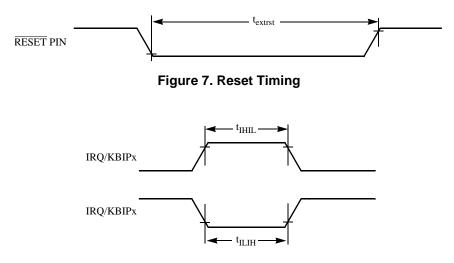

# 2.11.1 Control Timing

### Table 19. Control Timing

| # | Symbol                               | Parameter                                                                                                          |                            | Min                           | Typical <sup>1</sup> | Max  | С | Unit |

|---|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------|----------------------|------|---|------|

| 1 | f <sub>Bus</sub>                     | Bus frequency $(t_{cyc} = 1/f_{Bus})$                                                                              |                            |                               |                      |      |   | MHz  |

|   |                                      |                                                                                                                    | $V_{DD} \ge 1.8 \text{ V}$ | dc                            | _                    | 10   | D |      |

|   |                                      |                                                                                                                    | V <sub>DD</sub> > 2.1 V    | dc                            | —                    | 20   | D |      |

|   |                                      |                                                                                                                    | V <sub>DD</sub> > 2.4 V    | dc                            | _                    | 24   | D |      |

| 2 | t <sub>LPO</sub>                     | Internal low-power oscillator period                                                                               |                            | 800                           | 990<br>(TBD)         | 1500 | D | μS   |

| 3 | t <sub>extrst</sub>                  | External reset pulse width <sup>2</sup><br>( $t_{cyc} = 1/f_{Self\_reset}$ )                                       |                            | 100                           | —                    | —    | D | ns   |

| 4 | t <sub>rstdrv</sub>                  | Reset low drive                                                                                                    |                            | 66 x t <sub>cyc</sub>         | —                    | —    | D | ns   |

| 5 | t <sub>MSSU</sub>                    | Active background debug mode latch setup time                                                                      |                            | 500                           | —                    | —    | D | ns   |

| 6 | t <sub>MSH</sub>                     | Active background debug mode latch hold time                                                                       |                            | 100                           | —                    | _    | D | ns   |

| 7 | t <sub>ILIH,</sub> t <sub>IHIL</sub> | <ul> <li>IRQ pulse width</li> <li>Asynchronous path<sup>2</sup></li> <li>Synchronous path<sup>3</sup></li> </ul>   |                            | 100<br>1.5 x t <sub>cyc</sub> | _                    | _    | D | ns   |

| 8 | t <sub>ILIH,</sub> t <sub>IHIL</sub> | <ul> <li>KBIPx pulse width</li> <li>Asynchronous path<sup>2</sup></li> <li>Synchronous path<sup>3</sup></li> </ul> |                            | 100<br>1.5 x t <sub>cyc</sub> | _                    | _    | D | ns   |

| # | Symbol                                | Parameter                          |                                                 | Min | Typical <sup>1</sup> | Max | С | Unit |

|---|---------------------------------------|------------------------------------|-------------------------------------------------|-----|----------------------|-----|---|------|

| 9 | t <sub>Rise</sub> , t <sub>Fall</sub> | Port rise and fall time (load = 50 | 0 pF) <sup>4</sup> , Low Drive                  | )   |                      | ns  |   |      |

|   |                                       |                                    | Slew rate<br>control<br>disabled<br>(PTxSE = 0) | _   | 11                   | _   | D |      |

|   |                                       |                                    | Slew rate<br>control<br>enabled<br>(PTxSE = 1)  | _   | 35                   |     | D |      |

|   |                                       |                                    | Slew rate<br>control<br>disabled<br>(PTxSE = 0) | _   | 40                   | _   | D |      |

|   |                                       |                                    | Slew rate<br>control<br>enabled<br>(PTxSE = 1)  | _   | 75                   |     | D |      |

#### Table 19. Control Timing

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0 V, 25 °C unless otherwise stated.

<sup>2</sup> This is the shortest pulse that is guaranteed to be recognized as a reset pin request. Shorter pulses are not guaranteed to override reset requests from internal sources.

<sup>3</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

$^4$  Timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  levels. Temperature range –40 °C to 105 °C.

Figure 8. IRQ/KBIPx Timing

# 2.12 SPI Characteristics

Table 21 and Figure 11 through Figure 14 describe the timing requirements for the SPI system.

| No. <sup>1</sup> | Characteristic <sup>2</sup>          |                 | Symbol                             | Min                              | Мах                                        | Unit                                   | С |

|------------------|--------------------------------------|-----------------|------------------------------------|----------------------------------|--------------------------------------------|----------------------------------------|---|

| 1                | Operating frequency                  | Master<br>Slave | f <sub>op</sub>                    | f <sub>Bus</sub> /2048<br>0      | f <sub>Bus</sub> /2<br>f <sub>Bus</sub> /4 | Hz<br>Hz                               | D |

| 2                | SPSCK period                         | Master<br>Slave | t <sub>SPSCK</sub>                 | 2<br>4                           | 2048                                       | t <sub>cyc</sub><br>t <sub>cyc</sub>   | D |

| 3                | Enable lead time                     | Master<br>Slave | t <sub>Lead</sub>                  | 1/2<br>1                         |                                            | <sup>t</sup> spscк<br>t <sub>cyc</sub> | D |

| 4                | Enable lag time                      | Master<br>Slave | t <sub>Lag</sub>                   | 1/2<br>1                         |                                            | t <sub>SPSCK</sub><br>t <sub>сус</sub> | D |

| 5                | Clock (SPSCK) high or low time       | Master<br>Slave | t <sub>WSPSCK</sub>                | $t_{cyc} - 30$<br>$t_{cyc} - 30$ | 1024 t <sub>cyc</sub>                      | ns<br>ns                               | D |

| 6                | Data setup time (inputs)             | Master<br>Slave | t <sub>SU</sub><br>t <sub>SU</sub> | 15<br>15                         |                                            | ns<br>ns                               | D |

| 7                | Data hold time (inputs)              | Master<br>Slave | t <sub>HI</sub><br>t <sub>HI</sub> | 0<br>25                          |                                            | ns<br>ns                               | D |

| 8                | Slave access time <sup>3</sup>       |                 | t <sub>a</sub>                     | —                                | 1                                          | t <sub>cyc</sub>                       | D |

| 9                | Slave MISO disable time <sup>4</sup> |                 | t <sub>dis</sub>                   | —                                | 1                                          | t <sub>cyc</sub>                       | D |

| 10               | Data valid (after SPSCK edge)        | Master<br>Slave | t <sub>v</sub>                     |                                  | 25<br>25                                   | ns<br>ns                               | D |

| 11               | Data hold time (outputs)             | Master<br>Slave | t <sub>HO</sub>                    | 0<br>0                           |                                            | ns<br>ns                               | D |

| 12               | Rise time                            | Input<br>Output | t <sub>RI</sub><br>t <sub>RO</sub> |                                  | t <sub>cyc</sub> – 25<br>25                | ns<br>ns                               | D |

| 13               | Fall time                            | Input<br>Output | t <sub>FI</sub><br>t <sub>FO</sub> |                                  | t <sub>cyc</sub> – 25<br>25                | ns<br>ns                               | D |

### Table 21. SPI Timing

<sup>1</sup> Numbers in this column identify elements in Figure 11 through Figure 14.

<sup>2</sup> All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins. All timing assumes slew rate control disabled and high drive strength enabled for SPI output pins.

<sup>3</sup> Time to data active from high-impedance state.

<sup>4</sup> Hold time to high-impedance state.

# 2.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal V<sub>DD</sub> supply. For more detailed information about program/erase operations, see the Memory chapter in the Reference Manual for this device (MC9S08JE128RM).

| #  | Characteristic                                                                                        | Symbol                  | Min    | Typical     | Мах               | Unit              | С |

|----|-------------------------------------------------------------------------------------------------------|-------------------------|--------|-------------|-------------------|-------------------|---|

| 1  | Supply voltage for program/erase<br>-40°C to 105°C                                                    | V <sub>prog/erase</sub> | 1.8    | _           | 3.6               | V                 | D |

| 2  | Supply voltage for read operation                                                                     | V <sub>Read</sub>       | 1.8    | —           | 3.6               | V                 | D |

| 3  | Internal FCLK frequency <sup>1</sup>                                                                  | f <sub>FCLK</sub>       | 150    | —           | 200               | kHz               | D |

| 4  | Internal FCLK period (1/FCLK)                                                                         | t <sub>Fcyc</sub>       | 5      | —           | 6.67              | μS                | D |

| 5  | Byte program time (random location) <sup>2</sup>                                                      | t <sub>prog</sub>       | 9      |             | t <sub>Fcyc</sub> | Р                 |   |

| 6  | Byte program time (burst mode) <sup>2</sup>                                                           | t <sub>Burst</sub>      |        | 4           |                   | t <sub>Fcyc</sub> | Р |

| 7  | Page erase time <sup>2</sup>                                                                          | t <sub>Page</sub>       |        | 4000        |                   | t <sub>Fcyc</sub> | Р |

| 8  | Mass erase time <sup>2</sup>                                                                          | t <sub>Mass</sub>       |        | 20,000      |                   | t <sub>Fcyc</sub> | Р |

| 9  | Program/erase endurance <sup>3</sup><br>$T_L$ to $T_H = -40^{\circ}C$ to + 105°C<br>$T = 25^{\circ}C$ |                         | 10,000 | <br>100,000 | _                 | cycles            | С |

| 10 | Data retention <sup>4</sup>                                                                           | t <sub>D_ret</sub>      | 15     | 100         |                   | years             | С |

### Table 22. Flash Characteristics

<sup>1</sup> The frequency of this clock is controlled by a software setting.

<sup>2</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>3</sup> **Typical endurance for flash** was evaluated for this product family on the HC9S12Dx64. For additional information on how Freescale defines typical endurance, please refer to Engineering Bulletin EB619, *Typical Endurance for Nonvolatile Memory*.

<sup>4</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines typical data retention, please refer to Engineering Bulletin EB618, *Typical Data Retention for Nonvolatile Memory.*

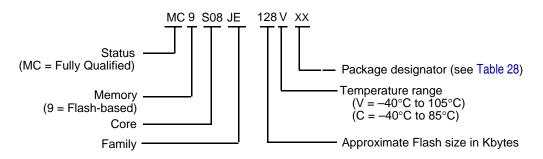

**Ordering Information**

# 3.1 Device Numbering System

Example of the device numbering system:

### Table 27. Device Numbering System

| Device Number <sup>1</sup> | Men     | nory   | Available Packages <sup>2</sup> |

|----------------------------|---------|--------|---------------------------------|

| Device Number              | Flash   | RAM    | Available Fackages              |

|                            | 131,072 | 12,288 | 64 LQFP                         |

| MC9S08JE128                | 131,072 | 12,288 | 80 LQFP                         |

|                            | 131,072 | 12,288 | 81 MAPBGA                       |

| MC9S08JE64                 | 65,536  | 12,288 | 64 LQFP                         |

<sup>1</sup> See Table 2 for a complete description of modules included on each device.

<sup>2</sup> See Table 28 for package information.

# 3.2 Package Information

#### Table 28. Package Descriptions

| Pin Count | Package Type                               | Abbreviation | Designator             | Case No. | Document No. |

|-----------|--------------------------------------------|--------------|------------------------|----------|--------------|

| 64        | Low Quad Flat Package LQFP                 |              | LH                     | 840F-02  | 98ASS23234W  |

| 80        | Low Quad Flat Package   LQFP   LK   917-01 |              | 98ASS23174W            |          |              |

| 81        | MAPBGA Package                             | Map PBGA     | MB 1662-01 98ASA10670D |          |              |

### 3.3 Mechanical Drawings

Table 28 provides the available package types and their document numbers. The latest package outline/mechanical drawings are available on the MC9S08JE128 series Product Summary pages at http://www.freescale.com.

To view the latest drawing, either:

- Click on the appropriate link in Table 28, or

- Open a browser to the Freescale<sup>®</sup> website (http://www.freescale.com), and enter the appropriate document number (from Table 28) in the "Enter Keyword" search box at the top of the page.

# 4 Revision History

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to: http://freescale.com/

The following revision history table summarizes changes contained in this document.

| Rev | Date    | Description of Changes                                     |  |

|-----|---------|------------------------------------------------------------|--|

| 0   | 6/2009  | Initial release of the Data Sheet.                         |  |

| 1   | 7/2009  | Updated MCG and XOSC Average internal reference frequency. |  |

| 2   | 04/2010 | Updated electrical characteristic data.                    |  |