Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Product Status             | Not For New Designs                                                          |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 25MHz                                                                        |

| Connectivity               | SCI, SmartCard                                                               |

| Peripherals                | DMA, PWM, WDT                                                                |

| Number of I/O              | 70                                                                           |

| Program Memory Size        | 512KB (512K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                |                                                                              |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-BFQFP                                                                    |

| Supplier Device Package    | 100-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3069rf25v |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table 2.8 Branching Instructions

# Instruction Size Function

\_\_\_\_

Bcc

JMP BSR JSR RTS Branches to a specified address if address specified condition is met. The branching conditions are listed below.

| Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                       | Condition                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------|

| BRA (BT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Always (true)                     | Always                    |

| BRN (BF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Never (false)                     | Never                     |

| BHI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | High                              | $C \lor Z = 0$            |

| BLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Low or same                       | C ∨ Z = 1                 |

| Bcc (BHS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Carry clear (high or same)        | C = 0                     |

| BCS (BLO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Carry set (low)                   | C = 1                     |

| BNE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Not equal                         | Z = 0                     |

| BEQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Equal                             | Z = 1                     |

| BVC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Overflow clear                    | V = 0                     |

| BVS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Overflow set                      | V = 1                     |

| BPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Plus                              | N = 0                     |

| BMI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Minus                             | N = 1                     |

| BGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Greater or equal                  | $N \oplus V = 0$          |

| BLT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Less than                         | N ⊕ V = 1                 |

| BGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Greater than                      | $Z \lor (N \oplus V) = 0$ |

| BLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Less or equal                     | $Z \lor (N \oplus V) = 1$ |

| <ul> <li>Branches uncor</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ditionally to a specified address |                           |

| <ul> <li>Branches to a second sec</li></ul> | ubroutine at a specified address  |                           |

| <ul> <li>Branches to a second sec</li></ul> | ubroutine at a specified address  |                           |

| <ul> <li>Returns from a s</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | subroutine                        |                           |

### **Execution of BCLR Instruction**

BCLR #0, @P4DDR ;Clear bit 0 in data direction register

### After Execution of BCLR Instruction

|              | P4 <sub>7</sub> | P4 <sub>6</sub> | P4 <sub>5</sub> | P4 <sub>4</sub> | P4 <sub>3</sub> | P4 <sub>2</sub> | P4 <sub>1</sub> | P4 <sub>0</sub> |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Input/output | Output          | Input           |

| DDR          | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 0               |

**Explanation:** To execute the BCLR instruction, the CPU begins by reading P4DDR. Since P4DDR is a write-only register, it is read as H'FF, even though its true value is H'3F.

Next the CPU clears bit 0 of the read data, changing the value to H'FE.

Finally, the CPU writes this value (H'FE) back to P4DDR to complete the BCLR instruction.

As a result,  $P4_0DDR$  is cleared to 0, making  $P4_0$  an input pin. In addition,  $P4_7DDR$  and  $P4_6DDR$  are set to 1, making  $P4_7$  and  $P4_6$  output pins.

The BCLR instruction can be used to clear flags in the on-chip registers to 0. In an interrupthandling routine, for example, if it is known that the flag is set to 1, it is not necessary to read the flag ahead of time.

**Bits 6 to 4—Standby Timer Select 2 to 0 (STS2 to STS0):** These bits select the length of time the CPU and on-chip supporting modules wait for the internal clock oscillator to settle when software standby mode is exited by an external interrupt.

When using a crystal oscillator, set these bits so that the waiting time will be at least 7 ms at the system clock rate.

For further information about waiting time selection, see section 20.4.3, Selection of Waiting Time for Exit from Software Standby Mode.

| Bit 6<br>STS2 | Bit 5<br>STS1 | Bit 4<br>STS0 | Description                   |                 |

|---------------|---------------|---------------|-------------------------------|-----------------|

| 0             | 0             | 0             | Waiting time = 8,192 states   | (Initial value) |

| 0             | 0             | 1             | Waiting time = 16,384 states  |                 |

| 0             | 1             | 0             | Waiting time = 32,768 states  |                 |

| 0             | 1             | 1             | Waiting time = 65,536 states  |                 |

| 1             | 0             | 0             | Waiting time = 131,072 states |                 |

| 1             | 0             | 1             | Waiting time = 262,144 states |                 |

| 1             | 1             | 0             | Waiting time = 1,024 states   |                 |

| 1             | 1             | 1             | Illegal setting               |                 |

Bit 3—User Bit Enable (UE): Selects whether to use the UI bit in the condition code register as a user bit or an interrupt mask bit.

| Bit 3<br>UE | Description                                    |                 |

|-------------|------------------------------------------------|-----------------|

| 0           | UI bit in CCR is used as an interrupt mask bit |                 |

| 1           | UI bit in CCR is used as a user bit            | (Initial value) |

Bit 2—NMI Edge Select (NMIEG): Selects the valid edge of the NMI input.

| Bit 2<br>NMIEG | Description                                          |                 |

|----------------|------------------------------------------------------|-----------------|

| 0              | An interrupt is requested at the falling edge of NMI | (Initial value) |

| 1              | An interrupt is requested at the rising edge of NMI  |                 |

|                                               |                            | Vector Vector Address*1 |                  |                                      |       |          |  |  |  |  |

|-----------------------------------------------|----------------------------|-------------------------|------------------|--------------------------------------|-------|----------|--|--|--|--|

| Interrupt Source                              | Origin                     | Number                  | Advanced Mode    | Normal Mode* <sup>2</sup>            | IPR   | Priority |  |  |  |  |

| IMIA2<br>(compare match/<br>input capture A2) | 16-bit timer<br>channel 2  | 32                      | H'0080 to H'0083 | H'0040 to H'0041                     | IPRA0 | High     |  |  |  |  |

| IMIB2<br>(compare match/<br>input capture B2) |                            | 33                      | H'0084 to H'0087 | H'0042 to H'0043                     |       |          |  |  |  |  |

| OVI2 (overflow 2)                             |                            | 34                      | H'0088 to H'008B | H'0044 to H'0045                     | _     |          |  |  |  |  |

| Reserved                                      | —                          | 35                      | H'008C to H'008F | H'0046 to H'0047                     |       | _        |  |  |  |  |

| CMIA0<br>(compare match<br>A0)                | 8-bit timer<br>channel 0/1 | 36                      | H'0090 to H'0093 | H'0048 to H'0049                     | IPRB7 |          |  |  |  |  |

| CMIB0<br>(compare match<br>B0)                |                            | 37                      | H'0094 to H'0097 | H'004A to H'004B                     |       |          |  |  |  |  |

| CMIA1/CMIB1<br>(compare match<br>A1/B1)       |                            | 38                      | H'0098 to H'009B | H'004C to H'004D                     |       |          |  |  |  |  |

| TOVI0/TOVI1<br>(overflow 0/1)                 |                            | 39                      | H'009C to H'009F | H'004E to H'004F                     |       | _        |  |  |  |  |

| CMIA2<br>(compare match<br>A2)                | 8-bit timer<br>channel 2/3 | 40                      | H'00A0 to H'00A3 | H'0050 to H'0051                     | IPRB6 |          |  |  |  |  |

| CMIB2<br>(compare match<br>B2)                |                            | 41                      | H'00A4 to H'00A7 | H'0052 to H'0053                     |       |          |  |  |  |  |

| CMIA3/CMIB3<br>(compare match<br>A3/B3)       |                            | 42                      | H'00A8 to H'00AB | H'0054 to H'0055                     |       |          |  |  |  |  |

| TOVI2/TOVI3<br>(overflow 2/3)                 |                            | 43                      | H'00AC to H'00AF | H'0056 to H'0057                     |       | _        |  |  |  |  |

| DEND0A                                        | DMAC                       | 44                      |                  | H'0058 to H'0059                     | IPRB5 |          |  |  |  |  |

| DEND0B<br>DEND1A                              |                            | 45<br>46                |                  | H'005A to H'005B<br>H'005C to H'005D |       |          |  |  |  |  |

| DEND1B                                        |                            | 40<br>47                |                  | H'005E to H'005F                     |       |          |  |  |  |  |

| Reserved                                      | _                          | 48                      | H'00C0 to H'00C3 | H'0060 to H'0061                     | _     | -        |  |  |  |  |

|                                               |                            | 49                      | H'00C4 to H'00C7 |                                      |       |          |  |  |  |  |

|                                               |                            | 50                      | H'00C8 to H'00CB |                                      |       | I        |  |  |  |  |

|                                               |                            | 51                      | H'00CC to H'00CF | H'0066 to H'0067                     |       | Low      |  |  |  |  |

Note: \* Only 0 can be written to clear the flag.

**Bit 7—Compare Match Flag (CMF):** Status flag that indicates a match between the values of RTCNT and RTCOR.

| Bit 7<br>CMF | Description                                                                                                       |                 |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----------------|

| 0            | [Clearing conditions]<br>When the chip is reset and in standby mode<br>Read CMF when CMF = 1, then write 0 in CMF | (Initial value) |

| 1            | [Setting condition]<br>When RTCNT = RTCOR                                                                         |                 |

**Bit 6—Compare Match Interrupt Enable (CMIE):** Enables or disables the CMI interrupt requested when the CMF flag is set to 1 in RTMCSR. The CMIE bit is always cleared to 0 when any of areas 2 to 5 is designated as DRAM space.

| Bit 6<br>CMIE | Description                                    |                 |

|---------------|------------------------------------------------|-----------------|

| 0             | The CMI interrupt requested by CMF is disabled | (Initial value) |

| 1             | The CMI interrupt requested by CMF is enabled  |                 |

**Bits 5 to 3—Refresh Counter Clock Select (CKS2 to CKS0):** These bits select the clock to be input to RTCNT from among 7 clocks obtained by dividing the system clock ( $\phi$ ). When the input clock is selected with bits CKS2 to CKS0, RTCNT begins counting up.

| Bit 5<br>CKS2 | Bit 4<br>CKS1 | Bit 3<br>CKS0 | Description                  |                 |

|---------------|---------------|---------------|------------------------------|-----------------|

| 0             | 0             | 0             | Count operation halted       | (Initial value) |

|               |               | 1             | ∲/2 used as counter clock    |                 |

|               | 1             | 0             | ∳/8 used as counter clock    |                 |

|               |               | 1             | ¢/32 used as counter clock   |                 |

| 1             | 0             | 0             | ¢/128 used as counter clock  |                 |

|               |               | 1             | ¢/512 used as counter clock  |                 |

|               | 1             | 0             | ¢/2048 used as counter clock |                 |

|               |               | 1             | ∲/4096 used as counter clock |                 |

Bits 2 to 0—Reserved: These bits cannot be modified and are always read as 1.

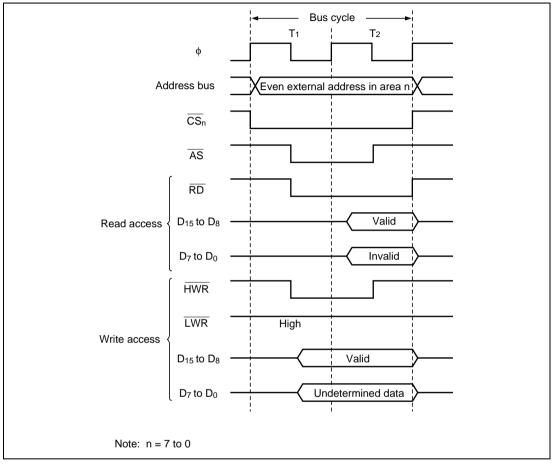

**16-Bit, Two-State-Access Areas:** Figures 6.14 to 6.16 show the timing of bus control signals for a 16-bit, two-state-access area. In these areas, the upper data bus  $(D_{15} \text{ to } D_8)$  is used in accesses to even addresses and the lower data bus  $(D_7 \text{ to } D_0)$  in accesses to odd addresses. Wait states cannot be inserted.

Figure 6.14 Bus Control Signal Timing for 16-Bit, Two-State-Access Area (1) (Byte Access to Even Address)

|                   | DRCR | в      | Column<br>Address        |                                                            |                             |                   |                   |                 | Add             | ress            | Pins                        | ;                           |                 |                             |                             |                |                 |

|-------------------|------|--------|--------------------------|------------------------------------------------------------|-----------------------------|-------------------|-------------------|-----------------|-----------------|-----------------|-----------------------------|-----------------------------|-----------------|-----------------------------|-----------------------------|----------------|-----------------|

|                   | MXC1 | MXC0   | Bits                     | $\rm A_{_{23}}$ to $\rm A_{_{13}}$                         | $A_{_{12}}$                 | A <sub>11</sub>   | $A_{_{10}}$       | $A_{_9}$        | $A_{_8}$        | A <sub>7</sub>  | $A_{_6}$                    | $A_{_5}$                    | $A_{_4}$        | $A_{_3}$                    | $A_{2}$                     | Α,             | A <sub>0</sub>  |

| Row<br>address    | 0    | 0      | 8 bits                   | $A_{_{23}}$ to $A_{_{13}}$                                 | A_20*                       | • A <sub>19</sub> | A <sub>18</sub>   | A <sub>17</sub> | A <sub>16</sub> | A <sub>15</sub> | A <sub>14</sub>             | A <sub>13</sub>             | A <sub>12</sub> | A <sub>11</sub>             | A <sub>10</sub>             | $A_{_9}$       | A <sub>8</sub>  |

|                   |      | 1      | 9 bits                   | $\rm A_{_{23}}$ to $\rm A_{_{13}}$                         | $A_{_{12}}$                 | A_20*             | $A_{_{19}}$       | A <sub>18</sub> | $A_{_{17}}$     | $A_{_{16}}$     | $A_{_{15}}$                 | A <sub>14</sub>             | A <sub>13</sub> | $A_{_{12}}$                 | $A_{_{11}}$                 | $A_{_{10}}$    | $A_{_9}$        |

|                   | 1    | 0      | 10 bits                  | $A_{\scriptscriptstyle 23}$ to $A_{\scriptscriptstyle 13}$ | $A_{\scriptscriptstyle 12}$ | $A_{_{11}}$       | A <sub>20</sub> * | $A_{_{19}}$     | A <sub>18</sub> | A <sub>17</sub> | $A_{\scriptscriptstyle 16}$ | $A_{\scriptscriptstyle 15}$ | $A_{_{14}}$     | $A_{\scriptscriptstyle 13}$ | $A_{\scriptscriptstyle 12}$ | $A_{_{11}}$    | A <sub>10</sub> |

|                   |      | 1      | Illegal<br>setting       | —                                                          | —                           | _                 | _                 | _               | _               | _               | _                           | _                           | _               | _                           | _                           | _              | —               |

| Column<br>address | _    | _      | _                        | $A_{\scriptscriptstyle 23}$ to $A_{\scriptscriptstyle 13}$ | A <sub>12</sub>             | A <sub>11</sub>   | A <sub>10</sub>   | $A_{_9}$        | $A_{_8}$        | A <sub>7</sub>  | $A_6$                       | $A_{5}$                     | $A_4$           | $A_{3}$                     | $A_2$                       | A <sub>1</sub> | A <sub>0</sub>  |

| Note: *           | Row  | addres | s bit A <sub>20</sub> is | not multip                                                 | lexe                        | d in              | 1-Mk              | oyte            | moc             | le.             |                             |                             |                 |                             |                             |                |                 |

### Table 6.6 Settings of Bits MXC1 and MXC0 and Address Multiplexing Method

### 6.5.4 Data Bus

If the bit in ABWCR corresponding to an area designated as DRAM space is set to 1, that area is designated as 8-bit DRAM space; if the bit is cleared to 0, the area is designated as 16-bit DRAM space. In 16-bit DRAM space, × 16-bit organization DRAM can be connected directly.

In 8-bit DRAM space the upper half of the data bus,  $D_{15}$  to  $D_8$ , is enabled, while in 16-bit DRAM space both the upper and lower halves of the data bus,  $D_{15}$  to  $D_0$ , are enabled.

Access sizes and data alignment are the same as for the basic bus interface: see section 6.4.2, Data Size and Data Alignment.

### 6.5.5 Pins Used for DRAM Interface

Table 6.7 shows the pins used for DRAM interfacing and their functions.

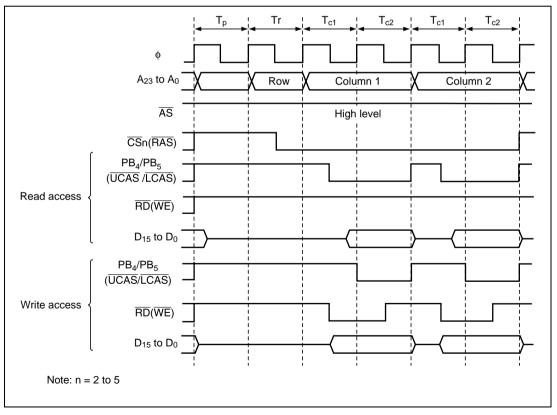

## 6.5.10 Burst Operation

With DRAM, in addition to full access (normal access) in which data is accessed by outputting a row address for each access, a fast page mode is also provided which can be used when making a number of consecutive accesses to the same row address. This mode enables fast (burst) access of data by simply changing the column address after the row address has been output. Burst access can be selected by setting the BE bit to 1 in DRCRA.

**Burst Access (Fast Page Mode) Operation Timing:** Figure 6.22 shows the operation timing for burst access. When there are consecutive access cycles for DRAM space, the column address and  $\overline{CAS}$  signal output cycles (two states) continue as long as the row address is the same for consecutive access cycles. In burst access, too, the bus cycle can be extended by inserting wait states between  $T_{c1}$  and  $T_{c2}$ . The wait state insertion method and timing are the same as for full access: see section 6.5.8, Wait Control, for details.

The row address used for the comparison is determined by the bus width of the relevant area set in bits MXC1 and MXC0 in DRCRB, and in ABWCR. Table 6.9 shows the compared row addresses corresponding to the various settings of bits MXC1 and MXC0, and ABWCR.

Figure 6.22 Operation Timing in Fast Page Mode

Rev. 5.0, 09/04, page 163 of 978

**Bit 7—Data Transfer Enable (DTE):** Together with the DTME bit in DTCRB, this bit enables or disables data transfer on the channel. When the DTME and DTE bits are both set to 1, the channel is enabled. If auto-request is specified, data transfer begins immediately. Otherwise, the channel waits for transfers to be requested. When the specified number of transfers have been completed, the DTE bit is automatically cleared to 0. When DTE is 0, the channel is disabled and does not accept transfer requests. DTE is set to 1 by reading the register when DTE is 0, then writing 1.

| Bit 7<br>DTE | Description                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------|

| 0            | Data transfer is disabled (DTE is cleared to 0 when the specified number (Initial value) of transfers have been completed) |

| 1            | Data transfer is enabled                                                                                                   |

If DTIE is set to 1, a CPU interrupt is requested when DTE is cleared to 0.

| Bit 6<br>DTSZ | Description        |                 |

|---------------|--------------------|-----------------|

| 0             | Byte-size transfer | (Initial value) |

| 1             | Word-size transfer |                 |

## Bit 5—Source Address Increment/Decrement (SAID) and,

**Bit 4—Source Address Increment/Decrement Enable (SAIDE):** These bits select whether the source address register (MARA) is incremented, decremented, or held fixed during the data transfer.

| Bit 5<br>SAID | Bit 4<br>SAIDE | Description                                                 |                 |

|---------------|----------------|-------------------------------------------------------------|-----------------|

| 0             | 0              | MARA is held fixed                                          | (Initial value) |

|               | 1              | MARA is incremented after each data transfer                |                 |

|               |                | • If DTSZ = 0, MARA is incremented by 1 after each transfer |                 |

|               |                | • If DTSZ = 1, MARA is incremented by 2 after each transf   | er              |

| 1             | 0              | MARA is held fixed                                          |                 |

|               | 1              | MARA is decremented after each data transfer                |                 |

|               |                | • If DTSZ = 0, MARA is decremented by 1 after each trans    | fer             |

|               |                | • If DTSZ = 1, MARA is decremented by 2 after each trans    | fer             |

### 9.5.3 Interrupt Sources

Each 16-bit timer channel can generate a compare match/input capture A interrupt, a compare match/input capture B interrupt, and an overflow interrupt. In total there are nine interrupt sources of three kinds, all independently vectored. An interrupt is requested when the interrupt request flag are set to 1.

The priority order of the channels can be modified in interrupt priority registers A (IPRA). For details see section 5, Interrupt Controller.

Table 9.6 lists the interrupt sources.

| Channel | Interrupt<br>Source    | Description                                                                    | Priority* |

|---------|------------------------|--------------------------------------------------------------------------------|-----------|

| 0       | IMIA0<br>IMIB0<br>OVI0 | Compare match/input capture A0<br>Compare match/input capture B0<br>Overflow 0 | High      |

| 1       | IMIA1<br>IMIB1<br>OVI1 | Compare match/input capture A1<br>Compare match/input capture B1<br>Overflow 1 |           |

| 2       | IMIA2<br>IMIB2<br>OVI2 | Compare match/input capture A2<br>Compare match/input capture B2<br>Overflow 2 | Low       |

Table 9.616-bit timer Interrupt Sources

Note: \* The priority immediately after a reset is indicated. Inter-channel priorities can be changed by settings in IPRA.

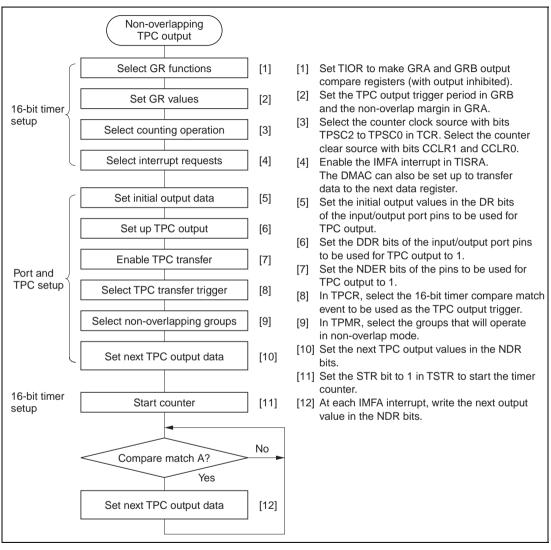

**Sample Setup Procedure for Non-Overlapping TPC Output:** Figure 11.6 shows a sample procedure for setting up non-overlapping TPC output.

Figure 11.6 Setup Procedure for Non-Overlapping TPC Output (Example)

**Bit 7—Watchdog Timer Reset (WRST):** During watchdog timer operation, this bit indicates that TCNT has overflowed and generated a reset signal. This reset signal resets the entire H8/3069R chip internally.

| Bit 7<br>WRST | Description                                                                                            |                 |

|---------------|--------------------------------------------------------------------------------------------------------|-----------------|

| 0             | [Clearing condition]<br>Reset signal at RES pin.<br>Read WRST when WRST =1, then write 0 in WRST.      | (Initial value) |

| 1             | [Setting condition]<br>Set when TCNT overflow generates a reset signal during watchdog timer operation |                 |

Bit 6—Reserved: The write value should always be 0.

Bits 5 to 0—Reserved: These bits are always read as 1. The write value should always be 1.

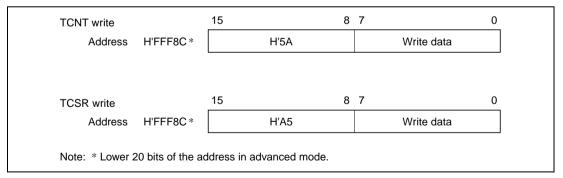

### 12.2.4 Notes on Register Access

The watchdog timer's TCNT, TCSR, and RSTCSR registers differ from other registers in being more difficult to write. The procedures for writing and reading these registers are given below.

**Writing to TCNT and TCSR:** These registers must be written by a word transfer instruction. They cannot be written by byte instructions. Figure 12.2 shows the format of data written to TCNT and TCSR. TCNT and TCSR both have the same write address. The write data must be contained in the lower byte of the written word. The upper byte must contain H'5A (password for TCNT) or H'A5 (password for TCSR). This transfers the write data from the lower byte to TCNT or TCSR.

Figure 12.2 Format of Data Written to TCNT and TCSR

**Bits 1 and 0—Clock Select 1 and 0 (CKS1/0):** These bits select the clock source for the on-chip baud rate generator. Four clock sources are available:  $\phi$ ,  $\phi/4$ ,  $\phi/16$ , and  $\phi/64$ .

For the relationship between the clock source, bit rate register setting, and baud rate, see section 13.2.8, Bit Rate Register (BRR).

| Bit 1<br>CKS1 | Bit 0<br>CKS0 | Description |                 |

|---------------|---------------|-------------|-----------------|

| 0             | 0             | φ           | (Initial value) |

| 0             | 1             | ф/4         |                 |

| 1             | 0             | ф/16        |                 |

| 1             | 1             | ф/64        |                 |

Figure 13.18 Sample Flowchart for Serial Receiving (2)

In receiving, the SCI operates as follows:

- The SCI synchronizes with serial clock input or output and synchronizes internally.

- Receive data is stored in RSR in order from LSB to MSB.

After receiving the data, the SCI checks that the RDRF flag is 0, so that receive data can be transferred from RSR to RDR. If this check passes, the RDRF flag is set to 1 and the received data is stored in RDR. If the checks fails (receive error), the SCI operates as shown in table 13.11.

When a receive error has been identified in the error check, subsequent transmit and receive operations are disabled.

• When the RDRF flag is set to 1, if the RIE bit is set to 1 in SCR, a receive-data-full interrupt (RXI) is requested. If the ORER flag is set to 1 and the RIE bit in SCR is also set to 1, a receive-error interrupt (ERI) is requested.

## Bit 7-D/A Output Enable 1 (DAOE1): Controls D/A conversion and analog output.

| Bit 7 |                                                            |

|-------|------------------------------------------------------------|

| DAOE1 | Description                                                |

| 0     | DA, analog output is disabled                              |

| 1     | Channel-1 D/A conversion and DA, analog output are enabled |

Bit 6—D/A Output Enable 0 (DAOE0): Controls D/A conversion and analog output.

| Bit 6<br>DAOE0 | Description                                                   |

|----------------|---------------------------------------------------------------|

| 0              | $DA_{_0}$ analog output is disabled                           |

| 1              | Channel-0 D/A conversion and $DA_0$ analog output are enabled |

**Bit 5—D/A Enable (DAE):** Controls D/A conversion, together with bits DAOE0 and DAOE1. When the DAE bit is cleared to 0, analog conversion is controlled independently in channels 0 and 1. When the DAE bit is set to 1, analog conversion is controlled together in channels 0 and 1. Output of the conversion results is always controlled independently by DAOE0 and DAOE1.

| Bit 7<br>DAOE1 | Bit 6<br>DAOE0 | Bit 5<br>DAE | Description                                    |  |

|----------------|----------------|--------------|------------------------------------------------|--|

| 0              | 0              | _            | D/A conversion is disabled in channels 0 and 1 |  |

|                | 1              | 0            | D/A conversion is enabled in channel 0         |  |

|                |                |              | D/A conversion is disabled in channel 1        |  |

|                |                | 1            | D/A conversion is enabled in channels 0 and 1  |  |

| 1              | 0              | 0            | D/A conversion is disabled in channel 0        |  |

|                |                |              | D/A conversion is enabled in channel 1         |  |

|                |                | 1            | D/A conversion is enabled in channels 0 and 1  |  |

|                | 1              | _            | D/A conversion is enabled in channels 0 and 1  |  |

When the DAE bit is set to 1, even if bits DAOE0 and DAOE1 in DACR and the ADST bit in ADCSR are cleared to 0, the same current is drawn from the analog power supply as during A/D and D/A conversion.

Bits 4 to 0—Reserved: These bits cannot be modified and are always read as 1.

# Table 18.9 Hardware Protection

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Function to be Protected |               |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|

| Item                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Download                 | Program/Erase |

| FWE-pin protection          | • The input of a low-level signal on the FWE pin clears the FWE bit of FCCS and the device enters a program/erase-protected state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                        | 0             |

| Reset/standby<br>protection | <ul> <li>A power-on reset (including a power-on reset by the WDT) and entry to standby mode reinitialize the program/erase interface register and the device enters a program/erase-protected state.</li> <li>Resetting by means of the RES pin after power is initially supplied will not make the device enter the reset state unless the RES pin is held low until oscillation has stabilized. In the case of a reset during operation, hold the RES pin low for the RES pulse width that is specified in the section on AC characteristics section. If the device is reset during programming or erasure, data values in the flash memory are not guaranteed. In this case, after keeping the RES pin low for at least 100 µs, execute erasure and then execute programming again.</li> </ul> | 0                        | 0             |

## **18.6.2** Software Protection

Software protection is set up in any of three ways: by disabling the downloading of on-chip programs for programming and erasing, by means of a key code, and by the RAM-emulation register.

RENESAS

Rev. 5.0, 09/04, page 629 of 978

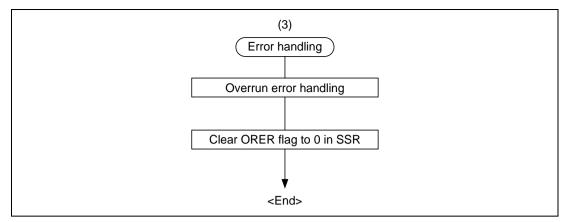

### 20.2.2 Module Standby Control Register H (MSTCRH)

MSTCRH is an 8-bit readable/writable register that controls output of the system clock ( $\phi$ ). It also controls the module standby function, which places individual on-chip supporting modules in the standby state. Module standby can be designated for the SCI0, SCI1, SCI2.

In modes 1 to 5, MSTCRH is initialized to H'78 by a reset and in hardware standby mode, while in mode 7 it is initialized to H'F8. It is not initialized in software standby mode.

Bit 7— $\phi$  Clock Stop (PSTOP): Enables or disables output of the system clock ( $\phi$ ).