Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | ARM® Cortex®-M0                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 50MHz                                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVR, POR, PWM, WDT                                             |

| Number of I/O              | 56                                                                                     |

| Program Memory Size        | 36KB (36K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 8K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                            |

| Data Converters            | A/D 8x12b                                                                              |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 64-LQFP                                                                                |

| Supplier Device Package    | 64-LQFP (7x7)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/m0518sc2ae |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8.3.3 Internal 22.1184 MHz High Speed Oscillator60 |

|----------------------------------------------------|

| 8.3.4 Internal 10 kHz Low Speed Oscillator61       |

| 8.4 Analog Characteristics62                       |

| 8.4.1 12-bit SARADC Specification                  |

| 8.4.2 LDO and Power Management Specification       |

| 8.4.3 Low Voltage Reset Specification              |

| 8.4.4 Brown-out Detector Specification             |

| 8.4.5 Power-on Reset Specification                 |

| 8.5 Flash DC Electrical Characteristics            |

| 8.6 I2C Dynamic Characteristics67                  |

| 8.7 SPI Dynamic Characteristics                    |

| 8.8 I2S Dynamic Characteristics                    |

| 9 ACKAGE DIMENSIONS                                |

| 9.1 64-pin LQFP (7x7x1.4 mm footprint 2.0 mm)72    |

| 9.2 48-pin LQFP (7x7x1.4 mm footprint 2.0 mm)73    |

| 10REVISION HISTORY                                 |

| List of Tables                                              |      |

|-------------------------------------------------------------|------|

| Table 3-1 List of Abbreviations                             | . 11 |

| Table 6-1 Address Space Assignments for On-Chip Controllers | . 28 |

| Table 6-2 Exception Model                                   | . 31 |

| Table 6-3 System Interrupt Map                              | .32  |

| Table 6-4 Vector Table Format                               | .33  |

| Table 6-5 PWM and BPWM Features Different Table             | .44  |

| Table 6-6 PWM and BPWM Features Different Table             | 46   |

channels

- Supports independent mode for BPWM output/Capture input channel

- Supports 12-bit pre-scalar from 1 to 4096

- Supports 16-bit resolution BPWM counter

- Up, down and up/down counter operation type

- Supports mask function and tri-state enable for each BPWM pin

- Supports interrupt on the following events:

- BPWM counter match zero, period value or compared value

- Supports trigger ADC on the following events:

- BPWM counter match zero, period value or compared value

- Supports up to 12 capture input channels with 16-bit resolution

- Supports rising edges, falling edges or both edges capture condition

- Supports input rising edges, falling edges or both edges capture interrupt

- Supports rising edges, falling edges or both edges capture with counter reload option

- PWM/Capture

- Supports maximum clock frequency up to 100MHz

- Supports up to two PWM modules, each module provides three 16-bit timers and 6 output channels

- Supports independent mode for PWM output/Capture input channel

- Supports complementary mode for 3 complementary paired PWM output channel

- Dead-time insertion with 12-bit resolution

- Two compared values during one period

- Supports 12-bit pre-scalar from 1 to 4096

- Supports 16-bit resolution PWM counter

- Up, down and up/down counter operation type

- Supports mask function and tri-state enable for each PWM pin

- Supports brake function

- Brake source from pin and system safety events (clock failed, Brown-out detection and CPU lockup)

- Noise filter for brake source from pin

- Edge detect brake source to control brake state until brake interrupt cleared

- Level detect brake source to auto recover function after brake condition removed

- Supports interrupt on the following events:

- PWM counter match zero, period value or compared value

- Brake condition happened

- Supports trigger ADC on the following events:

- PWM counter match zero, period value or compared value

- Supports up to 12 capture input channels with 16-bit resolution

- Supports rising edges, falling edges or both edges capture condition

- Supports input rising edges, falling edges or both edges capture interrupt

- Supports rising edges, falling edges or both edges capture with counter reload option

- UART

- Up to six UART controllers

- UART0 and UART1 ports with flow control (TXD, RXD, nCTS and nRTS)

- UART0, UART1 and UART2 with 16-byte FIFO for standard device

- Supports IrDA (SIR) and LIN function

- Supports RS-485 9-bit mode and direction control

- Supports auto baud-rate generator

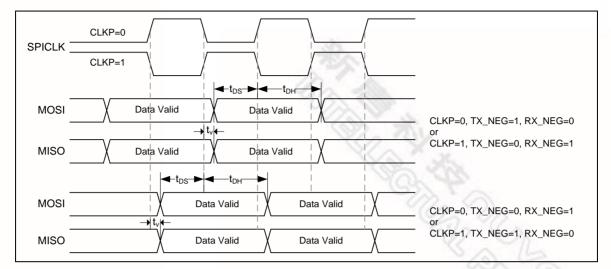

- SPI

- One set of SPI controller

- Supports SPI Master/Slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 8 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

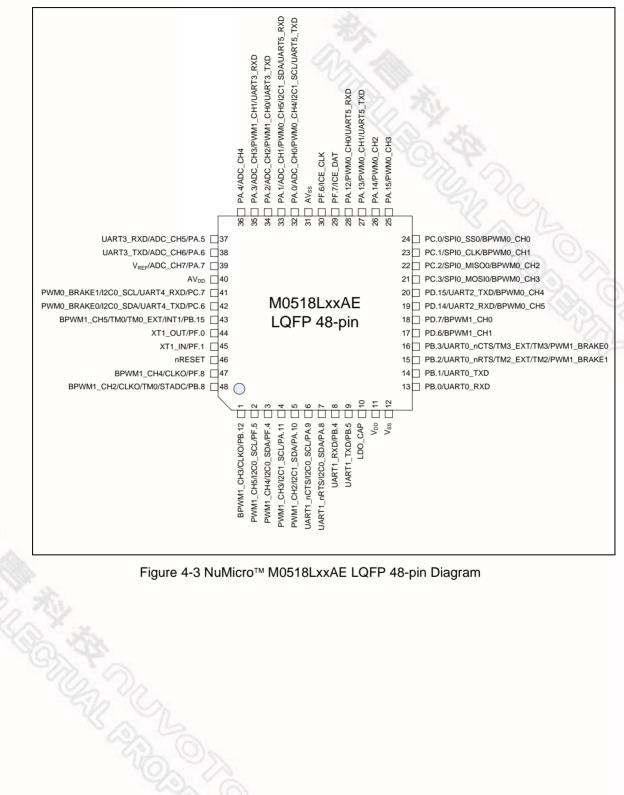

### **4** PARTS INFORMATION LIST AND PIN CONFIGURATION

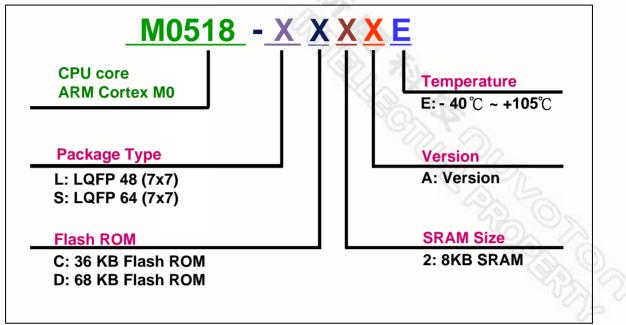

4.1 NuMicro™ M0518 Series Selection Code

Figure 4-1 NuMicro™ M0518 Series Selection Code

| Pin No.        |                |                  |             |                                          |

|----------------|----------------|------------------|-------------|------------------------------------------|

| LQFP<br>64-pin | LQFP<br>48-pin | Pin Name         | Pin<br>Type | Description                              |

|                |                | PWM0_CH3         | I/O         | PWM0 CH3 output/Capture input.           |

|                |                | PA.14            | I/O         | General purpose digital I/O pin.         |

| 38             | 26             | PWM0_CH2         | I/O         | PWM0 CH2 output/Capture input.           |

|                |                | PA.13            | I/O         | General purpose digital I/O pin.         |

| 39             | 27             | PWM0_CH1         | I/O         | PWM0 CH1 output/Capture input.           |

|                |                | UART5_TXD        | 0           | Data transmitter output pin for UART5.   |

|                |                | PA.12            | I/O         | General purpose digital I/O pin.         |

| 40             | 28             | PWM0_CH0         | I/O         | PWM0 CH0 output/Capture input.           |

|                |                | UART5_RXD        | I           | Data receiver input pin for UART5.       |

| 44             | 29             | PF.7             | I/O         | General purpose digital I/O pin.         |

| 41             | 29             | ICE_DAT          | I/O         | Serial wire debugger data pin.           |

| 40             |                | PF.6             | I/O         | General purpose digital I/O pin.         |

| 42             | 30             | ICE_CLK          | I           | Serial wire debugger clock pin.          |

| 43             | 31             | AV <sub>SS</sub> | AP          | Ground pin for analog circuit.           |

|                |                | PA.0             | I/O         | General purpose digital I/O pin.         |

|                |                | ADC_CH0          | AI          | ADC_CH0 analog input.                    |

| 44             | 32             | PWM0_CH4         | I/O         | PWM0 CH4 output/Capture input.           |

|                |                | I2C1_SCL         | I/O         | I <sup>2</sup> C1 clock pin.             |

|                |                | UART5_TXD        | 0           | Data transmitter output pin for UART5.   |

|                |                | PA.1             | I/O         | General purpose digital I/O pin.         |

| 6              |                | ADC_CH1          | AI          | ADC_CH1 analog input.                    |

| 45             | 33             | PWM0_CH5         | I/O         | PWM0 CH5 output/Capture input.           |

| × X            |                | I2C1_SDA         | I/O         | I <sup>2</sup> C1 data input/output pin. |

| 2              |                | UART5_RXD        | I           | Data receiver input pin for UART5.       |

| SÃ             | ŝ              | PA.2             | I/O         | General purpose digital I/O pin.         |

| 46             | 24             | ADC_CH2          | AI          | ADC_CH2 analog input.                    |

| 46             | 34             | PWM1_CH0         | I/O         | PWM1 CH0 output/Capture input.           |

|                |                | UART3_TXD        | 0           | Data transmitter output pin for UART3.   |

|                |                | PA.3             | 1/0         | General purpose digital I/O pin.         |

| 47             | 0.5            | ADC_CH3          | AI          | ADC_CH3 analog input.                    |

| 47             | 35             | PWM1_CH1         | 1/0         | PWM1 CH1 output/Capture input.           |

|                |                | UART3_RXD        | Sel.        | Data receiver input pin for UART3.       |

### 6.2.5 System Timer (SysTick)

The Cortex<sup>™</sup>-M0 includes an integrated system timer, SysTick, which provides a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used as a Real Time Operating System (RTOS) tick timer or as a simple counter.

When system timer is enabled, it will count down from the value in the SysTick Current Value Register (SYST\_CVR) to 0, and reload (wrap) to the value in the SysTick Reload Value Register (SYST\_RVR) on the next clock cycle, then decrement on subsequent clocks. When the counter transitions to 0, the COUNTFLAG status bit is set. The COUNTFLAG bit clears on reads.

The SYST\_CVR value is unknown on reset. Software should write to the register to clear it to 0 before enabling the feature. This ensures the timer will count from the SYST\_RVR value rather than an arbitrary value when it is enabled.

If the SYST\_RVR is 0, the timer will be maintained with a current value of 0 after it is reloaded with this value. This mechanism can be used to disable the feature independently from the timer enable bit.

For more detailed information, please refer to the "ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

### NuMicro<sup>™</sup> M0518 Series Datasheet

## nuvoTon

| 14 | SPI0_INT                                                                      | SPI0                                                                                                                                                                                                                            | SPI0 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|----|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15 | UART3_INT                                                                     | UART3                                                                                                                                                                                                                           | UART3 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 16 | UART4_INT                                                                     | UART4                                                                                                                                                                                                                           | UART4 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 17 | UART5_INT                                                                     | UART5                                                                                                                                                                                                                           | UART5 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 18 | I2C0_INT                                                                      | I <sup>2</sup> C0                                                                                                                                                                                                               | I <sup>2</sup> C0 interrupt                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 19 | I2C1_INT                                                                      | I <sup>2</sup> C1                                                                                                                                                                                                               | I <sup>2</sup> C1 interrupt                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 20 | -                                                                             | -                                                                                                                                                                                                                               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 21 | -                                                                             | -                                                                                                                                                                                                                               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 22 | PWM0_INT                                                                      | PWM0                                                                                                                                                                                                                            | PWM0 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 23 | PWM1_INT                                                                      | PWM1                                                                                                                                                                                                                            | PWM1 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 24 | BPWM0_INT                                                                     | BPWM0                                                                                                                                                                                                                           | BPWM0 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 25 | BPWM1_INT                                                                     | BPWM1                                                                                                                                                                                                                           | BPWM1 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 26 | BRAKE0_INT                                                                    | PWM0                                                                                                                                                                                                                            | PWM0 brake interrupt                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 27 | BRAKE1_INT                                                                    | PWM1                                                                                                                                                                                                                            | PWM1 brake interrupt                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 28 | PWRWU_INT                                                                     | CLKC                                                                                                                                                                                                                            | Clock controller interrupt for chip wake-up from Power-<br>down state                                                                                                                                                                                                                                                                                                                                                          |  |

| 29 | ADC_INT                                                                       | ADC                                                                                                                                                                                                                             | ADC interrupt                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 30 | CKD_INT                                                                       | CLKC                                                                                                                                                                                                                            | Clock detection interrupt                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 31 | -                                                                             | -                                                                                                                                                                                                                               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|    | 15   16   17   18   19   20   21   22   23   24   25   26   27   28   29   30 | 15   UART3_INT     16   UART4_INT     17   UART5_INT     18   I2C0_INT     19   I2C1_INT     20   -     21   -     23   PWM0_INT     24   BPWM0_INT     25   BRAKE0_INT     27   BRAKE1_INT     28   PWRWU_INT     30   CKD_INT | 15   UART3_INT   UART3     16   UART4_INT   UART4     17   UART5_INT   UART5     18   I2C0_INT   I <sup>2</sup> C0     19   I2C1_INT   I <sup>2</sup> C1     20   -   -     21   -   -     22   PWM0_INT   PWM0     23   PWM1_INT   BPWM0     24   BPWM0_INT   BPWM0     25   BRAKE0_INT   PWM0     26   BRAKE0_INT   PWM0     27   BRAKE1_INT   PWM1     28   PWRWU_INT   CLKC     29   ADC_INT   ADC     30   CKD_INT   CLKC |  |

Table 6-3 System Interrupt Map

#### 6.2.6.2 Vector Table

When an interrupt is accepted, the processor will automatically fetch the starting address of the interrupt service routine (ISR) from a vector table in memory. For ARMv6-M, the vector table base address is fixed at 0x00000000. The vector table contains the initialization value for the stack pointer on reset, and the entry point addresses for all exception handlers. The vector number on previous page defines the order of entries in the vector table associated with exception handler entry as illustrated in previous section.

| Vector Table Word Offset | Description                                      |

|--------------------------|--------------------------------------------------|

| 0                        | SP_main – The Main stack pointer                 |

| Vector Number            | Exception Entry Pointer using that Vector Number |

Table 6-4 Vector Table Format

#### 6.2.6.3 Operation Description

NVIC interrupts can be enabled and disabled by writing to their corresponding Interrupt Set-Enable or Interrupt Clear-Enable register bit-field. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current enabled state of the corresponding interrupts. When an interrupt is disabled, interrupt assertion will cause the interrupt to become Pending, however, the interrupt will not activate. If an interrupt is Active when it is disabled, it remains in its Active state until cleared by reset or an exception return. Clearing the enable bit prevents new activations of the associated interrupt.

NVIC interrupts can be pended/un-pended using a complementary pair of registers to those used to enable/disable the interrupts, named the Set-Pending Register and Clear-Pending Register respectively. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current pended state of the corresponding interrupts. The Clear-Pending Register has no effect on the execution status of an Active interrupt.

NVIC interrupts are prioritized by updating an 8-bit field within a 32-bit register (each register supporting four interrupts).

The general registers associated with the NVIC are all accessible from a block of memory in the System Control Space and will be described in next section.

## nuvoton

### 6.2.7 System Control

The Cortex<sup>™</sup>-M0 status and operating mode control are managed by System Control Registers. Including CPUID, Cortex<sup>™</sup>-M0 interrupt priority and Cortex<sup>™</sup>-M0 power management can be controlled through these system control registers.

For more detailed information, please refer to the "ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

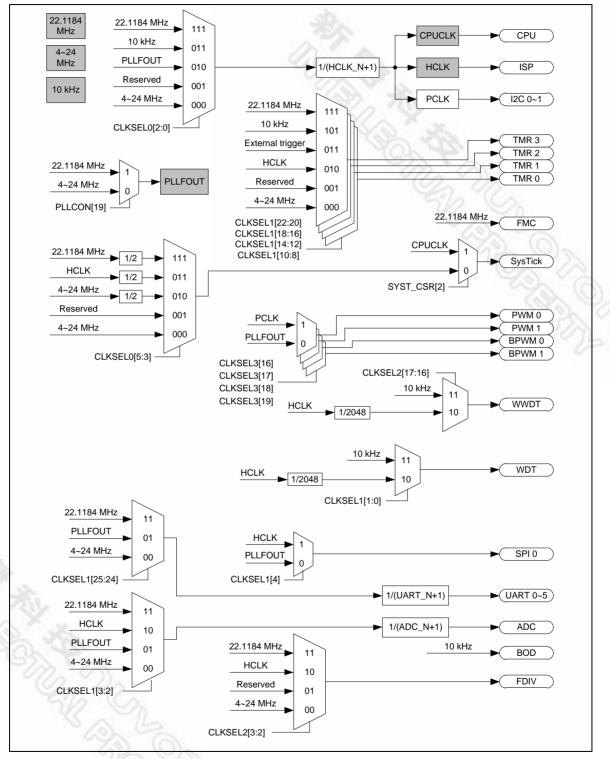

Figure 6-4 Clock Generator Global View Diagram

### 6.3.2 System Clock and SysTick Clock

The system clock has 4 clock sources which were generated from clock generator block. The

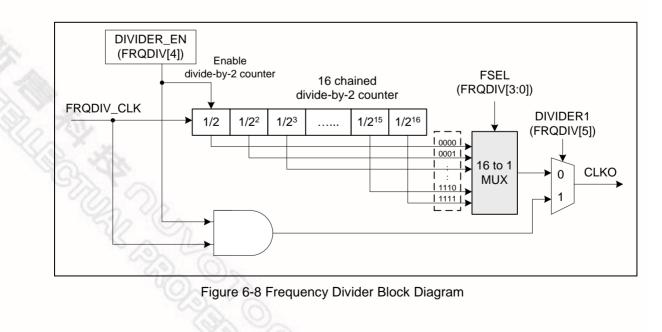

### 6.3.4 Frequency Divider Output

This device is equipped with a power-of-2 frequency divider which is composed by16 chained divide-by-2 shift registers. One of the 16 shift register outputs selected by a sixteen to one multiplexer is reflected to CLKO function pin. Therefore there are 16 options of power-of-2 divided clocks with the frequency from  $F_{in}/2^1$  to  $F_{in}/2^{16}$  where Fin is input clock frequency to the clock divider.

The output formula is  $F_{out} = F_{in}/2^{(N+1)}$ , where  $F_{in}$  is the input clock frequency,  $F_{out}$  is the clock divider output frequency and N is the 4-bit value in FSEL (FRQDIV[3:0]).

When writing 1 to DIVIDER\_EN (FRQDIV[4]), the chained counter starts to count. When writing 0 to DIVIDER\_EN (FRQDIV[4]), the chained counter continuously runs till divided clock reaches low state and stay in low state.

If DIVIDER1(FRQDIV[5]) is set to 1, the frequency divider clock (FRQDIV\_CLK) will bypass power-of-2 frequency divider. The frequency divider clock will be output to CLKO pin directly.

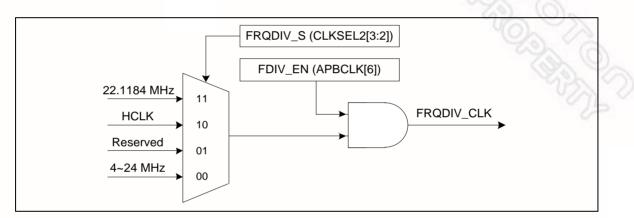

Figure 6-7 Clock Source of Frequency Divider

### 6.5 General Purpose I/O (GPIO)

#### 6.5.1 Overview

The NuMicro<sup>™</sup> M0518 series has up to 56 General Purpose I/O pins to be shared with other function pins depending on the chip configuration. These 56 pins are arranged in 6 ports named as GPIOA, GPIOB, GPIOC, GPIOD, GPIOE and GPIOF. The GPIOA/B port has the maximum of 16 pins. The GPIOC port has the maximum of 12 pins. The GPIOD port has the maximum of 4 pins. The GPIOE port has the maximum of 1 pin. The GPIOF port has the maximum of 7 pins. Each of the 56 pins is independent and has the corresponding register bits to control the pin mode function and data.

The I/O type of each of I/O pins can be configured by software individually as input, output, opendrain or Quasi-bidirectional mode. After reset, the I/O mode of all pins are depending on Config0[10] setting. In Quasi-bidirectional mode, I/O pin has a very weak individual pull-up resistor which is about 110~300 K $\Omega$  for V<sub>DD</sub> from 5.0 V to 2.5 V.

### 6.5.2 Features

- Four I/O modes:

- Quasi-bidirectional

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable by GPx\_TYPE[15:0] in GPx\_MFP[31:16]

- I/O pin configured as interrupt source with edge/level setting

- Configurable default I/O mode of all pins after reset by Config0[10] setting

- If Config[10] is 0, all GPIO pins in input tri-state mode after chip reset

- If Config[10] is 1, all GPIO pins in Quasi-bidirectional mode after chip reset

- I/O pin internal pull-up resistor enabled only in Quasi-bidirectional I/O mode

- Enabling the pin interrupt function will also enable the pin wake-up function

### 6.9 Watchdog Timer (WDT)

#### 6.9.1 Overview

The purpose of Watchdog Timer is to perform a system reset when system runs into an unknown state. This prevents system from hanging for an infinite period of time. Besides, this Watchdog Timer supports the function to wake-up system from Idle/Power-down mode.

#### 6.9.2 Features

- 18-bit free running up counter for Watchdog Timer time-out interval.

- Selectable time-out interval (2<sup>4</sup> ~ 2<sup>18</sup>) WDT\_CLK cycle and the time-out interval period is 104 ms ~ 26.3168 s if WDT\_CLK = 10 kHz.

- System kept in reset state for a period of (1 / WDT\_CLK) \* 63

- Supports Watchdog Timer reset delay period

- Selectable it includes (1026 \ 130 \ 18 or 3) \* WDT\_CLK reset delay period.

- Supports to force Watchdog Timer enabled after chip powered on or reset while CWDTEN (CONFIG0[31] Watchdog Enable) bit is set to 0.

- Supports Watchdog Timer time-out wake-up function only if WDT clock source is selected as 10 kHz

### 6.13 Serial Peripheral Interface (SPI)

#### 6.13.1 Overview

The Serial Peripheral Interface (SPI) is a synchronous serial data communication protocol that operates in full duplex mode. Devices communicate in Master/Slave mode with the 4-wire bidirection interface. The NuMicro<sup>™</sup> M0518 series contains one set of SPI controllers performing a serial-to-parallel conversion on data received from a peripheral device, and a parallel-to-serial conversion on data transmitted to a peripheral device. This SPI controller can be configured as a master or a slave device.

The SPI controller supports the variable bus clock function for special applications.

### 6.13.2 Features

- One set of SPI controller

- Supports Master or Slave mode operation

- Supports Dual I/O Transfer mode

- Configurable bit length of a transaction word from 8 to 32 bits

- Provides separate 8-layer depth transmit and receive FIFO buffers

- Supports MSB first or LSB first transfer sequence

- Supports the Byte Reorder function

- Supports Byte or Word Suspend mode

- Variable output bus clock frequency in Master mode

- Supports 3-wire, no slave select signal, bi-direction interface

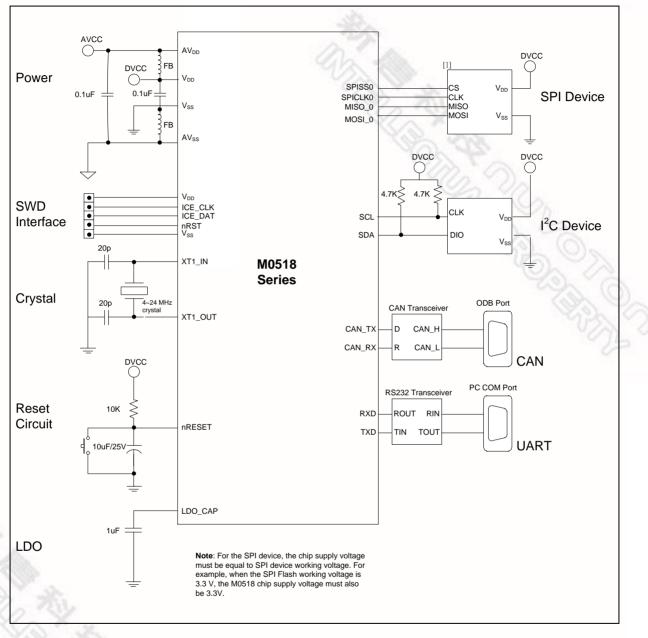

### 7 APPLICATION CIRCUIT

### 8.3 AC Electrical Characteristics

### 8.3.1 External 4~24 MHz High Speed Oscillator

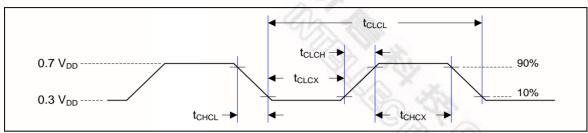

Note: Duty cycle is 50%.

| SYMBOL            | PARAMETER       | CONDITION | MIN.    | TYP. | MAX. | UNIT |

|-------------------|-----------------|-----------|---------|------|------|------|

| STIVIBUL          | PARAMETER       | CONDITION | IVIIIN. | ITP. | WAA. | UNIT |

| t <sub>CHCX</sub> | Clock High Time |           | 10      | - 2  | 10   | nS   |

| t <sub>CLCX</sub> | Clock Low Time  |           | 10      | -    | R    | nS   |

| t <sub>CLCH</sub> | Clock Rise Time |           | 2       | -    | 15   | nS   |

| t <sub>CHCL</sub> | Clock Fall Time |           | 2       | -    | 15   | nS   |

### 8.3.2 External 4~24 MHz High Speed Crystal

| SYMBOL           | PARAMETER                  | CONDITION               | MIN. | TYP | MAX. | UNIT |

|------------------|----------------------------|-------------------------|------|-----|------|------|

| V <sub>HXT</sub> | Operation Voltage $V_{DD}$ | -                       | 2.5  | -   | 5.5  | V    |

| T <sub>A</sub>   | Temperature                | -                       | -40  | -   | 105  | °C   |

| I <sub>HXT</sub> | Operating Current          | 12 MHz at $V_{DD} = 5V$ | -    | 2   | -    | mA   |

|                  |                            | 12 MHz at $V_{DD} = 3V$ |      | 0.8 |      | mA   |

| f <sub>HXT</sub> | Clock Frequency            | External crystal        | 4    |     | 24   | MHz  |

8.3.2.1 Typical Crystal Application Circuits

| CRYSTAL        | C1      | C2      | R       |

|----------------|---------|---------|---------|

| 4 MHz ~ 24 MHz | 10~20pF | 10~20pF | without |

| Caro.          |         |         |         |

|                |         |         |         |

|                |         |         |         |

|                |         |         |         |

|                |         |         |         |

|                |         |         |         |

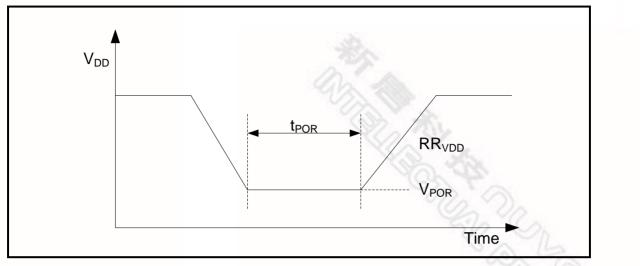

Figure 8-3 Power-up Ramp Condition

### 8.5 Flash DC Electrical Characteristics

| SYMBOL                          | PARAMETER       | CONDITIONS    | MIN.  | TYP. | MAX.     | UNIT                  |

|---------------------------------|-----------------|---------------|-------|------|----------|-----------------------|

| V <sub>FLA</sub> <sup>[2]</sup> | Supply Voltage  | pro la        | 1.62  | 1.8  | 1.98     | V <sup>[2]</sup>      |

| N <sub>ENDUR</sub>              | Endurance       | 92.3          | 20000 | -    | -        | cycles <sup>[1]</sup> |

| T <sub>RET</sub>                | Data Retention  | <b>At 85℃</b> | 100   | -    | -        | year                  |

| T <sub>ERASE</sub>              | Page Erase Time |               | 20    |      | -        | ms                    |

| T <sub>MER</sub>                | Mass Erase Time | 75            | 40    | Ż    | -        | ms                    |

| T <sub>PROG</sub>               | Program Time    |               | 40    | 0    | <u> </u> | μs                    |

Note:

1. Number of program/erase cycles.

2.  $V_{FLA}$  is source from chip LDO output voltage.

Figure 8-6 SPI Slave Mode Timing Diagram