Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 83                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 16K x 8                                                                 |

| RAM Size                   | 80K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 25x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 104-UFBGA, WLCSP                                                        |

| Supplier Device Package    | 104-WLCSP (5.09x4.1)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l162vey6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.7 Memories

The STM32L162xE devices have the following features:

- 80 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 512 Kbytes of embedded Flash program memory

- 16 Kbytes of data EEPROM

- Options bytes

Flash program and data EEPROM are divided into two banks, this enables writing in one bank while running code or reading data in the other bank.

The options bytes are used to write-protect or read-out protect the memory (with 4 Kbytes granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (ARM Cortex-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

# 3.8 DMA (direct memory access)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: AES, SPI, I<sup>2</sup>C, USART, general-purpose timers, DAC and ADC.

# 3.13 Ultra-low-power comparators and reference voltage

The STM32L162xE devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with fixed threshold

- One comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or a sub-multiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.14 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

# 3.15 Touch sensing

The STM32L162xE devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 34 capacitive sensing channels distributed over 11 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. The capacitive sensing acquisition only requires few external components to operate. This acquisition is managed directly by the GPIOs, timers and analog I/O groups (see Section 3.14: System configuration controller and routing interface).

Reliable touch sensing functionality can be quickly and easily implemented using the free STM32L1xx STMTouch touch sensing firmware library.

# 3.16 AES

The AES Hardware Accelerator can be used to encrypt and decrypt data using the AES

algorithm (compatible with FIPS PUB 197, 2001 Nov 26).

- Key scheduler

- Key derivation for decryption

- 128-bit data block processed

- 128-bit key length

- 213 clock cycles to encrypt/decrypt one 128-bit block

- Electronic codebook (ECB), cypher block chaining (CBC), and counter mode (CTR) supported by hardware.

AES data flow can be served by 2ch  $(D_{IN}/D_{OUT})$  of the DMA2 controller

## 3.17 Timers and watchdogs

The ultra-low-power STM32L162xE devices include seven general-purpose timers, two basic timers, and two watchdog timers.

*Table 6* compares the features of the general-purpose and basic timers.

| Timer                  | Counter resolution | Counter type         | Prescaler factor                   | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

|------------------------|--------------------|----------------------|------------------------------------|------------------------------|-----------------------------|--------------------------|

| TIM2,<br>TIM3,<br>TIM4 | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                          | 4                           | No                       |

| TIM5                   | 32-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                          | 4                           | No                       |

| TIM9                   | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | No                           | 2                           | No                       |

| TIM10,<br>TIM11        | 16-bit             | Up                   | Any integer between<br>1 and 65536 | No                           | 1                           | No                       |

| TIM6,<br>TIM7          | 16-bit             | Up                   | Any integer between<br>1 and 65536 | Yes                          | 0                           | No                       |

#### Table 6. Timer feature comparison

# 3.17.1 General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11)

There are seven synchronizable general-purpose timers embedded in the STM32L162xE devices (see *Table 6* for differences).

#### TIM2, TIM3, TIM4, TIM5

TIM2, TIM3, TIM4 are based on 16-bit auto-reload up/down counter. TIM5 is based on a 32bit auto-reload up/down counter. They include a 16-bit prescaler. They feature four independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input captures/output compares/PWMs on the largest packages.

TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together or with the TIM10, TIM11 and TIM9 general-purpose timers via the Timer Link feature for synchronization or

event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM10, TIM11 and TIM9

TIM10 and TIM11 are based on a 16-bit auto-reload upcounter. TIM9 is based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers.

They can also be used as simple time bases and be clocked by the LSE clock source (32.768 kHz) to provide time bases independent from the main CPU clock.

## 3.17.2 Basic timers (TIM6 and TIM7)

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

## 3.17.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches 0.

## 3.17.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

### 3.17.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.18 Communication interfaces

## 3.18.1 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

DocID025882 Rev 6

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 10: Voltage characteristics*, *Table 11: Current characteristics*, and *Table 12: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                              | Ratings                                                                         | Min                  | Мах                  | Unit |

|-------------------------------------|---------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> –V <sub>SS</sub>    | External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>      | Input voltage on five-volt tolerant pin                                         | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 | V    |

| VIN                                 | Input voltage on any other pin                                                  | V <sub>SS</sub> –0.3 | 4.0                  |      |

| ΔV <sub>DDx</sub>                   | Variations between different V <sub>DD</sub> power pins                         | -                    | 50                   | mV   |

| V <sub>SSX</sub> –V <sub>SS</sub>   | Variations between all different ground pins <sup>(3)</sup>                     | -                    | 50                   |      |

| V <sub>REF+</sub> –V <sub>DDA</sub> | Allowed voltage difference for $V_{REF+} > V_{DDA}$                             | -                    | 0.4                  | V    |

| V <sub>ESD(HBM)</sub>               | Electrostatic discharge voltage<br>(human body model)                           | see Sect             | ion 6.3.11           |      |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 11* for maximum allowed injected current values.

3. Include  $V_{REF-}$  pin.

#### Table 11. Current characteristics

| Symbol                               | Ratings                                                                        | Max.  | Unit |

|--------------------------------------|--------------------------------------------------------------------------------|-------|------|

| $I_{VDD(\Sigma)}$                    | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>   | 100   |      |

| $I_{VSS(\Sigma)}^{(2)}$              | Total current out of sum of all $V_{SS_x}$ ground lines (sink) <sup>(1)</sup>  | 100   |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each V <sub>DD_x</sub> power pin (source) <sup>(1)</sup>  | 70    | 1    |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS_x ground pin (sink) <sup>(1)</sup>             | -70   | 1    |

| 1                                    | Output current sunk by any I/O and control pin                                 | 25    | 1    |

| I <sub>IO</sub>                      | Output current sourced by any I/O and control pin                              | - 25  | mA   |

| ΣI                                   | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>    | 60    | 1    |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all IOs and control pins <sup>(2)</sup> | -60   |      |

| (3)                                  | Injected current on five-volt tolerant I/O <sup>(4)</sup> , RST and B pins     | -5/+0 | 1    |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on any other pin <sup>(5)</sup>                               | ± 5   |      |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>        | ± 25  | 1    |

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.17.

| Symbol | Parameter                  | Conditions       | Min | Max | Unit |

|--------|----------------------------|------------------|-----|-----|------|

| TJ     | Junction temperature range | 6 suffix version | -40 | 105 | °C   |

| IJ     | Sunction temperature range | 7 suffix version | -40 | 110 | C    |

#### Table 13. General operating conditions (continued)

1. When the ADC is used, refer to Table 55: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up .

3. To sustain a voltage higher than VDD+0.3V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 70: Thermal characteristics on page 124 ).

In low-power dissipation state, T<sub>A</sub> can be extended to -40°C to 105°C temperature range as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see *Table 70: Thermal characteristics on page 124*).

## 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the conditions summarized in *Table 13*.

| Symbol                               | Parameter                      | Conditions                                   | Min  | Тур  | Мах  | Unit  |

|--------------------------------------|--------------------------------|----------------------------------------------|------|------|------|-------|

|                                      | V <sub>DD</sub> rise time rate | BOR detector enabled                         | 0    | -    | 8    |       |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                | BOR detector disabled                        | 0    | -    | 1000 | μs/V  |

| ٩٥D                                  | V <sub>DD</sub> fall time rate | BOR detector enabled                         | 20   | -    | ∞    | μ3/ ν |

|                                      |                                | BOR detector disabled                        | 0    | -    | 1000 | ]     |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            | V <sub>DD</sub> rising, BOR enabled          | -    | 2    | 3.3  | - ms  |

| 'RSTTEMPO` '                         |                                | $V_{DD}$ rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6  | 1115  |

| N .                                  | Power on/power down reset      | Falling edge                                 | 1    | 1.5  | 1.65 |       |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                  | 1.3  | 1.5  | 1.65 | ]     |

| V                                    | Brown-out reset threshold 0    | Falling edge                                 | 1.67 | 1.7  | 1.74 | ]     |

| V <sub>BOR0</sub>                    |                                | Rising edge                                  | 1.69 | 1.76 | 1.8  | V     |

| N .                                  | Brown-out reset threshold 1    | Falling edge                                 | 1.87 | 1.93 | 1.97 |       |

| V <sub>BOR1</sub>                    |                                | Rising edge                                  | 1.96 | 2.03 | 2.07 | ]     |

| N .                                  | Brown-out reset threshold 2    | Falling edge                                 | 2.22 | 2.30 | 2.35 | ]     |

| V <sub>BOR2</sub>                    |                                | Rising edge                                  | 2.31 | 2.41 | 2.44 | ]     |

Table 14. Embedded reset and power control block characteristics

| Symbol            | Parameter                     | Conditions                                   | Min  | Тур  | Max  | Unit |

|-------------------|-------------------------------|----------------------------------------------|------|------|------|------|

| M                 | Drown out react threshold 2   | Falling edge                                 | 2.45 | 2.55 | 2.6  |      |

| V <sub>BOR3</sub> | Brown-out reset threshold 3   | Rising edge                                  | 2.54 | 2.66 | 2.7  |      |

| V                 | Brown-out reset threshold 4   | Falling edge                                 | 2.68 | 2.8  | 2.85 |      |

| V <sub>BOR4</sub> | BIOWN-OULTESEL INTESHOLU 4    | Rising edge                                  | 2.78 | 2.9  | 2.95 |      |

| V                 | Programmable voltage detector | Falling edge                                 | 1.8  | 1.85 | 1.88 |      |

| V <sub>PVD0</sub> | threshold 0                   | Rising edge                                  | 1.88 | 1.94 | 1.99 |      |

| V                 | PVD threshold 1               | Falling edge                                 | 1.98 | 2.04 | 2.09 |      |

| V <sub>PVD1</sub> |                               | Rising edge                                  | 2.08 | 2.14 | 2.18 |      |

| V                 | PVD threshold 2               | Falling edge                                 | 2.20 | 2.24 | 2.28 | v    |

| V <sub>PVD2</sub> |                               | Rising edge                                  | 2.28 | 2.34 | 2.38 |      |

| V                 | PVD threshold 3               | Falling edge                                 | 2.39 | 2.44 | 2.48 |      |

| V <sub>PVD3</sub> |                               | Rising edge                                  | 2.47 | 2.54 | 2.58 |      |

| V                 | PVD threshold 4               | Falling edge                                 | 2.57 | 2.64 | 2.69 |      |

| V <sub>PVD4</sub> |                               | Rising edge                                  | 2.68 | 2.74 | 2.79 |      |

| V                 | PVD threshold 5               | Falling edge                                 | 2.77 | 2.83 | 2.88 |      |

| V <sub>PVD5</sub> |                               | Rising edge                                  | 2.87 | 2.94 | 2.99 |      |

| V                 | PVD threshold 6               | Falling edge                                 | 2.97 | 3.05 | 3.09 |      |

| V <sub>PVD6</sub> |                               | Rising edge                                  | 3.08 | 3.15 | 3.20 |      |

|                   |                               | BOR0 threshold                               | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage            | All BOR and PVD<br>thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 14. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

| Symbol                             | Parameter          | С                                        | onditions                       |                                                                          | Тур  | Max <sup>(1)</sup> | Unit |

|------------------------------------|--------------------|------------------------------------------|---------------------------------|--------------------------------------------------------------------------|------|--------------------|------|

|                                    |                    |                                          |                                 | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 1.8 \text{ V}$ | 1.18 | -                  |      |

|                                    |                    |                                          | LCD                             | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.4  | 4                  |      |

|                                    |                    |                                          | OFF                             | T <sub>A</sub> = 55°C                                                    | 3.02 | 6                  |      |

|                                    |                    |                                          |                                 | T <sub>A</sub> = 85°C                                                    | 7.44 | 11                 |      |

|                                    |                    | RTC clocked by LSI or LSE external clock |                                 | T <sub>A</sub> = 105°C                                                   | 15.5 | 27                 |      |

|                                    |                    | (32.768kHz),                             | LCD                             | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.5  | 6                  |      |

|                                    |                    | regulator in LP mode,<br>HSI and HSE OFF | ON                              | T <sub>A</sub> = 55°C                                                    | 4.65 | 7                  |      |

|                                    |                    | (no independent                          | (static<br>duty) <sup>(2)</sup> | T <sub>A</sub> = 85°C                                                    | 9.07 | 13                 |      |

|                                    |                    | watchdog)                                | uuty)                           | T <sub>A</sub> = 105°C                                                   | 15.6 | 31                 |      |

|                                    |                    |                                          |                                 | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 3.9  | 10                 |      |

|                                    |                    |                                          | LCD<br>ON (1/8                  | T <sub>A</sub> = 55°C                                                    | 5.19 | 11                 |      |

|                                    |                    |                                          | duty) <sup>(3)</sup>            | T <sub>A</sub> = 85°C                                                    | 9.8  | 17                 |      |

|                                    |                    |                                          |                                 | T <sub>A</sub> = 105°C                                                   | 18.4 | 48                 |      |

|                                    | Supply current in  |                                          |                                 | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.65 | -                  |      |

| I <sub>DD</sub> (Stop<br>with RTC) | Stop mode with RTC |                                          | LCD                             | T <sub>A</sub> = 55°C                                                    | 3.32 | -                  | μA   |

| with IXIC)                         | enabled            |                                          | OFF                             | T <sub>A</sub> = 85°C                                                    | 7.83 | -                  |      |

|                                    |                    |                                          |                                 | T <sub>A</sub> = 105°C                                                   | 16   | -                  |      |

|                                    |                    |                                          |                                 | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.75 | -                  |      |

|                                    |                    |                                          | LCD<br>ON                       | T <sub>A</sub> = 55°C                                                    | 4.9  | -                  |      |

|                                    |                    | RTC clocked by LSE                       | (static<br>duty) <sup>(2)</sup> | T <sub>A</sub> = 85°C                                                    | 9.41 | -                  |      |

|                                    |                    | external quartz<br>(32.768kHz),          | uuty) (                         | T <sub>A</sub> = 105°C                                                   | 15.8 | -                  |      |

|                                    |                    | regulator in LP mode,                    |                                 | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 4.1  | -                  |      |

|                                    |                    | HSI and HSE OFF<br>(no independent       | LCD<br>ON (1/8                  | T <sub>A</sub> = 55°C                                                    | 5.53 | -                  |      |

|                                    |                    | watchdog <sup>(4)</sup>                  | duty) <sup>(3)</sup>            | T <sub>A</sub> = 85°C                                                    | 10   | -                  |      |

|                                    |                    |                                          |                                 | T <sub>A</sub> = 105°C                                                   | 18.5 | -                  |      |

|                                    |                    |                                          |                                 | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 1.8V$          | 1.33 | -                  |      |

|                                    |                    |                                          | LCD<br>OFF                      | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 3.0V$          | 1.62 | -                  |      |

|                                    |                    |                                          |                                 | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 3.6V$          | 1.87 | -                  |      |

| Table 22. Typical and maximum current consumptions in | n Stop mode |

|-------------------------------------------------------|-------------|

|-------------------------------------------------------|-------------|

| Symbol                                  | Parameter                                                 | Condit                                 | tions                                                                      | Тур   | Max <sup>(1)</sup> | Unit |

|-----------------------------------------|-----------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------|-------|--------------------|------|

|                                         |                                                           |                                        | $T_A = -40 \degree C \text{ to } 25 \degree C$<br>$V_{DD} = 1.8 \text{ V}$ | 0.865 | -                  |      |

|                                         |                                                           | RTC clocked by LSI (no                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                                    | 1.11  | 1.9                |      |

|                                         |                                                           | independent watchdog)                  | T <sub>A</sub> = 55 °C                                                     | 1.72  | 2.2                |      |

|                                         |                                                           |                                        | T <sub>A</sub> = 85 °C                                                     | 2.12  | 4                  |      |

| I <sub>DD</sub><br>(Standby             | Supply current in Standby mode with RTC                   |                                        | T <sub>A</sub> = 105 °C                                                    | 2.54  | 8.3 <sup>(2)</sup> |      |

| with RTC)                               | enabled                                                   |                                        | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V                | 0.97  | -                  |      |

|                                         |                                                           | RTC clocked by LSE external quartz (no | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                                    | 1.28  | -                  |      |

|                                         |                                                           | independent                            | T <sub>A</sub> = 55 °C                                                     | 2.01  | -                  | μA   |

|                                         |                                                           | watchdog) <sup>(3)</sup>               | T <sub>A</sub> = 85 °C                                                     | 2.5   | -                  |      |

|                                         |                                                           |                                        | T <sub>A</sub> = 105 °C                                                    | 2.98  | -                  |      |

|                                         |                                                           | Independent watchdog and LSI enabled   | $T_A = -40 \text{ °C to } 25 \text{ °C}$                                   | 1     | 1.7                |      |

| I <sub>DD</sub>                         | Supply current in                                         |                                        | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                                    | 0.29  | 1                  |      |

| (Standby)                               | Standby mode (RTC disabled)                               | Independent watchdog                   | T <sub>A</sub> = 55 °C                                                     | 0.96  | 1.3                |      |

|                                         |                                                           | and LSI OFF                            | T <sub>A</sub> = 85 °C                                                     | 1.38  | 3                  |      |

|                                         |                                                           |                                        | T <sub>A</sub> = 105 °C                                                    | 1.98  | 7 <sup>(2)</sup>   |      |

| I <sub>DD</sub><br>(WU from<br>Standby) | Supply current during<br>wakeup time from<br>Standby mode | -                                      | T <sub>A</sub> = -40 °C to 25 °C                                           | 1     | -                  | mA   |

| Table 23. Typical and maximum current consumptions in Standby m |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

1. Guaranteed by characterization results, unless otherwise specified.

2. Guaranteed by test in production.

3. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in the following table. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

| Symbol                  | Parameter                                                                            | Conditions                                                              | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|--------------------|------|

| t <sub>WUSLEEP</sub>    | Wakeup from Sleep mode                                                               | f <sub>HCLK</sub> = 32 MHz                                              | 0.4  | -                  |      |

|                         | Wakeup from Low-power sleep                                                          | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                            | 46   | -                  |      |

| <sup>t</sup> wusleep_lp | mode, f <sub>HCLK</sub> = 262 kHz                                                    | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                       | 46   | -                  |      |

|                         | Wakeup from Stop mode,<br>regulator in Run mode<br>ULP bit = 1 and FWU bit = 1       | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                          | 8.2  | -                  |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 and 2 | 7.7  | 8.9                |      |

|                         | Wakeup from Stop mode,<br>regulator in low-power mode<br>ULP bit = 1 and FWU bit = 1 | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3       | 8.2  | 13.1               | μs   |

| tWUSTOP                 |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                          | 10.2 | 13.4               |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                         | 16   | 20                 |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                          | 31   | 37                 |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                          | 57   | 66                 |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                          | 112  | 123                |      |

|                         |                                                                                      | f <sub>HCLK</sub> = MSI = 65 kHz                                        | 221  | 236                |      |

|                         | Wakeup from Standby mode<br>ULP bit = 1 and FWU bit = 1                              | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 58   | 104                |      |

| <sup>t</sup> wustdby    | Wakeup from Standby mode<br>FWU bit = 0                                              | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 2.6  | 3.25               | ms   |

Table 25. Low-power mode wakeup timings

1. Guaranteed by characterization, unless otherwise specified

## 6.3.6 External clock source characteristics

.

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.12*. However, the recommended clock input waveform is shown in *Figure 13*.

| Table 26 | High-speed | external | user clock | characteristics <sup>(1)</sup> |

|----------|------------|----------|------------|--------------------------------|

|          |            |          |            |                                |

| Symbol               | Parameter                                   | Conditions                  | Min | Тур | Max | Unit |

|----------------------|---------------------------------------------|-----------------------------|-----|-----|-----|------|

| f                    | _ <sup>ext</sup> User external clock source | CSS is on or<br>PLL is used | 1   | 8   | 32  | MHz  |

| <sup>T</sup> HSE_ext |                                             | CSS is off, PLL<br>not used | 0   | 8   | 32  | MHz  |

# 6.3.13 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the conditions summarized in *Table 13*. All I/Os are CMOS and TTL compliant.

| Symbol                    | Parameter                                          | Conditions                                                                                | Min                                       | Тур                                | Мах                                   | Unit |

|---------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|---------------------------------------|------|

| N/                        |                                                    | TC and FT I/O                                                                             | -                                         | -                                  | 0.3 V <sub>DD</sub> <sup>(1)(2)</sup> |      |

| V <sub>IL</sub>           | Input low level voltage                            | BOOT0                                                                                     | -                                         | -                                  | 0.14 V <sub>DD</sub> <sup>(2)</sup>   |      |

|                           |                                                    | TC I/O                                                                                    | 0.45 V <sub>DD</sub> +0.38 <sup>(2)</sup> | -                                  | -                                     |      |

| $V_{\rm IH}$              | H Input high level voltage                         | FT I/O                                                                                    | 0.39 V <sub>DD</sub> +0.59 <sup>(2)</sup> | -                                  | -                                     | V    |

|                           |                                                    | BOOT0                                                                                     | 0.15 V <sub>DD</sub> +0.56 <sup>(2)</sup> | -                                  | -                                     |      |

| V                         | I/O Schmitt trigger voltage                        | TC and FT I/O                                                                             | -                                         | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                     |      |

| V <sub>hys</sub>          | hysteresis <sup>(2)</sup>                          | BOOT0                                                                                     | -                                         | 0.01                               | -                                     |      |

| I <sub>lkg</sub> Input le |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with LCD                        | -                                         | -                                  | ±50                                   |      |

|                           | Input leakage current <sup>(4)</sup>               | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches         | -                                         | -                                  | ±50                                   |      |

|                           |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches and LCD | -                                         | -                                  | ±50                                   | nA   |

|                           |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with USB                        | -                                         | -                                  | ±250                                  |      |

|                           |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>TC and FT I/Os                       | -                                         | -                                  | ±50                                   |      |

|                           |                                                    | FT I/O<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5V                                            | -                                         | -                                  | ±10                                   | μA   |

| R <sub>PU</sub>           | Weak pull-up equivalent resistor <sup>(5)(1)</sup> | $V_{IN} = V_{SS}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ   |

| R <sub>PD</sub>           | Weak pull-down equivalent resistor <sup>(5)</sup>  | $V_{IN} = V_{DD}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ   |

| C <sub>IO</sub>           | I/O pin capacitance                                | -                                                                                         | -                                         | 5                                  | -                                     | pF   |

| Table 42 | . I/O | static | characteristics |

|----------|-------|--------|-----------------|

|          |       | Static | characteristics |

1. Guaranteed by test in production

2. Guaranteed by design.

3. With a minimum of 200 mV.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

## 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 45*)

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under the conditions summarized in *Table 13*.

| Symbol                                | Parameter                                          | Conditions                                                   | Min                       | Тур                               | Max                 | Unit |

|---------------------------------------|----------------------------------------------------|--------------------------------------------------------------|---------------------------|-----------------------------------|---------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                       | -                                                            | -                         | -                                 | 0.3 V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high<br>level voltage                   | -                                                            | 0.39V <sub>DD</sub> +0.59 | -                                 | -                   | V    |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | NRST output low                                    | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -                         | -                                 | 0.4                 | v    |

| VOL(NRST)                             | level voltage                                      | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -                         | -                                 | 0.4                 |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage hysteresis            | -                                                            | -                         | 10%V <sub>DD</sub> <sup>(2)</sup> | -                   | mV   |

| R <sub>PU</sub>                       | Weak pull-up<br>equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30                        | 45                                | 60                  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered<br>pulse                       | -                                                            | -                         | -                                 | 50                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(3)</sup>  | NRST input not<br>filtered pulse                   | -                                                            | 350                       | -                                 | -                   | ns   |

Table 45. NRST pin characteristics

1. Guaranteed by design.

2. With a minimum of 200 mV.

3. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

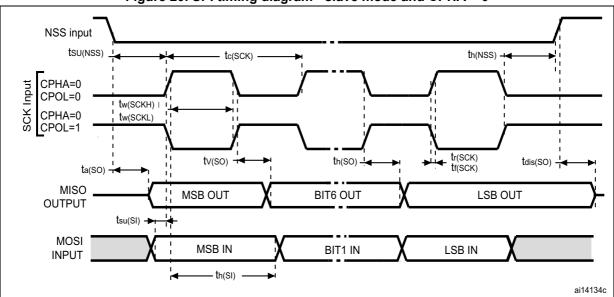

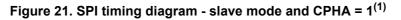

Figure 20. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}.}$

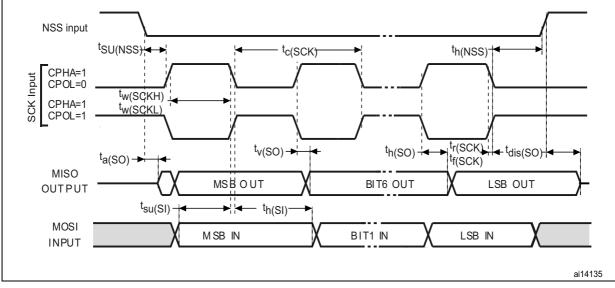

Figure 22. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

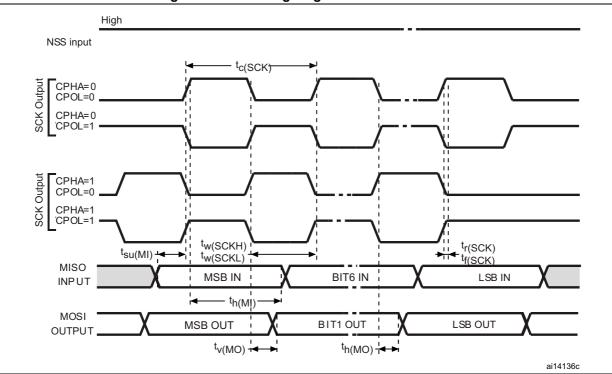

#### **Electrical characteristics**

| Symbol | Parameter                            | Test conditions                                                                                                                                                                           | Min <sup>(3)</sup> | Тур | Max <sup>(3)</sup> | Unit |

|--------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| ET     | Total unadjusted error               |                                                                                                                                                                                           | -                  | 2.5 | 4                  |      |

| EO     | Offset error                         | $2.4 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                                                                                             | -                  | 1   | 2                  |      |

| EG     | Gain error                           | 2.4 V ≤V <sub>REF+</sub> ≤ 3.6 V<br>f <sub>ADC</sub> = 8 MHz, R <sub>AIN</sub> = 50 Ω                                                                                                     | -                  | 1.5 | 3.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 °C                                                                                                                                                                     | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                                                                                                           | -                  | 2.2 | 3                  |      |

| ENOB   | Effective number of bits             |                                                                                                                                                                                           | 9.2                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | 2.4 V ≤V <sub>DDA</sub> ≤ 3.6 V<br>V <sub>DDA</sub> = V <sub>REF+</sub><br>f <sub>ADC</sub> = 16 MHz, R <sub>AIN</sub> = 50 Ω                                                             | 57.5               | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | $T_A = -40$ to 105 °C                                                                                                                                                                     | 57.5               | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10kHz                                                                                                                                                                 | -                  | -70 | -65                |      |

| ENOB   | Effective number of bits             | 1.8 V $\leq$ V <sub>DDA</sub> $\leq$ 2.4 V<br>V <sub>DDA</sub> = V <sub>REF+</sub><br>f <sub>ADC</sub> = 8 MHz or 4 MHz, R <sub>AIN</sub> = 50 $\Omega$<br>T <sub>A</sub> = -40 to 105 °C | 9.2                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio |                                                                                                                                                                                           | 57.5               | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                |                                                                                                                                                                                           | 57.5               | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10kHz                                                                                                                                                                 | -                  | -70 | -65                |      |

| ET     | Total unadjusted error               |                                                                                                                                                                                           | -                  | 4   | 6.5                |      |

| EO     | Offset error                         | $2.4 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                                                                                             | -                  | 1.5 | 4                  |      |

| EG     | Gain error                           | 1.8 V ≤V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω                                                                                                     | -                  | 3.5 | 6                  | LSB  |

| ED     | Differential linearity error         | $T_{A} = -40$ to 105 °C                                                                                                                                                                   | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                                                                                                           | -                  | 2.5 | 3                  |      |

| ET     | Total unadjusted error               |                                                                                                                                                                                           | -                  | 2   | 3                  |      |

| EO     | Offset error                         | 1.8 V ≤V <sub>DDA</sub> ≤ 2.4 V<br>1.8 V ≤V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω                                                                  | -                  | 1   | 1.5                |      |

| EG     | Gain error                           |                                                                                                                                                                                           | -                  | 1.5 | 2                  | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 °C                                                                                                                                                                     | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                                                                                                           | -                  | 2.2 | 3                  |      |

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.12 does not affect the ADC accuracy.

3. Guaranteed by characterization results.

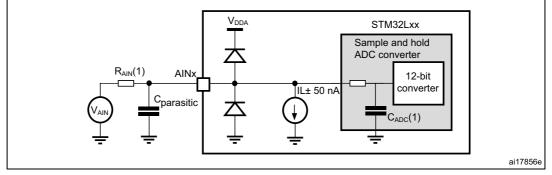

#### Figure 27. Typical connection diagram using the ADC

- 1. Refer to Table 57: Maximum source impedance RAIN max for the value of  $R_{AIN}$  and Table 55: ADC characteristics for the value of  $C_{ADC}$ .

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

| Symbol                    | Parameter                                                                                                                                                       | Conditions                                                                                                  | Min | Тур          | Max          | Unit   |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|--------------|--------------|--------|

| dOffset/dT <sup>(1)</sup> | Offset error temperature                                                                                                                                        | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0V$<br>$T_A = 0 \text{ to } 50 ^{\circ}\text{C}$<br>DAC output buffer OFF | -20 | -10          | 0            | W//°C  |

|                           | coefficient (code 0x800)                                                                                                                                        | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0V$<br>$T_A = 0 \text{ to } 50 ^{\circ}\text{C}$<br>DAC output buffer ON  | 0   | 20           | 50           | μV/°C  |

| Gain <sup>(1)</sup>       | Gain error <sup>(7)</sup>                                                                                                                                       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                                  | -   | +0.1 / -0.2% | +0.2 / -0.5% | %      |

| Gain                      | Gainenor                                                                                                                                                        | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                                                 | -   | +0 / -0.2%   | +0 / -0.4%   | 70     |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                          | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0V$<br>$T_A = 0 \text{ to } 50 \degree \text{C}$<br>DAC output buffer OFF | -10 | -2           | 0            | ∙μV/°C |

| dGain/d I                 | coefficient                                                                                                                                                     | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0V$<br>$T_A = 0 \text{ to } 50 ^{\circ}\text{C}$<br>DAC output buffer ON  | -40 | -8           | 0            | μν/ Ο  |

| TUE <sup>(1)</sup>        | Total upadiusted error                                                                                                                                          | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                              | -   | 12           | 30           | LSB    |

|                           | Total unadjusted error                                                                                                                                          | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                                                 | -   | 8            | 12           | LOD    |

| tsettling                 | Settling time (full scale:<br>for a 12-bit code<br>transition between the<br>lowest and the highest<br>input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$                                                         | -   | 7            | 12           | μs     |

| Update rate               | Max frequency for a<br>correct DAC_OUT<br>change (95% of final<br>value) with 1 LSB<br>variation in the input<br>code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                                          | -   | -            | 1            | Msps   |

| <sup>t</sup> wakeup       | Wakeup time from off<br>state (setting the ENx bit<br>in the DAC Control<br>register) <sup>(8)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                                          | -   | 9            | 15           | μs     |

| PSRR+                     | V <sub>DDA</sub> supply rejection<br>ratio (static DC<br>measurement)                                                                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                                          | -   | -60          | -35          | dB     |

Table 58. DAC characteristics (continued)

1. Data based on characterization results.

2. Connected between DAC\_OUT and  $\mathsf{V}_{\mathsf{SSA}}.$

3. Difference between two consecutive codes - 1 LSB.

# 6.3.20 Temperature sensor characteristics

| Calibration value name | Description                                                                                                   | Memory address            |

|------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C $\pm$ 5 °C V <sub>DDA</sub> = 3 V $\pm$ 10 mV                | 0x1FF8 00FA - 0x1FF8 00FB |

| TS_CAL2                | TS ADC raw data acquired at temperature of 110 $^{\circ}C \pm 5 ^{\circ}C$ V <sub>DDA</sub> = 3 V $\pm 10$ mV | 0x1FF8 00FE - 0x1FF8 00FF |

Table 60. Temperature sensor calibration values

| Table 61 | . Temperature | sensor | characteristics |

|----------|---------------|--------|-----------------|

|----------|---------------|--------|-----------------|

| Symbol                                | Parameter                                      | Min  | Тур   | Max       | Unit  |

|---------------------------------------|------------------------------------------------|------|-------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1    | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61  | 1.75      | mV/°C |

| V <sub>110</sub>                      | Voltage at 110°C ±5°C <sup>(2)</sup>           | 612  | 626.8 | 641.5     | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4   | 6         | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   | -    | -     | 10        |       |

| T <sub>S_temp</sub> <sup>(3)</sup>    | ADC sampling time when reading the temperature | 4    | -     | -         | μs    |

1. Guaranteed by characterization results.

2. Measured at V\_{DD} = 3 V  $\pm$ 10 mV. V110 ADC conversion result is stored in the TS\_CAL2 byte.

3. Guaranteed by design.

## 6.3.21 Comparator

| Symbol                   | Parameter                                                            | Conditions                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |

|--------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|--|

| V <sub>DDA</sub>         | Analog supply voltage                                                | -                                                                         | 1.65               |     | 3.6                | V         |  |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                              | -                                                                         | -                  | 400 | kΩ                 |           |  |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                               | -                                                                         | -                  | 10  | -                  | K22       |  |

| V <sub>IN</sub>          | Comparator 1 input<br>voltage range                                  | -                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |  |

| t <sub>START</sub>       | Comparator startup time                                              | -                                                                         | -                  | 7   | 10                 |           |  |

| td                       | Propagation delay <sup>(2)</sup>                                     | -                                                                         | -                  | 3   | 10                 | 10 µs     |  |

| Voffset                  | Comparator offset                                                    | -                                                                         | -                  | ±3  | ±10                | mV        |  |

| d <sub>Voffset</sub> /dt | Comparator offset<br>variation in worst voltage<br>stress conditions | $V_{DDA} = 3.6 V$ $V_{IN+} = 0 V$ $V_{IN-} = V_{REFINT}$ $T_{A} = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |  |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                                   | -                                                                         | -                  | 160 | 260                | nA        |  |

Table 62. Comparator 1 characteristics

|        |             |        | data   |                       |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |  |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| D1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| D3     | -           | 17.500 | -      | -                     | 0.6890 | -      |  |

| Е      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| E1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| E3     | -           | 17.500 | -      | -                     | 0.6890 | -      |  |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |  |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |  |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

| Table 65. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical |

|---------------------------------------------------------------------------------|

| data                                                                            |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| Symbol             | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------------------|-------------|-------|-------|-----------------------|--------|--------|--|

|                    | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А                  | 0.525       | 0.555 | 0.585 | 0.0207                | 0.0219 | 0.023  |  |

| A1                 | -           | 0.175 | -     | -                     | 0.0069 | -      |  |

| A2                 | -           | 0.38  | -     | -                     | 0.015  | -      |  |

| A3 <sup>(2)</sup>  | -           | 0.025 | -     | -                     | 0.001  | -      |  |

| ø b <sup>(3)</sup> | 0.22        | 0.25  | 0.28  | 0.0087                | 0.0098 | 0.011  |  |

| D                  | 4.06        | 4.095 | 4.13  | 0.1598                | 0.1612 | 0.1626 |  |

| E                  | 5.059       | 5.094 | 5.129 | 0.1992                | 0.2006 | 0.2019 |  |

| е                  | -           | 0.4   | -     | -                     | 0.0157 | -      |  |

| e1                 | -           | 3.2   | -     | -                     | 0.126  | -      |  |

| e2                 | -           | 4.4   | -     | -                     | 0.1732 | -      |  |

| F                  | -           | 0.447 | -     | -                     | 0.0176 | -      |  |

| G                  | -           | 0.347 | -     | -                     | 0.0137 | -      |  |

| aaa                | -           | -     | 0.1   | -                     | -      | 0.0039 |  |

| bbb                | -           | -     | 0.1   | -                     | -      | 0.0039 |  |

| ccc                | -           | -     | 0.1   | -                     | -      | 0.0039 |  |

| ddd                | -           | -     | 0.05  | -                     | -      | 0.002  |  |

| eee                | -           | -     | 0.05  | -                     | -      | 0.002  |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

# Figure 40. WLCSP104, 0.4 mm pitch wafer level chip scale package recommended footprint