Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 119                                                                              |

| Program Memory Size        | 384КВ (384К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xe167gm-48f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2011-07 Published by Infineon Technologies AG 81726 Munich, Germany © 2011 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Summary of Features**

# 16-Bit Single-Chip Real Time Signal Controller

XE167xM (XE166 Family)

# 1 Summary of Features

For a quick overview and easy reference, the features of the XE167xM are summarized here.

- High-performance CPU with five-stage pipeline and MPU

- 12.5 ns instruction cycle at 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1024 Bytes on-chip special function register area (C166 Family compatible)

- Integrated Memory Protection Unit (MPU)

- · Interrupt system with 16 priority levels for up to 96 sources

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- Up to 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 32 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 576 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

- On-Chip Peripheral Modules

- Multi-functional general purpose timer unit with 5 timers

- 16-channel general purpose capture/compare unit (CAPCOM2)

- Up to 4 capture/compare units for flexible PWM signal generation (CCU6x)

#### Summary of Features

### 1.2 Definition of Feature Variants

The XE167xM types are offered with several Flash memory sizes. **Table 2** describes the location of the available memory areas for each Flash memory size.

| Table 2 | Flash Memor | y Allocation |

|---------|-------------|--------------|

|---------|-------------|--------------|

| Total Flash Size | Flash Area A <sup>1)</sup> | Flash Area B         | Flash Area C         |

|------------------|----------------------------|----------------------|----------------------|

| 576 Kbytes       | C0'0000 <sub>H</sub>       | C1'0000 <sub>H</sub> | CC'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>       | C7'FFFF <sub>H</sub> | CC'FFFF <sub>H</sub> |

| 384 Kbytes       | C0'0000 <sub>H</sub>       | C1'0000 <sub>H</sub> | CC'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>       | C4'FFFF <sub>H</sub> | CC'FFFF <sub>H</sub> |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

#### Table 3 Flash Memory Module Allocation (in Kbytes)

| Total Flash Size | Flash 0 <sup>1)</sup> | Flash 1 | Flash 2 | Flash 3 |

|------------------|-----------------------|---------|---------|---------|

| 576 Kbytes       | 256                   | 256     |         | 64      |

| 384 Kbytes       | 256                   | 64      |         | 64      |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

The XE167xM types are offered with different interface options. Table 4 lists the available channels for each option.

| Total Number      | Available Channels                                        |

|-------------------|-----------------------------------------------------------|

| 16 ADC0 channels  | CH0 CH15                                                  |

| 8 ADC0 channels   | CH0 CH7                                                   |

| 8 ADC1 channels   | CH0 CH7 (overlay: CH8 CH11)                               |

| 6 CAN nodes       | CAN0, CAN1, CAN2, CAN3, CAN4, CAN5<br>128 message objects |

| 2 CAN nodes       | CAN0, CAN1<br>128 message objects                         |

| 8 serial channels | U0C0, U0C1, U1C0, U1C1, U2C0, U2C1, U3C0, U3C1            |

| 4 serial channels | U0C0, U0C1, U1C0, U1C1                                    |

#### Table 4 Interface Channel Association

#### **Summary of Features**

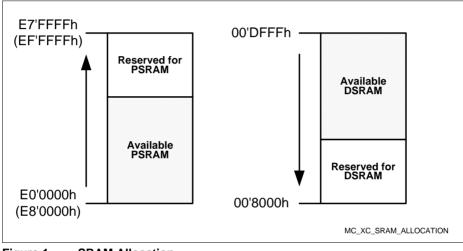

The XE167xM types are offered with several SRAM memory sizes. **Figure 1** shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- PSRAM allocation starts from the lower address

- DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

#### **General Device Information**

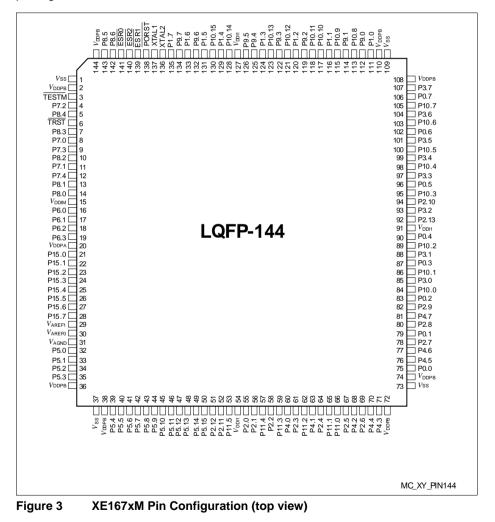

# 2.1 Pin Configuration and Definition

The pins of the XE167xM are described in detail in **Table 5**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. The following figure summarizes all pins, showing their locations on the four sides of the package.

| Table | Table 5         Pin Definitions and Functions (cont'd) |            |      |                                                   |  |  |

|-------|--------------------------------------------------------|------------|------|---------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                          |  |  |

| 56    | P2.1                                                   | O0 / I     | St/B | Bit 1 of Port 2, General Purpose Input/Output     |  |  |

|       | TxDC0                                                  | 01         | St/B | CAN Node 0 Transmit Data Output                   |  |  |

|       | CCU63_CC6<br>1                                         | O2         | St/B | CCU63 Channel 1 Output                            |  |  |

|       | AD14                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 14       |  |  |

|       | RxDC5C                                                 | I          | St/B | CAN Node 5 Receive Data Input                     |  |  |

|       | CCU63_CC6<br>1INB                                      | I          | St/B | CCU63 Channel 1 Input                             |  |  |

|       | T5EUDB                                                 | I          | St/B | GPT12E Timer T5 External Up/Down Control<br>Input |  |  |

|       | ESR1_5                                                 | I          | St/B | ESR1 Trigger Input 5                              |  |  |

| 57    | P11.4                                                  | O0 / I     | St/B | Bit 4 of Port 11, General Purpose Input/Output    |  |  |

|       | CCU61_CC6<br>2                                         | 01         | St/B | CCU61 Channel 2 Output                            |  |  |

|       | U3C1_DOUT                                              | 02         | St/B | USIC3 Channel 1 Shift Data Output                 |  |  |

|       | RxDC5B                                                 | I          | St/B | CAN Node 5 Receive Data Input                     |  |  |

|       | CCU61_CC6<br>2INB                                      | I          | St/B | CCU61 Channel 2 Input                             |  |  |

|       | U3C1_DX0B                                              | I          | St/B | USIC3 Channel 1 Shift Data Input                  |  |  |

| 58    | P2.2                                                   | O0 / I     | St/B | Bit 2 of Port 2, General Purpose Input/Output     |  |  |

|       | TxDC1                                                  | 01         | St/B | CAN Node 1 Transmit Data Output                   |  |  |

|       | CCU63_CC6<br>2                                         | O2         | St/B | CCU63 Channel 2 Output                            |  |  |

|       | AD15                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 15       |  |  |

|       | CCU63_CC6<br>2INB                                      | I          | St/B | CCU63 Channel 2 Input                             |  |  |

|       | ESR2_5                                                 | I          | St/B | ESR2 Trigger Input 5                              |  |  |

| Tabl | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                               |  |  |

|------|--------------------------------------------------------|--------|------|-----------------------------------------------|--|--|

| Pin  | Symbol                                                 | Ctrl.  | Туре | Function                                      |  |  |

| 75   | P0.0                                                   | O0 / I | St/B | Bit 0 of Port 0, General Purpose Input/Output |  |  |

|      | U1C0_DOUT                                              | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |  |

|      | CCU61_CC6<br>0                                         | O3     | St/B | CCU61 Channel 0 IOutput                       |  |  |

|      | A0                                                     | OH     | St/B | External Bus Interface Address Line 0         |  |  |

|      | U1C0_DX0A                                              | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |  |

|      | CCU61_CC6<br>0INA                                      | I      | St/B | CCU61 Channel 0 Input                         |  |  |

|      | ESR1_11                                                | I      | St/B | ESR1 Trigger Input 11                         |  |  |

| 76   | P4.5                                                   | O0 / I | St/B | Bit 5 of Port 4, General Purpose Input/Output |  |  |

|      | U3C0_DOUT                                              | 01     | St/B | USIC3 Channel 0 Shift Data Output             |  |  |

|      | CC2_CC29                                               | O3 / I | St/B | CAPCOM2 CC29IO Capture Inp./Compare Out.      |  |  |

|      | CCU61_CCP<br>OS0A                                      | I      | St/B | CCU61 Position Input 0                        |  |  |

|      | U3C0_DX0B                                              | I      | St/B | USIC3 Channel 0 Shift Data Input              |  |  |

|      | ESR2_10                                                | I      | St/B | ESR2 Trigger Input 10                         |  |  |

| 77   | P4.6                                                   | O0 / I | St/B | Bit 6 of Port 4, General Purpose Input/Output |  |  |

|      | U3C0_DOUT                                              | 01     | St/B | USIC3 Channel 0 Shift Data Output             |  |  |

|      | CC2_CC30                                               | O3 / I | St/B | CAPCOM2 CC30IO Capture Inp./ Compare Out.     |  |  |

|      | T4INA                                                  | I      | St/B | GPT12E Timer T4 Count/Gate Input              |  |  |

|      | CCU61_CCP<br>OS1A                                      | I      | St/B | CCU61 Position Input 1                        |  |  |

| 78   | P2.7                                                   | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |  |

|      | U0C1_SELO<br>0                                         | 01     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |  |

|      | U0C0_SELO<br>1                                         | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |  |

|      | CC2_CC20                                               | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |  |

|      | A20                                                    | ОН     | St/B | External Bus Interface Address Line 20        |  |  |

|      | U0C1_DX2C                                              | I      | St/B | USIC0 Channel 1 Shift Control Input           |  |  |

|      | RxDC1C                                                 | I      | St/B | CAN Node 1 Receive Data Input                 |  |  |

|      | ESR2_7                                                 | I      | St/B | ESR2 Trigger Input 7                          |  |  |

| Table | Table 5Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------|-----------------------------------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                             |  |  |  |

| 82    | P2.9                                          | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output                                                                                                                                                                                                                                                        |  |  |  |

|       | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |  |  |  |

|       | TxDC1                                         | O2     | St/B | CAN Node 1 Transmit Data Output                                                                                                                                                                                                                                                                      |  |  |  |

|       | CC2_CC22                                      | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.                                                                                                                                                                                                                                                            |  |  |  |

|       | A22                                           | ОН     | St/B | External Bus Interface Address Line 22                                                                                                                                                                                                                                                               |  |  |  |

|       | CLKIN1                                        | I      | St/B | Clock Signal Input 1                                                                                                                                                                                                                                                                                 |  |  |  |

|       | TCK_A                                         | IH     | St/B | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. A is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 0 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |  |

| 83    | P0.2                                          | O0 / I | St/B | Bit 2 of Port 0, General Purpose Input/Output                                                                                                                                                                                                                                                        |  |  |  |

|       | U1C0_SCLK<br>OUT                              | 01     | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                                                                                                                                                   |  |  |  |

|       | TxDC0                                         | 02     | St/B | CAN Node 0 Transmit Data Output                                                                                                                                                                                                                                                                      |  |  |  |

|       | CCU61_CC6<br>2                                | O3     | St/B | CCU61 Channel 2 Output                                                                                                                                                                                                                                                                               |  |  |  |

|       | A2                                            | ОН     | St/B | External Bus Interface Address Line 2                                                                                                                                                                                                                                                                |  |  |  |

|       | U1C0_DX1B                                     | I      | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                    |  |  |  |

|       | CCU61_CC6<br>2INA                             | I      | St/B | CCU61 Channel 2 Input                                                                                                                                                                                                                                                                                |  |  |  |

| Table | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |  |

|-------|--------------------------------------------------------|--------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                       |  |  |  |

| 90    | P0.4                                                   | O0 / I | St/B | Bit 4 of Port 0, General Purpose Input/Output  |  |  |  |

|       | U1C1_SELO<br>0                                         | O1     | St/B | USIC1 Channel 1 Select/Control 0 Output        |  |  |  |

|       | U1C0_SELO<br>1                                         | O2     | St/B | USIC1 Channel 0 Select/Control 1 Output        |  |  |  |

|       | CCU61_COU<br>T61                                       | O3     | St/B | CCU61 Channel 1 Output                         |  |  |  |

|       | A4                                                     | ОН     | St/B | External Bus Interface Address Line 4          |  |  |  |

|       | U1C1_DX2A                                              | I      | St/B | USIC1 Channel 1 Shift Control Input            |  |  |  |

|       | RxDC1B                                                 | I      | St/B | CAN Node 1 Receive Data Input                  |  |  |  |

|       | ESR2_8                                                 | I      | St/B | ESR2 Trigger Input 8                           |  |  |  |

| 92    | P2.13                                                  | O0 / I | St/B | Bit 13 of Port 2, General Purpose Input/Output |  |  |  |

|       | U2C1_SELO<br>2                                         | O1     | St/B | USIC2 Channel 1 Select/Control 2 Output        |  |  |  |

|       | RxDC2D                                                 | I      | St/B | CAN Node 2 Receive Data Input                  |  |  |  |

| 93    | P3.2                                                   | O0 / I | St/B | Bit 2 of Port 3, General Purpose Input/Output  |  |  |  |

|       | U2C0_SCLK<br>OUT                                       | O1     | St/B | USIC2 Channel 0 Shift Clock Output             |  |  |  |

|       | TxDC3                                                  | O2     | St/B | CAN Node 3 Transmit Data Output                |  |  |  |

|       | U2C0_DX1B                                              | Ι      | St/B | USIC2 Channel 0 Shift Clock Input              |  |  |  |

|       | HOLD                                                   | IH     | St/B | External Bus Master Hold Request Input         |  |  |  |

| 94    | P2.10                                                  | O0 / I | St/B | Bit 10 of Port 2, General Purpose Input/Output |  |  |  |

|       | U0C1_DOUT                                              | 01     | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |

|       | U0C0_SELO<br>3                                         | O2     | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |  |  |

|       | CC2_CC23                                               | O3 / I | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |  |  |  |

|       | A23                                                    | ОН     | St/B | External Bus Interface Address Line 23         |  |  |  |

|       | U0C1_DX0E                                              | I      | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |

|       | CAPINA                                                 | I      | St/B | GPT12E Register CAPREL Capture Input           |  |  |  |

|       | U3C1_DX0A                                              | Ι      | St/B | USIC3 Channel 1 Shift Data Input               |  |  |  |

| Table | able 5 Fin Definitions and Functions (cont d) |            |      |                                                   |  |  |  |

|-------|-----------------------------------------------|------------|------|---------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                          |  |  |  |

| 113   | P10.8                                         | O0 / I     | St/B | Bit 8 of Port 10, General Purpose Input/Output    |  |  |  |

|       | U0C0_MCLK<br>OUT                              | O1         | St/B | USIC0 Channel 0 Master Clock Output               |  |  |  |

|       | U0C1_SELO<br>0                                | O2         | St/B | USIC0 Channel 1 Select/Control 0 Output           |  |  |  |

|       | U2C1_DOUT                                     | O3         | St/B | USIC2 Channel 1 Shift Data Output                 |  |  |  |

|       | AD8                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 8        |  |  |  |

|       | CCU60_CCP<br>OS1A                             | I          | St/B | CCU60 Position Input 1                            |  |  |  |

|       | U0C0_DX1C                                     | I          | St/B | USIC0 Channel 0 Shift Clock Input                 |  |  |  |

|       | BRKIN_B                                       | I          | St/B | OCDS Break Signal Input                           |  |  |  |

|       | T3EUDB                                        | I          | St/B | GPT12E Timer T3 External Up/Down Control<br>Input |  |  |  |

| 114   | P9.1                                          | O0 / I     | St/B | Bit 1 of Port 9, General Purpose Input/Output     |  |  |  |

|       | CCU63_CC6<br>1                                | O1         | St/B | CCU63 Channel 1 Output                            |  |  |  |

|       | CCU63_CC6<br>1INA                             | I          | St/B | CCU63 Channel 1 Input                             |  |  |  |

#### **Functional Description**

### 3.6 Interrupt System

The architecture of the XE167xM supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Where in a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XE167xM has eight PEC channels, each whith fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XE167xM can react quickly to the occurrence of non-deterministic events.

#### Interrupt Nodes and Source Selection

The interrupt system provides 96 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

### External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

### Trap Processing

The XE167xM provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

#### **Functional Description**

### 3.18 Parallel Ports

The XE167xM provides up to 119 I/O lines which are organized into 11 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in Table 9.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

| Port | Width | I/O | Connected Modules                                                               |  |  |  |

|------|-------|-----|---------------------------------------------------------------------------------|--|--|--|

| P0   | 8     | I/O | EBC (A7A0),<br>CCU6, USIC, CAN                                                  |  |  |  |

| P1   | 8     | I/O | EBC (A15A8),<br>CCU6, USIC                                                      |  |  |  |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13),<br>CAN, CC2, GPT12E, USIC, DAP/JTAG |  |  |  |

| P3   | 8     | I/O | CAN, USIC                                                                       |  |  |  |

| P4   | 8     | I/O | EBC (CS3CS0),<br>CC2, CAN, GPT12E, USIC                                         |  |  |  |

| P5   | 16    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                      |  |  |  |

| P6   | 4     | I/O | ADC, CAN, GPT12E                                                                |  |  |  |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                     |  |  |  |

| P8   | 7     | I/O | CCU6, DAP/JTAG, USIC                                                            |  |  |  |

| P9   | 8     | I/O | CCU6, DAP/JTAG, CAN                                                             |  |  |  |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0),<br>CCU6, USIC, DAP/JTAG, CAN                 |  |  |  |

| P11  | 6     | I/O | CCU6, USIC, CAN                                                                 |  |  |  |

| P15  | 8     | Ι   | Analog Inputs, GPT12E                                                           |  |  |  |

#### Table 9Summary of the XE167xM's Ports

# 4 Electrical Parameters

The operating range for the XE167xM is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

### 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

### 4.1.1 Absolut Maximum Rating Conditions

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability.

During absolute maximum rating overload conditions ( $V_{\rm IN} > V_{\rm DDP}$  or  $V_{\rm IN} < V_{\rm SS}$ ) the voltage on  $V_{\rm DDP}$  pins with respect to ground ( $V_{\rm SS}$ ) must not exceed the values defined by the absolute maximum ratings.

| Parameter                                                       | Symbol                                      | Values    |   |                           | Unit | Note /                             |

|-----------------------------------------------------------------|---------------------------------------------|-----------|---|---------------------------|------|------------------------------------|

|                                                                 |                                             | Min. Typ. |   | Max.                      | 1    | Test Condition                     |

| Output current on a pin when high value is driven               | I <sub>OH</sub> SR                          | -30       | - | -                         | mA   |                                    |

| Output current on a pin when low value is driven                | I <sub>OL</sub> SR                          | -         | - | 30                        | mA   |                                    |

| Overload current                                                | $I_{\rm OV}{\rm SR}$                        | -10       | - | 10                        | mA   | 1)                                 |

| Absolute sum of overload currents                               | $\Sigma  I_{\rm OV} $<br>SR                 | -         | - | 100                       | mA   | 1)                                 |

| Junction Temperature                                            | $T_{\sf J}{\sf SR}$                         | -40       | - | 150                       | °C   |                                    |

| Storage Temperature                                             | $T_{\rm ST}{ m SR}$                         | -65       | - | 150                       | °C   |                                    |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDPA}, \\ V_{\rm DDPB} \\ {\rm SR}$ | -0.5      | - | 6.0                       | V    |                                    |

| Voltage on any pin with respect to ground (Vss)                 | $V_{\rm IN}$ SR                             | -0.5      | - | V <sub>DDP</sub><br>+ 0.5 | V    | $V_{\rm IN} \leq V_{\rm DDP(max)}$ |

### Table 11 Absolute Maximum Rating Parameters

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

### 4.2.3 Power Consumption

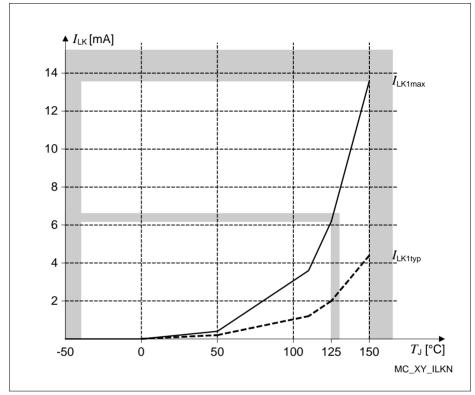

The power consumed by the XE167xM depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current I<sub>LK</sub> depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  and  $V_{\rm DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

| Parameter                                                                    | Symbol                  | Values |                           |                                                 | Unit | Note /         |

|------------------------------------------------------------------------------|-------------------------|--------|---------------------------|-------------------------------------------------|------|----------------|

|                                                                              |                         | Min.   | Тур.                      | Max.                                            |      | Test Condition |

| Power supply current<br>(active) with all peripherals<br>active and EVVRs on | I <sub>SACT</sub><br>CC | _      | $10 + 0.6 x f_{SYS}^{1)}$ | 10 +<br>1.0 x<br>f <sub>SYS</sub> <sup>1)</sup> | mA   | 2)3)           |

| Power supply current in stopover mode, EVVRs on                              | I <sub>SSO</sub> CC     | -      | 0.7                       | 2.0                                             | mA   |                |

### Table 15 Switching Power Consumption

1)  $f_{\rm SYS}$  in MHz.

#### **Electrical Parameters**

Figure 15 Leakage Supply Current as a Function of Temperature

### 4.6.4 Pad Properties

The output pad drivers of the XE167xM can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . The following table lists the pad parameters.

- Note: These parameters are not subject to production test but verified by design and/or characterization.

- Note: Operating Conditions apply.

Table 25

is valid under the following conditions:

$V_{\text{DDP}} \ge 4.5 \text{ V}; V_{\text{DDPtyp}} = 5 \text{ V}; V_{\text{DDP}} \le 5.5 \text{ V}; C_{\text{L}} \ge 20 \text{ pF}; C_{\text{L}} \le 100 \text{ pF};$

#### Table 25 Standard Pad Parameters for Upper Voltage Range

| Parameter                                                       | Symbol                  | Values |      |                                           | Unit | Note /                        |

|-----------------------------------------------------------------|-------------------------|--------|------|-------------------------------------------|------|-------------------------------|

|                                                                 |                         | Min.   | Тур. | Max.                                      |      | Test Condition                |

| Maximum output driver<br>current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -      | -    | 10                                        | mA   | Strong driver                 |

|                                                                 |                         | _      | -    | 4.0                                       | mA   | Medium driver                 |

|                                                                 |                         | -      | -    | 0.5                                       | mA   | Weak driver                   |

| Nominal output driver current (absolute value)                  | I <sub>Onom</sub><br>CC | -      | -    | 2.5                                       | mA   | Strong driver                 |

|                                                                 |                         | _      | -    | 1.0                                       | mA   | Medium driver                 |

|                                                                 |                         | _      | -    | 0.1                                       | mA   | Weak driver                   |

| Rise and Fall times (10% -<br>90%)                              | t <sub>RF</sub> CC      | -      | -    | 4.2 +<br>0.14 x<br><i>C</i> <sub>L</sub>  | ns   | Strong driver;<br>Sharp edge  |

|                                                                 |                         | -      | -    | 11.6 +<br>0.22 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Medium edge |

|                                                                 |                         | -      | -    | 20.6 +<br>0.22 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Slow edge   |

|                                                                 |                         | -      | -    | 23 +<br>0.6 x<br><i>C</i> L               | ns   | Medium driver                 |

|                                                                 |                         | -      | -    | 212 +<br>1.9 x<br><i>C</i> L              | ns   | Weak driver                   |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

### 4.6.5 External Bus Timing

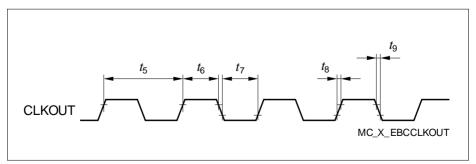

The following parameters specify the behavior of the XE167xM bus interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

#### **Bus Interface Performance Limits**

The output frequency at the bus interface pins is limited by the performance of the output drivers. The fast clock driver (used for CLKOUT) can drive 80-MHz signals, the standard drivers can drive 40-MHz signals

Therefore, the speed of the EBC must be limited, either by limiting the system frequency to  $f_{SYS} \le 80$  MHz or by adding waitstates so that signal transitions have a minimum distance of 12.5 ns.

For a description of the bus protocol and the programming of its variable timing parameters, please refer to the User's Manual.

| Parameter                       | Symbol            | Values |                 |      | Unit | Note /         |

|---------------------------------|-------------------|--------|-----------------|------|------|----------------|

|                                 |                   | Min.   | Тур.            | Max. |      | Test Condition |

| CLKOUT Cycle Time <sup>1)</sup> | t <sub>5</sub> CC | -      | $1/f_{\rm SYS}$ | -    | ns   |                |

| CLKOUT high time                | t <sub>6</sub> CC | 2      | -               | -    |      |                |

| CLKOUT low time                 | t <sub>7</sub> CC | 2      | _               | _    |      |                |

| CLKOUT rise time                | t <sub>8</sub> CC | -      | -               | 3    | ns   |                |

| CLKOUT fall time                | t <sub>9</sub> CC | -      | -               | 3    |      |                |

#### Table 27 EBC Parameters

1) The CLKOUT cycle time is influenced by PLL jitter. For longer periods the relative deviation decreases (see PLL deviation formula).

#### Debug via JTAG

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_L$ = 20 pF.

| Parameter                                                                | Symbol                    | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|------------------|------|------|------|----------------|

|                                                                          |                           | Min.             | Тур. | Max. |      | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 50 <sup>1)</sup> | _    | -    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR         | 16               | -    | -    | ns   |                |

| TCK low time                                                             | t <sub>3</sub> SR         | 16               | -    | -    | ns   |                |

| TCK clock rise time                                                      | $t_4$ SR                  | -                | -    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | -                | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                | -    | -    | ns   |                |

#### Table 39JTAG Interface Timing for Upper Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.

| Parameter                                                                | Symbol                    | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|------------------|------|------|------|----------------|

|                                                                          |                           | Min.             | Тур. | Max. | 1    | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 50 <sup>1)</sup> | _    | _    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR         | 16               | _    | _    | ns   |                |

| TCK low time                                                             | t <sub>3</sub> SR         | 16               | -    | -    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR         | -                | _    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | -                | 32   | 36   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | -                | 32   | 36   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | -                | 32   | 36   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                | -    | -    | ns   |                |

### Table 40 JTAG Interface Timing for Lower Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.