Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 119                                                                              |

| Program Memory Size        | 576KB (576K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 50K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xe167gm-72f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

### 16-Bit Single-Chip Real Time Signal Controller

XE167xM (XE166 Family)

# 1 Summary of Features

For a quick overview and easy reference, the features of the XE167xM are summarized here.

- High-performance CPU with five-stage pipeline and MPU

- 12.5 ns instruction cycle at 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1024 Bytes on-chip special function register area (C166 Family compatible)

- Integrated Memory Protection Unit (MPU)

- · Interrupt system with 16 priority levels for up to 96 sources

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- Up to 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 32 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 576 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

- On-Chip Peripheral Modules

- Multi-functional general purpose timer unit with 5 timers

- 16-channel general purpose capture/compare unit (CAPCOM2)

- Up to 4 capture/compare units for flexible PWM signal generation (CCU6x)

#### Summary of Features

#### **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the function set of the corresponding product type

- the temperature range:

- SAF-...: -40°C to 85°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XE167xM please contact your sales representative or local distributor.

This document describes several derivatives of the XE167xM group:

Table 1 lists these derivatives and summarizes the differences.

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term **XE167xM** is used for all derivatives throughout this document.

#### Summary of Features

### 1.2 Definition of Feature Variants

The XE167xM types are offered with several Flash memory sizes. **Table 2** describes the location of the available memory areas for each Flash memory size.

| Table 2 | Flash Memor | y Allocation |

|---------|-------------|--------------|

|---------|-------------|--------------|

| Total Flash Size | Flash Area A <sup>1)</sup> | Flash Area B         | Flash Area C         |

|------------------|----------------------------|----------------------|----------------------|

| 576 Kbytes       | C0'0000 <sub>H</sub>       | C1'0000 <sub>H</sub> | CC'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>       | C7'FFFF <sub>H</sub> | CC'FFFF <sub>H</sub> |

| 384 Kbytes       | C0'0000 <sub>H</sub>       | C1'0000 <sub>H</sub> | CC'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>       | C4'FFFF <sub>H</sub> | CC'FFFF <sub>H</sub> |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

#### Table 3 Flash Memory Module Allocation (in Kbytes)

| Total Flash Size | Flash 0 <sup>1)</sup> | Flash 1 | Flash 2 | Flash 3 |

|------------------|-----------------------|---------|---------|---------|

| 576 Kbytes       | 256                   | 256     |         | 64      |

| 384 Kbytes       | 256                   | 64      |         | 64      |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

The XE167xM types are offered with different interface options. Table 4 lists the available channels for each option.

| Total Number      | Available Channels                                        |  |  |  |  |

|-------------------|-----------------------------------------------------------|--|--|--|--|

| 16 ADC0 channels  | CH0 CH15                                                  |  |  |  |  |

| 8 ADC0 channels   | CH0 CH7                                                   |  |  |  |  |

| 8 ADC1 channels   | CH0 CH7 (overlay: CH8 CH11)                               |  |  |  |  |

| 6 CAN nodes       | CAN0, CAN1, CAN2, CAN3, CAN4, CAN5<br>128 message objects |  |  |  |  |

| 2 CAN nodes       | CAN0, CAN1<br>128 message objects                         |  |  |  |  |

| 8 serial channels | U0C0, U0C1, U1C0, U1C1, U2C0, U2C1, U3C0, U3C1            |  |  |  |  |

| 4 serial channels | ial channels U0C0, U0C1, U1C0, U1C1                       |  |  |  |  |

#### Table 4 Interface Channel Association

| Table | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                                   |  |

|-------|--------------------------------------------------------|--------|------|---------------------------------------------------|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                          |  |

| 69    | P2.6                                                   | O0 / I | St/B | Bit 6 of Port 2, General Purpose Input/Output     |  |

|       | U0C0_SELO<br>0                                         | O1     | St/B | USIC0 Channel 0 Select/Control 0 Output           |  |

|       | U0C1_SELO<br>1                                         | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output           |  |

|       | CC2_CC19                                               | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.         |  |

|       | A19                                                    | ОН     | St/B | External Bus Interface Address Line 19            |  |

|       | U0C0_DX2D                                              | I      | St/B | USIC0 Channel 0 Shift Control Input               |  |

|       | RxDC0D                                                 | I      | St/B | CAN Node 0 Receive Data Input                     |  |

|       | ESR2_6                                                 | I      | St/B | ESR2 Trigger Input 6                              |  |

| 70    | P4.4                                                   | O0 / I | St/B | Bit 4 of Port 4, General Purpose Input/Output     |  |

|       | U3C0_SELO<br>2                                         | O1     | St/B | USIC3 Channel 0 Select/Control 2 Output           |  |

|       | CC2_CC28                                               | O3 / I | St/B | CAPCOM2 CC28IO Capture Inp./ Compare Out.         |  |

|       | CS4                                                    | ОН     | St/B | External Bus Interface Chip Select 4 Output       |  |

|       | CLKIN2                                                 | I      | St/B | Clock Signal Input 2                              |  |

|       | U3C0_DX2C                                              | I      | St/B | USIC3 Channel 0 Shift Control Input               |  |

| 71    | P4.3                                                   | O0 / I | St/B | Bit 3 of Port 4, General Purpose Input/Output     |  |

|       | U0C1_DOUT                                              | 01     | St/B | USIC0 Channel 1 Shift Data Output                 |  |

|       | CC2_CC27                                               | O3 / I | St/B | CAPCOM2 CC27IO Capture Inp./ Compare Out.         |  |

|       | CS3                                                    | ОН     | St/B | External Bus Interface Chip Select 3 Output       |  |

|       | RxDC2A                                                 | I      | St/B | CAN Node 2 Receive Data Input                     |  |

|       | T2EUDA                                                 | I      | St/B | GPT12E Timer T2 External Up/Down Control<br>Input |  |

|       | CCU62_CCP<br>OS2B                                      | I      | St/B | CCU62 Position Input 2                            |  |

### XE167FM, XE167GM, XE167HM, XE167KM XE166 Family / Base Line

### **General Device Information**

| Tabl | Table 5         Pin Definitions and Functions (cont'd) |            |      |                                                |  |

|------|--------------------------------------------------------|------------|------|------------------------------------------------|--|

| Pin  | Symbol                                                 | Ctrl.      | Туре | Function                                       |  |

| 84   | P10.0                                                  | O0 / I     | St/B | Bit 0 of Port 10, General Purpose Input/Output |  |

|      | U0C1_DOUT                                              | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |

|      | CCU60_CC6<br>0                                         | O2         | St/B | CCU60 Channel 0 Output                         |  |

|      | AD0                                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 0     |  |

|      | CCU60_CC6<br>0INA                                      | I          | St/B | CCU60 Channel 0 Input                          |  |

|      | ESR1_2                                                 | I          | St/B | ESR1 Trigger Input 2                           |  |

|      | U0C0_DX0A                                              | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |

|      | U0C1_DX0A                                              | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |

| 85   | P3.0                                                   | O0 / I     | St/B | Bit 0 of Port 3, General Purpose Input/Output  |  |

| -    | U2C0_DOUT                                              | 01         | St/B | USIC2 Channel 0 Shift Data Output              |  |

|      | BREQ                                                   | OH         | St/B | External Bus Request Output                    |  |

|      | ESR1_1                                                 | I          | St/B | ESR1 Trigger Input 1                           |  |

|      | U2C0_DX0A                                              | I          | St/B | USIC2 Channel 0 Shift Data Input               |  |

|      | RxDC3B                                                 | I          | St/B | CAN Node 3 Receive Data Input                  |  |

|      | U2C0_DX1A                                              | I          | St/B | USIC2 Channel 0 Shift Clock Input              |  |

| 86   | P10.1                                                  | O0 / I     | St/B | Bit 1 of Port 10, General Purpose Input/Output |  |

|      | U0C0_DOUT                                              | 01         | St/B | USIC0 Channel 0 Shift Data Output              |  |

|      | CCU60_CC6<br>1                                         | O2         | St/B | CCU60 Channel 1 Output                         |  |

|      | AD1                                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 1     |  |

|      | CCU60_CC6<br>1INA                                      | I          | St/B | CCU60 Channel 1 Input                          |  |

|      | U0C0_DX1A                                              | I          | St/B | USIC0 Channel 0 Shift Clock Input              |  |

|      | U0C0_DX0B                                              | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |

| Table 5         Pin Definitions and Functions (cont'd) |                   |        |      |                                                |  |

|--------------------------------------------------------|-------------------|--------|------|------------------------------------------------|--|

| Pin                                                    | Symbol            | Ctrl.  | Туре | Function                                       |  |

| 107                                                    | P3.7              | O0 / I | St/B | Bit 7 of Port 3, General Purpose Input/Output  |  |

|                                                        | U2C1_DOUT         | 01     | St/B | USIC2 Channel 1 Shift Data Output              |  |

|                                                        | U2C0_SELO<br>3    | O2     | St/B | USIC2 Channel 0 Select/Control 3 Output        |  |

|                                                        | U0C0_SELO<br>7    | O3     | St/B | USIC0 Channel 0 Select/Control 7 Output        |  |

|                                                        | U2C1_DX0B         | I      | St/B | USIC2 Channel 1 Shift Data Input               |  |

| 111                                                    | P1.0              | O0 / I | St/B | Bit 0 of Port 1, General Purpose Input/Output  |  |

|                                                        | U1C0_MCLK<br>OUT  | 01     | St/B | USIC1 Channel 0 Master Clock Output            |  |

|                                                        | U1C0_SELO<br>4    | O2     | St/B | USIC1 Channel 0 Select/Control 4 Output        |  |

|                                                        | A8                | OH     | St/B | External Bus Interface Address Line 8          |  |

|                                                        | ESR1_3            | I      | St/B | ESR1 Trigger Input 3                           |  |

|                                                        | CCU62_CTR<br>APB  | I      | St/B | CCU62 Emergency Trap Input                     |  |

|                                                        | T6INB             | I      | St/B | GPT12E Timer T6 Count/Gate Input               |  |

| 112                                                    | P9.0              | O0 / I | St/B | Bit 0 of Port 9, General Purpose Input/Output  |  |

|                                                        | CCU63_CC6<br>0    | 01     | St/B | CCU63 Channel 0 Output                         |  |

|                                                        | CCU63_CC6<br>0INA | I      | St/B | CCU63 Channel 0 Input                          |  |

|                                                        | T6EUDB            | I      | St/B | GPT12E Timer T6 External Up/Down Control Input |  |

| Table | able 5 Pin Definitions and Functions (cont'd) |            |      |                                                                                                                                                                    |  |  |

|-------|-----------------------------------------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                                                                                                                                           |  |  |

| 117   | P10.10                                        | O0 / I     | St/B | Bit 10 of Port 10, General Purpose Input/Output                                                                                                                    |  |  |

|       | U0C0_SELO<br>0                                | 01         | St/B | USIC0 Channel 0 Select/Control 0 Output                                                                                                                            |  |  |

|       | CCU60_COU<br>T63                              | O2         | St/B | CCU60 Channel 3 Output                                                                                                                                             |  |  |

|       | AD10                                          | OH /<br>IH | St/B | External Bus Interface Address/Data Line 10                                                                                                                        |  |  |

|       | U0C0_DX2C                                     | I          | St/B | USIC0 Channel 0 Shift Control Input                                                                                                                                |  |  |

|       | U0C1_DX1A                                     | I          | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                  |  |  |

|       | TDI_B                                         | IH         | St/B | JTAG Test Data Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.           |  |  |

| 118   | P10.11                                        | O0 / I     | St/B | Bit 11 of Port 10, General Purpose Input/Output                                                                                                                    |  |  |

| -     | U1C0_SCLK<br>OUT                              | 01         | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                 |  |  |

|       | BRKOUT                                        | O2         | St/B | OCDS Break Signal Output                                                                                                                                           |  |  |

|       | U3C0_SELO<br>0                                | O3         | St/B | USIC3 Channel 0 Select/Control 0 Output                                                                                                                            |  |  |

|       | AD11                                          | OH /<br>IH | St/B | External Bus Interface Address/Data Line 11                                                                                                                        |  |  |

|       | U1C0_DX1D                                     | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                  |  |  |

|       | RxDC2B                                        | I          | St/B | CAN Node 2 Receive Data Input                                                                                                                                      |  |  |

|       | TMS_B                                         | IH         | St/B | JTAG Test Mode Selection Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it. |  |  |

|       | U3C0_DX2A                                     | I          | St/B | USIC3 Channel 0 Shift Control Input                                                                                                                                |  |  |

| 119   | P9.2                                          | O0 / I     | St/B | Bit 2 of Port 9, General Purpose Input/Output                                                                                                                      |  |  |

|       | CCU63_CC6<br>2                                | 01         | St/B | CCU63 Channel 2 Output                                                                                                                                             |  |  |

|       | CCU63_CC6<br>2INA                             | 1          | St/B | CCU63 Channel 2 Input                                                                                                                                              |  |  |

|       | CAPINB                                        | Ι          | St/B | GPT12E Register CAPREL Capture Input                                                                                                                               |  |  |

| Table | Table 5         Pin Definitions and Functions (cont'd) |            |      |                                                                                                                                                                               |  |  |

|-------|--------------------------------------------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                                                                                                                                                      |  |  |

| 120   | P1.2                                                   | O0 / I     | St/B | Bit 2 of Port 1, General Purpose Input/Output                                                                                                                                 |  |  |

|       | CCU62_CC6<br>2                                         | 01         | St/B | CCU62 Channel 2 Output                                                                                                                                                        |  |  |

|       | U1C0_SELO<br>6                                         | O2         | St/B | USIC1 Channel 0 Select/Control 6 Output                                                                                                                                       |  |  |

|       | U2C1_SCLK<br>OUT                                       | O3         | St/B | USIC2 Channel 1 Shift Clock Output                                                                                                                                            |  |  |

|       | A10                                                    | ОН         | St/B | External Bus Interface Address Line 10                                                                                                                                        |  |  |

|       | ESR1_4                                                 | I          | St/B | ESR1 Trigger Input 4                                                                                                                                                          |  |  |

|       | CCU61_T12<br>HRB                                       | I          | St/B | External Run Control Input for T12 of CCU61                                                                                                                                   |  |  |

| -     | CCU62_CC6<br>2INA                                      | I          | St/B | CCU62 Channel 2 Input                                                                                                                                                         |  |  |

|       | U2C1_DX0D                                              | I          | St/B | USIC2 Channel 1 Shift Data Input                                                                                                                                              |  |  |

|       | U2C1_DX1C                                              | I          | St/B | USIC2 Channel 1 Shift Clock Input                                                                                                                                             |  |  |

| 121   | P10.12                                                 | O0 / I     | St/B | Bit 12 of Port 10, General Purpose Input/Output                                                                                                                               |  |  |

|       | U1C0_DOUT                                              | O1         | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                             |  |  |

|       | TxDC2                                                  | O2         | St/B | CAN Node 2 Transmit Data Output                                                                                                                                               |  |  |

|       | TDO_B                                                  | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |

|       | AD12                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 12                                                                                                                                   |  |  |

|       | U1C0_DX0C                                              | I          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                              |  |  |

|       | U1C0_DX1E                                              | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                             |  |  |

| 122   | P9.3                                                   | O0 / I     | St/B | Bit 3 of Port 9, General Purpose Input/Output                                                                                                                                 |  |  |

|       | CCU63_COU<br>T60                                       | O1         | St/B | CCU63 Channel 0 Output                                                                                                                                                        |  |  |

|       | BRKOUT                                                 | O2         | St/B | OCDS Break Signal Output                                                                                                                                                      |  |  |

| Table | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                                 |  |  |

|-------|--------------------------------------------------------|--------|------|-------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                        |  |  |

| 126   | P9.5                                                   | O0 / I | St/B | Bit 5 of Port 9, General Purpose Input/Output   |  |  |

|       | CCU63_COU<br>T62                                       | O1     | St/B | CCU63 Channel 2 Output                          |  |  |

|       | U2C0_DOUT                                              | 02     | St/B | USIC2 Channel 0 Shift Data Output               |  |  |

|       | CCU62_COU<br>T62                                       | O3     | St/B | CCU62 Channel 2 Output                          |  |  |

|       | U2C0_DX0E                                              | I      | St/B | USIC2 Channel 0 Shift Data Input                |  |  |

|       | CCU60_CCP<br>OS2B                                      | 1      | St/B | CCU60 Position Input 2                          |  |  |

| 128   | P10.14                                                 | O0 / I | St/B | Bit 14 of Port 10, General Purpose Input/Output |  |  |

|       | U1C0_SELO<br>1                                         | O1     | St/B | USIC1 Channel 0 Select/Control 1 Output         |  |  |

|       | U0C1_DOUT                                              | 02     | St/B | USIC0 Channel 1 Shift Data Output               |  |  |

| -     | U3C0_SCLK<br>OUT                                       | O3     | St/B | USIC3 Channel 0 Shift Clock Output              |  |  |

|       | RD                                                     | ОН     | St/B | External Bus Interface Read Strobe Output       |  |  |

|       | ESR2_2                                                 | I      | St/B | ESR2 Trigger Input 2                            |  |  |

|       | U0C1_DX0C                                              | I      | St/B | USIC0 Channel 1 Shift Data Input                |  |  |

|       | RxDC3C                                                 | I      | St/B | CAN Node 3 Receive Data Input                   |  |  |

|       | U3C0_DX1A                                              | I      | St/B | USIC3 Channel 0 Shift Clock Input               |  |  |

| 129   | P1.4                                                   | O0 / I | St/B | Bit 4 of Port 1, General Purpose Input/Output   |  |  |

|       | CCU62_COU<br>T61                                       | O1     | St/B | CCU62 Channel 1 Output                          |  |  |

|       | U1C1_SELO<br>4                                         | O2     | St/B | USIC1 Channel 1 Select/Control 4 Output         |  |  |

|       | U2C0_SELO<br>5                                         | O3     | St/B | USIC2 Channel 0 Select/Control 5 Output         |  |  |

|       | A12                                                    | ОН     | St/B | External Bus Interface Address Line 12          |  |  |

|       | U2C0_DX2B                                              | I      | St/B | USIC2 Channel 0 Shift Control Input             |  |  |

|       | RxDC5A                                                 | I      | St/B | CAN Node 5 Receive Data Input                   |  |  |

### 3.1 Memory Subsystem and Organization

The memory space of the XE167xM is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

| Address Area                         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes               |

|--------------------------------------|----------------------|----------------------|-------------------------|---------------------|

| IMB register space                   | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 Bytes               | -                   |

| Reserved (Access trap)               | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | <1 Mbyte                | Minus IMB registers |

| Reserved for EPSRAM                  | E8'8000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 480 Kbytes              | Mirrors EPSRAM      |

| Emulated PSRAM                       | E8'0000 <sub>H</sub> | E8'7FFF <sub>H</sub> | 32 Kbytes               | With Flash timing   |

| Reserved for PSRAM                   | E0'8000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 480 Kbytes              | Mirrors PSRAM       |

| Program SRAM                         | E0'0000 <sub>H</sub> | E0'7FFF <sub>H</sub> | 32 Kbytes               | Maximum speed       |

| Reserved for Flash                   | CD'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | <1.25 Mbytes            | -                   |

| Program Flash 3                      | CC'0000 <sub>H</sub> | CC'FFFF <sub>H</sub> | 64 Kbytes               | -                   |

| Program Flash 2                      | C8'0000 <sub>H</sub> | CB'FFFF <sub>H</sub> | 256 Kbytes              | -                   |

| Program Flash 1                      | C4'0000 <sub>H</sub> | C7'FFFF <sub>H</sub> | 256 Kbytes              | -                   |

| Program Flash 0                      | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes              | 3)                  |

| External memory area                 | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                | -                   |

| Available Ext. IO area <sup>4)</sup> | 21'0000 <sub>H</sub> | 3F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus USIC/CAN      |

| Reserved                             | 20'BC00 <sub>H</sub> | 20'FFFF <sub>H</sub> | 17 Kbytes               | -                   |

| USIC alternate regs.                 | 20'B000 <sub>H</sub> | 20'BFFF <sub>H</sub> | 4 Kbytes                | Accessed via EBC    |

| MultiCAN alternate regs.             | 20'8000 <sub>H</sub> | 20'AFFF <sub>H</sub> | 12 Kbytes               | Accessed via EBC    |

| Reserved                             | 20'6000 <sub>H</sub> | 20'7FFF <sub>H</sub> | 8 Kbytes                | -                   |

| USIC registers                       | 20'4000 <sub>H</sub> | 20'5FFF <sub>H</sub> | 8 Kbytes                | Accessed via EBC    |

| MultiCAN registers                   | 20'0000 <sub>H</sub> | 20'3FFF <sub>H</sub> | 16 Kbytes               | Accessed via EBC    |

| External memory area                 | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus segment 0     |

| SFR area                             | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbyte               | -                   |

| Dual-Port RAM                        | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                | -                   |

| Reserved for DPRAM                   | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbyte                 | -                   |

| ESFR area                            | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbyte               | -                   |

| XSFR area                            | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                | -                   |

### Table 7XE167xM Memory Map 1)

### 3.2 External Bus Controller

All external memory access operations are performed by a special on-chip External Bus Controller (EBC). The EBC also controls access to resources connected to the on-chip LXBus (MultiCAN and the USIC modules). The LXBus is an internal representation of the external bus that allows access to integrated peripherals and modules in the same way as to external components.

The EBC can be programmed either to Single Chip Mode, when no external memory is required, or to an external bus mode with the following selections<sup>1)</sup>:

- Address Bus Width with a range of 0 ... 24-bit

- Data Bus Width 8-bit or 16-bit

- Bus Operation Multiplexed or Demultiplexed

The bus interface uses Port 10 and Port 2 for addresses and data. In the demultiplexed bus modes, the lower addresses are output separately on Port 0 and Port 1. The number of active segment address lines is selectable, restricting the external address space to 8 Mbytes ... 64 Kbytes. This is required when interface lines shall be assigned to Port 2.

External CS signals (address windows plus default) can be generated and output on Port 4 in order to save external glue logic. External modules can be directly connected to the common address/data bus and their individual select lines.

A HOLD/HLDA protocol is available for bus arbitration; this allows the sharing of external resources with other bus masters. The bus arbitration is enabled by software, after which pins P3.0 ... P3.2 (BREQ, HLDA, HOLD) are automatically controlled by the EBC. In Master Mode (default after reset) the HLDA pin is an output. In Slave Mode pin HLDA is switched to be an input. This allows the direct connection of the slave controller to another master controller without glue logic.

Important timing characteristics of the external bus interface are programmable (with registers TCONCSx/FCONCSx) to allow the user to adapt it to a wide range of different types of memories and external peripherals.

Access to very slow memories or modules with varying access times is supported by a special 'Ready' function. The active level of the control input signal is selectable.

In addition, up to four independent address windows may be defined (using registers ADDRSELx) to control access to resources with different bus characteristics. These address windows are arranged hierarchically where window 4 overrides window 3, and window 2 overrides window 1. All accesses to locations not covered by these four address windows are controlled by TCONCS0/FCONCS0. The currently active window can generate a chip select signal.

The external bus timing is based on the rising edge of the reference clock output CLKOUT. The external bus protocol is compatible with that of the standard C166 Family.

<sup>1)</sup> Bus modes are switched dynamically if several address windows with different mode settings are used.

### 3.8 Capture/Compare Unit (CAPCOM2)

The CAPCOM2 unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM2 unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers (T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range or variation for the timer period and resolution and allows precise adjustments to the application-specific requirements. In addition, an external count input allows event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

| Compare Modes | Function                                                                                   |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Mode 0        | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |  |  |  |  |

| Mode 1        | Pin toggles on each compare match;<br>Several compare events per timer period are possible |  |  |  |  |

Table 8 Compare Modes

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The counting direction (up/down) for each timer can be programmed by software or altered dynamically with an external signal on a port pin (TxEUD). Concatenation of the timers is supported with the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can also be used to clock the CAPCOM2 timers and to initiate a reload from the CAPREL register.

The CAPREL register can capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN); timer T5 may optionally be cleared after the capture procedure. This allows the XE167xM to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) can also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

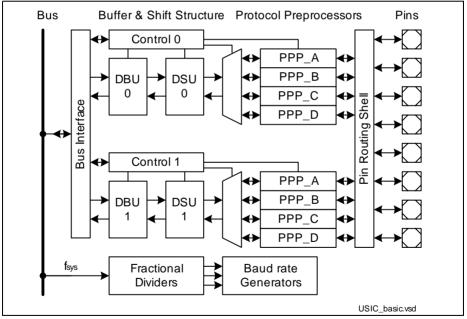

## 3.13 Universal Serial Interface Channel Modules (USIC)

The XE167xM features the USIC modules USIC0, USIC1, USIC2, USIC3. Each module provides two serial communication channels.

The Universal Serial Interface Channel (USIC) module is based on a generic data shift and data storage structure which is identical for all supported serial communication protocols. Each channel supports complete full-duplex operation with a basic data buffer structure (one transmit buffer and two receive buffer stages). In addition, the data handling software can use FIFOs.

The protocol part (generation of shift clock/data/control signals) is independent of the general part and is handled by protocol-specific preprocessors (PPPs).

The USIC's input/output lines are connected to pins by a pin routing unit. The inputs and outputs of each USIC channel can be assigned to different interface pins, providing great flexibility to the application software. All assignments can be made during runtime.

#### Figure 11 General Structure of a USIC Module

The regular structure of the USIC module brings the following advantages:

- Higher flexibility through configuration with same look-and-feel for data management

- Reduced complexity for low-level drivers serving different protocols

- Wide range of protocols with improved performances (baud rate, buffer handling)

### **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

### 3.16 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.42 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

### 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XE167xM from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

#### **Functional Description**

| Table To Instruction Set Summary (cont d) |                                     |       |  |  |

|-------------------------------------------|-------------------------------------|-------|--|--|

| Mnemonic                                  | Description                         | Bytes |  |  |

| NOP                                       | Null operation                      | 2     |  |  |

| CoMUL/CoMAC                               | Multiply (and accumulate)           | 4     |  |  |

| CoADD/CoSUB                               | Add/Subtract                        | 4     |  |  |

| Co(A)SHR                                  | (Arithmetic) Shift right            | 4     |  |  |

| CoSHL                                     | Shift left                          | 4     |  |  |

| CoLOAD/STORE                              | Load accumulator/Store MAC register | 4     |  |  |

| CoCMP                                     | Compare                             | 4     |  |  |

| CoMAX/MIN                                 | Maximum/Minimum                     | 4     |  |  |

| CoABS/CoRND                               | Absolute value/Round accumulator    | 4     |  |  |

| CoMOV                                     | Data move                           | 4     |  |  |

| CoNEG/NOP                                 | Negate accumulator/Null operation   | 4     |  |  |

#### Instruction Set Summary (cont'd) Table 10

1) The Enter Power Down Mode instruction is not used in the XE167xM, due to the enhanced power control scheme. PWRDN will be correctly decoded, but will trigger no action.

#### **Electrical Parameters**

| Table 20          | Coding of bit fields LEVXV | ing of bit fields LEVXV in Register SwDCONU (contra) |  |  |  |  |

|-------------------|----------------------------|------------------------------------------------------|--|--|--|--|

| Code              | Default Voltage Level      | Notes <sup>1)</sup>                                  |  |  |  |  |

| 1001 <sub>B</sub> | 4.5 V                      | LEV2V: no request                                    |  |  |  |  |

| 1010 <sub>B</sub> | 4.6 V                      |                                                      |  |  |  |  |

| 1011 <sub>B</sub> | 4.7 V                      |                                                      |  |  |  |  |

| 1100 <sub>B</sub> | 4.8 V                      |                                                      |  |  |  |  |

| 1101 <sub>B</sub> | 4.9 V                      |                                                      |  |  |  |  |

| 1110 <sub>B</sub> | 5.0 V                      |                                                      |  |  |  |  |

| 1111 <sub>B</sub> | 5.5 V                      |                                                      |  |  |  |  |

### Table 20 Coding of bit fields LEVxV in Register SWDCON0 (cont'd)

1) The indicated default levels are selected automatically after a power reset.

#### Table 21 Coding of Bitfields LEVxV in Registers PVCyCONz

| Code             | Default Voltage Level | Notes <sup>1)</sup>                    |  |  |  |  |

|------------------|-----------------------|----------------------------------------|--|--|--|--|

| 000 <sub>B</sub> | 0.95 V                |                                        |  |  |  |  |

| 001 <sub>B</sub> | 1.05 V                |                                        |  |  |  |  |

| 010 <sub>B</sub> | 1.15 V                |                                        |  |  |  |  |

| 011 <sub>B</sub> | 1.25 V                |                                        |  |  |  |  |

| 100 <sub>B</sub> | 1.35 V                | LEV1V: reset request                   |  |  |  |  |

| 101 <sub>B</sub> | 1.45 V                | LEV2V: interrupt request <sup>2)</sup> |  |  |  |  |

| 110 <sub>B</sub> | 1.55 V                |                                        |  |  |  |  |

| 111 <sub>B</sub> | 1.65 V                |                                        |  |  |  |  |

1) The indicated default levels are selected automatically after a power reset.

2) Due to variations of the tolerance of both the Embedded Voltage Regulators (EVR) and the PVC levels, this interrupt can be triggered inadvertently, even though the core voltage is within the normal range. It is, therefore, recommended not to use the this warning level.

#### **Electrical Parameters**

#### Table 36 USIC SSC Slave Mode Timing for Lower Voltage Range

| Parameter                                                                         | Symbol                    | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                                   |                           | Min.   | Тур. | Max. | 1    | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7      | -    | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | -    | -    | ns   |                |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup>    | <i>t</i> <sub>13</sub> SR | 5      | -    | _    | ns   |                |

| Data output DOUT valid time                                                       | <i>t</i> <sub>14</sub> CC | 8      | -    | 41   | ns   |                |

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

#### **Electrical Parameters**

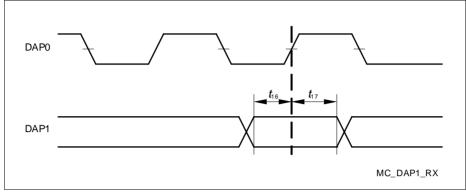

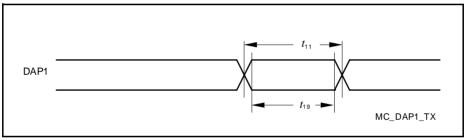

Figure 30 DAP Timing Host to Device

Figure 31 DAP Timing Device to Host

Note: The transmission timing is determined by the receiving debugger by evaluating the sync-request synchronization pattern telegram.