Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C1665V2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                     |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 119                                                                              |

| Program Memory Size        | 576KB (576K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 50K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xe167km-72f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

# 1.2 Definition of Feature Variants

The XE167xM types are offered with several Flash memory sizes. **Table 2** describes the location of the available memory areas for each Flash memory size.

| Table 2 | Flash Memor | y Allocation |

|---------|-------------|--------------|

|---------|-------------|--------------|

| Total Flash Size | Flash Area A <sup>1)</sup> | Flash Area B         | Flash Area C         |

|------------------|----------------------------|----------------------|----------------------|

| 576 Kbytes       | C0'0000 <sub>H</sub>       | C1'0000 <sub>H</sub> | CC'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>       | C7'FFFF <sub>H</sub> | CC'FFFF <sub>H</sub> |

| 384 Kbytes       | C0'0000 <sub>H</sub>       | C1'0000 <sub>H</sub> | CC'0000 <sub>H</sub> |

|                  | C0'EFFF <sub>H</sub>       | C4'FFFF <sub>H</sub> | CC'FFFF <sub>H</sub> |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

#### Table 3 Flash Memory Module Allocation (in Kbytes)

| Total Flash Size | Flash 0 <sup>1)</sup> | Flash 1 | Flash 2 | Flash 3 |

|------------------|-----------------------|---------|---------|---------|

| 576 Kbytes       | 256                   | 256     |         | 64      |

| 384 Kbytes       | 256                   | 64      |         | 64      |

1) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

The XE167xM types are offered with different interface options. Table 4 lists the available channels for each option.

| Total Number      | Available Channels                                        |

|-------------------|-----------------------------------------------------------|

| 16 ADC0 channels  | CH0 CH15                                                  |

| 8 ADC0 channels   | CH0 CH7                                                   |

| 8 ADC1 channels   | CH0 CH7 (overlay: CH8 CH11)                               |

| 6 CAN nodes       | CAN0, CAN1, CAN2, CAN3, CAN4, CAN5<br>128 message objects |

| 2 CAN nodes       | CAN0, CAN1<br>128 message objects                         |

| 8 serial channels | U0C0, U0C1, U1C0, U1C1, U2C0, U2C1, U3C0, U3C1            |

| 4 serial channels | U0C0, U0C1, U1C0, U1C1                                    |

### Table 4 Interface Channel Association

### **General Device Information**

# 2 General Device Information

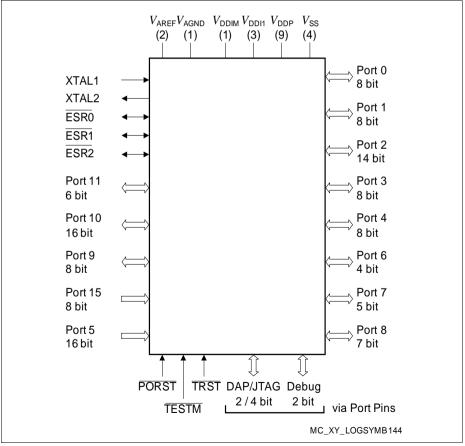

The XE167xM series (16-Bit Single-Chip Real Time Signal Controller) is a part of the Infineon XE166 Family of full-feature single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

Figure 2 XE167xM Logic Symbol

| Table | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |

|-------|--------------------------------------------------------|--------|------|------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                       |  |  |

| 45    | P5.10                                                  | I      | In/A | Bit 10 of Port 5, General Purpose Input        |  |  |

|       | ADC0_CH10                                              | I      | In/A | Analog Input Channel 10 for ADC0               |  |  |

|       | ADC1_CH10                                              | I      | In/A | Analog Input Channel 10 for ADC1               |  |  |

|       | BRKIN_A                                                | I      | In/A | OCDS Break Signal Input                        |  |  |

|       | U2C1_DX0F                                              | I      | In/A | USIC2 Channel 1 Shift Data Input               |  |  |

|       | CCU61_T13<br>HRA                                       | I      | In/A | External Run Control Input for T13 of CCU61    |  |  |

| 46    | P5.11                                                  | I      | In/A | Bit 11 of Port 5, General Purpose Input        |  |  |

|       | ADC0_CH11                                              | I      | In/A | Analog Input Channel 11 for ADC0               |  |  |

|       | ADC1_CH11                                              | I      | In/A | Analog Input Channel 11 for ADC1               |  |  |

| 47    | P5.12                                                  | I      | In/A | Bit 12 of Port 5, General Purpose Input        |  |  |

|       | ADC0_CH12                                              | I      | In/A | Analog Input Channel 12 for ADC0               |  |  |

| 48    | P5.13                                                  | I      | In/A | Bit 13 of Port 5, General Purpose Input        |  |  |

|       | ADC0_CH13                                              | I      | In/A | Analog Input Channel 13 for ADC0               |  |  |

|       | CCU63_T13<br>HRF                                       | I      | In/A | External Run Control Input for T13 of CCU63    |  |  |

| 49    | P5.14                                                  | I      | In/A | Bit 14 of Port 5, General Purpose Input        |  |  |

|       | ADC0_CH14                                              | I      | In/A | Analog Input Channel 14 for ADC0               |  |  |

| 50    | P5.15                                                  | I      | In/A | Bit 15 of Port 5, General Purpose Input        |  |  |

|       | ADC0_CH15                                              | I      | In/A | Analog Input Channel 15 for ADC0               |  |  |

|       | RxDC2F                                                 | I      | In/A | CAN Node 2 Receive Data Input                  |  |  |

| 51    | P2.12                                                  | O0 / I | St/B | Bit 12 of Port 2, General Purpose Input/Output |  |  |

|       | U0C0_SELO<br>4                                         | 01     | St/B | USIC0 Channel 0 Select/Control 4 Output        |  |  |

|       | U0C1_SELO<br>3                                         | O2     | St/B | USIC0 Channel 1 Select/Control 3 Output        |  |  |

|       | TXDC2                                                  | O3     | St/B | CAN Node 2 Transmit Data Output                |  |  |

|       | READY                                                  | IH     | St/B | External Bus Interface READY Input             |  |  |

| Table | e 5 Pin De        | finitior | ns and | Functions (cont'd)                                |

|-------|-------------------|----------|--------|---------------------------------------------------|

| Pin   | Symbol            | Ctrl.    | Туре   | Function                                          |

| 63    | P4.1              | O0 / I   | St/B   | Bit 1 of Port 4, General Purpose Input/Output     |

|       | U3C0_SELO<br>3    | O1       | St/B   | USIC3 Channel Select/Control 3 Output             |

|       | TxDC2             | 02       | St/B   | CAN Node 2 Transmit Data Output                   |

|       | CC2_CC25          | O3 / I   | St/B   | CAPCOM2 CC25IO Capture Inp./ Compare Out.         |

|       | CS1               | OH       | St/B   | External Bus Interface Chip Select 1 Output       |

|       | CCU62_CCP<br>OS0B | I        | St/B   | CCU62 Position Input 0                            |

|       | T4EUDB            | I        | St/B   | GPT12E Timer T4 External Up/Down Control<br>Input |

|       | ESR1_8            | I        | St/B   | ESR1 Trigger Input 8                              |

| 64    | P2.4              | O0 / I   | St/B   | Bit 4 of Port 2, General Purpose Input/Output     |

|       | U0C1_DOUT         | 01       | St/B   | USIC0 Channel 1 Shift Data Output                 |

| _     | TxDC0             | 02       | St/B   | CAN Node 0 Transmit Data Output                   |

|       | CC2_CC17          | O3 / I   | St/B   | CAPCOM2 CC17IO Capture Inp./ Compare Out.         |

|       | A17               | OH       | St/B   | External Bus Interface Address Line 17            |

|       | ESR1_0            | I        | St/B   | ESR1 Trigger Input 0                              |

|       | U0C0_DX0F         | I        | St/B   | USIC0 Channel 0 Shift Data Input                  |

|       | RxDC1A            | I        | St/B   | CAN Node 1 Receive Data Input                     |

| 65    | P11.1             | O0 / I   | St/B   | Bit 1 of Port 11, General Purpose Input/Output    |

|       | CCU61_COU<br>T61  | O1       | St/B   | CCU61 Channel 1 Output                            |

|       | TxDC0             | 02       | St/B   | CAN Node 0 Transmit Data Output                   |

|       | U3C1_SELO<br>0    | O3       | St/B   | USIC3 Channel 1 Select/Control 0 Output           |

|       | CCU63_CCP<br>OS1A | I        | St/B   | CCU63 Position Input 1                            |

|       | CCU61_CTR<br>APD  | I        | St/B   | CCU61 Emergency Trap Input                        |

|       | U3C1_DX2A         | I        | St/B   | USIC3 Channel 1 Shift Control Input               |

| Table | Table 5         Pin Definitions and Functions (cont'd) |            |      |                                                                                           |  |  |  |

|-------|--------------------------------------------------------|------------|------|-------------------------------------------------------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                                                                  |  |  |  |

| 87    | P0.3                                                   | O0 / I     | St/B | Bit 3 of Port 0, General Purpose Input/Output                                             |  |  |  |

|       | U1C0_SELO<br>0                                         | 01         | St/B | USIC1 Channel 0 Select/Control 0 Output                                                   |  |  |  |

|       | U1C1_SELO<br>1                                         | O2         | St/B | USIC1 Channel 1 Select/Control 1 Output                                                   |  |  |  |

|       | CCU61_COU<br>T60                                       | O3         | St/B | CCU61 Channel 0 Output                                                                    |  |  |  |

|       | A3                                                     | ОН         | St/B | External Bus Interface Address Line 3                                                     |  |  |  |

|       | U1C0_DX2A                                              | I          | St/B | USIC1 Channel 0 Shift Control Input                                                       |  |  |  |

|       | RxDC0B                                                 | I          | St/B | CAN Node 0 Receive Data Input                                                             |  |  |  |

| 88    | P3.1                                                   | O0 / I     | St/B | Bit 1 of Port 3, General Purpose Input/Output                                             |  |  |  |

|       | U2C0_DOUT                                              | O1         | St/B | USIC2 Channel 0 Shift Data Output                                                         |  |  |  |

| _     | TxDC3                                                  | O2         | St/B | CAN Node 3 Transmit Data Output                                                           |  |  |  |

|       | HLDA                                                   | OH /<br>IH | St/B | External Bus Hold Acknowledge Output/Input<br>Output in master mode, input in slave mode. |  |  |  |

|       | U2C0_DX0B                                              | I          | St/B | USIC2 Channel 0 Shift Data Input                                                          |  |  |  |

| 89    | P10.2                                                  | O0 / I     | St/B | Bit 2 of Port 10, General Purpose Input/Output                                            |  |  |  |

|       | U0C0_SCLK<br>OUT                                       | 01         | St/B | USIC0 Channel 0 Shift Clock Output                                                        |  |  |  |

|       | CCU60_CC6<br>2                                         | O2         | St/B | CCU60 Channel 2 Output                                                                    |  |  |  |

|       | U3C0_SELO<br>1                                         | O3         | St/B | USIC3 Channel 0 Select/Control 1 Output                                                   |  |  |  |

|       | AD2                                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 2                                                |  |  |  |

|       | CCU60_CC6<br>2INA                                      | 1          | St/B | CCU60 Channel 2 Input                                                                     |  |  |  |

|       | U0C0_DX1B                                              | I          | St/B | USIC0 Channel 0 Shift Clock Input                                                         |  |  |  |

|       | U3C0_DX2B                                              | I          | St/B | USIC3 Channel 0 Shift Control Input                                                       |  |  |  |

| Table | Table 5         Pin Definitions and Functions (cont'd) |            |      |                                                                                                                                                                               |  |  |

|-------|--------------------------------------------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                                                                                                                                                      |  |  |

| 120   | P1.2                                                   | O0 / I     | St/B | Bit 2 of Port 1, General Purpose Input/Output                                                                                                                                 |  |  |

|       | CCU62_CC6<br>2                                         | 01         | St/B | CCU62 Channel 2 Output                                                                                                                                                        |  |  |

|       | U1C0_SELO<br>6                                         | O2         | St/B | USIC1 Channel 0 Select/Control 6 Output                                                                                                                                       |  |  |

|       | U2C1_SCLK<br>OUT                                       | O3         | St/B | USIC2 Channel 1 Shift Clock Output                                                                                                                                            |  |  |

|       | A10                                                    | ОН         | St/B | External Bus Interface Address Line 10                                                                                                                                        |  |  |

|       | ESR1_4                                                 | I          | St/B | ESR1 Trigger Input 4                                                                                                                                                          |  |  |

|       | CCU61_T12<br>HRB                                       | I          | St/B | External Run Control Input for T12 of CCU61                                                                                                                                   |  |  |

|       | CCU62_CC6<br>2INA                                      | I          | St/B | CCU62 Channel 2 Input                                                                                                                                                         |  |  |

|       | U2C1_DX0D                                              | I          | St/B | USIC2 Channel 1 Shift Data Input                                                                                                                                              |  |  |

|       | U2C1_DX1C                                              | I          | St/B | USIC2 Channel 1 Shift Clock Input                                                                                                                                             |  |  |

| 121   | P10.12                                                 | O0 / I     | St/B | Bit 12 of Port 10, General Purpose Input/Output                                                                                                                               |  |  |

|       | U1C0_DOUT                                              | O1         | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                                             |  |  |

|       | TxDC2                                                  | O2         | St/B | CAN Node 2 Transmit Data Output                                                                                                                                               |  |  |

|       | TDO_B                                                  | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 1 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |

|       | AD12                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 12                                                                                                                                   |  |  |

|       | U1C0_DX0C                                              | I          | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                              |  |  |

|       | U1C0_DX1E                                              | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                             |  |  |

| 122   | P9.3                                                   | O0 / I     | St/B | Bit 3 of Port 9, General Purpose Input/Output                                                                                                                                 |  |  |

|       | CCU63_COU<br>T60                                       | O1         | St/B | CCU63 Channel 0 Output                                                                                                                                                        |  |  |

|       | BRKOUT                                                 | O2         | St/B | OCDS Break Signal Output                                                                                                                                                      |  |  |

| Address Area         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes |  |  |  |  |

|----------------------|----------------------|----------------------|-------------------------|-------|--|--|--|--|

| Data SRAM            | 00'A000 <sub>H</sub> | 00'DFFF <sub>H</sub> | 16 Kbytes               | -     |  |  |  |  |

| Reserved for DSRAM   | 00'8000 <sub>H</sub> | 00'9FFF <sub>H</sub> | 8 Kbytes                | -     |  |  |  |  |

| External memory area | 00'000 <sub>H</sub>  | 00'7FFF <sub>H</sub> | 32 Kbytes               | -     |  |  |  |  |

### Table 7XE167xM Memory Map (cont'd)<sup>1)</sup>

Accesses to the shaded areas are reserved. In devices with external bus interface these accesses generate external bus accesses.

2) The areas marked with "<" are slightly smaller than indicated. See column "Notes".

3) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

4) Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

Up to 32 Kbytes of on-chip Program SRAM (PSRAM) are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Up to 16 Kbytes of on-chip Data SRAM (DSRAM) are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

With this hardware most XE167xM instructions are executed in a single machine cycle of 12.5 ns with an 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 wordwide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XE167xM instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

# 3.10 General Purpose Timer (GPT12E) Unit

The GPT12E unit is a very flexible multifunctional timer/counter structure which can be used for many different timing tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT12E unit incorporates five 16-bit timers organized in two separate modules, GPT1 and GPT2. Each timer in each module may either operate independently in a number of different modes or be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation: Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the system clock and divided by a programmable prescaler. Counter Mode allows timer clocking in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes each timer has one associated port pin (TxIN) which serves as a gate or clock input. The maximum resolution of the timers in module GPT1 is 4 system clock cycles.

The counting direction (up/down) for each timer can be programmed by software or altered dynamically by an external signal on a port pin (TxEUD), e.g. to facilitate position tracking.

In Incremental Interface Mode the GPT1 timers can be directly connected to the incremental position sensor signals A and B through their respective inputs TxIN and TxEUD. Direction and counting signals are internally derived from these two input signals, so that the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components. It may also be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to the basic operating modes, T2 and T4 may be configured as reload or capture register for timer T3. A timer used as capture or reload register is stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at the associated input pin (TxIN). Timer T3 is reloaded with the contents of T2 or T4, triggered either by an external signal or a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be continuously generated without software intervention.

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The counting direction (up/down) for each timer can be programmed by software or altered dynamically with an external signal on a port pin (TxEUD). Concatenation of the timers is supported with the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can also be used to clock the CAPCOM2 timers and to initiate a reload from the CAPREL register.

The CAPREL register can capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN); timer T5 may optionally be cleared after the capture procedure. This allows the XE167xM to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) can also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

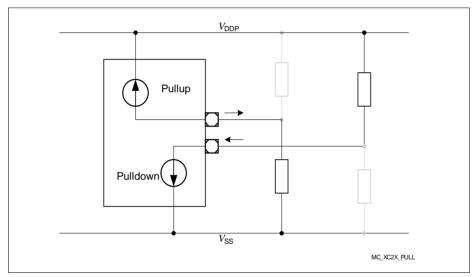

### Pullup/Pulldown Device Behavior

Most pins of the XE167xM feature pullup or pulldown devices. For some special pins these are fixed; for the port pins they can be selected by the application.

The specified current values indicate how to load the respective pin depending on the intended signal level. **Figure 13** shows the current paths.

The shaded resistors shown in the figure may be required to compensate system pull currents that do not match the given limit values.

Figure 13 Pullup/Pulldown Current Definition

| Parameter                        | Symbol             | Values |      | ol Value |   | alues Unit                           |  | Note / |

|----------------------------------|--------------------|--------|------|----------|---|--------------------------------------|--|--------|

|                                  |                    | Min.   | Тур. | Max.     |   | Test Condition                       |  |        |

| Output Low Voltage <sup>8)</sup> | V <sub>OL</sub> CC | -      | -    | 1.0      | V | $I_{\rm OL} \leq I_{\rm OLmax}$      |  |        |

|                                  |                    | -      | -    | 0.4      | V | $I_{\rm OL} \leq I_{\rm OLnom}^{9)}$ |  |        |

#### Table 13 DC Characteristics for Upper Voltage Range (cont'd)

1) Because each double bond pin is connected to two pads (standard pad and high-speed pad), it has twice the normal value. For a list of affected pins refer to the pin definitions table in chapter 2.

- Not subject to production test verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 3) If the input voltage exceeds the respective supply voltage due to ground bouncing ( $V_{\rm IN} < V_{\rm SS}$ ) or supply ripple ( $V_{\rm IN} > V_{\rm DDP}$ ), a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current ( $I_{\rm INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm CV}$ .

- 4) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (*T*<sub>J</sub> = junction temperature [°C]): *I*<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x TJ-)</sup> [µA]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 µA. Leakage derating depending on voltage level (DV = *V*<sub>DDP</sub> *V*<sub>PIN</sub> [V]): *I*<sub>OZ</sub> = *I*<sub>OZtempmax</sub> (1.6 x DV) (µA]. This voltage derating formula is an approximation which applies for maximum temperature.

- 5) Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device: V<sub>PIN</sub> ≤ V<sub>ILmax</sub> for a pullup; V<sub>PIN</sub> ≥ V<sub>ILmin</sub> for a pulldown.

- 6) These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in general purpose IO pins.

- 7) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level: V<sub>PIN</sub> ≥ V<sub>IHmin</sub> for a pullup; V<sub>PIN</sub> ≤ V<sub>ILmax</sub> for a pulldown.

- 8) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 9) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL}$ -> $V_{SS}$ ,  $V_{OH}$ -> $V_{DDP}$ ). However, only the levels for nominal output currents are verified.

# 4.2.2 DC Parameters for Lower Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

Note: Operating Conditions apply.

Table 14 is valid under the following conditions:

$V_{\text{DDP}} \ge 3.0 \text{ V}; V_{\text{DDPtvp}} = 3.3 \text{ V}; V_{\text{DDP}} \le 4.5 \text{ V}$

| Parameter                                                                                            | Symbol                   |                                 | Values | 5                                 | Unit | Note /                                                                                             |

|------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------|--------|-----------------------------------|------|----------------------------------------------------------------------------------------------------|

|                                                                                                      |                          | Min.                            | Тур.   | Typ. Max.                         |      | Test Condition                                                                                     |

| Pin capacitance (digital<br>inputs/outputs). To be<br>doubled for double bond<br>pins. <sup>1)</sup> | C <sub>IO</sub> CC       | -                               | -      | 10                                | pF   | not subject to production test                                                                     |

| Input Hysteresis <sup>2)</sup>                                                                       | HYS CC                   | $0.07 	ext{ x}$ $V_{	ext{DDP}}$ | _      | -                                 | V    | $R_{\rm S} = 0$ Ohm                                                                                |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                                 | I <sub>OZ1</sub>  <br>CC | -                               | 10     | 200                               | nA   | $V_{\rm IN} > V_{\rm SS}; \\ V_{\rm IN} < V_{\rm DDP}$                                             |

| Absolute input leakage<br>current for all other pins.<br>To be doubled for double                    | I <sub>OZ2</sub>  <br>CC | -                               | 0.2    | 2.5                               | μΑ   | $T_{\rm J} \leq 110 ~^{\circ}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| bond pins. <sup>3)1)4)</sup>                                                                         |                          | -                               | 0.2    | 8                                 | μA   | $T_{\rm J} \leq 150 ~^{\circ}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| Pull Level Force Current <sup>5)</sup>                                                               | $ I_{PLF} $ SR           | 150                             | -      | -                                 |      | 6)                                                                                                 |

| Pull Level Keep Current <sup>7)</sup>                                                                | I <sub>PLK</sub>  <br>SR | -                               | _      | 10                                | μA   | 6)                                                                                                 |

| Input high voltage<br>(all except XTAL1)                                                             | $V_{\rm IH}{ m SR}$      | 0.7  x<br>$V_{\text{DDP}}$      | -      | V <sub>DDP</sub><br>+ 0.3         | V    |                                                                                                    |

| Input low voltage<br>(all except XTAL1)                                                              | $V_{IL}  SR$             | -0.3                            | -      | $0.3 	ext{ x}$<br>$V_{	ext{DDP}}$ | V    |                                                                                                    |

| Output High voltage <sup>8)</sup>                                                                    | V <sub>OH</sub> CC       | V <sub>DDP</sub><br>- 1.0       | -      | -                                 | V    | $I_{\rm OH} \ge I_{\rm OHmax}$                                                                     |

|                                                                                                      |                          | V <sub>DDP</sub><br>- 0.4       | -      | -                                 | V    | $I_{\rm OH} \ge I_{\rm OHnom}^{9)}$                                                                |

### Table 14 DC Characteristics for Lower Voltage Range

# 4.2.3 Power Consumption

The power consumed by the XE167xM depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current I<sub>LK</sub> depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  and  $V_{\rm DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

| Parameter                                                                    | Symbol                  | Values |                           |                                                 | Unit | Note /         |

|------------------------------------------------------------------------------|-------------------------|--------|---------------------------|-------------------------------------------------|------|----------------|

|                                                                              |                         | Min.   | Тур.                      | Max.                                            |      | Test Condition |

| Power supply current<br>(active) with all peripherals<br>active and EVVRs on | I <sub>SACT</sub><br>CC | _      | $10 + 0.6 x f_{SYS}^{1)}$ | 10 +<br>1.0 x<br>f <sub>SYS</sub> <sup>1)</sup> | mA   | 2)3)           |

| Power supply current in stopover mode, EVVRs on                              | I <sub>SSO</sub> CC     | -      | 0.7                       | 2.0                                             | mA   |                |

### Table 15 Switching Power Consumption

1)  $f_{\rm SYS}$  in MHz.

| Table 20 Coding of bit fields LEVXV in Register SWDCON0 (contrd) |                       |                     |  |  |  |  |

|------------------------------------------------------------------|-----------------------|---------------------|--|--|--|--|

| Code                                                             | Default Voltage Level | Notes <sup>1)</sup> |  |  |  |  |

| 1001 <sub>B</sub>                                                | 4.5 V                 | LEV2V: no request   |  |  |  |  |

| 1010 <sub>B</sub>                                                | 4.6 V                 |                     |  |  |  |  |

| 1011 <sub>B</sub>                                                | 4.7 V                 |                     |  |  |  |  |

| 1100 <sub>B</sub>                                                | 4.8 V                 |                     |  |  |  |  |

| 1101 <sub>B</sub>                                                | 4.9 V                 |                     |  |  |  |  |

| 1110 <sub>B</sub>                                                | 5.0 V                 |                     |  |  |  |  |

| 1111 <sub>B</sub>                                                | 5.5 V                 |                     |  |  |  |  |

# Table 20 Coding of bit fields LEVxV in Register SWDCON0 (cont'd)

1) The indicated default levels are selected automatically after a power reset.

### Table 21 Coding of Bitfields LEVxV in Registers PVCyCONz

| Code             | Default Voltage Level | Notes <sup>1)</sup>                    |

|------------------|-----------------------|----------------------------------------|

| 000 <sub>B</sub> | 0.95 V                |                                        |

| 001 <sub>B</sub> | 1.05 V                |                                        |

| 010 <sub>B</sub> | 1.15 V                |                                        |

| 011 <sub>B</sub> | 1.25 V                |                                        |

| 100 <sub>B</sub> | 1.35 V                | LEV1V: reset request                   |

| 101 <sub>B</sub> | 1.45 V                | LEV2V: interrupt request <sup>2)</sup> |

| 110 <sub>B</sub> | 1.55 V                |                                        |

| 111 <sub>B</sub> | 1.65 V                |                                        |

1) The indicated default levels are selected automatically after a power reset.

2) Due to variations of the tolerance of both the Embedded Voltage Regulators (EVR) and the PVC levels, this interrupt can be triggered inadvertently, even though the core voltage is within the normal range. It is, therefore, recommended not to use the this warning level.

# **Direct Drive**

When direct drive operation is selected (SYSCON0.CLKSEL =  $11_B$ ), the system clock is derived directly from the input clock signal CLKIN1:

$f_{SYS} = f_{IN}$ .

The frequency of  $f_{SYS}$  is the same as the frequency of  $f_{IN}$ . In this case the high and low times of  $f_{SYS}$  are determined by the duty cycle of the input clock  $f_{IN}$ .

Selecting Bypass Operation from the XTAL1<sup>1)</sup> input and using a divider factor of 1 results in a similar configuration.

### **Prescaler Operation**

When prescaler operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $1_B$ ), the system clock is derived either from the crystal oscillator (input clock signal XTAL1) or from the internal clock source through the output prescaler K1 (= K1DIV+1):

$f_{\text{SYS}} = f_{\text{OSC}} / \text{K1}.$

If a divider factor of 1 is selected, the frequency of  $f_{\rm SYS}$  equals the frequency of  $f_{\rm OSC}$ . In this case the high and low times of  $f_{\rm SYS}$  are determined by the duty cycle of the input clock  $f_{\rm OSC}$  (external or internal).

The lowest system clock frequency results from selecting the maximum value for the divider factor K1:

$f_{\rm SYS} = f_{\rm OSC} / 1024.$

# 4.6.2.1 Phase Locked Loop (PLL)

When PLL operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $0_B$ ), the on-chip phase locked loop is enabled and provides the system clock. The PLL multiplies the input frequency by the factor **F** ( $f_{SYS} = f_{IN} \times F$ ).

**F** is calculated from the input divider P (= PDIV+1), the multiplication factor N (= NDIV+1), and the output divider K2 (= K2DIV+1):

$(F = N / (P \times K2)).$

The input clock can be derived either from an external source at XTAL1 or from the onchip clock source.

The PLL circuit synchronizes the system clock to the input clock. This synchronization is performed smoothly so that the system clock frequency does not change abruptly.

Adjustment to the input clock continuously changes the frequency of  $f_{\text{SYS}}$  so that it is locked to  $f_{\text{IN}}$ . The slight variation causes a jitter of  $f_{\text{SYS}}$  which in turn affects the duration of individual TCSs.

<sup>1)</sup> Voltages on XTAL1 must comply to the core supply voltage  $V_{\text{DDIM}}$ .

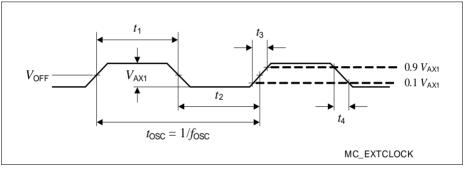

- 1) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

- 2) Overload conditions must not occur on pin XTAL1.

- Note: For crystal or ceramic resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

The manufacturers of crystals and ceramic resonators offer an oscillator evaluation service. This evaluation checks the crystal/resonator specification limits to ensure a reliable oscillator operation.

Figure 21 External Clock Drive XTAL1

Table 26 is valid under the following conditions:

$V_{\text{DDP}} \ge 3.0 \text{ V}; V_{\text{DDPtyp}} = 3.3 \text{ V}; V_{\text{DDP}} \le 4.5 \text{ V}; C_{\text{L}} \ge 20 \text{ pF}; C_{\text{L}} \le 100 \text{ pF};$

| Table 26 | Standard Pad Parameters for Lower Voltage Range |

|----------|-------------------------------------------------|

|----------|-------------------------------------------------|

| Parameter                                                       | Symbol                  | Values |      |                                          | Unit | Note /                        |

|-----------------------------------------------------------------|-------------------------|--------|------|------------------------------------------|------|-------------------------------|

|                                                                 |                         | Min.   | Тур. | Max.                                     |      | Test Condition                |

| Maximum output driver<br>current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -      | -    | 10                                       | mA   | Strong driver                 |

|                                                                 |                         | _      | -    | 2.5                                      | mA   | Medium driver                 |

|                                                                 |                         | -      | -    | 0.5                                      | mA   | Weak driver                   |

| Nominal output driver current (absolute value)                  | I <sub>Onom</sub><br>CC | -      | -    | 2.5                                      | mA   | Strong driver                 |

|                                                                 |                         | _      | -    | 1.0                                      | mA   | Medium driver                 |

|                                                                 |                         | -      | -    | 0.1                                      | mA   | Weak driver                   |

| Rise and Fall times (10% -<br>90%)                              | t <sub>RF</sub> CC      | -      | -    | 6.2 +<br>0.24 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Sharp edge  |

|                                                                 |                         | -      | -    | 24 +<br>0.3 x<br>C <sub>L</sub>          | ns   | Strong driver;<br>Medium edge |

|                                                                 |                         | -      | -    | 34 +<br>0.3 x<br>C <sub>L</sub>          | ns   | Strong driver;<br>Slow edge   |

|                                                                 |                         | _      | -    | 37 +<br>0.65 x<br><i>C</i> <sub>L</sub>  | ns   | Medium driver                 |

|                                                                 |                         | -      | -    | 500 +<br>2.5 x<br><i>C</i> L             | ns   | Weak driver                   |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

# 4.6.5 External Bus Timing

The following parameters specify the behavior of the XE167xM bus interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

### **Bus Interface Performance Limits**

The output frequency at the bus interface pins is limited by the performance of the output drivers. The fast clock driver (used for CLKOUT) can drive 80-MHz signals, the standard drivers can drive 40-MHz signals

Therefore, the speed of the EBC must be limited, either by limiting the system frequency to  $f_{SYS} \le 80$  MHz or by adding waitstates so that signal transitions have a minimum distance of 12.5 ns.

For a description of the bus protocol and the programming of its variable timing parameters, please refer to the User's Manual.

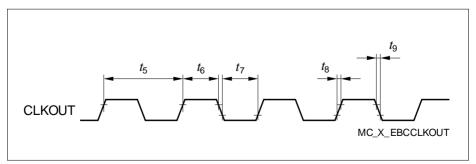

| Parameter                       | Symbol            | Values |                 |      | Unit | Note /         |

|---------------------------------|-------------------|--------|-----------------|------|------|----------------|

|                                 |                   | Min.   | Тур.            | Max. |      | Test Condition |

| CLKOUT Cycle Time <sup>1)</sup> | t <sub>5</sub> CC | -      | $1/f_{\rm SYS}$ | -    | ns   |                |

| CLKOUT high time                | t <sub>6</sub> CC | 2      | -               | -    |      |                |

| CLKOUT low time                 | t <sub>7</sub> CC | 2      | _               | _    |      |                |

| CLKOUT rise time                | t <sub>8</sub> CC | -      | -               | 3    | ns   |                |

| CLKOUT fall time                | t <sub>9</sub> CC | -      | -               | 3    |      |                |

### Table 27 EBC Parameters

1) The CLKOUT cycle time is influenced by PLL jitter. For longer periods the relative deviation decreases (see PLL deviation formula).

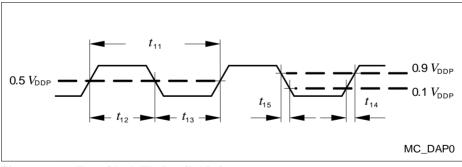

| Parameter                                         | Symbol                    | Values           |      |      | Unit | Note /                 |

|---------------------------------------------------|---------------------------|------------------|------|------|------|------------------------|

|                                                   |                           | Min.             | Тур. | Max. |      | Test Condition         |

| DAP0 clock period                                 | <i>t</i> <sub>11</sub> SR | 25 <sup>1)</sup> | -    | -    | ns   |                        |

| DAP0 high time                                    | t <sub>12</sub> SR        | 8                | -    | -    | ns   |                        |

| DAP0 low time                                     | t <sub>13</sub> SR        | 8                | -    | _    | ns   |                        |

| DAP0 clock rise time                              | t <sub>14</sub> SR        | -                | -    | 4    | ns   |                        |

| DAP0 clock fall time                              | t <sub>15</sub> SR        | -                | -    | 4    | ns   |                        |

| DAP1 setup to DAP0<br>rising edge                 | <i>t</i> <sub>16</sub> SR | 6                | -    | -    | ns   | pad_type= stan<br>dard |

| DAP1 hold after DAP0 rising edge                  | <i>t</i> <sub>17</sub> SR | 6                | -    | -    | ns   | pad_type= stan<br>dard |

| DAP1 valid per DAP0<br>clock period <sup>2)</sup> | <i>t</i> <sub>19</sub> CC | 12               | 17   | -    | ns   | pad_type= stan<br>dard |

# Table 38 DAP Interface Timing for Lower Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_{11} \ge t_{SYS}$ .

2) The Host has to find a suitable sampling point by analyzing the sync telegram response.

Figure 29 Test Clock Timing (DAP0)