E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 119                                                                              |

| Program Memory Size        | 384KB (384K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 24x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xe167fm-48f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 4.6<br>4.6.1 | AC Parameters                                  |

|--------------|------------------------------------------------|

| 4.6.2        | Definition of Internal Timing 109              |

| 4.6.2.1      | Phase Locked Loop (PLL) 110                    |

| 4.6.2.2      | Wakeup Clock 113                               |

| 4.6.2.3      | Selecting and Changing the Operating Frequency |

| 4.6.3        | External Clock Input Parameters 114            |

| 4.6.4        | Pad Properties                                 |

| 4.6.5        | External Bus Timing 119                        |

| 4.6.5.1      | Bus Cycle Control with the READY Input 125     |

| 4.6.5.2      | External Bus Arbitration 127                   |

| 4.6.6        | Synchronous Serial Interface Timing 130        |

| 4.6.7        | Debug Interface Timing 134                     |

| 5            | Package and Reliability 140                    |

| 5.1          | Packaging                                      |

| 5.2          | Thermal Considerations 142                     |

| 5.3          | Quality Declarations                           |

#### Summary of Features

- Two Synchronizable A/D Converters with a total of up to 24 channels, 10-bit resolution, conversion time below  $1 \,\mu s$ , optional data preprocessing (data reduction, range check), broken wire detection

- Up to 8 serial interface channels to be used as UART, LIN, high-speed synchronous channel (SPI), IIC bus interface (10-bit addressing, 400 kbit/s), IIS interface

- On-chip MultiCAN interface (Rev. 2.0B active) with up to 128 message objects (Full CAN/Basic CAN) on up to 6 CAN nodes and gateway functionality

- On-chip system timer and on-chip real time clock

- Up to 12 Mbytes external address space for code and data

- Programmable external bus characteristics for different address ranges

- Multiplexed or demultiplexed external address/data buses

- Selectable address bus width

- 16-bit or 8-bit data bus width

- Five programmable chip-select signals

- Hold- and hold-acknowledge bus arbitration support

- Single power supply from 3.0 V to 5.5 V

- Programmable watchdog timer and oscillator watchdog

- Up to 119 general purpose I/O lines

- On-chip bootstrap loaders

- Supported by a full range of development tools including C compilers, macroassembler packages, emulators, evaluation boards, HLL debuggers, simulators, logic analyzer disassemblers, programming boards

- On-chip debug support via Device Access Port (DAP) or JTAG interface

- 144-pin Green LQFP package, 0.5 mm (19.7 mil) pitch

| Tabl | Table 5         Pin Definitions and Functions (cont'd) |        |      |                                               |  |

|------|--------------------------------------------------------|--------|------|-----------------------------------------------|--|

| Pin  | Symbol                                                 | Ctrl.  | Туре | Function                                      |  |

| 75   | P0.0                                                   | O0 / I | St/B | Bit 0 of Port 0, General Purpose Input/Output |  |

|      | U1C0_DOUT                                              | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |

|      | CCU61_CC6<br>0                                         | O3     | St/B | CCU61 Channel 0 IOutput                       |  |

|      | A0                                                     | OH     | St/B | External Bus Interface Address Line 0         |  |

|      | U1C0_DX0A                                              | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |

|      | CCU61_CC6<br>0INA                                      | I      | St/B | CCU61 Channel 0 Input                         |  |

|      | ESR1_11                                                | I      | St/B | ESR1 Trigger Input 11                         |  |

| 76   | P4.5                                                   | O0 / I | St/B | Bit 5 of Port 4, General Purpose Input/Output |  |

|      | U3C0_DOUT                                              | 01     | St/B | USIC3 Channel 0 Shift Data Output             |  |

|      | CC2_CC29                                               | O3 / I | St/B | CAPCOM2 CC29IO Capture Inp./Compare Out.      |  |

|      | CCU61_CCP<br>OS0A                                      | I      | St/B | CCU61 Position Input 0                        |  |

|      | U3C0_DX0B                                              | I      | St/B | USIC3 Channel 0 Shift Data Input              |  |

|      | ESR2_10                                                | I      | St/B | ESR2 Trigger Input 10                         |  |

| 77   | P4.6                                                   | O0 / I | St/B | Bit 6 of Port 4, General Purpose Input/Output |  |

|      | U3C0_DOUT                                              | 01     | St/B | USIC3 Channel 0 Shift Data Output             |  |

|      | CC2_CC30                                               | O3 / I | St/B | CAPCOM2 CC30IO Capture Inp./ Compare Out.     |  |

|      | T4INA                                                  | I      | St/B | GPT12E Timer T4 Count/Gate Input              |  |

|      | CCU61_CCP<br>OS1A                                      | I      | St/B | CCU61 Position Input 1                        |  |

| 78   | P2.7                                                   | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |

|      | U0C1_SELO<br>0                                         | 01     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |

|      | U0C0_SELO<br>1                                         | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |

|      | CC2_CC20                                               | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |

|      | A20                                                    | ОН     | St/B | External Bus Interface Address Line 20        |  |

|      | U0C1_DX2C                                              | I      | St/B | USIC0 Channel 1 Shift Control Input           |  |

|      | RxDC1C                                                 | I      | St/B | CAN Node 1 Receive Data Input                 |  |

|      | ESR2_7                                                 | I      | St/B | ESR2 Trigger Input 7                          |  |

| Table | Table 5         Pin Definitions and Functions (cont'd) |            |      |                                                                                                                                                                    |  |  |

|-------|--------------------------------------------------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                                                                                                                                           |  |  |

| 117   | P10.10                                                 | O0 / I     | St/B | Bit 10 of Port 10, General Purpose Input/Output                                                                                                                    |  |  |

|       | U0C0_SELO<br>0                                         | 01         | St/B | USIC0 Channel 0 Select/Control 0 Output                                                                                                                            |  |  |

|       | CCU60_COU<br>T63                                       | 02         | St/B | CCU60 Channel 3 Output                                                                                                                                             |  |  |

|       | AD10                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 10                                                                                                                        |  |  |

|       | U0C0_DX2C                                              | I          | St/B | USIC0 Channel 0 Shift Control Input                                                                                                                                |  |  |

|       | U0C1_DX1A                                              | I          | St/B | USIC0 Channel 1 Shift Clock Input                                                                                                                                  |  |  |

|       | TDI_B                                                  | IH         | St/B | JTAG Test Data Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.           |  |  |

| 118   | P10.11                                                 | O0 / I     | St/B | Bit 11 of Port 10, General Purpose Input/Output                                                                                                                    |  |  |

|       | U1C0_SCLK<br>OUT                                       | 01         | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                 |  |  |

|       | BRKOUT                                                 | O2         | St/B | OCDS Break Signal Output                                                                                                                                           |  |  |

|       | U3C0_SELO<br>0                                         | O3         | St/B | USIC3 Channel 0 Select/Control 0 Output                                                                                                                            |  |  |

|       | AD11                                                   | OH /<br>IH | St/B | External Bus Interface Address/Data Line 11                                                                                                                        |  |  |

|       | U1C0_DX1D                                              | I          | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                  |  |  |

|       | RxDC2B                                                 | I          | St/B | CAN Node 2 Receive Data Input                                                                                                                                      |  |  |

|       | TMS_B                                                  | IH         | St/B | JTAG Test Mode Selection Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it. |  |  |

|       | U3C0_DX2A                                              | I          | St/B | USIC3 Channel 0 Shift Control Input                                                                                                                                |  |  |

| 119   | P9.2                                                   | O0 / I     | St/B | Bit 2 of Port 9, General Purpose Input/Output                                                                                                                      |  |  |

|       | CCU63_CC6<br>2                                         | 01         | St/B | CCU63 Channel 2 Output                                                                                                                                             |  |  |

|       | CCU63_CC6<br>2INA                                      | I          | St/B | CCU63 Channel 2 Input                                                                                                                                              |  |  |

|       | CAPINB                                                 | I          | St/B | GPT12E Register CAPREL Capture Input                                                                                                                               |  |  |

| Table 5     Pin Definitions and Functions (cont'd) |                  |        |      |                                                                                                                                                    |  |

|----------------------------------------------------|------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                                                | Symbol           | Ctrl.  | Туре | Function                                                                                                                                           |  |

| 123                                                | P10.13           | O0 / I | St/B | Bit 13 of Port 10, General Purpose Input/Output                                                                                                    |  |

|                                                    | U1C0_DOUT        | O1     | St/B | USIC1 Channel 0 Shift Data Output                                                                                                                  |  |

|                                                    | TxDC3            | O2     | St/B | CAN Node 3 Transmit Data Output                                                                                                                    |  |

|                                                    | U1C0_SELO<br>3   | O3     | St/B | USIC1 Channel 0 Select/Control 3 Output                                                                                                            |  |

|                                                    | WR/WRL           | ОН     | St/B | External Bus Interface Write Strobe Output<br>Active for each external write access, when WR,<br>active for ext. writes to the low byte, when WRL. |  |

|                                                    | U1C0_DX0D        | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                   |  |

| 124                                                | P1.3             | O0 / I | St/B | Bit 3 of Port 1, General Purpose Input/Output                                                                                                      |  |

|                                                    | CCU62_COU<br>T63 | 01     | St/B | CCU62 Channel 3 Output                                                                                                                             |  |

|                                                    | U1C0_SELO<br>7   | 02     | St/B | USIC1 Channel 0 Select/Control 7 Output                                                                                                            |  |

|                                                    | U2C0_SELO<br>4   | O3     | St/B | USIC2 Channel 0 Select/Control 4 Output                                                                                                            |  |

|                                                    | A11              | ОН     | St/B | External Bus Interface Address Line 11                                                                                                             |  |

|                                                    | ESR2_4           | I      | St/B | ESR2 Trigger Input 4                                                                                                                               |  |

|                                                    | CCU62_T12<br>HRB | I      | St/B | External Run Control Input for T12 of CCU62                                                                                                        |  |

| 125                                                | P9.4             | O0 / I | St/B | Bit 4 of Port 9, General Purpose Input/Output                                                                                                      |  |

|                                                    | CCU63_COU<br>T61 | 01     | St/B | CCU63 Channel 1 Output                                                                                                                             |  |

|                                                    | U2C0_DOUT        | O2     | St/B | USIC2 Channel 0 Shift Data Output                                                                                                                  |  |

|                                                    | CCU62_COU<br>T63 | O3     | St/B | CCU62 Channel 3 Output                                                                                                                             |  |

| Table 5         Pin Definitions and Functions (cont'd) |           |        |      |                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------------------------------------|-----------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                                                    | Symbol    | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                         |  |

| 137                                                    | XTAL1     | I      | Sp/M | <b>Crystal Oscillator Amplifier Input</b><br>To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected.<br>Voltages on XTAL1 must comply to the core supply voltage $V_{\text{DDIM}}$ .                                                                                                                          |  |

|                                                        | ESR2_9    | I      | St/B | ESR2 Trigger Input 9                                                                                                                                                                                                                                                                                                                             |  |

| 138                                                    | PORST     | 1      | In/B | <b>Power On Reset Input</b><br>A low level at this pin resets the XE167xM<br>completely. A spike filter suppresses input pulses<br><10 ns. Input pulses >100 ns safely pass the filter.<br>The minimum duration for a safe recognition<br>should be 120 ns.<br>An internal pull-up device will hold this pin high<br>when nothing is driving it. |  |

| 139                                                    | ESR1      | O0 / I | St/B | <b>External Service Request 1</b><br>After power-up, an internal weak pull-up device<br>holds this pin high when nothing is driving it.                                                                                                                                                                                                          |  |

|                                                        | RxDC0E    | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                                                                                                                                                                                    |  |

|                                                        | U1C0_DX0F | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                 |  |

|                                                        | U1C0_DX2C | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                                                                              |  |

|                                                        | U1C1_DX0C | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                                                 |  |

|                                                        | U1C1_DX2B | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                                                                                                              |  |

|                                                        | U2C1_DX2C | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                                                                                                              |  |

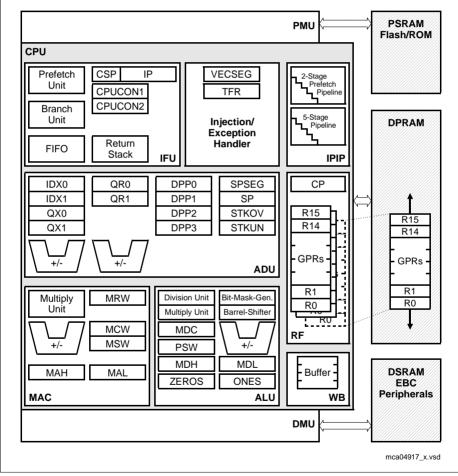

# 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

# 3.8 Capture/Compare Unit (CAPCOM2)

The CAPCOM2 unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM2 unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

Two 16-bit timers (T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range or variation for the timer period and resolution and allows precise adjustments to the application-specific requirements. In addition, an external count input allows event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

| Compare Modes | Function                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| Mode 0        | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1        | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

Table 8 Compare Modes

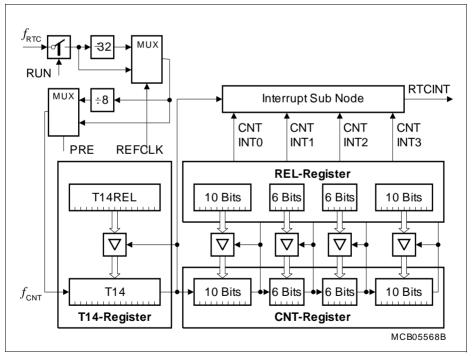

# 3.11 Real Time Clock

The Real Time Clock (RTC) module of the XE167xM can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

### Figure 10 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

# 3.16 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.42 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

## 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XE167xM from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

2) The pad supply voltage pins (V<sub>DDPB</sub>) provide the input current for the on-chip EVVRs and the current consumed by the pin output drivers. A small current is consumed because the drivers input stages are switched.

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to  $3 + 0.6 \text{ x} f_{SYS}$ .

3) Please consider the additional conditions described in section "Active Mode Power Supply Current".

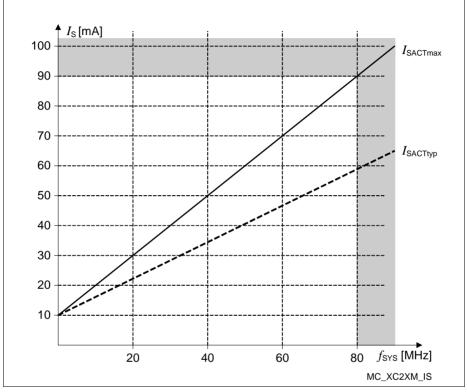

### Active Mode Power Supply Current

The actual power supply current in active mode not only depends on the system frequency but also on the configuration of the XE167xM's subsystem.

Besides the power consumed by the device logic the power supply pins also provide the current that flows through the pin output drivers.

A small current is consumed because the drivers' input stages are switched.

The IO power domains can be supplied separately. Power domain A ( $V_{\rm DDPA}$ ) supplies the A/D converters and Port 6. Power domain B ( $V_{\rm DDPB}$ ) supplies the on-chip EVVRs and all other ports.

During operation domain A draws a maximum current of 1.5 mA for each active A/D converter module from  $V_{\rm DDPA}$ .

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to  $(3 + 0.6 \times f_{SYS})$  mA.

### **Electrical Parameters**

Figure 14Supply Current in Active Mode as a Function of FrequencyNote: Operating Conditions apply.

**Electrical Parameters**

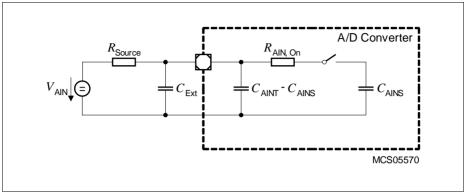

Figure 16 Equivalent Circuitry for Analog Inputs

## 4.5 Flash Memory Parameters

The XE167xM is delivered with all Flash sectors erased and with no protection installed. The data retention time of the XE167xM's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                 | Symbol                                 |           | Values          | 8               | Unit       | Note /                                                                    |  |

|-------------------------------------------|----------------------------------------|-----------|-----------------|-----------------|------------|---------------------------------------------------------------------------|--|

|                                           |                                        | Min. Typ. |                 | Max.            |            | Test Condition                                                            |  |

| Parallel Flash module program/erase limit | $N_{\rm PP}{ m SR}$                    | -         | -               | 4 <sup>1)</sup> |            | $N_{\text{FL}_{\text{RD}}} \le 1,$<br>$f_{\text{SYS}} \le 80 \text{ MHz}$ |  |

| depending on Flash read activity          |                                        | -         | -               | 1 <sup>2)</sup> |            | $N_{\rm FL_RD}$ > 1                                                       |  |

| Flash erase endurance for security pages  | $N_{\rm SEC}{ m SR}$                   | 10        | -               | -               | cycle<br>s | $t_{RET} \ge 20$ years                                                    |  |

| Flash wait states3)                       | N <sub>WSFLAS</sub><br><sub>H</sub> SR | 1         | -               | -               |            | $f_{SYS} \le 8 \text{ MHz}$                                               |  |

|                                           |                                        | 2         | -               | -               |            | $f_{SYS} \le 13 \text{ MHz}$                                              |  |

|                                           |                                        | 3         | -               | -               |            | $f_{\rm SYS} \le 17 \ \rm MHz$                                            |  |

|                                           |                                        | 4         | -               | -               |            | $f_{\rm SYS}$ > 17 MHz                                                    |  |

| Erase time per<br>sector/page             | t <sub>ER</sub> CC                     | -         | 7 <sup>4)</sup> | 8.0             | ms         |                                                                           |  |

| Programming time per page                 | t <sub>PR</sub> CC                     | -         | 34)             | 3.5             | ms         |                                                                           |  |

| Data retention time                       | t <sub>RET</sub> CC                    | 20        | -               | -               | year<br>s  | $N_{\rm Er} \le 1\ 000$ cycles                                            |  |

| Drain disturb limit                       | $N_{\rm DD}{ m SR}$                    | 32        | -               | -               | cycle<br>s |                                                                           |  |

#### Table 22 Flash Parameters

## 4.6 AC Parameters

These parameters describe the dynamic behavior of the XE167xM.

## 4.6.1 Testing Waveforms

These values are used for characterization and production testing (except pin XTAL1).

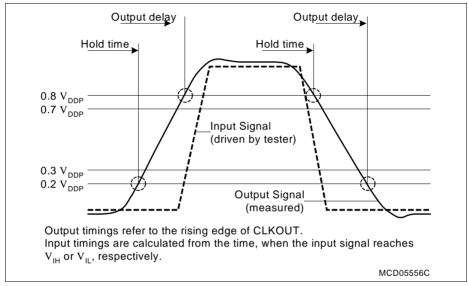

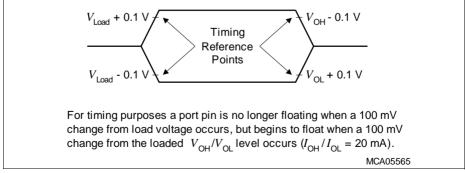

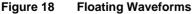

Figure 17 Input Output Waveforms

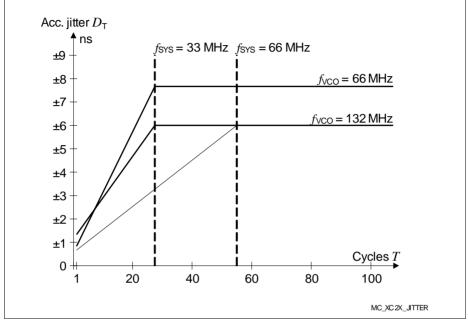

Figure 20 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_L = 20 \text{ pF}$ .

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{DDPB}$  pin 100 and  $V_{SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

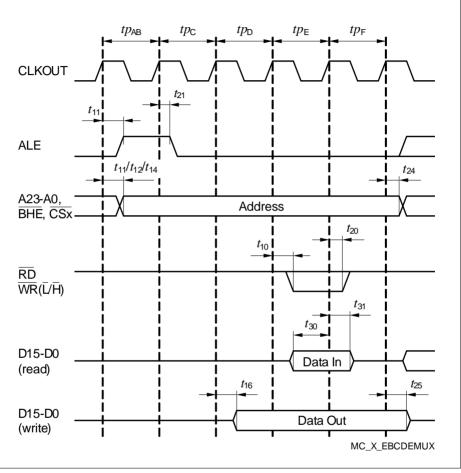

### Variable Memory Cycles

External bus cycles of the XE167xM are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

| Table 28Programmable Bus Cycle Phases (see timing diagrams) |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| Bus Cycle Phase                                                                                                                                | Parameter | Valid Values | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 $\dots$ 2 TCS) can be extended by 0 $\dots$ 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                                            | tpC       | 03           | TCS  |

| Write Data setup/MUX Tristate phase                                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                                  | tpF       | 03           | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

**Electrical Parameters**

**Electrical Parameters**

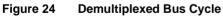

Figure 25 READY Timing

Note: If the READY input is sampled inactive at the indicated sampling point ("Not Rdy") a READY-controlled waitstate is inserted (tpRDY),

sampling the READY input active at the indicated sampling point ("Ready") terminates the currently running bus cycle.

Note the different sampling points for synchronous and asynchronous READY. This example uses one mandatory waitstate (see tpE) before the READY input value is used.

### Debug via JTAG

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_L$ = 20 pF.

| Parameter                                                                | Symbol                    | Values           |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|------------------|------|------|------|----------------|

|                                                                          |                           | Min.             | Тур. | Max. |      | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 50 <sup>1)</sup> | _    | -    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR         | 16               | -    | -    | ns   |                |

| TCK low time                                                             | t <sub>3</sub> SR         | 16               | -    | -    | ns   |                |

| TCK clock rise time                                                      | $t_4$ SR                  | -                | -    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | -                | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | -                | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                | -    | -    | ns   |                |

#### Table 39JTAG Interface Timing for Upper Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the interface can operate at transfer rates up to 20 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.