Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C1665V2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 119                                                                              |

| Program Memory Size        | 384КВ (384К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/sak-xe167gm-48f80l-aa |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| XE167xI<br>Revisio | M<br>n History: V2.1, 2011-07                             |  |  |  |  |

|--------------------|-----------------------------------------------------------|--|--|--|--|

| Previous           | s Version(s):                                             |  |  |  |  |

| V2.0, 20           | 09-03                                                     |  |  |  |  |

| V1.3, 20           | 08-11                                                     |  |  |  |  |

| V1.2, 20           | 08-09                                                     |  |  |  |  |

| V1.1, 20           | 08-06 Preliminary                                         |  |  |  |  |

| V1.0, 20           | 08-06 (Intermediate version)                              |  |  |  |  |

| Page               | Subjects (major changes since last revisions)             |  |  |  |  |

| 52                 | ID registers added                                        |  |  |  |  |

| 99                 | ADC capacitances corrected (typ. vs. max.)                |  |  |  |  |

| 103                | <b>103</b> Conditions relaxed for $\Delta f_{\text{INT}}$ |  |  |  |  |

|                    | Range for $f_{WU}$ adapted according to PCN 2010-013-A    |  |  |  |  |

|                    | Added startup time from power-on $t_{SPO}$                |  |  |  |  |

| 143                | Quality #declarations added                               |  |  |  |  |

#### Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### **Summary of Features**

## 16-Bit Single-Chip Real Time Signal Controller

XE167xM (XE166 Family)

# 1 Summary of Features

For a quick overview and easy reference, the features of the XE167xM are summarized here.

- High-performance CPU with five-stage pipeline and MPU

- 12.5 ns instruction cycle at 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1024 Bytes on-chip special function register area (C166 Family compatible)

- Integrated Memory Protection Unit (MPU)

- · Interrupt system with 16 priority levels for up to 96 sources

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- Up to 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 32 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 576 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

- On-Chip Peripheral Modules

- Multi-functional general purpose timer unit with 5 timers

- 16-channel general purpose capture/compare unit (CAPCOM2)

- Up to 4 capture/compare units for flexible PWM signal generation (CCU6x)

#### **Summary of Features**

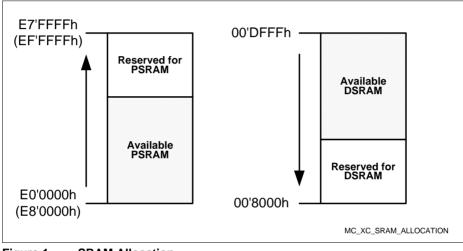

The XE167xM types are offered with several SRAM memory sizes. **Figure 1** shows the allocation rules for PSRAM and DSRAM. Note that the rules differ:

- PSRAM allocation starts from the lower address

- DSRAM allocation starts from the higher address

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

Figure 1 SRAM Allocation

| Table 5         Pin Definitions and Functions (cont'd) |                   |        |      |                                                |  |  |

|--------------------------------------------------------|-------------------|--------|------|------------------------------------------------|--|--|

| Pin                                                    | Symbol            | Ctrl.  | Туре | Function                                       |  |  |

| 66                                                     | P11.0             | O0 / I | St/B | Bit 0 of Port 11, General Purpose Input/Output |  |  |

|                                                        | CCU61_COU<br>T60  | 01     | St/B | CCU61 Channel 0 Output                         |  |  |

|                                                        | U3C1_SCLK<br>OUT  | O2     | St/B | USIC3 Channel 1 Shift Clock Output             |  |  |

|                                                        | CCU63_CCP<br>OS0A | 1      | St/B | CCU63 Position Input 0                         |  |  |

|                                                        | RxDC0F            | I      | St/B | CAN Node 0 Receive Data Input                  |  |  |

|                                                        | U3C1_DX1A         | I      | St/B | USIC3 Channel 1 Shift Clock Input              |  |  |

|                                                        | ESR1_7            | I      | St/B | ESR1 Trigger Input 7                           |  |  |

| 67                                                     | P2.5              | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output  |  |  |

| -                                                      | U0C0_SCLK<br>OUT  | 01     | St/B | USIC0 Channel 0 Shift Clock Output             |  |  |

|                                                        | TxDC0             | O2     | St/B | CAN Node 0 Transmit Data Output                |  |  |

|                                                        | CC2_CC18          | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.      |  |  |

|                                                        | A18               | ОН     | St/B | External Bus Interface Address Line 18         |  |  |

|                                                        | U0C0_DX1D         | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |

|                                                        | ESR1_10           | I      | St/B | ESR1 Trigger Input 10                          |  |  |

| 68                                                     | P4.2              | O0 / I | St/B | Bit 2 of Port 4, General Purpose Input/Output  |  |  |

|                                                        | U3C0_SCLK<br>OUT  | 01     | St/B | USIC3 Channel 0 Shift Clock Output             |  |  |

|                                                        | TxDC2             | O2     | St/B | CAN Node 2 Transmit Data Output                |  |  |

|                                                        | CC2_CC26          | O3 / I | St/B | CAPCOM2 CC26IO Capture Inp./ Compare Out.      |  |  |

|                                                        | CS2               | ОН     | St/B | External Bus Interface Chip Select 2 Output    |  |  |

|                                                        | T2INA             | I      | St/B | GPT12E Timer T2 Count/Gate Input               |  |  |

|                                                        | CCU62_CCP<br>OS1B | I      | St/B | CCU62 Position Input 1                         |  |  |

|                                                        | U3C0_DX1B         | I      | St/B | USIC3 Channel 0 Shift Clock Input              |  |  |

## XE167FM, XE167GM, XE167HM, XE167KM XE166 Family / Base Line

### **General Device Information**

| Table 5         Pin Definitions and Functions (cont'd) |                   |            |      |                                                |  |

|--------------------------------------------------------|-------------------|------------|------|------------------------------------------------|--|

| Pin                                                    | Symbol            | Ctrl.      | Туре | Function                                       |  |

| 84                                                     | P10.0             | O0 / I     | St/B | Bit 0 of Port 10, General Purpose Input/Output |  |

|                                                        | U0C1_DOUT         | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |

|                                                        | CCU60_CC6<br>0    | O2         | St/B | CCU60 Channel 0 Output                         |  |

|                                                        | AD0               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 0     |  |

|                                                        | CCU60_CC6<br>0INA | I          | St/B | CCU60 Channel 0 Input                          |  |

|                                                        | ESR1_2            | I          | St/B | ESR1 Trigger Input 2                           |  |

|                                                        | U0C0_DX0A         | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |

|                                                        | U0C1_DX0A         | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |

| 85                                                     | P3.0              | O0 / I     | St/B | Bit 0 of Port 3, General Purpose Input/Output  |  |

| -                                                      | U2C0_DOUT         | 01         | St/B | USIC2 Channel 0 Shift Data Output              |  |

|                                                        | BREQ              | OH         | St/B | External Bus Request Output                    |  |

|                                                        | ESR1_1            | I          | St/B | ESR1 Trigger Input 1                           |  |

|                                                        | U2C0_DX0A         | I          | St/B | USIC2 Channel 0 Shift Data Input               |  |

|                                                        | RxDC3B            | I          | St/B | CAN Node 3 Receive Data Input                  |  |

|                                                        | U2C0_DX1A         | I          | St/B | USIC2 Channel 0 Shift Clock Input              |  |

| 86                                                     | P10.1             | O0 / I     | St/B | Bit 1 of Port 10, General Purpose Input/Output |  |

|                                                        | U0C0_DOUT         | 01         | St/B | USIC0 Channel 0 Shift Data Output              |  |

|                                                        | CCU60_CC6<br>1    | O2         | St/B | CCU60 Channel 1 Output                         |  |

|                                                        | AD1               | OH /<br>IH | St/B | External Bus Interface Address/Data Line 1     |  |

|                                                        | CCU60_CC6<br>1INA | I          | St/B | CCU60 Channel 1 Input                          |  |

|                                                        | U0C0_DX1A         | I          | St/B | USIC0 Channel 0 Shift Clock Input              |  |

|                                                        | U0C0_DX0B         | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |

| Table 5         Pin Definitions and Functions (cont'd) |                  |            |      |                                                |  |

|--------------------------------------------------------|------------------|------------|------|------------------------------------------------|--|

| Pin                                                    | Symbol           | Ctrl.      | Туре | Function                                       |  |

| 101                                                    | P3.5             | O0 / I     | St/B | Bit 5 of Port 3, General Purpose Input/Output  |  |

|                                                        | U2C1_SCLK<br>OUT | O1         | St/B | USIC2 Channel 1 Shift Clock Output             |  |

|                                                        | U2C0_SELO<br>2   | O2         | St/B | USIC2 Channel 0 Select/Control 2 Output        |  |

|                                                        | U0C0_SELO<br>5   | O3         | St/B | USIC0 Channel 0 Select/Control 5 Output        |  |

|                                                        | U2C1_DX1A        | I          | St/B | USIC2 Channel 1 Shift Clock Input              |  |

| 102                                                    | P0.6             | O0 / I     | St/B | Bit 6 of Port 0, General Purpose Input/Output  |  |

|                                                        | U1C1_DOUT        | O1         | St/B | USIC1 Channel 1 Shift Data Output              |  |

|                                                        | TxDC1            | O2         | St/B | CAN Node 1 Transmit Data Output                |  |

| -                                                      | CCU61_COU<br>T63 | O3         | St/B | CCU61 Channel 3 Output                         |  |

|                                                        | A6               | ОН         | St/B | External Bus Interface Address Line 6          |  |

|                                                        | U1C1_DX0A        | I          | St/B | USIC1 Channel 1 Shift Data Input               |  |

|                                                        | CCU61_CTR<br>APA | I          | St/B | CCU61 Emergency Trap Input                     |  |

|                                                        | U1C1_DX1B        | I          | St/B | USIC1 Channel 1 Shift Clock Input              |  |

| 103                                                    | P10.6            | O0 / I     | St/B | Bit 6 of Port 10, General Purpose Input/Output |  |

|                                                        | U0C0_DOUT        | 01         | St/B | USIC0 Channel 0 Shift Data Output              |  |

|                                                        | TxDC4            | O2         | St/B | CAN Node 4 Transmit Data Output                |  |

|                                                        | U1C0_SELO<br>0   | O3         | St/B | USIC1 Channel 0 Select/Control 0 Output        |  |

|                                                        | AD6              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 6     |  |

|                                                        | U0C0_DX0C        | I          | St/B | USIC0 Channel 0 Shift Data Input               |  |

|                                                        | U1C0_DX2D        | I          | St/B | USIC1 Channel 0 Shift Control Input            |  |

| _                                                      | CCU60_CTR<br>APA | 1          | St/B | CCU60 Emergency Trap Input                     |  |

| Table | e 5 Pin De        | finition   | is and | Functions (cont'd)                                                                                                                                                 |

|-------|-------------------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin   | Symbol            | Ctrl.      | Туре   | Function                                                                                                                                                           |

| 117   | P10.10            | O0 / I     | St/B   | Bit 10 of Port 10, General Purpose Input/Output                                                                                                                    |

|       | U0C0_SELO<br>0    | 01         | St/B   | USIC0 Channel 0 Select/Control 0 Output                                                                                                                            |

|       | CCU60_COU<br>T63  | 02         | St/B   | CCU60 Channel 3 Output                                                                                                                                             |

|       | AD10              | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 10                                                                                                                        |

|       | U0C0_DX2C         | I          | St/B   | USIC0 Channel 0 Shift Control Input                                                                                                                                |

|       | U0C1_DX1A         | I          | St/B   | USIC0 Channel 1 Shift Clock Input                                                                                                                                  |

|       | TDI_B             | IH         | St/B   | JTAG Test Data Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.           |

| 118   | P10.11            | O0 / I     | St/B   | Bit 11 of Port 10, General Purpose Input/Output                                                                                                                    |

| -     | U1C0_SCLK<br>OUT  | 01         | St/B   | USIC1 Channel 0 Shift Clock Output                                                                                                                                 |

|       | BRKOUT            | O2         | St/B   | OCDS Break Signal Output                                                                                                                                           |

|       | U3C0_SELO<br>0    | O3         | St/B   | USIC3 Channel 0 Select/Control 0 Output                                                                                                                            |

|       | AD11              | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 11                                                                                                                        |

|       | U1C0_DX1D         | I          | St/B   | USIC1 Channel 0 Shift Clock Input                                                                                                                                  |

|       | RxDC2B            | I          | St/B   | CAN Node 2 Receive Data Input                                                                                                                                      |

|       | TMS_B             | IH         | St/B   | JTAG Test Mode Selection Input<br>If JTAG pos. B is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it. |

|       | U3C0_DX2A         | I          | St/B   | USIC3 Channel 0 Shift Control Input                                                                                                                                |

| 119   | P9.2              | O0 / I     | St/B   | Bit 2 of Port 9, General Purpose Input/Output                                                                                                                      |

|       | CCU63_CC6<br>2    | 01         | St/B   | CCU63 Channel 2 Output                                                                                                                                             |

|       | CCU63_CC6<br>2INA | 1          | St/B   | CCU63 Channel 2 Input                                                                                                                                              |

|       | CAPINB            | Ι          | St/B   | GPT12E Register CAPREL Capture Input                                                                                                                               |

| Table 5         Pin Definitions and Functions (cont'd) |           |        |      |                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------|-----------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                                                    | Symbol    | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                  |

| 137                                                    | XTAL1     | I      | Sp/M | <b>Crystal Oscillator Amplifier Input</b><br>To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Voltages on XTAL1 must comply to the core supply voltage $V_{\text{DDIM}}$ .                                                                                                                      |

|                                                        | ESR2_9    | I      | St/B | ESR2 Trigger Input 9                                                                                                                                                                                                                                                                                                                      |

| 138                                                    | PORST     | 1      | In/B | Power On Reset Input<br>A low level at this pin resets the XE167xM<br>completely. A spike filter suppresses input pulses<br><10 ns. Input pulses >100 ns safely pass the filter.<br>The minimum duration for a safe recognition<br>should be 120 ns.<br>An internal pull-up device will hold this pin high<br>when nothing is driving it. |

| 139                                                    | ESR1      | O0 / I | St/B | <b>External Service Request 1</b><br>After power-up, an internal weak pull-up device<br>holds this pin high when nothing is driving it.                                                                                                                                                                                                   |

|                                                        | RxDC0E    | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                                                                                                                                                                             |

|                                                        | U1C0_DX0F | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                          |

|                                                        | U1C0_DX2C | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                                                                       |

|                                                        | U1C1_DX0C | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                                          |

|                                                        | U1C1_DX2B | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                                                                                                       |

|                                                        | U2C1_DX2C | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                                                                                                       |

| Table 5         Pin Definitions and Functions (cont'd) |                   |        |      |                                                                                                                                                                                                                                                                            |  |

|--------------------------------------------------------|-------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                                                    | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                   |  |

| 143                                                    | P8.5              | O0 / I | St/B | Bit 5 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                              |  |

|                                                        | CCU60_COU<br>T62  | O1     | St/B | CCU60 Channel 2 Output                                                                                                                                                                                                                                                     |  |

|                                                        | CCU62_CC6<br>2    | O2     | St/B | CCU62 Channel 2 Output                                                                                                                                                                                                                                                     |  |

|                                                        | TCK_D             | IH     | St/B | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. D is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.                                                                                                           |  |

|                                                        | CCU62_CC6<br>2INB | I      | St/B | CCU62 Channel 2 Input                                                                                                                                                                                                                                                      |  |

| 15                                                     | V <sub>DDIM</sub> | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.                                                                                                                                                       |  |

| 54,<br>91,<br>127                                      | V <sub>DDI1</sub> | -      | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All $V_{\text{DDI1}}$ pins must be connected to each other.                                                                                        |  |

| 20                                                     | V <sub>DDPA</sub> | -      | PS/A | Digital Pad Supply Voltage for Domain A<br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The A/D_Converters and ports P5, P6 and<br>P15 are fed from supply voltage $V_{\text{DDPA}}$ . |  |

#### **Functional Description**

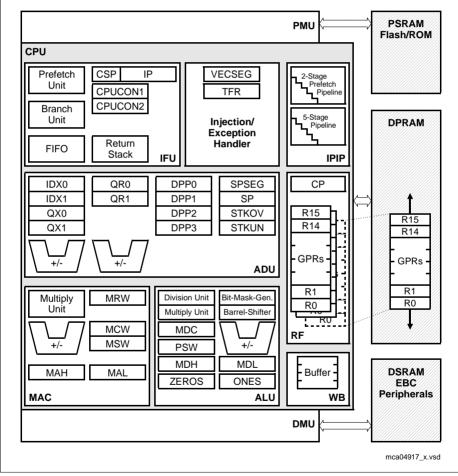

## 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

#### **Functional Description**

## 3.16 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.42 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

### 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XE167xM from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

#### **Functional Description**

### 3.18 Parallel Ports

The XE167xM provides up to 119 I/O lines which are organized into 11 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in Table 9.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

| Port | Width | I/O | Connected Modules                                                               |

|------|-------|-----|---------------------------------------------------------------------------------|

| P0   | 8     | I/O | EBC (A7A0),<br>CCU6, USIC, CAN                                                  |

| P1   | 8     | I/O | EBC (A15A8),<br>CCU6, USIC                                                      |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13),<br>CAN, CC2, GPT12E, USIC, DAP/JTAG |

| P3   | 8     | I/O | CAN, USIC                                                                       |

| P4   | 8     | I/O | EBC (CS3CS0),<br>CC2, CAN, GPT12E, USIC                                         |

| P5   | 16    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                      |

| P6   | 4     | I/O | ADC, CAN, GPT12E                                                                |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                     |

| P8   | 7     | I/O | CCU6, DAP/JTAG, USIC                                                            |

| P9   | 8     | I/O | CCU6, DAP/JTAG, CAN                                                             |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0),<br>CCU6, USIC, DAP/JTAG, CAN                 |

| P11  | 6     | I/O | CCU6, USIC, CAN                                                                 |

| P15  | 8     | Ι   | Analog Inputs, GPT12E                                                           |

#### Table 9Summary of the XE167xM's Ports

2) The pad supply voltage pins (V<sub>DDPB</sub>) provide the input current for the on-chip EVVRs and the current consumed by the pin output drivers. A small current is consumed because the drivers input stages are switched.

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to  $3 + 0.6 \text{ x} f_{SYS}$ .

3) Please consider the additional conditions described in section "Active Mode Power Supply Current".

#### Active Mode Power Supply Current

The actual power supply current in active mode not only depends on the system frequency but also on the configuration of the XE167xM's subsystem.

Besides the power consumed by the device logic the power supply pins also provide the current that flows through the pin output drivers.

A small current is consumed because the drivers' input stages are switched.

The IO power domains can be supplied separately. Power domain A ( $V_{\rm DDPA}$ ) supplies the A/D converters and Port 6. Power domain B ( $V_{\rm DDPB}$ ) supplies the on-chip EVVRs and all other ports.

During operation domain A draws a maximum current of 1.5 mA for each active A/D converter module from  $V_{\rm DDPA}$ .

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to  $(3 + 0.6 \times f_{SYS})$  mA.

#### Table 17ADC Parameters (cont'd)

| Parameter                                                  | Symbol               |                                                          | Values                                          |                             | Unit | Note /         |

|------------------------------------------------------------|----------------------|----------------------------------------------------------|-------------------------------------------------|-----------------------------|------|----------------|

|                                                            |                      | Min.                                                     | Тур.                                            | Max.                        |      | Test Condition |

| Broken wire detection delay against VAGND <sup>2)</sup>    | t <sub>BWG</sub> CC  | -                                                        | -                                               | 50                          | 3)   |                |

| Broken wire detection delay against VAREF <sup>2)</sup>    | t <sub>BWR</sub> CC  | -                                                        | -                                               | 50                          | 4)   |                |

| Conversion time for 8-bit result <sup>2)</sup>             | t <sub>c8</sub> CC   | (11 + STC) x t <sub>ADCI</sub><br>+ 2 x t <sub>SYS</sub> |                                                 |                             |      |                |

| Conversion time for 10-bit result <sup>2)</sup>            |                      |                                                          | $(13 + STC) \times t_{ADCI}$<br>+ 2 x $t_{SYS}$ |                             |      |                |

| Total Unadjusted Error                                     | TUE <br>CC           | -                                                        | 1                                               | 2                           | LSB  | 5)             |

| Wakeup time from analog powerdown, fast mode <sup>2)</sup> | t <sub>WAF</sub> CC  | -                                                        | -                                               | 4                           | μS   |                |

| Wakeup time from analog powerdown, slow mode <sup>2)</sup> | t <sub>WAS</sub> CC  | -                                                        | -                                               | 15                          | μS   |                |

| Analog reference ground                                    | $V_{AGND}$ SR        | V <sub>SS</sub><br>- 0.05                                | -                                               | 1.5                         | V    |                |

| Analog input voltage range                                 | $V_{\rm AIN}{ m SR}$ | $V_{AGND}$                                               | -                                               | $V_{AREF}$                  | V    | 6)             |

| Analog reference voltage                                   | $V_{AREF}$ SR        | V <sub>AGND</sub><br>+ 1.0                               | -                                               | V <sub>DDPA</sub><br>+ 0.05 | V    | 5)             |

These parameter values cover the complete operating range. Under relaxed operating conditions (room temperature, nominal supply voltage) the typical values can be used for calculation.

2) This parameter includes the sample time (also the additional sample time specified by STC), the time to determine the digital result and the time to load the result register with the conversion result. Values for the basic clock t<sub>ADCI</sub> depend on programming.

- 3) The broken wire detection delay against  $V_{AGND}$  is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 500 µs. Result below 10% (66<sub>H</sub>).

- 4) The broken wire detection delay against V<sub>AREF</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 10 μs. This function is influenced by leakage current, in particular at high temperature. Result above 80% (332<sub>H</sub>).

- 5) TUE is tested at V<sub>AREF</sub> = V<sub>DDPA</sub> = 5.0 V, V<sub>AGND</sub> = 0 V. It is verified by design for all other voltages within the defined voltage range. The specified TUE is valid only if the absolute sum of input overload currents on analog port pins (see I<sub>OV</sub> specification) does not exceed 10 mA, and if V<sub>AREF</sub> and V<sub>AGND</sub> remain stable during the measurement time.

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

**Electrical Parameters**

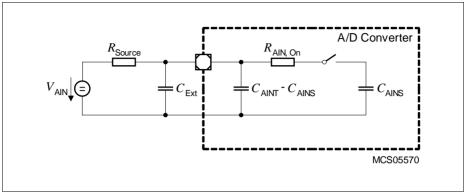

Figure 16 Equivalent Circuitry for Analog Inputs

Sample time and conversion time of the XE167xM's A/D converters are programmable. The timing above can be calculated using **Table 18**.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

| GLOBCTR.5-0<br>(DIVA) | A/D Converter<br>Analog Clock $f_{\text{ADCI}}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup><br>t <sub>s</sub> |

|-----------------------|-------------------------------------------------|---------------------|---------------------------------------------|

| 000000 <sub>B</sub>   | f <sub>SYS</sub>                                | 00 <sub>H</sub>     | $t_{ADCI} \times 2$                         |

| 000001 <sub>B</sub>   | f <sub>SYS</sub> / 2                            | 01 <sub>H</sub>     | $t_{\sf ADCI} 	imes {f 3}$                  |

| 000010 <sub>B</sub>   | f <sub>SYS</sub> / 3                            | 02 <sub>H</sub>     | $t_{ADCI} \times 4$                         |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                        | :                   | $t_{ADCI} \times (STC+2)$                   |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                           | FE <sub>H</sub>     | $t_{\rm ADCI} 	imes 256$                    |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                           | FF <sub>H</sub>     | $t_{\rm ADCI} 	imes 257$                    |

Table 18

A/D Converter Computation Table

1) The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

### **Converter Timing Example A:**

| Assumptions:          | $f_{\rm SYS}$    | = 80 MHz (i.e. $t_{SYS}$ = 12.5 ns), DIVA = 03 <sub>H</sub> , STC = 00 <sub>H</sub>             |

|-----------------------|------------------|-------------------------------------------------------------------------------------------------|

| Analog clock          | $f_{\rm ADCI}$   | $= f_{SYS} / 4 = 20 \text{ MHz}$ , i.e. $t_{ADCI} = 50 \text{ ns}$                              |

| Sample time           | t <sub>S</sub>   | $= t_{ADCI} \times 2 = 100 \text{ ns}$                                                          |

| Conversion 10-        | bit:             |                                                                                                 |

|                       | t <sub>C10</sub> | = $13 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $13 \times 50$ ns + $2 \times 12.5$ ns = 0.675 µs |

| <b>Conversion 8-b</b> | it:              |                                                                                                 |

|                       | t <sub>C8</sub>  | = $11 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $11 \times 50$ ns + $2 \times 12.5$ ns = 0.575 µs |

#### **Converter Timing Example B:**

| Assumptions:          | $f_{\rm SYS}$           | = 40 MHz (i.e. $t_{SYS}$ = 25 ns), DIVA = 02 <sub>H</sub> , STC = 03 <sub>H</sub> |

|-----------------------|-------------------------|-----------------------------------------------------------------------------------|

| Analog clock          | $f_{\rm ADCI}$          | $= f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e. $t_{ADCI} = 75 \text{ ns}$              |

| Sample time           | t <sub>S</sub>          | $= t_{ADCI} \times 5 = 375 \text{ ns}$                                            |

| <b>Conversion 10-</b> | bit:                    |                                                                                   |

|                       | <i>t</i> <sub>C10</sub> | = $16 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 16 × 75 ns + 2 × 25 ns = 1.25 µs         |

| <b>Conversion 8-b</b> | it:                     |                                                                                   |

|                       | t <sub>C8</sub>         | = $14 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 14 × 75 ns + 2 × 25 ns = 1.10 µs         |

|                       |                         |                                                                                   |

### **Direct Drive**

When direct drive operation is selected (SYSCON0.CLKSEL =  $11_B$ ), the system clock is derived directly from the input clock signal CLKIN1:

$f_{SYS} = f_{IN}$ .

The frequency of  $f_{SYS}$  is the same as the frequency of  $f_{IN}$ . In this case the high and low times of  $f_{SYS}$  are determined by the duty cycle of the input clock  $f_{IN}$ .

Selecting Bypass Operation from the XTAL1<sup>1)</sup> input and using a divider factor of 1 results in a similar configuration.

### **Prescaler Operation**

When prescaler operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $1_B$ ), the system clock is derived either from the crystal oscillator (input clock signal XTAL1) or from the internal clock source through the output prescaler K1 (= K1DIV+1):

$f_{\text{SYS}} = f_{\text{OSC}} / \text{K1}.$

If a divider factor of 1 is selected, the frequency of  $f_{\rm SYS}$  equals the frequency of  $f_{\rm OSC}$ . In this case the high and low times of  $f_{\rm SYS}$  are determined by the duty cycle of the input clock  $f_{\rm OSC}$  (external or internal).

The lowest system clock frequency results from selecting the maximum value for the divider factor K1:

$f_{\rm SYS} = f_{\rm OSC} / 1024.$

## 4.6.2.1 Phase Locked Loop (PLL)

When PLL operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $0_B$ ), the on-chip phase locked loop is enabled and provides the system clock. The PLL multiplies the input frequency by the factor **F** ( $f_{SYS} = f_{IN} \times F$ ).

**F** is calculated from the input divider P (= PDIV+1), the multiplication factor N (= NDIV+1), and the output divider K2 (= K2DIV+1):

$(F = N / (P \times K2)).$

The input clock can be derived either from an external source at XTAL1 or from the onchip clock source.

The PLL circuit synchronizes the system clock to the input clock. This synchronization is performed smoothly so that the system clock frequency does not change abruptly.

Adjustment to the input clock continuously changes the frequency of  $f_{\text{SYS}}$  so that it is locked to  $f_{\text{IN}}$ . The slight variation causes a jitter of  $f_{\text{SYS}}$  which in turn affects the duration of individual TCSs.

<sup>1)</sup> Voltages on XTAL1 must comply to the core supply voltage  $V_{\text{DDIM}}$ .

### PLL frequency band selection

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

| Parameter                                  | Symbol                |      | Values | 5    | Unit | Note /          |

|--------------------------------------------|-----------------------|------|--------|------|------|-----------------|

|                                            |                       | Min. | Тур.   | Max. |      | Test Condition  |

| VCO output frequency                       | $f_{\rm VCO}{\rm CC}$ | 50   | -      | 110  | MHz  | $VCOSEL = 00_B$ |

| (VCO controlled)                           |                       | 100  | _      | 160  | MHz  | $VCOSEL = 01_B$ |

| VCO output frequency<br>(VCO free-running) | $f_{\rm VCO}{\rm CC}$ | 10   | -      | 40   | MHz  | $VCOSEL = 00_B$ |

|                                            |                       | 20   | -      | 80   | MHz  | $VCOSEL = 01_B$ |

### Table 23 System PLL Parameters

### 4.6.2.2 Wakeup Clock

When wakeup operation is selected (SYSCON0.CLKSEL =  $00_B$ ), the system clock is derived from the low-frequency wakeup clock source:

$f_{SYS} = f_{WU}$ .

In this mode, a basic functionality can be maintained without requiring an external clock source and while minimizing the power consumption.

## 4.6.2.3 Selecting and Changing the Operating Frequency

When selecting a clock source and the clock generation method, the required parameters must be carefully written to the respective bit fields, to avoid unintended intermediate states.

Many applications change the frequency of the system clock ( $f_{SYS}$ ) during operation in order to optimize system performance and power consumption. Changing the operating frequency also changes the switching currents, which influences the power supply.

To ensure proper operation of the on-chip EVRs while they generate the core voltage, the operating frequency shall only be changed in certain steps. This prevents overshoots and undershoots of the supply voltage.

To avoid the indicated problems, recommended sequences are provided which ensure the intended operation of the clock system interacting with the power system. Please refer to the Programmer's Guide.

## 4.6.6 Synchronous Serial Interface Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

| Parameter                                                               | Symbol            | Values                                       |      |      | Unit | Note /         |

|-------------------------------------------------------------------------|-------------------|----------------------------------------------|------|------|------|----------------|

|                                                                         |                   | Min.                                         | Тур. | Max. | 1    | Test Condition |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC | <i>t</i> <sub>SYS</sub><br>- 8 <sup>1)</sup> | -    | -    | ns   |                |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC | <i>t</i> <sub>SYS</sub><br>- 6 <sup>1)</sup> | _    | -    | ns   |                |

| Data output DOUT valid time                                             | t <sub>3</sub> CC | -6                                           | -    | 9    | ns   |                |

| Receive data input setup time to SCLKOUT receive edge                   | t <sub>4</sub> SR | 31                                           | -    | -    | ns   |                |

| Data input DX0 hold time<br>from SCLKOUT receive<br>edge                | t <sub>5</sub> SR | -4                                           | -    | -    | ns   |                |

### Table 33 USIC SSC Master Mode Timing for Upper Voltage Range

1)  $t_{SYS} = 1 / f_{SYS}$

### Table 34 USIC SSC Master Mode Timing for Lower Voltage Range

| Parameter                                                               | Symbol            | Values                                        |      |      | Unit | Note /         |

|-------------------------------------------------------------------------|-------------------|-----------------------------------------------|------|------|------|----------------|

|                                                                         |                   | Min.                                          | Тур. | Max. |      | Test Condition |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC | <i>t</i> <sub>SYS</sub><br>- 10 <sup>1)</sup> | -    | -    | ns   |                |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC | <i>t</i> <sub>SYS</sub><br>- 9 <sup>1)</sup>  | -    | -    | ns   |                |

| Data output DOUT valid<br>time                                          | t <sub>3</sub> CC | -7                                            | _    | 11   | ns   |                |

#### Package and Reliability

# 5 Package and Reliability

The XE166 Family devices use the package type PG-LQFP (Plastic Green - Low Profile Quad Flat Package). The following specifications must be regarded to ensure proper integration of the XE167xM in its target environment.

### 5.1 Packaging

These parameters specify the packaging rather than the silicon.

| Parameter             | Symbol           | Lin  | nit Values    | Unit | Notes                         |

|-----------------------|------------------|------|---------------|------|-------------------------------|

|                       |                  | Min. | Max.          |      |                               |

| Exposed Pad Dimension | $E x \times E y$ | _    | 6.5 	imes 6.5 | mm   | -                             |

| Power Dissipation     | $P_{DISS}$       | _    | 1.0           | W    | -                             |

| Thermal resistance    | $R_{\Theta JA}$  | _    | 43            | K/W  | No thermal via <sup>1)</sup>  |

| Junction-Ambient      |                  |      | 34            | K/W  | 4-layer, no pad <sup>2)</sup> |

|                       |                  |      | 21            | K/W  | 4-layer, pad <sup>3)</sup>    |

Table 41

Package Parameters (PG-LQFP-144-13)

1) Device mounted on a 2-layer JEDEC board (according to JESD 51-3) or a 4-layer board without thermal vias; exposed pad not soldered.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad not soldered.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad soldered to the board.

Note: To improve the EMC behavior, it is recommended to connect the exposed pad to the board ground, independent of the thermal requirements. Board layout examples are given in an application note.

### Package Compatibility Considerations

The XE167xM is a member of the XE166 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In particular, the size of the Exposed Pad (if present) may vary.

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.