# E·XFL

# XMOS - XS1-U8A-64-FB96-C5 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | XCore                                                        |

| Core Size                  | 32-Bit 8-Core                                                |

| Speed                      | 500MIPS                                                      |

| Connectivity               | Configurable                                                 |

| Peripherals                | -                                                            |

| Number of I/O              | 38                                                           |

| Program Memory Size        | 64KB (16K x 32)                                              |

| Program Memory Type        | SRAM                                                         |

| EEPROM Size                | -                                                            |

| RAM Size                   | -                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                    |

| Data Converters            | A/D 4x12b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 96-LFBGA                                                     |

| Supplier Device Package    | 96-FBGA (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-u8a-64-fb96-c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 xCORE Multicore Microcontrollers

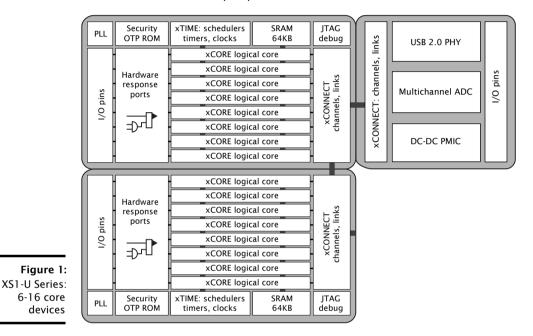

The XS1-U Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

Key features of the XS1-U8A-64-FB96 include:

- Tiles: Devices consist of one or more xCORE tiles. Each tile contains between four and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 7.1

- ▶ **xTIME scheduler** The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 7.2

| Signal | Function                        |                   | Туре | Properties |

|--------|---------------------------------|-------------------|------|------------|

| X0D50  | XLC <sup>3</sup> <sub>out</sub> | 32A <sup>1</sup>  | I/0  | PDs        |

| X0D51  | XLC <sup>2</sup> <sub>out</sub> | 32A <sup>2</sup>  | I/0  | PDs        |

| X0D52  | XLC <sup>1</sup>                | 32A <sup>3</sup>  | I/0  | PDs        |

| X0D53  | XLC <sup>0</sup> <sub>out</sub> | 32A <sup>4</sup>  | I/O  | PDs        |

| X0D54  | XLC <sup>0</sup> <sub>in</sub>  | 32A <sup>5</sup>  | I/0  | PDs        |

| X0D55  | XLC <sup>1</sup>                | 32A <sup>6</sup>  | I/0  | PDs        |

| X0D56  | XLC <sup>2</sup> <sub>in</sub>  | 32A <sup>7</sup>  | I/0  | PDs        |

| X0D57  | XLC <sup>3</sup>                | 32A <sup>8</sup>  | I/O  | PDs        |

| X0D58  | XLC <sup>4</sup>                | 32A <sup>9</sup>  | I/O  | PDs        |

| X0D61  | XLD <sup>4</sup> <sub>out</sub> | 32A <sup>10</sup> | I/O  | PDs        |

| X0D62  | XLD <sup>3</sup> <sub>out</sub> | 32A <sup>11</sup> | I/0  | PDs        |

| X0D63  | XLD <sup>2</sup> <sub>out</sub> | 32A <sup>12</sup> | I/0  | PDs        |

| X0D64  | XLD <sup>1</sup> <sub>out</sub> | 32A <sup>13</sup> | I/0  | PDs        |

| X0D65  | XLD <sup>0</sup> <sub>out</sub> | 32A <sup>14</sup> | I/0  | PDs        |

| X0D66  | XLD <sup>0</sup> <sub>in</sub>  | 32A <sup>15</sup> | I/0  | PDs        |

| X0D67  | XLD <sup>1</sup>                | 32A <sup>16</sup> | I/O  | PDs        |

| X0D68  | XLD <sup>2</sup> <sub>in</sub>  | 32A <sup>17</sup> | I/O  | PDs        |

| X0D69  | XLD <sup>3</sup> <sub>in</sub>  | 32A <sup>18</sup> | I/O  | PDs        |

| X0D70  | XLD <sup>4</sup> <sub>in</sub>  | 32A <sup>19</sup> | I/O  | PDs        |

#### 9.3 Boot from OTP

If an xCORE tile is set to use secure boot (see Figure 9), the boot image is read from address 0 of the OTP memory in the tile's security module.

This feature can be used to implement a secure bootloader which loads an encrypted image from external flash, decrypts and CRC checks it with the processor, and discontinues the boot process if the decryption or CRC check fails. XMOS provides a default secure bootloader that can be written to the OTP along with secret decryption keys.

Each tile has its own individual OTP memory, and hence some tiles can be booted from OTP while others are booted from SPI or the channel interface. This enables systems to be partially programmed, dedicating one or more tiles to perform a particular function, leaving the other tiles user-programmable.

#### 9.4 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 12 provide a strong level of protection and are sufficient for providing strong IP security.

| Feature              | Bit  | Description                                                                                                                                                                                                                                |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible<br>for the tile state or memory content to be accessed<br>via the JTAG interface.                                                                                                     |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state<br>via the system switch. Disabling both JTAG and Link<br>access transforms an xCORE Tile into a "secure island"<br>with other tiles free for non-secure user application<br>code. |

| Secure Boot          | 5    | The processor is forced to boot from address 0 of the OTP, allowing the processor boot ROM to be bypassed ( <i>see</i> §9).                                                                                                                |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                             |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                                       |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                                       |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                                       |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                                       |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables up-<br>dates to all sectors and security register.                                                                                                                                            |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG inter-<br>face to this OTP.                                                                                                                                                                |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                                        |

|                      | 2115 | General purpose software accessable security register available to end-users.                                                                                                                                                              |

|                      | 3122 | General purpose user programmable JTAG UserID code extension.                                                                                                                                                                              |

$-X \Lambda ()S$

Figure 12: Security register features

reset was due to the watchdog. The watchdog timer is only enabled and clocked whilst the processor is in the AWAKE power state.

## 14 Energy management

XS1-U8A-64-FB96 devices can be powered by:

- An external 5v core and 3.3v I/O supply, increasing efficiency for USB bus powered applications.

- ► A single 3.3v supply.

#### 14.1 DC-DC

XS1-U8A-64-FB96 devices include two DC-DC buck converters which can be configured to take input voltages between 3.3-5V power supply and output circuit voltages (nominally 1.8V and 1.0V) required by the analog peripherals and digital node.

#### 14.2 Power mode controller

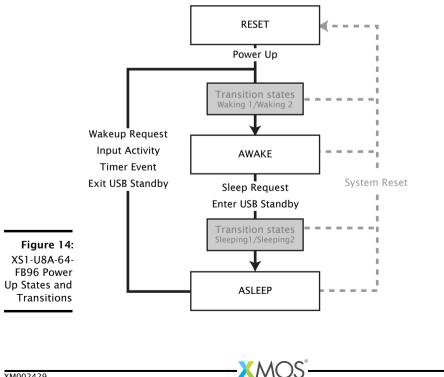

The device transitions through multiple states during the power-up and powerdown process.

22

The SW output pin must have an LC filter on the output with a 4.7uH inductor and 22uF X5R capacitor. The capacitor must have maximum ESR value of 0.015R, and the inductor should have a maximum DCR value of 0.07R, to meet the efficiency specifications of the DC-DC converter, although this requirement may be relaxed if a drop in efficiency is acceptable. A list of suggested inductors is in Figure 19.

|                   |        | Part number       | Current | Max DCR         | Package      |

|-------------------|--------|-------------------|---------|-----------------|--------------|

|                   | Yuden  | CBC2518T4R7M      | 680 mA  | $260 \ m\Omega$ | 2518 (1007)  |

|                   | TDK    | NLCV32T-4R7M-PFR  | 620 mA  | 200 $m\Omega$   | 3225 (1210)  |

|                   | Murata | LQM2HPN4R7MGC     | 800 mA  | 225 $m\Omega$   | 2520 (1008)  |

| Figure 19:        | Sumida | 0420CDMCBDS-4R7MC | 3400 mA | <b>80</b> mΩ    | 4.7 x 4.3 mm |

| Example 4.7       | Wurth  | 744043004         | 1550 mA | 70 $m\Omega$    | 4.8 x 4.8 mm |

| $\mu$ H inductors | Murata | LQH55DN4R7M03L    | 2700 mA | 57 $m\Omega$    | 5750 (2220)  |

The traces from the SW output pins to the inductor and from the output capacitor back to the VDD pins must be routed to minimize the coupling between them.

The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDDIO supply to the XS1-U8A-64-FB96 requires a 100nF X5R or X7R ceramic decoupling capacitor placed as close as possible to the supply pins.

If the ADC Is used, it requires a 100nF X5R or X7R ceramic decoupling capacitor placed as close as possible to the AVDD pin. Care should be taken to minimize noise on these inputs, and if necessary an extra 10uF decoupling capacitor and ferrite bead can be used to remove noise from this supply.

The crystal oscillator requires careful routing of the XI / XO nodes as these are high impedance and very noise sensitive. Hence, the traces should be as wide and short as possible, and routed over a continuous ground plane. They should not be routed near noisy supply lines or clocks. The device has a load capacitance of 18pF for the crystal. Care must be taken, so that the inductance and resistance of the ground returns from the capacitors to the ground of the device is minimized.

#### 16.1 USB connections

USB\_VBUS should be connected to the VBUS pin of the USB connector. A 2.2 uF capacitor to ground is required on the VBUS pin. A ferrite bead may be used to reduce HF noise.

For self-powered systems, a bleeder resistor may be required to stop VBUS from floating when no USB cable is attached.

USB\_DP and USB\_DN should be connected to the USB connector. USB\_ID does not need to be connected.

# **B** Processor Status Configuration

The processor status control registers can be accessed directly by the processor using processor status reads and writes (use getps(reg) and setps(reg,value) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RW   | RAM base address                      |

| 0x01      | RW   | Vector base address                   |

| 0x02      | RW   | xCORE Tile control                    |

| 0x03      | RO   | xCORE Tile boot status                |

| 0x05      | RO   | Security configuration                |

| 0x06      | RW   | Ring Oscillator Control               |

| 0x07      | RO   | Ring Oscillator Value                 |

| 0x08      | RO   | Ring Oscillator Value                 |

| 0x09      | RO   | Ring Oscillator Value                 |

| 0x0A      | RO   | Ring Oscillator Value                 |

| 0x10      | DRW  | Debug SSR                             |

| 0x11      | DRW  | Debug SPC                             |

| 0x12      | DRW  | Debug SSP                             |

| 0x13      | DRW  | DGETREG operand 1                     |

| 0x14      | DRW  | DGETREG operand 2                     |

| 0x15      | DRW  | Debug interrupt type                  |

| 0x16      | DRW  | Debug interrupt data                  |

| 0x18      | DRW  | Debug core control                    |

| 0x20 0x27 | DRW  | Debug scratch                         |

| 0x30 0x33 | DRW  | Instruction breakpoint address        |

| 0x40 0x43 | DRW  | Instruction breakpoint control        |

| 0x50 0x53 | DRW  | Data watchpoint address 1             |

| 0x60 0x63 | DRW  | Data watchpoint address 2             |

| 0x70 0x73 | DRW  | Data breakpoint control register      |

| 0x80 0x83 | DRW  | Resources breakpoint mask             |

| 0x90 0x93 | DRW  | Resources breakpoint value            |

| 0x9C 0x9F | DRW  | Resources breakpoint control register |

-XMOS<sup>®</sup>

Figure 44: Summary

#### B.1 RAM base address: 0x00

This register contains the base address of the RAM. It is initialized to 0x00010000.

**0x00**: RAM base address

| 00: | Bits | Perm | Init | Description                                |

|-----|------|------|------|--------------------------------------------|

| ise | 31:2 | RW   |      | Most significant 16 bits of all addresses. |

| ess | 1:0  | RO   | -    | Reserved                                   |

#### B.2 Vector base address: 0x01

Base address of event vectors in each resource. On an interrupt or event, the 16 most significant bits of the destination address are provided by this register; the least significant 16 bits come from the event vector.

0x01: Vector base address

| - | Bits  | Perm | Init | Description                                                    |

|---|-------|------|------|----------------------------------------------------------------|

| e | 31:16 | RW   |      | The most significant bits for all event and interrupt vectors. |

| S | 15:0  | RO   | -    | Reserved                                                       |

## B.3 xCORE Tile control: 0x02

Register to control features in the xCORE tile

| Bits | Perm | Init | Description                                                                                                                                                                                                                                             |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:6 | RO   | -    | Reserved                                                                                                                                                                                                                                                |

| 5    | RW   | 0    | Set to 1 to select the dynamic mode for the clock divider when<br>the clock divider is enabled. In dynamic mode the clock divider is<br>only activated when all active logical cores are paused. In static<br>mode the clock divider is always enabled. |

| 4    | RW   | 0    | Set to 1 to enable the clock divider. This slows down the xCORE tile clock in order to use less power.                                                                                                                                                  |

| 3:0  | RO   | -    | Reserved                                                                                                                                                                                                                                                |

0x02: xCORE Tile control

# B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

| Bits  | Perm | Init | Description                                                                        |

|-------|------|------|------------------------------------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                                           |

| 23:16 | RO   |      | xCORE tile number on the switch.                                                   |

| 15:9  | RO   | -    | Reserved                                                                           |

| 8     | RO   |      | Set to 1 if boot from OTP is enabled.                                              |

| 7:0   | RO   |      | The boot mode pins MODE0, MODE1,, specifying the boot frequency, boot source, etc. |

0x03: xCORE Tile boot status

## **B.5** Security configuration: 0x05

Copy of the security register as read from OTP.

0x05: Security configuration

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

# B.6 Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator is stopped. The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06** Ring Oscillator Control

| -       | Bits | Perm | Init | Description                                        |

|---------|------|------|------|----------------------------------------------------|

| 6:      | 31:2 | RO   | -    | Reserved                                           |

| g<br>or | 1    | RW   | 0    | Set to 1 to enable the xCORE tile ring oscillators |

| ol      | 0    | RW   | 0    | Set to 1 to enable the peripheral ring oscillators |

# B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

**0x07:** Ring Oscillator Value

| Bits  | Perm | Init | Description                   |

|-------|------|------|-------------------------------|

| 31:16 | RO   | -    | Reserved                      |

| 15:0  | RO   | -    | Ring oscillator counter data. |

#### B.19 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over JTAG. This is the same set of registers as the Debug Scratch registers in the xCORE tile configuration.

0x20 .. 0x27: Debug scratch

| 0x27:<br>ebug | Bits | Perm | Init | Description |

|---------------|------|------|------|-------------|

| ratch         | 31:0 | DRW  |      | Value.      |

#### B.20 Instruction breakpoint address: 0x30 .. 0x33

This register contains the address of the instruction breakpoint. If the PC matches this address, then a debug interrupt will be taken. There are four instruction breakpoints that are controlled individually.

0x30 .. 0x33: Instruction breakpoint address

| ction |      |      |      |             |

|-------|------|------|------|-------------|

| point | Bits | Perm | Init | Description |

| dress | 31:0 | DRW  |      | Value.      |

## B.21 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

| Bits  | Perm | Init | Description                                                                                                                                                                                 |  |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:24 | RO   | -    | Reserved                                                                                                                                                                                    |  |

| 23:16 | DRW  | 0    | bit for each logical core in the tile allowing the breakpoint to e nabled individually for each logical core.                                                                               |  |

| 15:2  | RO   | -    | Reserved                                                                                                                                                                                    |  |

| 1     | DRW  | 0    | Set to 1 to cause an instruction breakpoint if the PC is not<br>equal to the breakpoint address. By default, the breakpoint is<br>triggered when the PC is equal to the breakpoint address. |  |

| 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                               |  |

0x40 .. 0x43: Instruction breakpoint control

## B.22 Data watchpoint address 1: 0x50 ... 0x53

This set of registers contains the first address for the four data watchpoints.

# C xCORE Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                                    |  |

|-----------|------|------------------------------------------------|--|

| 0x00      | RO   | Device identification                          |  |

| 0x01      | RO   | xCORE Tile description 1                       |  |

| 0x02      | RO   | xCORE Tile description 2                       |  |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |  |

| 0x05      | CRW  | Cause debug interrupts                         |  |

| 0x06      | RW   | xCORE Tile clock divider                       |  |

| 0x07      | RO   | Security configuration                         |  |

| 0x10 0x13 | RO   | PLink status                                   |  |

| 0x20 0x27 | CRW  | Debug scratch                                  |  |

| 0x40      | RO   | PC of logical core 0                           |  |

| 0x41      | RO   | PC of logical core 1                           |  |

| 0x42      | RO   | PC of logical core 2                           |  |

| 0x43      | RO   | PC of logical core 3                           |  |

| 0x44      | RO   | PC of logical core 4                           |  |

| 0x45      | RO   | PC of logical core 5                           |  |

| 0x46      | RO   | PC of logical core 6                           |  |

| 0x47      | RO   | RO PC of logical core 7                        |  |

| 0x60      | RO   | SR of logical core 0                           |  |

| 0x61      | RO   | SR of logical core 1                           |  |

| 0x62      | RO   | SR of logical core 2                           |  |

| 0x63      | RO   | SR of logical core 3                           |  |

| 0x64      | RO   | SR of logical core 4                           |  |

| 0x65      | RO   | SR of logical core 5                           |  |

| 0x66      | RO   | SR of logical core 6                           |  |

| 0x67      | RO   | SR of logical core 7                           |  |

| 0x80 0x9F | RO   | Chanend status                                 |  |

Figure 45: Summary

#### C.1 Device identification: 0x00

| 0x00:          |

|----------------|

| Device         |

| identification |

description

| Bits  | Perm | Init | Description                                             |

|-------|------|------|---------------------------------------------------------|

| 31:24 | RO   |      | Processor ID of this xCORE tile.                        |

| 23:16 | RO   |      | Number of the node in which this xCORE tile is located. |

| 15:8  | RO   |      | xCORE tile revision.                                    |

| 7:0   | RO   |      | xCORE tile version.                                     |

# C.2 xCORE Tile description 1: 0x01

Bits Perm Init Description

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

|               |       | -  |   |                          |

|---------------|-------|----|---|--------------------------|

|               | 31:24 | RO |   | Number of channel ends.  |

| 0x01:         | 23:16 | RO |   | Number of locks.         |

| xCORE Tile    | 15:8  | RO |   | Number of synchronisers. |

| description 1 | 7:0   | RO | - | Reserved                 |

|               |       |    |   |                          |

## C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02: xCORE Tile description 2

| Bits  | Perm | Init | Description             |

|-------|------|------|-------------------------|

| 31:16 | RO   | -    | Reserved                |

| 15:8  | RO   |      | Number of clock blocks. |

| 7:0   | RO   |      | Number of timers.       |

## C.4 Control PSwitch permissions to debug registers: 0x04

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

| 0x04:         |

|---------------|

| Node          |

| configuration |

| register      |

| Bits | Perm | Init | Description                                                                                          |

|------|------|------|------------------------------------------------------------------------------------------------------|

| 31   | RW   | 0    | Set to 1 to disable further updates to the node configuration and link control and status registers. |

| 30:1 | RO   | -    | Reserved                                                                                             |

| 0    | RW   | 0    | Header mode. 0: 3-byte headers; 1: 1-byte headers.                                                   |

#### E.3 Node identifier: 0x05

| 0x05      |  |

|-----------|--|

|           |  |

| Node      |  |

| identifie |  |

|         | Bits  | Perm | Init | Description                                                                                               |

|---------|-------|------|------|-----------------------------------------------------------------------------------------------------------|

| 5:      | 31:16 | RO   | -    | Reserved                                                                                                  |

| e<br>er | 15:0  | RW   | 0    | 16-bit node identifier. This does not need to be set, and is present for compatibility with XS1-switches. |

#### E.4 Reset and Mode Control: 0x50

The XS1-S has two main reset signals: a system-reset and an xCORE Tile-reset. System-reset resets the whole system including external devices, whilst xCORE Tile-reset resets the xCORE Tile(s) only. The resets are induced either by software (by a write to the register below) or by one of the following:

- \* External reset on RST\_N (System reset)

- \* Brown out on one of the power supplies (System reset)

- \* Watchdog timer (System reset)

- \* Sleep sequence (xCORE Tile reset)

- \* Clock source change (xCORE Tile reset)

The minimum system reset duration is achieved when the fastest permissible clock is used. The reset durations will be proportionately longer when a slower clock is used. Note that the minimum system reset duration allows for all power rails except the VOUT2 to turn off, and decay.

The length of the system reset comes from an internal counter, counting 524,288 oscillator clock cycles which gives the maximum time allowable for the supply rails to discharge. The system reset duration is a balance between leaving a long time for the supply rails to discharge, and a short time for the system to boot. Example reset times are 44 ms with a 12 MHz oscillator or 5.5 ms with a 96 MHz oscillator.

| Bits | Perm | Init | Description                                        |

|------|------|------|----------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                           |

| 7    | RW   | 0    | Set to 1 to switch UIFM to EXTVBUSIND mode.        |

| 6    | RW   | 0    | Set to 1 to switch UIFM to DRVVBUSEXT mode.        |

| 5    | RO   | -    | Reserved                                           |

| 4    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ CHRGVBUS mode.    |

| 3    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DISCHRGVBUS mode. |

| 2    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DMPULLDOWN mode.  |

| 1    | RW   | 0    | Set to 1 to switch UIFM to UTMI+ DPPULLDOWN mode.  |

| 0    | RW   | 0    | Set to 1 to switch UIFM to IDPULLUP mode.          |

**0x10:** UIFM on-the-go control

# F.6 UIFM on-the-go flags: 0x14

Status flags used for on-the-go negotiation

|   | Bits | Perm | Init | Description                  |

|---|------|------|------|------------------------------|

| 3 | 31:6 | RO   | -    | Reserved                     |

|   | 5    | RO   | 0    | Value of UTMI+ Bvalid flag.  |

|   | 4    | RO   | 0    | Value of UTMI+ IDGND flag.   |

|   | 3    | RO   | 0    | Value of UTMI+ HOSTDIS flag. |

|   | 2    | RO   | 0    | Value of UTMI+ VBUSVLD flag. |

|   | 1    | RO   | 0    | Value of UTMI+ SESSVLD flag. |

|   | 0    | RO   | 0    | Value of UTMI+ SESSEND flag. |

**0x14:** UIFM on-the-go flags **0x20:** UIFM Sticky flags

| Bits | Perm | Init | Description               |

|------|------|------|---------------------------|

| 31:7 | RO   | -    | Reserved                  |

| 6:0  | RW   | 0    | Stickyness for each flag. |

#### F.10 UIFM port masks: 0x24

Set of masks that identify how port 1N, port 1O and port 1P are affected by changes to the flags in  $\ensuremath{\mathsf{FLAGS}}$

| Bits  | Perm | Init | Description                                                                                                                                         |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:23 | RO   | -    | Reserved                                                                                                                                            |

| 22:16 | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1P. If any flag listed in this bitmask is high, port 1P will be high. |

| 15    | RO   | -    | Reserved                                                                                                                                            |

| 14:8  | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 10. If any flag listed in this bitmask is high, port 10 will be high. |

| 7     | RO   | -    | Reserved                                                                                                                                            |

| 6:0   | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1N. If any flag listed in this bitmask is high, port 1N will be high. |

**0x24:** UIFM port masks

#### F.11 UIFM SOF value: 0x28

USB Start-Of-Frame counter

**0x28:** UIFM SOF value

| Bits  | Perm | Init | Description                             |

|-------|------|------|-----------------------------------------|

| 31:11 | RO   | -    | Reserved                                |

| 10:8  | RW   | 0    | Most significant 3 bits of SOF counter  |

| 7:0   | RW   | 0    | Least significant 8 bits of SOF counter |

# F.12 UIFM PID: 0x2C

The last USB packet identifier received

78

#### I.1 General oscillator control: 0x00

**0x00:** General oscillator control

| Bits | Perm | Init | Description                                                                                                   |

|------|------|------|---------------------------------------------------------------------------------------------------------------|

| 7:2  | RO   | -    | Reserved                                                                                                      |

| 1    | RW   | 0    | Set to 1 to reset the xCORE Tile when the value of the oscillator select control register (bit 0) is changed. |

| 0    | RW   | pin  | Selects the oscillator to use:<br>0: Crystal oscillator<br>1: On-silicon oscillator                           |

#### I.2 On-silicon-oscillator control: 0x01

This register controls the on-chip logic that implements an on-chip oscillator. The on-chip oscillator does not require an external crystal, but does not provide an accurate timing source. The nominal frequency of the on-silicon-oscillator is given below, but the actual frequency are temperature, voltage, and chip dependent.

0x01: On-siliconoscillator control

| Bits | Perm | Init | Description                                                                                                                           |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 7:2  | RO   | -    | Reserved                                                                                                                              |

| 1    | RW   | 0    | Selects the clock speed of the on-chip oscillator:<br>0: approximately 20 Mhz (fast clock)<br>1: approximately 31,250 Hz (slow clock) |

| 0    | RW   | 1    | Set to 0 to disable the on-chip oscillator. Do not do this unless the xCORE Tile is running off the crystal oscillator.               |

## I.3 Crystal-oscillator control: 0x02

This register controls the on-chip logic that implements the crystal oscillator; the crystal-oscillator requires an external crystal.

Bits Perm Init Description 7:2 RO -Reserved 1 RW 1 Set to 0 to disable the crystal bias circuit. Only switch the bias off 0x02: if an external oscillator rather than a crystal is connected. 0 RW 1 Set to 0 to disable the crystal oscillator. Do not do this unless the xCORE Tile is running off the on-silicon oscillator.

Crystaloscillator control

| Number | Perm | Description                                |

|--------|------|--------------------------------------------|

| 0x00   | RW   | General control                            |

| 0x04   | RW   | Time to wake-up, least significant 32 bits |

| 0x08   | RW   | Time to wake-up, most significant 32 bits  |

| 0x0C   | RW   | Power supply states whilst ASLEEP          |

| 0x10   | RW   | Power supply states whilst WAKING1         |

| 0x14   | RW   | Power supply states whilst WAKING2         |

| 0x18   | RW   | Power supply states whilst AWAKE           |

| 0x1C   | RW   | Power supply states whilst SLEEPING1       |

| 0x20   | RW   | Power supply states whilst SLEEPING2       |

| 0x24   | RW   | Power sequence status                      |

| 0x2C   | RW   | DCDC control                               |

| 0x30   | RW   | Power supply status                        |

| 0x34   | RW   | VDDCORE level control                      |

| 0x40   | RW   | LDO5 level control                         |

Figure 53: Summary

# K.1 General control: 0x00

This register controls the basic settings for power modes.

| Bits  | Perm | Init | Description                                                                                                                                    |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:21 | RO   | -    | Reserved                                                                                                                                       |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state:<br>0: 1 clock cycles<br>1: 2 clock cycles<br>2: 4 clock cycles<br><br>31: 2147483648 clock cycles |

| 15    | RO   | -    | Reserved                                                                                                                                       |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                                   |

| 13:10 | RO   | -    | Reserved                                                                                                                                       |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                                              |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                                              |

| 7:6   | RO   | -    | Reserved                                                                                                                                       |

| 5     | RW   | 1    | Set to 1 to enable VOUT6 (IO supply).                                                                                                          |

| 4     | RW   | 1    | Set to 1 to enable LDO5 (core PLL supply).                                                                                                     |

| 3:2   | RO   | -    | Reserved                                                                                                                                       |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                                    |

| 0     | RW   | 1    | Set to 1 to enable DCDC1 (core supply).                                                                                                        |

0x14: Power supply states whilst WAKING2

# K.7 Power supply states whilst AWAKE: 0x18

This register controls what state the power control block should be in when in the AWAKE state.

-XMOS<sup>®</sup>

| Bits  | Perm | Init | Description                                                                                                                                    |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:21 | RO   | -    | Reserved                                                                                                                                       |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state:<br>0: 1 clock cycles<br>1: 2 clock cycles<br>2: 4 clock cycles<br><br>31: 2147483648 clock cycles |

| 15    | RO   | -    | Reserved                                                                                                                                       |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                                   |

| 13:10 | RO   | -    | Reserved                                                                                                                                       |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                                              |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                                              |

| 7:6   | RO   | -    | Reserved                                                                                                                                       |

| 5     | RW   | 0    | Set to 1 to enable VOUT6 (IO supply).                                                                                                          |

| 4     | RW   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                                     |

| 3:2   | RO   | -    | Reserved                                                                                                                                       |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                                    |

| 0     | RW   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                                        |

0x20: Power supply states whilst SLEEPING2

# K.10 Power sequence status: 0x24

This register defines the current status of the power supply controller.

| Bits  | Perm | Init | Description                                                                                                                                                                                       |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                          |

| 25:24 | RW   | 2    | Sets the power good level for VDDCORE and VDD1V8:<br>0: 0.80 x VDDCORE, 0.80 x VDD1V8<br>1: 0.85 x VDDCORE, 0.85 x VDD1V8<br>2: 0.90 x VDDCORE, 0.90 x VDD1V8<br>3: 0.75 x VDDCORE, 0.75 x VDD1V8 |

| 23:17 | RO   | -    | Reserved                                                                                                                                                                                          |

| 16    | RW   | 0    | Clear DCDC1 and DCDC2 error flags, not self clearing.                                                                                                                                             |

| 15    | RO   | -    | Reserved                                                                                                                                                                                          |

| 14:13 | RW   | 0    | Sets the DCDC2 current limit:<br>0: 1A<br>1: 1.5A<br>2: 2A<br>3: 0.5A                                                                                                                             |

| 12:10 | RO   | -    | Reserved                                                                                                                                                                                          |

| 9:8   | RW   | 1    | Sets the clock used by DCDC2 to generate VDD1V8:<br>0: 0.9 MHz<br>1: 1.0 MHz<br>2: 1.1 MHz<br>3: 1.2 MHz                                                                                          |

| 7     | RO   | -    | Reserved                                                                                                                                                                                          |

| 6:5   | RW   | 0    | Sets the DCDC1 current limit:<br>0: 1.2A<br>1: 1.8A<br>2: 2.5A<br>3: 0.8A                                                                                                                         |

| 4:2   | RO   | -    | Reserved                                                                                                                                                                                          |

| 1:0   | RW   | 1    | Sets the clock used by DCDC1 to generate VDDCORE:<br>0: 0.9 MHz<br>1: 1.0 MHz<br>2: 1.1 MHz<br>3: 1.2 MHz                                                                                         |

0x2C: DCDC control

# K.12 Power supply status: 0x30

This register provides the current status of the power supplies.

0x40: LDO5 level control

| Bits | Perm | Init | Description                                                                                      |

|------|------|------|--------------------------------------------------------------------------------------------------|

| 31:3 | RO   | -    | Reserved                                                                                         |

| 2:0  | RW   | pin  | The required voltage in 100 mV steps:<br>0: 0.6V<br>1: 0.7V<br>2: 0.8V<br><br>6: 1.2V<br>7: 1.3V |

98