# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

#### Details

| Product Status                  | Obsolete                                                   |

|---------------------------------|------------------------------------------------------------|

| Programmable Type               | In System Programmable                                     |

| Delay Time tpd(1) Max           | 6 ns                                                       |

| Voltage Supply - Internal       | 4.75V ~ 5.25V                                              |

| Number of Logic Elements/Blocks | 8                                                          |

| Number of Macrocells            | 128                                                        |

| Number of Gates                 | 2500                                                       |

| Number of I/O                   | 84                                                         |

| Operating Temperature           | 0°C ~ 70°C (TA)                                            |

| Mounting Type                   | Surface Mount                                              |

| Package / Case                  | 100-BQFP                                                   |

| Supplier Device Package         | 100-PQFP (20x14)                                           |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm7128sqc100-6 |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

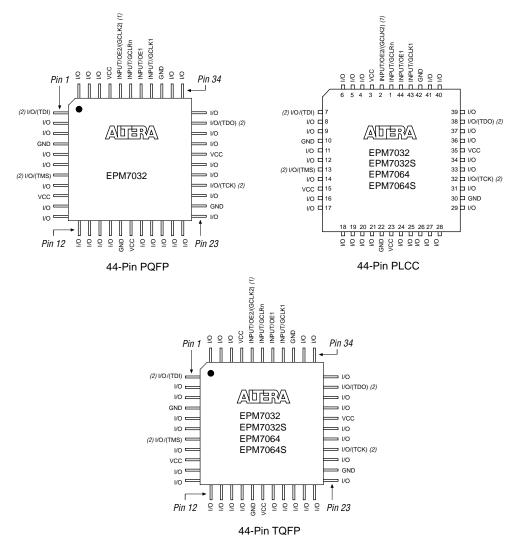

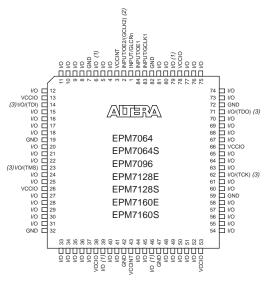

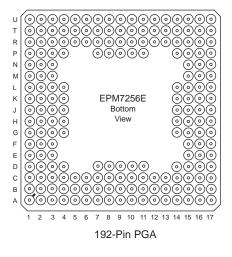

The MAX 7000 architecture supports 100% TTL emulation and high-density integration of SSI, MSI, and LSI logic functions. The MAX 7000 architecture easily integrates multiple devices ranging from PALs, GALs, and 22V10s to MACH and pLSI devices. MAX 7000 devices are available in a wide range of packages, including PLCC, PGA, PQFP, RQFP, and TQFP packages. See Table 5.

| Table 5. M | AX 7000            | ) Maxim            | um Use             | r I/O Piı          | ns N               | ote (1)             |                     |                     |                    |                    |                     |                     |

|------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|---------------------|---------------------|

| Device     | 44-<br>Pin<br>PLCC | 44-<br>Pin<br>PQFP | 44-<br>Pin<br>TQFP | 68-<br>Pin<br>PLCC | 84-<br>Pin<br>PLCC | 100-<br>Pin<br>PQFP | 100-<br>Pin<br>TQFP | 160-<br>Pin<br>PQFP | 160-<br>Pin<br>PGA | 192-<br>Pin<br>PGA | 208-<br>Pin<br>PQFP | 208-<br>Pin<br>RQFP |

| EPM7032    | 36                 | 36                 | 36                 |                    |                    |                     |                     |                     |                    |                    |                     |                     |

| EPM7032S   | 36                 |                    | 36                 |                    |                    |                     |                     |                     |                    |                    |                     |                     |

| EPM7064    | 36                 |                    | 36                 | 52                 | 68                 | 68                  |                     |                     |                    |                    |                     |                     |

| EPM7064S   | 36                 |                    | 36                 |                    | 68                 |                     | 68                  |                     |                    |                    |                     |                     |

| EPM7096    |                    |                    |                    | 52                 | 64                 | 76                  |                     |                     |                    |                    |                     |                     |

| EPM7128E   |                    |                    |                    |                    | 68                 | 84                  |                     | 100                 |                    |                    |                     |                     |

| EPM7128S   |                    |                    |                    |                    | 68                 | 84                  | 84 (2)              | 100                 |                    |                    |                     |                     |

| EPM7160E   |                    |                    |                    |                    | 64                 | 84                  |                     | 104                 |                    |                    |                     |                     |

| EPM7160S   |                    |                    |                    |                    | 64                 |                     | 84 (2)              | 104                 |                    |                    |                     |                     |

| EPM7192E   |                    |                    |                    |                    |                    |                     |                     | 124                 | 124                |                    |                     |                     |

| EPM7192S   |                    |                    |                    |                    |                    |                     |                     | 124                 |                    |                    |                     |                     |

| EPM7256E   |                    |                    |                    |                    |                    |                     |                     | 132 (2)             |                    | 164                |                     | 164                 |

| EPM7256S   |                    |                    |                    |                    |                    |                     |                     |                     |                    |                    | 164 (2)             | 164                 |

Notes:

When the JTAG interface in MAX 7000S devices is used for either boundary-scan testing or for ISP, four I/O pins become JTAG pins.

(2) Perform a complete thermal analysis before committing a design to this device package. For more information, see the *Operating Requirements for Altera Devices Data Sheet*.

MAX 7000 devices use CMOS EEPROM cells to implement logic functions. The user-configurable MAX 7000 architecture accommodates a variety of independent combinatorial and sequential logic functions. The devices can be reprogrammed for quick and efficient iterations during design development and debug cycles, and can be programmed and erased up to 100 times.

Each LAB is fed by the following signals:

- **3**6 signals from the PIA that are used for general logic inputs

- Global controls that are used for secondary register functions

- Direct input paths from I/O pins to the registers that are used for fast setup times for MAX 7000E and MAX 7000S devices

#### Macrocells

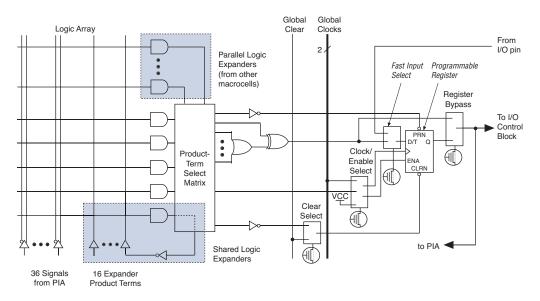

The MAX 7000 macrocell can be individually configured for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register. The macrocell of EPM7032, EPM7064, and EPM7096 devices is shown in Figure 3.

Figure 3. EPM7032, EPM7064 & EPM7096 Device Macrocell

Each programmable register can be clocked in three different modes:

- By a global clock signal. This mode achieves the fastest clock-tooutput performance.

- By a global clock signal and enabled by an active-high clock enable. This mode provides an enable on each flipflop while still achieving the fast clock-to-output performance of the global clock.

- By an array clock implemented with a product term. In this mode, the flipflop can be clocked by signals from buried macrocells or I/O pins.

In EPM7032, EPM7064, and EPM7096 devices, the global clock signal is available from a dedicated clock pin, GCLK1, as shown in Figure 1. In MAX 7000E and MAX 7000S devices, two global clock signals are available. As shown in Figure 2, these global clock signals can be the true or the complement of either of the global clock pins, GCLK1 or GCLK2.

Each register also supports asynchronous preset and clear functions. As shown in Figures 3 and 4, the product-term select matrix allocates product terms to control these operations. Although the product-term-driven preset and clear of the register are active high, active-low control can be obtained by inverting the signal within the logic array. In addition, each register clear function can be individually driven by the active-low dedicated global clear pin (GCLRn). Upon power-up, each register in the device will be set to a low state.

All MAX 7000E and MAX 7000S I/O pins have a fast input path to a macrocell register. This dedicated path allows a signal to bypass the PIA and combinatorial logic and be driven to an input D flipflop with an extremely fast (2.5 ns) input setup time.

### **Expander Product Terms**

Although most logic functions can be implemented with the five product terms available in each macrocell, the more complex logic functions require additional product terms. Another macrocell can be used to supply the required logic resources; however, the MAX 7000 architecture also allows both shareable and parallel expander product terms ("expanders") that provide additional product terms directly to any macrocell in the same LAB. These expanders help ensure that logic is synthesized with the fewest possible logic resources to obtain the fastest possible speed.

# Programmable Speed/Power Control

MAX 7000 devices offer a power-saving mode that supports low-power operation across user-defined signal paths or the entire device. This feature allows total power dissipation to be reduced by 50% or more, because most logic applications require only a small fraction of all gates to operate at maximum frequency.

The designer can program each individual macrocell in a MAX 7000 device for either high-speed (i.e., with the Turbo Bit<sup>TM</sup> option turned on) or low-power (i.e., with the Turbo Bit option turned off) operation. As a result, speed-critical paths in the design can run at high speed, while the remaining paths can operate at reduced power. Macrocells that run at low power incur a nominal timing delay adder ( $t_{LPA}$ ) for the  $t_{LAD}$ ,  $t_{LAC}$ ,  $t_{IC}$ ,  $t_{EN}$ , and  $t_{SEXP}$ ,  $\mathbf{t}_{ACL}$ , and  $\mathbf{t}_{CPPW}$  parameters.

Output Configuration

MAX 7000 device outputs can be programmed to meet a variety of system-level requirements.

## MultiVolt I/O Interface

MAX 7000 devices—except 44-pin devices—support the MultiVolt I/O interface feature, which allows MAX 7000 devices to interface with systems that have differing supply voltages. The 5.0-V devices in all packages can be set for 3.3-V or 5.0-V I/O pin operation. These devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The VCCINT pins must always be connected to a 5.0-V power supply. With a 5.0-V V<sub>CCINT</sub> level, input voltage thresholds are at TTL levels, and are therefore compatible with both 3.3-V and 5.0-V inputs.

The VCCIO pins can be connected to either a 3.3-V or a 5.0-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 5.0-V supply, the output levels are compatible with 5.0-V systems. When V<sub>CCIO</sub> is connected to a 3.3-V supply, the output high is 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with V<sub>CCIO</sub> levels lower than 4.75 V incur a nominally greater timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

# Open-Drain Output Option (MAX 7000S Devices Only)

MAX 7000S devices provide an optional open-drain (functionally equivalent to open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write enable signals) that can be asserted by any of several devices. It can also provide an additional wired-OR plane.

# Operating Conditions

Tables 13 through 18 provide information about absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for 5.0-V MAX 7000 devices.

#### Table 13. MAX 7000 5.0-V Device Absolute Maximum Ratings Note (1)

| Symbol           | Parameter                  | Conditions                         | Min  | Max | Unit |

|------------------|----------------------------|------------------------------------|------|-----|------|

| V <sub>CC</sub>  | Supply voltage             | With respect to ground (2)         | -2.0 | 7.0 | V    |

| VI               | DC input voltage           |                                    | -2.0 | 7.0 | V    |

| I <sub>OUT</sub> | DC output current, per pin |                                    | -25  | 25  | mA   |

| T <sub>STG</sub> | Storage temperature        | No bias                            | -65  | 150 | °C   |

| T <sub>AMB</sub> | Ambient temperature        | Under bias                         | -65  | 135 | °C   |

| TJ               | Junction temperature       | Ceramic packages, under bias       |      | 150 | °C   |

|                  |                            | PQFP and RQFP packages, under bias |      | 135 | °C   |

| Table 1            | 4. MAX 7000 5.0-V Device Reco                                  | ommended Operating Conditions |                |                          |      |

|--------------------|----------------------------------------------------------------|-------------------------------|----------------|--------------------------|------|

| Symbol             | Parameter                                                      | Conditions                    | Min            | Мах                      | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers            | (3), (4), (5)                 | 4.75<br>(4.50) | 5.25<br>(5.50)           | V    |

| V <sub>CCIO</sub>  | Supply voltage for output drivers, (3), (4)<br>5.0-V operation |                               | 4.75<br>(4.50) | 5.25<br>(5.50)           | V    |

|                    | Supply voltage for output drivers, 3.3-V operation             | (3), (4), (6)                 | 3.00<br>(3.00) | 3.60<br>(3.60)           | V    |

| V <sub>CCISP</sub> | Supply voltage during ISP                                      | (7)                           | 4.75           | 5.25                     | V    |

| VI                 | Input voltage                                                  |                               | -0.5 (8)       | V <sub>CCINT</sub> + 0.5 | V    |

| Vo                 | Output voltage                                                 |                               | 0              | V <sub>CCIO</sub>        | V    |

| T <sub>A</sub>     | Ambient temperature                                            | For commercial use            | 0              | 70                       | °C   |

|                    |                                                                | For industrial use            | -40            | 85                       | °C   |

| TJ                 | Junction temperature                                           | For commercial use            | 0              | 90                       | °C   |

|                    |                                                                | For industrial use            | -40            | 105                      | °C   |

| t <sub>R</sub>     | Input rise time                                                |                               |                | 40                       | ns   |

| t <sub>F</sub>     | Input fall time                                                |                               |                | 40                       | ns   |

| Table 1         | 5. MAX 7000 5.0-V Device DC (              | <b>Operating Conditions</b> Note (9)                        |                         |                          |      |

|-----------------|--------------------------------------------|-------------------------------------------------------------|-------------------------|--------------------------|------|

| Symbol          | Parameter                                  | Conditions                                                  | Min                     | Max                      | Unit |

| V <sub>IH</sub> | High-level input voltage                   |                                                             | 2.0                     | V <sub>CCINT</sub> + 0.5 | V    |

| V <sub>IL</sub> | Low-level input voltage                    |                                                             | -0.5 (8)                | 0.8                      | V    |

| V <sub>OH</sub> | 5.0-V high-level TTL output voltage        | $I_{OH} = -4 \text{ mA DC}, V_{CCIO} = 4.75 \text{ V} (10)$ | 2.4                     |                          | V    |

|                 | 3.3-V high-level TTL output voltage        | $I_{OH} = -4 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V} (10)$ | 2.4                     |                          | V    |

|                 | 3.3-V high-level CMOS output voltage       | $I_{OH}$ = -0.1 mA DC, $V_{CCIO}$ = 3.0 V (10)              | V <sub>CCIO</sub> – 0.2 |                          | V    |

| V <sub>OL</sub> | 5.0-V low-level TTL output voltage         | I <sub>OL</sub> = 12 mA DC, V <sub>CCIO</sub> = 4.75 V (11) |                         | 0.45                     | V    |

|                 | 3.3-V low-level TTL output voltage         | I <sub>OL</sub> = 12 mA DC, V <sub>CCIO</sub> = 3.00 V (11) |                         | 0.45                     | V    |

|                 | 3.3-V low-level CMOS output voltage        | I <sub>OL</sub> = 0.1 mA DC, V <sub>CCIO</sub> = 3.0 V(11)  |                         | 0.2                      | V    |

| I <sub>I</sub>  | Leakage current of dedicated input pins    | $V_{I} = -0.5$ to 5.5 V (11)                                | -10                     | 10                       | μΑ   |

| I <sub>OZ</sub> | I/O pin tri-state output off-state current | V <sub>I</sub> = -0.5 to 5.5 V (11), (12)                   | -40                     | 40                       | μA   |

| Table 1          | Table 16. MAX 7000 5.0-V Device Capacitance: EPM7032, EPM7064 & EPM7096 Devices       Note (13) |                                     |  |    |    |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------|-------------------------------------|--|----|----|--|--|--|--|

| Symbol           | Parameter                                                                                       | Parameter Conditions Min            |  |    |    |  |  |  |  |

| CIN              | Input pin capacitance                                                                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |  | 12 | pF |  |  |  |  |

| C <sub>I/O</sub> | I/O pin capacitance                                                                             | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |  | 12 | pF |  |  |  |  |

| Table 1          | Table 17. MAX 7000 5.0-V Device Capacitance: MAX 7000E Devices       Note (13) |                                     |     |     |      |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|--|--|

| Symbol           | Parameter                                                                      | Conditions                          | Min | Max | Unit |  |  |  |  |  |

| C <sub>IN</sub>  | Input pin capacitance                                                          | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 15  | pF   |  |  |  |  |  |

| C <sub>I/O</sub> | I/O pin capacitance                                                            | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 15  | pF   |  |  |  |  |  |

| Table 1          | Table 18. MAX 7000 5.0-V Device Capacitance: MAX 7000S Devices       Note (13) |                                     |     |     |      |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|--|--|

| Symbol           | Parameter                                                                      | Conditions                          | Min | Max | Unit |  |  |  |  |  |

| CIN              | Dedicated input pin capacitance                                                | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |  |  |  |  |

| C <sub>I/O</sub> | I/O pin capacitance                                                            | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |  |  |  |  |

.

| Table 2           | 21. MAX 7000 & MAX 7000E Ext               | ernal Timing Parame | eters Note | (1)       |                  |      |      |

|-------------------|--------------------------------------------|---------------------|------------|-----------|------------------|------|------|

| Symbol            | Parameter                                  | Conditions          |            | Speed (   | Grade            |      | Unit |

|                   |                                            |                     | MAX 700    | 0E (-10P) | MAX 70<br>Max 70 |      |      |

|                   |                                            |                     | Min        | Max       | Min              | Max  |      |

| t <sub>PD1</sub>  | Input to non-registered output             | C1 = 35 pF          |            | 10.0      |                  | 10.0 | ns   |

| t <sub>PD2</sub>  | I/O input to non-registered output         | C1 = 35 pF          |            | 10.0      |                  | 10.0 | ns   |

| t <sub>SU</sub>   | Global clock setup time                    |                     | 7.0        |           | 8.0              |      | ns   |

| t <sub>H</sub>    | Global clock hold time                     |                     | 0.0        |           | 0.0              |      | ns   |

| t <sub>FSU</sub>  | Global clock setup time of fast input      | (2)                 | 3.0        |           | 3.0              |      | ns   |

| t <sub>FH</sub>   | Global clock hold time of fast input       | (2)                 | 0.5        |           | 0.5              |      | ns   |

| t <sub>CO1</sub>  | Global clock to output delay               | C1 = 35 pF          |            | 5.0       |                  | 5    | ns   |

| t <sub>CH</sub>   | Global clock high time                     |                     | 4.0        |           | 4.0              |      | ns   |

| t <sub>CL</sub>   | Global clock low time                      |                     | 4.0        |           | 4.0              |      | ns   |

| t <sub>ASU</sub>  | Array clock setup time                     |                     | 2.0        |           | 3.0              |      | ns   |

| t <sub>AH</sub>   | Array clock hold time                      |                     | 3.0        |           | 3.0              |      | ns   |

| t <sub>ACO1</sub> | Array clock to output delay                | C1 = 35 pF          |            | 10.0      |                  | 10.0 | ns   |

| t <sub>ACH</sub>  | Array clock high time                      |                     | 4.0        |           | 4.0              |      | ns   |

| t <sub>ACL</sub>  | Array clock low time                       |                     | 4.0        |           | 4.0              |      | ns   |

| t <sub>CPPW</sub> | Minimum pulse width for clear and preset   | (3)                 | 4.0        |           | 4.0              |      | ns   |

| t <sub>ODH</sub>  | Output data hold time after clock          | C1 = 35 pF (4)      | 1.0        |           | 1.0              |      | ns   |

| t <sub>CNT</sub>  | Minimum global clock period                |                     |            | 10.0      |                  | 10.0 | ns   |

| f <sub>CNT</sub>  | Maximum internal global clock<br>frequency | (5)                 | 100.0      |           | 100.0            |      | MHz  |

| t <sub>ACNT</sub> | Minimum array clock period                 |                     |            | 10.0      |                  | 10.0 | ns   |

| f <sub>acnt</sub> | Maximum internal array clock<br>frequency  | (5)                 | 100.0      |           | 100.0            |      | MHz  |

| f <sub>MAX</sub>  | Maximum clock frequency                    | (6)                 | 125.0      |           | 125.0            |      | MHz  |

|                   | 5. MAX 7000 & MAX 7000E                     | -              | aramete |      | lote (1) |       |      |      |      |

|-------------------|---------------------------------------------|----------------|---------|------|----------|-------|------|------|------|

| Symbol            | Parameter                                   | Conditions     |         |      | Speed    | Grade |      |      | Unit |

|                   |                                             |                | -       | -15  |          | -15T  |      | 20   |      |

|                   |                                             |                | Min     | Max  | Min      | Max   | Min  | Max  |      |

| t <sub>PD1</sub>  | Input to non-registered output              | C1 = 35 pF     |         | 15.0 |          | 15.0  |      | 20.0 | ns   |

| t <sub>PD2</sub>  | I/O input to non-registered<br>output       | C1 = 35 pF     |         | 15.0 |          | 15.0  |      | 20.0 | ns   |

| t <sub>SU</sub>   | Global clock setup time                     |                | 11.0    |      | 11.0     |       | 12.0 |      | ns   |

| t <sub>H</sub>    | Global clock hold time                      |                | 0.0     |      | 0.0      |       | 0.0  |      | ns   |

| t <sub>FSU</sub>  | Global clock setup time of fast input       | (2)            | 3.0     |      | -        |       | 5.0  |      | ns   |

| t <sub>FH</sub>   | Global clock hold time of fast input        | (2)            | 0.0     |      | -        |       | 0.0  |      | ns   |

| t <sub>CO1</sub>  | Global clock to output delay                | C1 = 35 pF     |         | 8.0  |          | 8.0   |      | 12.0 | ns   |

| t <sub>CH</sub>   | Global clock high time                      |                | 5.0     |      | 6.0      |       | 6.0  |      | ns   |

| t <sub>CL</sub>   | Global clock low time                       |                | 5.0     |      | 6.0      |       | 6.0  |      | ns   |

| t <sub>ASU</sub>  | Array clock setup time                      |                | 4.0     |      | 4.0      |       | 5.0  |      | ns   |

| t <sub>AH</sub>   | Array clock hold time                       |                | 4.0     |      | 4.0      |       | 5.0  |      | ns   |

| t <sub>ACO1</sub> | Array clock to output delay                 | C1 = 35 pF     |         | 15.0 |          | 15.0  |      | 20.0 | ns   |

| t <sub>ACH</sub>  | Array clock high time                       |                | 6.0     |      | 6.5      |       | 8.0  |      | ns   |

| t <sub>ACL</sub>  | Array clock low time                        |                | 6.0     |      | 6.5      |       | 8.0  |      | ns   |

| t <sub>CPPW</sub> | Minimum pulse width for clear<br>and preset | (3)            | 6.0     |      | 6.5      |       | 8.0  |      | ns   |

| t <sub>odh</sub>  | Output data hold time after<br>clock        | C1 = 35 pF (4) | 1.0     |      | 1.0      |       | 1.0  |      | ns   |

| t <sub>CNT</sub>  | Minimum global clock period                 |                |         | 13.0 |          | 13.0  |      | 16.0 | ns   |

| fcnt              | Maximum internal global clock frequency     | (5)            | 76.9    |      | 76.9     |       | 62.5 |      | MHz  |

| t <sub>ACNT</sub> | Minimum array clock period                  |                |         | 13.0 |          | 13.0  |      | 16.0 | ns   |

| facnt             | Maximum internal array clock frequency      | (5)            | 76.9    |      | 76.9     |       | 62.5 |      | MHz  |

| f <sub>MAX</sub>  | Maximum clock frequency                     | (6)            | 100     |      | 83.3     |       | 83.3 |      | MHz  |

| Symbol            | Parameter                                                                                | Conditions     |     |      | Speed | Grade |     |      | Unit |

|-------------------|------------------------------------------------------------------------------------------|----------------|-----|------|-------|-------|-----|------|------|

|                   |                                                                                          |                | -   | 15   | -1    | 5T    | -2  | 20   |      |

|                   |                                                                                          |                | Min | Max  | Min   | Max   | Min | Max  |      |

| t <sub>IN</sub>   | Input pad and buffer delay                                                               |                |     | 2.0  |       | 2.0   |     | 3.0  | ns   |

| t <sub>IO</sub>   | I/O input pad and buffer delay                                                           |                |     | 2.0  |       | 2.0   |     | 3.0  | ns   |

| t <sub>FIN</sub>  | Fast input delay                                                                         | (2)            |     | 2.0  |       | -     |     | 4.0  | ns   |

| t <sub>SEXP</sub> | Shared expander delay                                                                    |                |     | 8.0  |       | 10.0  |     | 9.0  | ns   |

| t <sub>PEXP</sub> | Parallel expander delay                                                                  |                |     | 1.0  |       | 1.0   |     | 2.0  | ns   |

| t <sub>LAD</sub>  | Logic array delay                                                                        |                |     | 6.0  |       | 6.0   |     | 8.0  | ns   |

| tLAC              | Logic control array delay                                                                |                |     | 6.0  |       | 6.0   |     | 8.0  | ns   |

| t <sub>IOE</sub>  | Internal output enable delay                                                             | (2)            |     | 3.0  |       | -     |     | 4.0  | ns   |

| t <sub>OD1</sub>  | Output buffer and pad delay<br>Slow slew rate = off<br>V <sub>CCIO</sub> = 5.0 V         | C1 = 35 pF     |     | 4.0  |       | 4.0   |     | 5.0  | ns   |

| t <sub>OD2</sub>  | Output buffer and pad delay<br>Slow slew rate = off<br>V <sub>CCIO</sub> = 3.3 V         | C1 = 35 pF (7) |     | 5.0  |       | -     |     | 6.0  | ns   |

| t <sub>OD3</sub>  | Output buffer and pad delay<br>Slow slew rate = on<br>V <sub>CCIO</sub> = 5.0 V or 3.3 V | C1 = 35 pF (2) |     | 8.0  |       | -     |     | 9.0  | ns   |

| t <sub>ZX1</sub>  | Output buffer enable delay<br>Slow slew rate = off<br>V <sub>CCIO</sub> = 5.0 V          | C1 = 35 pF     |     | 6.0  |       | 6.0   |     | 10.0 | ns   |

| t <sub>ZX2</sub>  | Output buffer enable delay<br>Slow slew rate = off<br>V <sub>CCIO</sub> = 3.3 V          | C1 = 35 pF (7) |     | 7.0  |       | -     |     | 11.0 | ns   |

| t <sub>ZX3</sub>  | Output buffer enable delay<br>Slow slew rate = on<br>V <sub>CCIO</sub> = 5.0 V or 3.3 V  | C1 = 35 pF (2) |     | 10.0 |       | -     |     | 14.0 | ns   |

| t <sub>XZ</sub>   | Output buffer disable delay                                                              | C1 = 5 pF      |     | 6.0  |       | 6.0   |     | 10.0 | ns   |

| t <sub>SU</sub>   | Register setup time                                                                      |                | 4.0 |      | 4.0   |       | 4.0 |      | ns   |

| t <sub>H</sub>    | Register hold time                                                                       |                | 4.0 |      | 4.0   |       | 5.0 |      | ns   |

| t <sub>FSU</sub>  | Register setup time of fast input                                                        | (2)            | 2.0 |      | -     |       | 4.0 |      | ns   |

| t <sub>FH</sub>   | Register hold time of fast input                                                         | (2)            | 2.0 |      | -     |       | 3.0 |      | ns   |

| t <sub>RD</sub>   | Register delay                                                                           |                |     | 1.0  |       | 1.0   |     | 1.0  | ns   |

| t <sub>COMB</sub> | Combinatorial delay                                                                      |                |     | 1.0  |       | 1.0   |     | 1.0  | ns   |

| t <sub>IC</sub>   | Array clock delay                                                                        |                |     | 6.0  |       | 6.0   |     | 8.0  | ns   |

| t <sub>EN</sub>   | Register enable time                                                                     |                |     | 6.0  |       | 6.0   |     | 8.0  | ns   |

| t <sub>GLOB</sub> | Global control delay                                                                     |                |     | 1.0  |       | 1.0   |     | 3.0  | ns   |

| t <sub>PRE</sub>  | Register preset time                                                                     |                |     | 4.0  |       | 4.0   |     | 4.0  | ns   |

| t <sub>CLR</sub>  | Register clear time                                                                      |                |     | 4.0  |       | 4.0   |     | 4.0  | ns   |

| t <sub>PIA</sub>  | PIA delay                                                                                |                |     | 2.0  |       | 2.0   |     | 3.0  | ns   |

| t <sub>LPA</sub>  | Low-power adder                                                                          | (8)            |     | 13.0 |       | 15.0  |     | 15.0 | ns   |

| Symbol            | Parameter                         | Conditions     | Speed Grade |      |     |      |     |      |     |      |    |

|-------------------|-----------------------------------|----------------|-------------|------|-----|------|-----|------|-----|------|----|

|                   |                                   |                | -6          |      | -7  |      | -10 |      | -1  | 15   |    |

|                   |                                   |                | Min         | Max  | Min | Max  | Min | Max  | Min | Max  | -  |

| t <sub>IN</sub>   | Input pad and buffer delay        |                |             | 0.2  |     | 0.5  |     | 0.5  |     | 2.0  | ns |

| t <sub>IO</sub>   | I/O input pad and buffer delay    |                |             | 0.2  |     | 0.5  |     | 0.5  |     | 2.0  | ns |

| t <sub>FIN</sub>  | Fast input delay                  |                |             | 2.6  |     | 1.0  |     | 1.0  |     | 2.0  | ns |

| t <sub>SEXP</sub> | Shared expander delay             |                |             | 3.7  |     | 4.0  |     | 5.0  |     | 8.0  | ns |

| t <sub>PEXP</sub> | Parallel expander delay           |                |             | 1.1  |     | 0.8  |     | 0.8  |     | 1.0  | ns |

| t <sub>LAD</sub>  | Logic array delay                 |                |             | 3.0  |     | 3.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>LAC</sub>  | Logic control array delay         |                |             | 3.0  |     | 3.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>IOE</sub>  | Internal output enable delay      |                |             | 0.7  |     | 2.0  |     | 2.0  |     | 3.0  | ns |

| t <sub>OD1</sub>  | Output buffer and pad delay       | C1 = 35 pF     |             | 0.4  |     | 2.0  |     | 1.5  |     | 4.0  | ns |

| t <sub>OD2</sub>  | Output buffer and pad delay       | C1 = 35 pF (6) |             | 0.9  |     | 2.5  |     | 2.0  |     | 5.0  | ns |

| t <sub>OD3</sub>  | Output buffer and pad delay       | C1 = 35 pF     |             | 5.4  |     | 7.0  |     | 5.5  |     | 8.0  | ns |

| t <sub>ZX1</sub>  | Output buffer enable delay        | C1 = 35 pF     |             | 4.0  |     | 4.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>ZX2</sub>  | Output buffer enable delay        | C1 = 35 pF (6) |             | 4.5  |     | 4.5  |     | 5.5  |     | 7.0  | ns |

| t <sub>ZX3</sub>  | Output buffer enable delay        | C1 = 35 pF     |             | 9.0  |     | 9.0  |     | 9.0  |     | 10.0 | ns |

| t <sub>XZ</sub>   | Output buffer disable delay       | C1 = 5 pF      |             | 4.0  |     | 4.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>SU</sub>   | Register setup time               |                | 1.0         |      | 3.0 |      | 2.0 |      | 4.0 |      | ns |

| t <sub>H</sub>    | Register hold time                |                | 1.7         |      | 2.0 |      | 5.0 |      | 4.0 |      | ns |

| t <sub>FSU</sub>  | Register setup time of fast input |                | 1.9         |      | 3.0 |      | 3.0 |      | 2.0 |      | ns |

| t <sub>FH</sub>   | Register hold time of fast input  |                | 0.6         |      | 0.5 |      | 0.5 |      | 1.0 |      | ns |

| t <sub>RD</sub>   | Register delay                    |                |             | 1.4  |     | 1.0  |     | 2.0  |     | 1.0  | ns |

| t <sub>COMB</sub> | Combinatorial delay               |                |             | 1.0  |     | 1.0  |     | 2.0  |     | 1.0  | ns |

| t <sub>IC</sub>   | Array clock delay                 |                |             | 3.1  |     | 3.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>EN</sub>   | Register enable time              |                |             | 3.0  |     | 3.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>GLOB</sub> | Global control delay              |                |             | 2.0  |     | 1.0  |     | 1.0  |     | 1.0  | ns |

| t <sub>PRE</sub>  | Register preset time              |                |             | 2.4  |     | 2.0  |     | 3.0  |     | 4.0  | ns |

| t <sub>CLR</sub>  | Register clear time               |                |             | 2.4  |     | 2.0  |     | 3.0  |     | 4.0  | ns |

| t <sub>PIA</sub>  | PIA delay                         | (7)            |             | 1.4  |     | 1.0  |     | 1.0  |     | 2.0  | ns |

| t <sub>LPA</sub>  | Low-power adder                   | (8)            |             | 11.0 |     | 10.0 |     | 11.0 |     | 13.0 | ns |

#### Notes to tables:

- (1) These values are specified under the recommended operating conditions shown in Table 14. See Figure 13 for more information on switching waveforms.

- (2) This minimum pulse width for preset and clear applies for both global clear and array controls. The t<sub>LPA</sub> parameter must be added to this minimum width if the clear or reset signal incorporates the t<sub>LAD</sub> parameter into the signal path.

- (3) This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This parameter applies for both global and array clocking.

- (4) These parameters are measured with a 16-bit loadable, enabled, up/down counter programmed into each LAB.

- (5) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- (6) Operating conditions:  $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial and industrial use.

- (7) For EPM7064S-5, EPM7064S-6, EPM7128S-6, EPM7160S-6, EPM7160S-7, EPM7192S-7, and EPM7256S-7 devices, these values are specified for a PIA fan-out of one LAB (16 macrocells). For each additional LAB fan-out in these devices, add an additional 0.1 ns to the PIA timing value.

- (8) The  $t_{LPA}$  parameter must be added to the  $t_{LAD}$ ,  $t_{LAC}$ ,  $t_{IC}$ ,  $t_{EN}$ ,  $t_{SEXP}$ ,  $t_{ACL}$ , and  $t_{CPPW}$  parameters for macrocells running in the low-power mode.

#### Tables 33 and 34 show the EPM7160S AC operating conditions.

| Symbol            | Parameter                                   | Conditions            | Speed Grade |     |       |     |       |      |      |      |     |

|-------------------|---------------------------------------------|-----------------------|-------------|-----|-------|-----|-------|------|------|------|-----|

|                   |                                             |                       | -6          |     | -7    |     | -10   |      | -15  |      |     |

|                   |                                             |                       | Min         | Max | Min   | Max | Min   | Max  | Min  | Max  |     |

| t <sub>PD1</sub>  | Input to non-registered output              | C1 = 35 pF            |             | 6.0 |       | 7.5 |       | 10.0 |      | 15.0 | ns  |

| t <sub>PD2</sub>  | I/O input to non-registered<br>output       | C1 = 35 pF            |             | 6.0 |       | 7.5 |       | 10.0 |      | 15.0 | ns  |

| t <sub>SU</sub>   | Global clock setup time                     |                       | 3.4         |     | 4.2   |     | 7.0   |      | 11.0 |      | ns  |

| t <sub>H</sub>    | Global clock hold time                      |                       | 0.0         |     | 0.0   |     | 0.0   |      | 0.0  |      | ns  |

| t <sub>FSU</sub>  | Global clock setup time of fast input       |                       | 2.5         |     | 3.0   |     | 3.0   |      | 3.0  |      | ns  |

| t <sub>FH</sub>   | Global clock hold time of fast input        |                       | 0.0         |     | 0.0   |     | 0.5   |      | 0.0  |      | ns  |

| t <sub>CO1</sub>  | Global clock to output delay                | C1 = 35 pF            |             | 3.9 |       | 4.8 |       | 5    |      | 8    | ns  |

| t <sub>CH</sub>   | Global clock high time                      |                       | 3.0         |     | 3.0   |     | 4.0   |      | 5.0  |      | ns  |

| t <sub>CL</sub>   | Global clock low time                       |                       | 3.0         |     | 3.0   |     | 4.0   |      | 5.0  |      | ns  |

| t <sub>ASU</sub>  | Array clock setup time                      |                       | 0.9         |     | 1.1   |     | 2.0   |      | 4.0  |      | ns  |

| t <sub>AH</sub>   | Array clock hold time                       |                       | 1.7         |     | 2.1   |     | 3.0   |      | 4.0  |      | ns  |

| t <sub>ACO1</sub> | Array clock to output delay                 | C1 = 35 pF            |             | 6.4 |       | 7.9 |       | 10.0 |      | 15.0 | ns  |

| t <sub>ACH</sub>  | Array clock high time                       |                       | 3.0         |     | 3.0   |     | 4.0   |      | 6.0  |      | ns  |

| t <sub>ACL</sub>  | Array clock low time                        |                       | 3.0         |     | 3.0   |     | 4.0   |      | 6.0  |      | ns  |

| t <sub>CPPW</sub> | Minimum pulse width for clear<br>and preset | (2)                   | 2.5         |     | 3.0   |     | 4.0   |      | 6.0  |      | ns  |

| t <sub>ODH</sub>  | Output data hold time after<br>clock        | C1 = 35 pF <i>(3)</i> | 1.0         |     | 1.0   |     | 1.0   |      | 1.0  |      | ns  |

| t <sub>CNT</sub>  | Minimum global clock period                 |                       |             | 6.7 |       | 8.2 |       | 10.0 |      | 13.0 | ns  |

| f <sub>сnт</sub>  | Maximum internal global clock frequency     | (4)                   | 149.3       |     | 122.0 |     | 100.0 |      | 76.9 |      | MHz |

**Altera Corporation**

| Table 3                                 | 3. EPM7160S External Time                 | ing Parameters | (Part 2       | 2 of 2) | No    | nte (1) |       |      |       |      |      |

|-----------------------------------------|-------------------------------------------|----------------|---------------|---------|-------|---------|-------|------|-------|------|------|

| Symbol Parameter Conditions Speed Grade |                                           |                |               |         |       |         |       |      |       |      | Unit |

|                                         |                                           |                | -6 -7 -10 -15 |         |       |         |       |      |       |      |      |

|                                         |                                           |                | Min           | Max     | Min   | Max     | Min   | Max  | Min   | Max  |      |

| t <sub>ACNT</sub>                       | Minimum array clock period                |                |               | 6.7     |       | 8.2     |       | 10.0 |       | 13.0 | ns   |

| f <sub>acnt</sub>                       | Maximum internal array clock<br>frequency | (4)            | 149.3         |         | 122.0 |         | 100.0 |      | 76.9  |      | MHz  |

| f <sub>MAX</sub>                        | Maximum clock frequency                   | (5)            | 166.7         |         | 166.7 |         | 125.0 |      | 100.0 |      | MHz  |

| Symbol            | Parameter                         | Conditions     |     |     |     | Speed | Grade |     |     |      | Unit |

|-------------------|-----------------------------------|----------------|-----|-----|-----|-------|-------|-----|-----|------|------|

|                   |                                   |                | -6  |     | -7  |       | -10   |     | -15 |      |      |

|                   |                                   |                | Min | Max | Min | Max   | Min   | Max | Min | Max  |      |

| t <sub>IN</sub>   | Input pad and buffer delay        |                |     | 0.2 |     | 0.3   |       | 0.5 |     | 2.0  | ns   |

| t <sub>IO</sub>   | I/O input pad and buffer delay    |                |     | 0.2 |     | 0.3   |       | 0.5 |     | 2.0  | ns   |

| t <sub>FIN</sub>  | Fast input delay                  |                |     | 2.6 |     | 3.2   |       | 1.0 |     | 2.0  | ns   |

| t <sub>SEXP</sub> | Shared expander delay             |                |     | 3.6 |     | 4.3   |       | 5.0 |     | 8.0  | ns   |

| t <sub>PEXP</sub> | Parallel expander delay           |                |     | 1.0 |     | 1.3   |       | 0.8 |     | 1.0  | ns   |

| t <sub>LAD</sub>  | Logic array delay                 |                |     | 2.8 |     | 3.4   |       | 5.0 |     | 6.0  | ns   |

| t <sub>LAC</sub>  | Logic control array delay         |                |     | 2.8 |     | 3.4   |       | 5.0 |     | 6.0  | ns   |

| t <sub>IOE</sub>  | Internal output enable delay      |                |     | 0.7 |     | 0.9   |       | 2.0 |     | 3.0  | ns   |

| t <sub>OD1</sub>  | Output buffer and pad delay       | C1 = 35 pF     |     | 0.4 |     | 0.5   |       | 1.5 |     | 4.0  | ns   |

| t <sub>OD2</sub>  | Output buffer and pad delay       | C1 = 35 pF (6) |     | 0.9 |     | 1.0   |       | 2.0 |     | 5.0  | ns   |

| t <sub>OD3</sub>  | Output buffer and pad delay       | C1 = 35 pF     |     | 5.4 |     | 5.5   |       | 5.5 |     | 8.0  | ns   |

| t <sub>ZX1</sub>  | Output buffer enable delay        | C1 = 35 pF     |     | 4.0 |     | 4.0   |       | 5.0 |     | 6.0  | ns   |

| t <sub>ZX2</sub>  | Output buffer enable delay        | C1 = 35 pF (6) |     | 4.5 |     | 4.5   |       | 5.5 |     | 7.0  | ns   |

| t <sub>ZX3</sub>  | Output buffer enable delay        | C1 = 35 pF     |     | 9.0 |     | 9.0   |       | 9.0 |     | 10.0 | ns   |

| t <sub>XZ</sub>   | Output buffer disable delay       | C1 = 5 pF      |     | 4.0 |     | 4.0   |       | 5.0 |     | 6.0  | ns   |

| t <sub>SU</sub>   | Register setup time               |                | 1.0 |     | 1.2 |       | 2.0   |     | 4.0 |      | ns   |

| t <sub>H</sub>    | Register hold time                |                | 1.6 |     | 2.0 |       | 3.0   |     | 4.0 |      | ns   |

| t <sub>FSU</sub>  | Register setup time of fast input |                | 1.9 |     | 2.2 |       | 3.0   |     | 2.0 |      | ns   |

| t <sub>FH</sub>   | Register hold time of fast input  |                | 0.6 |     | 0.8 |       | 0.5   |     | 1.0 |      | ns   |

| t <sub>RD</sub>   | Register delay                    |                |     | 1.3 |     | 1.6   |       | 2.0 |     | 1.0  | ns   |

| t <sub>COMB</sub> | Combinatorial delay               |                |     | 1.0 |     | 1.3   |       | 2.0 |     | 1.0  | ns   |

| t <sub>IC</sub>   | Array clock delay                 |                |     | 2.9 |     | 3.5   |       | 5.0 |     | 6.0  | ns   |

| t <sub>EN</sub>   | Register enable time              |                |     | 2.8 |     | 3.4   |       | 5.0 |     | 6.0  | ns   |

| t <sub>GLOB</sub> | Global control delay              |                |     | 2.0 |     | 2.4   |       | 1.0 |     | 1.0  | ns   |

| t <sub>PRE</sub>  | Register preset time              |                |     | 2.4 |     | 3.0   |       | 3.0 |     | 4.0  | ns   |

Г

-

| Table 3          | 4. EPM7160S Internal 1 | <i>Timing Parameters</i> | s (Part )   | 2 of 2) | No  | te (1) |     |      |     |      |    |

|------------------|------------------------|--------------------------|-------------|---------|-----|--------|-----|------|-----|------|----|

| Symbol           | Parameter              | Conditions               | Speed Grade |         |     |        |     |      |     |      |    |

|                  |                        |                          | -           | 6       | -   | 7      | -1  | 10   |     | 15   |    |

|                  |                        |                          | Min         | Max     | Min | Max    | Min | Max  | Min | Max  |    |

| t <sub>CLR</sub> | Register clear time    |                          |             | 2.4     |     | 3.0    |     | 3.0  |     | 4.0  | ns |

| t <sub>PIA</sub> | PIA delay              | (7)                      |             | 1.6     |     | 2.0    |     | 1.0  |     | 2.0  | ns |

| t <sub>LPA</sub> | Low-power adder        | (8)                      |             | 11.0    |     | 10.0   |     | 11.0 |     | 13.0 | ns |

#### Notes to tables:

- These values are specified under the recommended operating conditions shown in Table 14. See Figure 13 for more (1)information on switching waveforms.

- This minimum pulse width for preset and clear applies for both global clear and array controls. The  $t_{LPA}$  parameter (2)must be added to this minimum width if the clear or reset signal incorporates the  $t_{IAD}$  parameter into the signal path.

This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This (3) parameter applies for both global and array clocking.

These parameters are measured with a 16-bit loadable, enabled, up/down counter programmed into each LAB. (4)

- (5) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- Operating conditions:  $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial and industrial use. (6)

For EPM7064S-5, EPM7064S-6, EPM7128S-6, EPM7160S-6, EPM7160S-7, EPM7192S-7, and EPM7256S-7 devices, (7) these values are specified for a PIA fan-out of one LAB (16 macrocells). For each additional LAB fan-out in these devices, add an additional 0.1 ns to the PIA timing value.

(8)The  $t_{LPA}$  parameter must be added to the  $t_{LAD}$ ,  $t_{LAC}$ ,  $t_{IC}$ ,  $t_{EN}$ ,  $t_{SEXP}$ ,  $t_{ACL}$  and  $t_{CPPW}$  parameters for macrocells running in the low-power mode.

#### Tables 35 and 36 show the EPM7192S AC operating conditions.

| Table 3          | 35. EPM7192S External Tim             | ing Parameters (P | art 1 of 2  | <b>?)</b> No | ote (1) |      |      |      |    |  |

|------------------|---------------------------------------|-------------------|-------------|--------------|---------|------|------|------|----|--|

| Symbol           | Parameter                             | Conditions        | Speed Grade |              |         |      |      |      |    |  |

|                  |                                       |                   | -7          |              | -10     |      | -15  |      | 1  |  |

|                  |                                       |                   | Min         | Max          | Min     | Max  | Min  | Max  |    |  |

| t <sub>PD1</sub> | Input to non-registered output        | C1 = 35 pF        |             | 7.5          |         | 10.0 |      | 15.0 | ns |  |

| t <sub>PD2</sub> | I/O input to non-registered<br>output | C1 = 35 pF        |             | 7.5          |         | 10.0 |      | 15.0 | ns |  |

| t <sub>SU</sub>  | Global clock setup time               |                   | 4.1         |              | 7.0     |      | 11.0 |      | ns |  |

| t <sub>H</sub>   | Global clock hold time                |                   | 0.0         |              | 0.0     |      | 0.0  |      | ns |  |

| t <sub>FSU</sub> | Global clock setup time of fast input |                   | 3.0         |              | 3.0     |      | 3.0  |      | ns |  |

| t <sub>FH</sub>  | Global clock hold time of fast input  |                   | 0.0         |              | 0.5     |      | 0.0  |      | ns |  |

| t <sub>CO1</sub> | Global clock to output delay          | C1 = 35 pF        |             | 4.7          |         | 5.0  |      | 8.0  | ns |  |

| t <sub>CH</sub>  | Global clock high time                |                   | 3.0         |              | 4.0     |      | 5.0  |      | ns |  |

| t <sub>CL</sub>  | Global clock low time                 |                   | 3.0         |              | 4.0     |      | 5.0  |      | ns |  |

| t <sub>ASU</sub> | Array clock setup time                |                   | 1.0         |              | 2.0     |      | 4.0  |      | ns |  |

| Symbol            | Parameter                         | Conditions | Speed Grade |      |     |      |     |      |    |  |

|-------------------|-----------------------------------|------------|-------------|------|-----|------|-----|------|----|--|

|                   |                                   |            | -7          |      | -10 |      | -15 |      | 1  |  |

|                   |                                   |            | Min         | Max  | Min | Max  | Min | Max  |    |  |

| t <sub>H</sub>    | Register hold time                |            | 1.7         |      | 3.0 |      | 4.0 |      | ns |  |

| t <sub>FSU</sub>  | Register setup time of fast input |            | 2.3         |      | 3.0 |      | 2.0 |      | ns |  |

| t <sub>FH</sub>   | Register hold time of fast input  |            | 0.7         |      | 0.5 |      | 1.0 |      | ns |  |

| t <sub>RD</sub>   | Register delay                    |            |             | 1.4  |     | 2.0  |     | 1.0  | ns |  |

| t <sub>COMB</sub> | Combinatorial delay               |            |             | 1.2  |     | 2.0  |     | 1.0  | ns |  |

| t <sub>IC</sub>   | Array clock delay                 |            |             | 3.2  |     | 5.0  |     | 6.0  | ns |  |

| t <sub>EN</sub>   | Register enable time              |            |             | 3.1  |     | 5.0  |     | 6.0  | ns |  |

| t <sub>GLOB</sub> | Global control delay              |            |             | 2.5  |     | 1.0  |     | 1.0  | ns |  |

| t <sub>PRE</sub>  | Register preset time              |            |             | 2.7  |     | 3.0  |     | 4.0  | ns |  |

| t <sub>CLR</sub>  | Register clear time               |            |             | 2.7  |     | 3.0  |     | 4.0  | ns |  |

| t <sub>PIA</sub>  | PIA delay                         | (7)        |             | 2.4  |     | 1.0  |     | 2.0  | ns |  |

| t <sub>LPA</sub>  | Low-power adder                   | (8)        |             | 10.0 |     | 11.0 |     | 13.0 | ns |  |

#### Notes to tables:

- (1) These values are specified under the recommended operating conditions shown in Table 14. See Figure 13 for more information on switching waveforms.

- (2) This minimum pulse width for preset and clear applies for both global clear and array controls. The t<sub>LPA</sub> parameter must be added to this minimum width if the clear or reset signal incorporates the t<sub>LAD</sub> parameter into the signal path.

- (3) This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This parameter applies for both global and array clocking.

- (4) These parameters are measured with a 16-bit loadable, enabled, up/down counter programmed into each LAB.

- (5) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- (6) Operating conditions:  $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial and industrial use.

- (7) For EPM7064S-5, EPM7064S-6, EPM7128S-6, EPM7160S-6, EPM7160S-7, EPM7192S-7, and EPM7256S-7 devices, these values are specified for a PIA fan-out of one LAB (16 macrocells). For each additional LAB fan-out in these devices, add an additional 0.1 ns to the PIA timing value.

- (8) The  $t_{LPA}$  parameter must be added to the  $t_{LAD}$ ,  $t_{LAC}$ ,  $t_{IC}$ ,  $t_{EN}$ ,  $t_{SEXP}$ ,  $t_{ACL}$ , and  $t_{CPPW}$  parameters for macrocells running in the low-power mode.

| Symbol            | Parameter                                   | Conditions     | Speed Grade |     |       |      |       |      |     |

|-------------------|---------------------------------------------|----------------|-------------|-----|-------|------|-------|------|-----|

|                   |                                             |                | -7          |     | -10   |      | -15   |      | -   |

|                   |                                             |                | Min         | Max | Min   | Max  | Min   | Max  |     |

| t <sub>PD1</sub>  | Input to non-registered output              | C1 = 35 pF     |             | 7.5 |       | 10.0 |       | 15.0 | ns  |

| t <sub>PD2</sub>  | I/O input to non-registered<br>output       | C1 = 35 pF     |             | 7.5 |       | 10.0 |       | 15.0 | ns  |

| t <sub>SU</sub>   | Global clock setup time                     |                | 3.9         |     | 7.0   |      | 11.0  |      | ns  |

| t <sub>H</sub>    | Global clock hold time                      |                | 0.0         |     | 0.0   |      | 0.0   |      | ns  |

| t <sub>FSU</sub>  | Global clock setup time of fast input       |                | 3.0         |     | 3.0   |      | 3.0   |      | ns  |

| t <sub>FH</sub>   | Global clock hold time of fast input        |                | 0.0         |     | 0.5   |      | 0.0   |      | ns  |

| t <sub>CO1</sub>  | Global clock to output delay                | C1 = 35 pF     |             | 4.7 |       | 5.0  |       | 8.0  | ns  |

| t <sub>CH</sub>   | Global clock high time                      |                | 3.0         |     | 4.0   |      | 5.0   |      | ns  |

| t <sub>CL</sub>   | Global clock low time                       |                | 3.0         |     | 4.0   |      | 5.0   |      | ns  |

| t <sub>ASU</sub>  | Array clock setup time                      |                | 0.8         |     | 2.0   |      | 4.0   |      | ns  |

| t <sub>AH</sub>   | Array clock hold time                       |                | 1.9         |     | 3.0   |      | 4.0   |      | ns  |

| t <sub>ACO1</sub> | Array clock to output delay                 | C1 = 35 pF     |             | 7.8 |       | 10.0 |       | 15.0 | ns  |

| t <sub>ACH</sub>  | Array clock high time                       |                | 3.0         |     | 4.0   |      | 6.0   |      | ns  |

| t <sub>ACL</sub>  | Array clock low time                        |                | 3.0         |     | 4.0   |      | 6.0   |      | ns  |

| t <sub>CPPW</sub> | Minimum pulse width for clear<br>and preset | (2)            | 3.0         |     | 4.0   |      | 6.0   |      | ns  |

| t <sub>ODH</sub>  | Output data hold time after<br>clock        | C1 = 35 pF (3) | 1.0         |     | 1.0   |      | 1.0   |      | ns  |

| t <sub>CNT</sub>  | Minimum global clock period                 |                |             | 7.8 |       | 10.0 |       | 13.0 | ns  |

| fcnt              | Maximum internal global clock frequency     | (4)            | 128.2       |     | 100.0 |      | 76.9  |      | MHz |

| t <sub>ACNT</sub> | Minimum array clock period                  |                |             | 7.8 |       | 10.0 |       | 13.0 | ns  |

| f <sub>acnt</sub> | Maximum internal array clock frequency      | (4)            | 128.2       |     | 100.0 |      | 76.9  |      | MHz |

| f <sub>MAX</sub>  | Maximum clock frequency                     | (5)            | 166.7       |     | 125.0 |      | 100.0 |      | MHz |

### Tables 37 and 38 show the EPM7256S AC operating conditions.

Figures 16 through 22 show the package pin-out diagrams for MAX 7000 devices.

#### Figure 16. 44-Pin Package Pin-Out Diagram

Package outlines not drawn to scale.

Notes:

- (1) The pin functions shown in parenthesis are only available in MAX 7000E and MAX 7000S devices.

- (2) JTAG ports are available in MAX 7000S devices only.

#### Figure 18. 84-Pin Package Pin-Out Diagram

Package outline not drawn to scale.

84-Pin PLCC

Notes:

- (1) Pins 6, 39, 46, and 79 are no-connect (N.C.) pins on EPM7096, EPM7160E, and EPM7160S devices.

- (2) The pin functions shown in parenthesis are only available in MAX 7000E and MAX 7000S devices.

- (3) JTAG ports are available in MAX 7000S devices only.

Figure 21. 192-Pin Package Pin-Out Diagram

Package outline not drawn to scale.

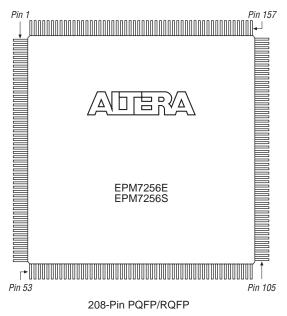

Figure 22. 208-Pin Package Pin-Out Diagram

Package outline not drawn to scale.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: literature@altera.com Copyright © 2005 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability

arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Altera Corporation