Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

### **Applications of Embedded - CPLDs**

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Obsolete                                                    |

| Programmable Type               | EE PLD                                                      |

| Delay Time tpd(1) Max           | 12 ns                                                       |

| Voltage Supply - Internal       | 4.75V ~ 5.25V                                               |

| Number of Logic Elements/Blocks | 12                                                          |

| Number of Macrocells            | 192                                                         |

| Number of Gates                 | 3750                                                        |

| Number of I/O                   | 124                                                         |

| Operating Temperature           | 0°C ~ 70°C (TA)                                             |

| Mounting Type                   | Through Hole                                                |

| Package / Case                  | 160-BPGA                                                    |

| Supplier Device Package         | 160-PGA (39.62x39.62)                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm7192egc160-12 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, and VeriBest

- Programming support

- Altera's Master Programming Unit (MPU) and programming hardware from third-party manufacturers program all MAX 7000 devices

- The BitBlaster<sup>TM</sup> serial download cable, ByteBlasterMV<sup>TM</sup> parallel port download cable, and MasterBlaster<sup>TM</sup> serial/universal serial bus (USB) download cable program MAX 7000S devices

# General Description

The MAX 7000 family of high-density, high-performance PLDs is based on Altera's second-generation MAX architecture. Fabricated with advanced CMOS technology, the EEPROM-based MAX 7000 family provides 600 to 5,000 usable gates, ISP, pin-to-pin delays as fast as 5 ns, and counter speeds of up to 175.4 MHz. MAX 7000S devices in the -5, -6, -7, and -10 speed grades as well as MAX 7000 and MAX 7000E devices in -5, -6, -7, -10P, and -12P speed grades comply with the PCI Special Interest Group (PCI SIG) *PCI Local Bus Specification, Revision 2.2.* See Table 3 for available speed grades.

| Device   | Speed Grade |          |          |          |          |          |          |          |          |          |  |

|----------|-------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--|

|          | -5          | -6       | -7       | -10P     | -10      | -12P     | -12      | -15      | -15T     | -20      |  |

| EPM7032  |             | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |  |

| EPM7032S | <b>✓</b>    | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          |          |          |          |          |  |

| EPM7064  |             | <b>✓</b> | <b>✓</b> |          | ~        |          | <b>✓</b> | <b>✓</b> |          |          |  |

| EPM7064S | <b>✓</b>    | <b>✓</b> | <b>✓</b> |          | ~        |          |          |          |          |          |  |

| EPM7096  |             |          | <b>✓</b> |          | ~        |          | <b>✓</b> | <b>✓</b> |          |          |  |

| EPM7128E |             |          | <b>✓</b> | <b>✓</b> | ~        |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |  |

| EPM7128S |             | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |          |          | <b>✓</b> |          |          |  |

| EPM7160E |             |          |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |  |

| EPM7160S |             | <b>✓</b> | <b>✓</b> |          | ~        |          |          | <b>✓</b> |          |          |  |

| EPM7192E |             |          |          |          |          | <b>✓</b> | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |  |

| EPM7192S |             |          | <b>✓</b> |          | <b>✓</b> |          |          | <b>✓</b> |          |          |  |

| EPM7256E |             |          |          |          |          | <b>✓</b> | <b>✓</b> | <b>✓</b> |          | <b>✓</b> |  |

| EPM7256S |             |          | <b>✓</b> |          | <b>✓</b> |          |          | <b>✓</b> |          |          |  |

The MAX 7000 architecture supports 100% TTL emulation and high-density integration of SSI, MSI, and LSI logic functions. The MAX 7000 architecture easily integrates multiple devices ranging from PALs, GALs, and 22V10s to MACH and pLSI devices. MAX 7000 devices are available in a wide range of packages, including PLCC, PGA, PQFP, RQFP, and TQFP packages. See Table 5.

| Table 5. M. | AX 7000            | ) Maxim            | um Use             | r I/O Pii          | ıs N               | ote (1)             |                     |                     |                    |                    |                     |                     |

|-------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|---------------------|---------------------|

| Device      | 44-<br>Pin<br>PLCC | 44-<br>Pin<br>PQFP | 44-<br>Pin<br>TQFP | 68-<br>Pin<br>PLCC | 84-<br>Pin<br>PLCC | 100-<br>Pin<br>PQFP | 100-<br>Pin<br>TQFP | 160-<br>Pin<br>PQFP | 160-<br>Pin<br>PGA | 192-<br>Pin<br>PGA | 208-<br>Pin<br>PQFP | 208-<br>Pin<br>RQFP |

| EPM7032     | 36                 | 36                 | 36                 |                    |                    |                     |                     |                     |                    |                    |                     |                     |

| EPM7032S    | 36                 |                    | 36                 |                    |                    |                     |                     |                     |                    |                    |                     |                     |

| EPM7064     | 36                 |                    | 36                 | 52                 | 68                 | 68                  |                     |                     |                    |                    |                     |                     |

| EPM7064S    | 36                 |                    | 36                 |                    | 68                 |                     | 68                  |                     |                    |                    |                     |                     |

| EPM7096     |                    |                    |                    | 52                 | 64                 | 76                  |                     |                     |                    |                    |                     |                     |

| EPM7128E    |                    |                    |                    |                    | 68                 | 84                  |                     | 100                 |                    |                    |                     |                     |

| EPM7128S    |                    |                    |                    |                    | 68                 | 84                  | 84 (2)              | 100                 |                    |                    |                     |                     |

| EPM7160E    |                    |                    |                    |                    | 64                 | 84                  |                     | 104                 |                    |                    |                     |                     |

| EPM7160S    |                    |                    |                    |                    | 64                 |                     | 84 (2)              | 104                 |                    |                    |                     |                     |

| EPM7192E    |                    |                    |                    |                    |                    |                     |                     | 124                 | 124                |                    |                     |                     |

| EPM7192S    |                    |                    |                    |                    |                    |                     |                     | 124                 |                    |                    |                     |                     |

| EPM7256E    |                    |                    |                    |                    |                    |                     |                     | 132 (2)             |                    | 164                |                     | 164                 |

| EPM7256S    |                    |                    |                    |                    |                    |                     |                     |                     |                    |                    | 164 (2)             | 164                 |

#### Notes:

- When the JTAG interface in MAX 7000S devices is used for either boundary-scan testing or for ISP, four I/O pins become JTAG pins.

- (2) Perform a complete thermal analysis before committing a design to this device package. For more information, see the Operating Requirements for Altera Devices Data Sheet.

MAX 7000 devices use CMOS EEPROM cells to implement logic functions. The user-configurable MAX 7000 architecture accommodates a variety of independent combinatorial and sequential logic functions. The devices can be reprogrammed for quick and efficient iterations during design development and debug cycles, and can be programmed and erased up to 100 times.

Each LAB is fed by the following signals:

- 36 signals from the PIA that are used for general logic inputs

- Global controls that are used for secondary register functions

- Direct input paths from I/O pins to the registers that are used for fast setup times for MAX 7000E and MAX 7000S devices

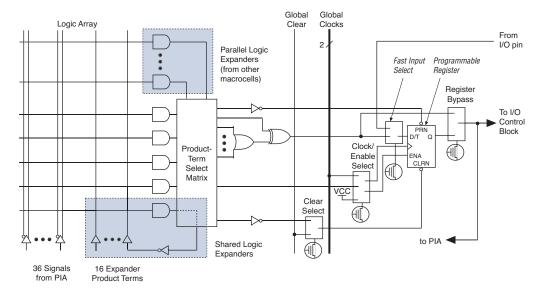

### **Macrocells**

The MAX 7000 macrocell can be individually configured for either sequential or combinatorial logic operation. The macrocell consists of three functional blocks: the logic array, the product-term select matrix, and the programmable register. The macrocell of EPM7032, EPM7064, and EPM7096 devices is shown in Figure 3.

Figure 3. EPM7032, EPM7064 & EPM7096 Device Macrocell

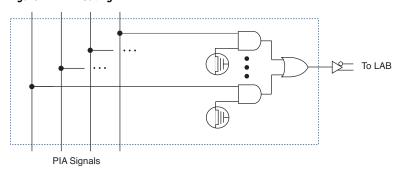

### Programmable Interconnect Array

Logic is routed between LABs via the programmable interconnect array (PIA). This global bus is a programmable path that connects any signal source to any destination on the device. All MAX 7000 dedicated inputs, I/O pins, and macrocell outputs feed the PIA, which makes the signals available throughout the entire device. Only the signals required by each LAB are actually routed from the PIA into the LAB. Figure 7 shows how the PIA signals are routed into the LAB. An EEPROM cell controls one input to a 2-input AND gate, which selects a PIA signal to drive into the LAB.

Figure 7. PIA Routing

While the routing delays of channel-based routing schemes in masked or FPGAs are cumulative, variable, and path-dependent, the MAX 7000 PIA has a fixed delay. The PIA thus eliminates skew between signals and makes timing performance easy to predict.

### I/O Control Blocks

The I/O control block allows each I/O pin to be individually configured for input, output, or bidirectional operation. All I/O pins have a tri-state buffer that is individually controlled by one of the global output enable signals or directly connected to ground or  $V_{\rm CC}$ . Figure 8 shows the I/O control block for the MAX 7000 family. The I/O control block of EPM7032, EPM7064, and EPM7096 devices has two global output enable signals that are driven by two dedicated active-low output enable pins (OE1 and OE2). The I/O control block of MAX 7000E and MAX 7000S devices has six global output enable signals that are driven by the true or complement of two output enable signals, a subset of the I/O pins, or a subset of the I/O macrocells.

When the tri-state buffer control is connected to ground, the output is tri-stated (high impedance) and the I/O pin can be used as a dedicated input. When the tri-state buffer control is connected to  $V_{CC}$ , the output is enabled.

The MAX 7000 architecture provides dual I/O feedback, in which macrocell and pin feedbacks are independent. When an I/O pin is configured as an input, the associated macrocell can be used for buried logic.

# In-System Programmability (ISP)

MAX 7000S devices are in-system programmable via an industry-standard 4-pin Joint Test Action Group (JTAG) interface (IEEE Std. 1149.1-1990). ISP allows quick, efficient iterations during design development and debugging cycles. The MAX 7000S architecture internally generates the high programming voltage required to program EEPROM cells, allowing in-system programming with only a single 5.0 V power supply. During in-system programming, the I/O pins are tri-stated and pulled-up to eliminate board conflicts. The pull-up value is nominally 50 k%.

ISP simplifies the manufacturing flow by allowing devices to be mounted on a printed circuit board with standard in-circuit test equipment before they are programmed. MAX 7000S devices can be programmed by downloading the information via in-circuit testers (ICT), embedded processors, or the Altera MasterBlaster, ByteBlasterMV, ByteBlaster, BitBlaster download cables. (The ByteBlaster cable is obsolete and is replaced by the ByteBlasterMV cable, which can program and configure 2.5-V, 3.3-V, and 5.0-V devices.) Programming the devices after they are placed on the board eliminates lead damage on high-pin-count packages (e.g., QFP packages) due to device handling and allows devices to be reprogrammed after a system has already shipped to the field. For example, product upgrades can be performed in the field via software or modem.

In-system programming can be accomplished with either an adaptive or constant algorithm. An adaptive algorithm reads information from the unit and adapts subsequent programming steps to achieve the fastest possible programming time for that unit. Because some in-circuit testers cannot support an adaptive algorithm, Altera offers devices tested with a constant algorithm. Devices tested to the constant algorithm have an "F" suffix in the ordering code.

The Jam<sup>TM</sup> Standard Test and Programming Language (STAPL) can be used to program MAX 7000S devices with in-circuit testers, PCs, or embedded processor.

The programming times described in Tables 6 through 8 are associated with the worst-case method using the enhanced ISP algorithm.

| Table 6. MAX 7000S t <sub>PU</sub> | <sub>LSE</sub> & Cycle <sub>TCK</sub> Values | 3                     |                         |                       |

|------------------------------------|----------------------------------------------|-----------------------|-------------------------|-----------------------|

| Device                             | Progra                                       | ımming                | Stand-Alone             | Verification          |

|                                    | t <sub>PPULSE</sub> (s)                      | Cycle <sub>PTCK</sub> | t <sub>VPULSE</sub> (s) | Cycle <sub>VTCK</sub> |

| EPM7032S                           | 4.02                                         | 342,000               | 0.03                    | 200,000               |

| EPM7064S                           | 4.50                                         | 504,000               | 0.03                    | 308,000               |

| EPM7128S                           | 5.11                                         | 832,000               | 0.03                    | 528,000               |

| EPM7160S                           | 5.35                                         | 1,001,000             | 0.03                    | 640,000               |

| EPM7192S                           | 5.71                                         | 1,192,000             | 0.03                    | 764,000               |

| EPM7256S                           | 6.43                                         | 1,603,000             | 0.03                    | 1,024,000             |

Tables 7 and 8 show the in-system programming and stand alone verification times for several common test clock frequencies.

| Table 7. MAX 7000S In-System Programming Times for Different Test Clock Frequencies |        |       |       |       |         |         |         |        |       |  |  |

|-------------------------------------------------------------------------------------|--------|-------|-------|-------|---------|---------|---------|--------|-------|--|--|

| Device                                                                              |        |       |       | 1     | TCK     |         |         |        | Units |  |  |

|                                                                                     | 10 MHz | 5 MHz | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |       |  |  |

| EPM7032S                                                                            | 4.06   | 4.09  | 4.19  | 4.36  | 4.71    | 5.73    | 7.44    | 10.86  | s     |  |  |

| EPM7064S                                                                            | 4.55   | 4.60  | 4.76  | 5.01  | 5.51    | 7.02    | 9.54    | 14.58  | S     |  |  |

| EPM7128S                                                                            | 5.19   | 5.27  | 5.52  | 5.94  | 6.77    | 9.27    | 13.43   | 21.75  | S     |  |  |

| EPM7160S                                                                            | 5.45   | 5.55  | 5.85  | 6.35  | 7.35    | 10.35   | 15.36   | 25.37  | S     |  |  |

| EPM7192S                                                                            | 5.83   | 5.95  | 6.30  | 6.90  | 8.09    | 11.67   | 17.63   | 29.55  | S     |  |  |

| EPM7256S                                                                            | 6.59   | 6.75  | 7.23  | 8.03  | 9.64    | 14.45   | 22.46   | 38.49  | S     |  |  |

| Table 8. MAX 7000S Stand-Alone Verification Times for Different Test Clock Frequencies |        |       |       |       |         |         |         |        |       |  |  |

|----------------------------------------------------------------------------------------|--------|-------|-------|-------|---------|---------|---------|--------|-------|--|--|

| Device                                                                                 |        |       |       | 1     | тск     |         |         |        | Units |  |  |

|                                                                                        | 10 MHz | 5 MHz | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |       |  |  |

| EPM7032S                                                                               | 0.05   | 0.07  | 0.13  | 0.23  | 0.43    | 1.03    | 2.03    | 4.03   | s     |  |  |

| EPM7064S                                                                               | 0.06   | 0.09  | 0.18  | 0.34  | 0.64    | 1.57    | 3.11    | 6.19   | S     |  |  |

| EPM7128S                                                                               | 0.08   | 0.14  | 0.29  | 0.56  | 1.09    | 2.67    | 5.31    | 10.59  | S     |  |  |

| EPM7160S                                                                               | 0.09   | 0.16  | 0.35  | 0.67  | 1.31    | 3.23    | 6.43    | 12.83  | S     |  |  |

| EPM7192S                                                                               | 0.11   | 0.18  | 0.41  | 0.79  | 1.56    | 3.85    | 7.67    | 15.31  | S     |  |  |

| EPM7256S                                                                               | 0.13   | 0.24  | 0.54  | 1.06  | 2.08    | 5.15    | 10.27   | 20.51  | S     |  |  |

# **Design Security**

All MAX 7000 devices contain a programmable security bit that controls access to the data programmed into the device. When this bit is programmed, a proprietary design implemented in the device cannot be copied or retrieved. This feature provides a high level of design security because programmed data within EEPROM cells is invisible. The security bit that controls this function, as well as all other programmed data, is reset only when the device is reprogrammed.

# **Generic Testing**

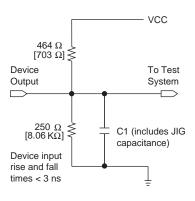

Each MAX 7000 device is functionally tested. Complete testing of each programmable EEPROM bit and all internal logic elements ensures 100% programming yield. AC test measurements are taken under conditions equivalent to those shown in Figure 10. Test patterns can be used and then erased during early stages of the production flow.

### Figure 10. MAX 7000 AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast ground-current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground. significant reductions in observable noise immunity can result. Numbers in brackets are for 2.5-V devices and outputs. Numbers without brackets are for 3.3-V devices and outputs.

# QFP Carrier & Development Socket

MAX 7000 and MAX 7000E devices in QFP packages with 100 or more pins are shipped in special plastic carriers to protect the QFP leads. The carrier is used with a prototype development socket and special programming hardware available from Altera. This carrier technology makes it possible to program, test, erase, and reprogram a device without exposing the leads to mechanical stress.

For detailed information and carrier dimensions, refer to the *QFP Carrier* & *Development Socket Data Sheet*.

MAX 7000S devices are not shipped in carriers.

| Symbol          | Parameter                                  | Conditions                                                    | Min                     | Max                      | Unit |

|-----------------|--------------------------------------------|---------------------------------------------------------------|-------------------------|--------------------------|------|

| V <sub>IH</sub> | High-level input voltage                   |                                                               | 2.0                     | V <sub>CCINT</sub> + 0.5 | V    |

| V <sub>IL</sub> | Low-level input voltage                    |                                                               | -0.5 (8)                | 0.8                      | V    |

| V <sub>OH</sub> | 5.0-V high-level TTL output voltage        | $I_{OH} = -4 \text{ mA DC}, V_{CCIO} = 4.75 \text{ V} (10)$   | 2.4                     |                          | V    |

|                 | 3.3-V high-level TTL output voltage        | $I_{OH} = -4 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (10)$  | 2.4                     |                          | V    |

| v               | 3.3-V high-level CMOS output voltage       | $I_{OH} = -0.1 \text{ mA DC}, V_{CCIO} = 3.0 \text{ V } (10)$ | V <sub>CCIO</sub> - 0.2 |                          | V    |

| V <sub>OL</sub> | 5.0-V low-level TTL output voltage         | I <sub>OL</sub> = 12 mA DC, V <sub>CCIO</sub> = 4.75 V (11)   |                         | 0.45                     | V    |

|                 | 3.3-V low-level TTL output voltage         | I <sub>OL</sub> = 12 mA DC, V <sub>CCIO</sub> = 3.00 V (11)   |                         | 0.45                     | V    |

|                 | 3.3-V low-level CMOS output voltage        | $I_{OL} = 0.1 \text{ mA DC}, V_{CCIO} = 3.0 V(11)$            |                         | 0.2                      | V    |

| I <sub>I</sub>  | Leakage current of dedicated input pins    | V <sub>I</sub> = -0.5 to 5.5 V (11)                           | -10                     | 10                       | μА   |

| l <sub>OZ</sub> | I/O pin tri-state output off-state current | V <sub>I</sub> = -0.5 to 5.5 V (11), (12)                     | -40                     | 40                       | μА   |

| Table 1          | Table 16. MAX 7000 5.0-V Device Capacitance: EPM7032, EPM7064 & EPM7096 Devices       Note (13) |                                     |     |     |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|

| Symbol           | Parameter                                                                                       | Conditions                          | Min | Max | Unit |  |  |  |

| C <sub>IN</sub>  | Input pin capacitance                                                                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |  |

| C <sub>I/O</sub> | I/O pin capacitance                                                                             | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 12  | pF   |  |  |  |

| Table 1          | 7. MAX 7000 5.0-V Device Capa | acitance: MAX 7000E Devices Note    | (13) |     |      |

|------------------|-------------------------------|-------------------------------------|------|-----|------|

| Symbol           | Parameter                     | Conditions                          | Min  | Max | Unit |

| C <sub>IN</sub>  | Input pin capacitance         | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |      | 15  | pF   |

| C <sub>I/O</sub> | I/O pin capacitance           | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |      | 15  | pF   |

| Table 1          | Table 18. MAX 7000 5.0-V Device Capacitance: MAX 7000S Devices Note (13) |                                     |     |     |      |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|--|--|

| Symbol           | Parameter                                                                | Conditions                          | Min | Max | Unit |  |  |  |  |  |

| C <sub>IN</sub>  | Dedicated input pin capacitance                                          | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |  |  |  |  |

| C <sub>I/O</sub> | I/O pin capacitance                                                      | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |  |  |  |  |

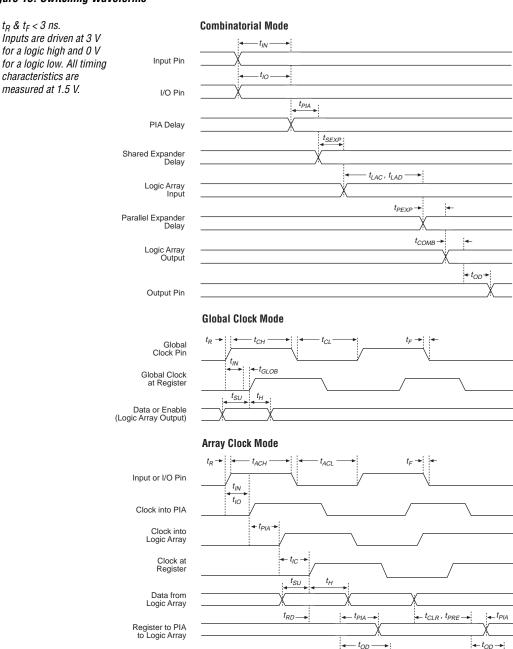

### Figure 13. Switching Waveforms

30 Altera Corporation

Register Output to Pin

| Symbol            | Parameter                                                                                 | Conditions     | Speed | Grade -6 | Speed ( | Grade -7 | Unit |

|-------------------|-------------------------------------------------------------------------------------------|----------------|-------|----------|---------|----------|------|

|                   |                                                                                           |                | Min   | Max      | Min     | Max      |      |

| t <sub>IN</sub>   | Input pad and buffer delay                                                                |                |       | 0.4      |         | 0.5      | ns   |

| $t_{IO}$          | I/O input pad and buffer delay                                                            |                |       | 0.4      |         | 0.5      | ns   |

| t <sub>FIN</sub>  | Fast input delay                                                                          | (2)            |       | 0.8      |         | 1.0      | ns   |

| t <sub>SEXP</sub> | Shared expander delay                                                                     |                |       | 3.5      |         | 4.0      | ns   |

| $t_{PEXP}$        | Parallel expander delay                                                                   |                |       | 0.8      |         | 0.8      | ns   |

| $t_{LAD}$         | Logic array delay                                                                         |                |       | 2.0      |         | 3.0      | ns   |

| t <sub>LAC</sub>  | Logic control array delay                                                                 |                |       | 2.0      |         | 3.0      | ns   |

| t <sub>IOE</sub>  | Internal output enable delay                                                              | (2)            |       |          |         | 2.0      | ns   |

| t <sub>OD1</sub>  | Output buffer and pad delay<br>Slow slew rate = off, V <sub>CCIO</sub> = 5.0 V            | C1 = 35 pF     |       | 2.0      |         | 2.0      | ns   |

| t <sub>OD2</sub>  | Output buffer and pad delay<br>Slow slew rate = off, V <sub>CCIO</sub> = 3.3 V            | C1 = 35 pF (7) |       | 2.5      |         | 2.5      | ns   |

| t <sub>OD3</sub>  | Output buffer and pad delay<br>Slow slew rate = on,<br>V <sub>CCIO</sub> = 5.0 V or 3.3 V | C1 = 35 pF (2) |       | 7.0      |         | 7.0      | ns   |

| t <sub>ZX1</sub>  | Output buffer enable delay<br>Slow slew rate = off, V <sub>CCIO</sub> = 5.0 V             | C1 = 35 pF     |       | 4.0      |         | 4.0      | ns   |

| t <sub>ZX2</sub>  | Output buffer enable delay<br>Slow slew rate = off, V <sub>CCIO</sub> = 3.3 V             | C1 = 35 pF (7) |       | 4.5      |         | 4.5      | ns   |

| t <sub>ZX3</sub>  | Output buffer enable delay<br>Slow slew rate = on<br>V <sub>CCIO</sub> = 5.0 V or 3.3 V   | C1 = 35 pF (2) |       | 9.0      |         | 9.0      | ns   |

| $t_{XZ}$          | Output buffer disable delay                                                               | C1 = 5 pF      |       | 4.0      |         | 4.0      | ns   |

| $t_{SU}$          | Register setup time                                                                       |                | 3.0   |          | 3.0     |          | ns   |

| $t_H$             | Register hold time                                                                        |                | 1.5   |          | 2.0     |          | ns   |

| t <sub>FSU</sub>  | Register setup time of fast input                                                         | (2)            | 2.5   |          | 3.0     |          | ns   |

| $t_{FH}$          | Register hold time of fast input                                                          | (2)            | 0.5   |          | 0.5     |          | ns   |

| $t_{RD}$          | Register delay                                                                            |                |       | 0.8      |         | 1.0      | ns   |

| t <sub>COMB</sub> | Combinatorial delay                                                                       |                |       | 0.8      |         | 1.0      | ns   |

| t <sub>IC</sub>   | Array clock delay                                                                         |                |       | 2.5      |         | 3.0      | ns   |

| t <sub>EN</sub>   | Register enable time                                                                      |                |       | 2.0      |         | 3.0      | ns   |

| t <sub>GLOB</sub> | Global control delay                                                                      |                |       | 0.8      |         | 1.0      | ns   |

| t <sub>PRE</sub>  | Register preset time                                                                      |                |       | 2.0      |         | 2.0      | ns   |

| t <sub>CLR</sub>  | Register clear time                                                                       |                |       | 2.0      |         | 2.0      | ns   |

| t <sub>PIA</sub>  | PIA delay                                                                                 |                |       | 0.8      |         | 1.0      | ns   |

| $t_{LPA}$         | Low-power adder                                                                           | (8)            |       | 10.0     |         | 10.0     | ns   |

| Table 2           | 5. MAX 7000 & MAX 7000E                  | External Timing I | Paramete | ers / | lote (1) |       |      |      |      |

|-------------------|------------------------------------------|-------------------|----------|-------|----------|-------|------|------|------|

| Symbol            | Parameter                                | Conditions        |          |       | Speed    | Grade |      |      | Unit |

|                   |                                          |                   | -        | 15    | -1       | 5T    | -2   | 20   |      |

|                   |                                          |                   | Min      | Max   | Min      | Max   | Min  | Max  |      |

| t <sub>PD1</sub>  | Input to non-registered output           | C1 = 35 pF        |          | 15.0  |          | 15.0  |      | 20.0 | ns   |

| t <sub>PD2</sub>  | I/O input to non-registered output       | C1 = 35 pF        |          | 15.0  |          | 15.0  |      | 20.0 | ns   |

| t <sub>SU</sub>   | Global clock setup time                  |                   | 11.0     |       | 11.0     |       | 12.0 |      | ns   |

| t <sub>H</sub>    | Global clock hold time                   |                   | 0.0      |       | 0.0      |       | 0.0  |      | ns   |

| t <sub>FSU</sub>  | Global clock setup time of fast input    | (2)               | 3.0      |       | -        |       | 5.0  |      | ns   |

| t <sub>FH</sub>   | Global clock hold time of fast input     | (2)               | 0.0      |       | -        |       | 0.0  |      | ns   |

| t <sub>CO1</sub>  | Global clock to output delay             | C1 = 35 pF        |          | 8.0   |          | 8.0   |      | 12.0 | ns   |

| t <sub>CH</sub>   | Global clock high time                   |                   | 5.0      |       | 6.0      |       | 6.0  |      | ns   |

| t <sub>CL</sub>   | Global clock low time                    |                   | 5.0      |       | 6.0      |       | 6.0  |      | ns   |

| t <sub>ASU</sub>  | Array clock setup time                   |                   | 4.0      |       | 4.0      |       | 5.0  |      | ns   |

| t <sub>AH</sub>   | Array clock hold time                    |                   | 4.0      |       | 4.0      |       | 5.0  |      | ns   |

| t <sub>ACO1</sub> | Array clock to output delay              | C1 = 35 pF        |          | 15.0  |          | 15.0  |      | 20.0 | ns   |

| t <sub>ACH</sub>  | Array clock high time                    |                   | 6.0      |       | 6.5      |       | 8.0  |      | ns   |

| t <sub>ACL</sub>  | Array clock low time                     |                   | 6.0      |       | 6.5      |       | 8.0  |      | ns   |

| t <sub>CPPW</sub> | Minimum pulse width for clear and preset | (3)               | 6.0      |       | 6.5      |       | 8.0  |      | ns   |

| t <sub>ODH</sub>  | Output data hold time after clock        | C1 = 35 pF (4)    | 1.0      |       | 1.0      |       | 1.0  |      | ns   |

| t <sub>CNT</sub>  | Minimum global clock period              |                   |          | 13.0  |          | 13.0  |      | 16.0 | ns   |

| f <sub>CNT</sub>  | Maximum internal global clock frequency  | (5)               | 76.9     |       | 76.9     |       | 62.5 |      | MHz  |

| t <sub>ACNT</sub> | Minimum array clock period               |                   |          | 13.0  |          | 13.0  |      | 16.0 | ns   |

| f <sub>ACNT</sub> | Maximum internal array clock frequency   | (5)               | 76.9     |       | 76.9     |       | 62.5 |      | MHz  |

| f <sub>MAX</sub>  | Maximum clock frequency                  | (6)               | 100      |       | 83.3     | _     | 83.3 | _    | MHz  |

#### Notes to tables:

- (1) These values are specified under the recommended operating conditions shown in Table 14. See Figure 13 for more information on switching waveforms.

- (2) This parameter applies to MAX 7000E devices only.

- This minimum pulse width for preset and clear applies for both global clear and array controls. The  $t_{LPA}$  parameter must be added to this minimum width if the clear or reset signal incorporates the  $t_{LAD}$  parameter into the signal path.

- (4) This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This parameter applies for both global and array clocking.

- (5) These parameters are measured with a 16-bit loadable, enabled, up/down counter programmed into each LAB.

- (6) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- (7) Operating conditions:  $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial and industrial use.

- (8) The  $t_{LPA}$  parameter must be added to the  $t_{LAD}$ ,  $t_{LAC}$ ,  $t_{IC}$ ,  $t_{EN}$ ,  $t_{SEXP}$ ,  $t_{ACL}$ , and  $t_{CPPW}$  parameters for macrocells running in the low-power mode.

Tables 27 and 28 show the EPM7032S AC operating conditions.

| Table 2           | Table 27. EPM7032S External Timing Parameters (Part 1 of 2) Note (1) |                |             |     |       |     |       |     |       |      |     |  |  |

|-------------------|----------------------------------------------------------------------|----------------|-------------|-----|-------|-----|-------|-----|-------|------|-----|--|--|

| Symbol            | Parameter                                                            | Conditions     | Speed Grade |     |       |     |       |     |       |      |     |  |  |

|                   |                                                                      |                | -5          |     | -6    |     | -7    |     | -10   |      |     |  |  |

|                   |                                                                      |                | Min         | Max | Min   | Max | Min   | Max | Min   | Max  |     |  |  |

| t <sub>PD1</sub>  | Input to non-registered output                                       | C1 = 35 pF     |             | 5.0 |       | 6.0 |       | 7.5 |       | 10.0 | ns  |  |  |

| t <sub>PD2</sub>  | I/O input to non-registered output                                   | C1 = 35 pF     |             | 5.0 |       | 6.0 |       | 7.5 |       | 10.0 | ns  |  |  |

| t <sub>SU</sub>   | Global clock setup time                                              |                | 2.9         |     | 4.0   |     | 5.0   |     | 7.0   |      | ns  |  |  |

| t <sub>H</sub>    | Global clock hold time                                               |                | 0.0         |     | 0.0   |     | 0.0   |     | 0.0   |      | ns  |  |  |

| t <sub>FSU</sub>  | Global clock setup time of fast input                                |                | 2.5         |     | 2.5   |     | 2.5   |     | 3.0   |      | ns  |  |  |

| t <sub>FH</sub>   | Global clock hold time of fast input                                 |                | 0.0         |     | 0.0   |     | 0.0   |     | 0.5   |      | ns  |  |  |

| t <sub>CO1</sub>  | Global clock to output delay                                         | C1 = 35 pF     |             | 3.2 |       | 3.5 |       | 4.3 |       | 5.0  | ns  |  |  |

| t <sub>CH</sub>   | Global clock high time                                               |                | 2.0         |     | 2.5   |     | 3.0   |     | 4.0   |      | ns  |  |  |

| t <sub>CL</sub>   | Global clock low time                                                |                | 2.0         |     | 2.5   |     | 3.0   |     | 4.0   |      | ns  |  |  |

| t <sub>ASU</sub>  | Array clock setup time                                               |                | 0.7         |     | 0.9   |     | 1.1   |     | 2.0   |      | ns  |  |  |

| t <sub>AH</sub>   | Array clock hold time                                                |                | 1.8         |     | 2.1   |     | 2.7   |     | 3.0   |      | ns  |  |  |

| t <sub>ACO1</sub> | Array clock to output delay                                          | C1 = 35 pF     |             | 5.4 |       | 6.6 |       | 8.2 |       | 10.0 | ns  |  |  |

| t <sub>ACH</sub>  | Array clock high time                                                |                | 2.5         |     | 2.5   |     | 3.0   |     | 4.0   |      | ns  |  |  |

| t <sub>ACL</sub>  | Array clock low time                                                 |                | 2.5         |     | 2.5   |     | 3.0   |     | 4.0   |      | ns  |  |  |

| t <sub>CPPW</sub> | Minimum pulse width for clear and preset                             | (2)            | 2.5         |     | 2.5   |     | 3.0   |     | 4.0   |      | ns  |  |  |

| t <sub>ODH</sub>  | Output data hold time after clock                                    | C1 = 35 pF (3) | 1.0         |     | 1.0   |     | 1.0   |     | 1.0   |      | ns  |  |  |

| t <sub>CNT</sub>  | Minimum global clock period                                          |                |             | 5.7 |       | 7.0 |       | 8.6 |       | 10.0 | ns  |  |  |

| f <sub>CNT</sub>  | Maximum internal global clock frequency                              | (4)            | 175.4       |     | 142.9 |     | 116.3 |     | 100.0 |      | MHz |  |  |

| t <sub>ACNT</sub> | Minimum array clock period                                           |                |             | 5.7 |       | 7.0 |       | 8.6 |       | 10.0 | ns  |  |  |

| Table 2           | Table 27. EPM7032S External Timing Parameters (Part 2 of 2) Note (1) |            |       |              |       |       |       |     |       |     |      |  |

|-------------------|----------------------------------------------------------------------|------------|-------|--------------|-------|-------|-------|-----|-------|-----|------|--|

| Symbol            | Parameter                                                            | Conditions |       |              |       | Speed | Grade | 1   |       |     | Unit |  |

|                   |                                                                      |            | -     | -5 -6 -7 -10 |       |       |       |     |       |     |      |  |

|                   |                                                                      |            | Min   | Max          | Min   | Max   | Min   | Max | Min   | Max |      |  |

| f <sub>ACNT</sub> | Maximum internal array clock frequency                               | (4)        | 175.4 |              | 142.9 |       | 116.3 |     | 100.0 |     | MHz  |  |

| f <sub>MAX</sub>  | Maximum clock frequency                                              | (5)        | 250.0 |              | 200.0 |       | 166.7 |     | 125.0 |     | MHz  |  |

| Table 2           | 8. EPM7032S Internal Tim          | ing Parameter  | <b>s</b> /  | Note (1) |     |     |     |     |     |     |    |  |

|-------------------|-----------------------------------|----------------|-------------|----------|-----|-----|-----|-----|-----|-----|----|--|

| Symbol            | Parameter                         | Conditions     | Speed Grade |          |     |     |     |     |     |     |    |  |

|                   |                                   |                | -5          |          | -6  |     | -7  |     | -10 |     |    |  |

|                   |                                   |                | Min         | Max      | Min | Max | Min | Max | Min | Max |    |  |

| t <sub>IN</sub>   | Input pad and buffer delay        |                |             | 0.2      |     | 0.2 |     | 0.3 |     | 0.5 | ns |  |

| t <sub>IO</sub>   | I/O input pad and buffer delay    |                |             | 0.2      |     | 0.2 |     | 0.3 |     | 0.5 | ns |  |

| t <sub>FIN</sub>  | Fast input delay                  |                |             | 2.2      |     | 2.1 |     | 2.5 |     | 1.0 | ns |  |

| t <sub>SEXP</sub> | Shared expander delay             |                |             | 3.1      |     | 3.8 |     | 4.6 |     | 5.0 | ns |  |

| t <sub>PEXP</sub> | Parallel expander delay           |                |             | 0.9      |     | 1.1 |     | 1.4 |     | 0.8 | ns |  |

| t <sub>LAD</sub>  | Logic array delay                 |                |             | 2.6      |     | 3.3 |     | 4.0 |     | 5.0 | ns |  |

| t <sub>LAC</sub>  | Logic control array delay         |                |             | 2.5      |     | 3.3 |     | 4.0 |     | 5.0 | ns |  |

| t <sub>IOE</sub>  | Internal output enable delay      |                |             | 0.7      |     | 0.8 |     | 1.0 |     | 2.0 | ns |  |

| t <sub>OD1</sub>  | Output buffer and pad delay       | C1 = 35 pF     |             | 0.2      |     | 0.3 |     | 0.4 |     | 1.5 | ns |  |

| t <sub>OD2</sub>  | Output buffer and pad delay       | C1 = 35 pF (6) |             | 0.7      |     | 0.8 |     | 0.9 |     | 2.0 | ns |  |

| t <sub>OD3</sub>  | Output buffer and pad delay       | C1 = 35 pF     |             | 5.2      |     | 5.3 |     | 5.4 |     | 5.5 | ns |  |

| t <sub>ZX1</sub>  | Output buffer enable delay        | C1 = 35 pF     |             | 4.0      |     | 4.0 |     | 4.0 |     | 5.0 | ns |  |

| t <sub>ZX2</sub>  | Output buffer enable delay        | C1 = 35 pF (6) |             | 4.5      |     | 4.5 |     | 4.5 |     | 5.5 | ns |  |

| t <sub>ZX3</sub>  | Output buffer enable delay        | C1 = 35 pF     |             | 9.0      |     | 9.0 |     | 9.0 |     | 9.0 | ns |  |

| t <sub>XZ</sub>   | Output buffer disable delay       | C1 = 5 pF      |             | 4.0      |     | 4.0 |     | 4.0 |     | 5.0 | ns |  |

| t <sub>SU</sub>   | Register setup time               |                | 0.8         |          | 1.0 |     | 1.3 |     | 2.0 |     | ns |  |

| t <sub>H</sub>    | Register hold time                |                | 1.7         |          | 2.0 |     | 2.5 |     | 3.0 |     | ns |  |

| t <sub>FSU</sub>  | Register setup time of fast input |                | 1.9         |          | 1.8 |     | 1.7 |     | 3.0 |     | ns |  |

| t <sub>FH</sub>   | Register hold time of fast input  |                | 0.6         |          | 0.7 |     | 0.8 |     | 0.5 |     | ns |  |

| t <sub>RD</sub>   | Register delay                    |                |             | 1.2      |     | 1.6 |     | 1.9 |     | 2.0 | ns |  |

| t <sub>COMB</sub> | Combinatorial delay               |                |             | 0.9      |     | 1.1 |     | 1.4 |     | 2.0 | ns |  |

| t <sub>IC</sub>   | Array clock delay                 |                |             | 2.7      |     | 3.4 |     | 4.2 |     | 5.0 | ns |  |

| t <sub>EN</sub>   | Register enable time              |                |             | 2.6      |     | 3.3 |     | 4.0 |     | 5.0 | ns |  |

| t <sub>GLOB</sub> | Global control delay              |                |             | 1.6      |     | 1.4 |     | 1.7 |     | 1.0 | ns |  |

| t <sub>PRE</sub>  | Register preset time              |                |             | 2.0      |     | 2.4 |     | 3.0 |     | 3.0 | ns |  |

| t <sub>CLR</sub>  | Register clear time               |                |             | 2.0      |     | 2.4 |     | 3.0 |     | 3.0 | ns |  |

| Table 28. EPM7032S Internal Timing Parameters Note (1) |                 |            |              |      |     |       |       |      |     |      |      |

|--------------------------------------------------------|-----------------|------------|--------------|------|-----|-------|-------|------|-----|------|------|

| Symbol                                                 | Parameter       | Conditions |              |      |     | Speed | Grade |      |     |      | Unit |

|                                                        |                 |            | -5 -6 -7 -10 |      |     |       |       |      |     |      |      |

|                                                        |                 |            | Min          | Max  | Min | Max   | Min   | Max  | Min | Max  |      |

| t <sub>PIA</sub>                                       | PIA delay       | (7)        |              | 1.1  |     | 1.1   |       | 1.4  |     | 1.0  | ns   |

| $t_{LPA}$                                              | Low-power adder | (8)        |              | 12.0 |     | 10.0  |       | 10.0 |     | 11.0 | ns   |

#### Notes to tables:

- (1) These values are specified under the recommended operating conditions shown in Table 14. See Figure 13 for more information on switching waveforms.

- (2) This minimum pulse width for preset and clear applies for both global clear and array controls. The t<sub>LPA</sub> parameter must be added to this minimum width if the clear or reset signal incorporates the t<sub>LAD</sub> parameter into the signal path.

- (3) This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This parameter applies for both global and array clocking.

- (4) These parameters are measured with a 16-bit loadable, enabled, up/down counter programmed into each LAB.

- (5) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- (6) Operating conditions:  $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial and industrial use.

- (7) For EPM7064S-5, EPM7064S-6, EPM7128S-6, EPM7160S-6, EPM7160S-7, EPM7192S-7, and EPM7256S-7 devices, these values are specified for a PIA fan-out of one LAB (16 macrocells). For each additional LAB fan-out in these devices, add an additional 0.1 ns to the PIA timing value.

- (8) The  $t_{LPA}$  parameter must be added to the  $t_{LAD}$ ,  $t_{LAC}$ ,  $t_{IC}$ ,  $t_{EN}$ ,  $t_{SEXP}$ ,  $\mathbf{t_{ACL}}$ , and  $\mathbf{t_{CPPW}}$  parameters for macrocells running in the low-power mode.

Tables 29 and 30 show the EPM7064S AC operating conditions.

| Table 2          | 9. EPM7064\$ External Time            | ing Parameters | (Part | 1 of 2) | No  | nte (1) |       |     |     |      |      |

|------------------|---------------------------------------|----------------|-------|---------|-----|---------|-------|-----|-----|------|------|

| Symbol           | Parameter                             | Conditions     |       |         |     | Speed   | Grade | )   |     |      | Unit |

|                  |                                       |                | -5    |         | -6  |         | -7    |     | -10 |      |      |

|                  |                                       |                | Min   | Max     | Min | Max     | Min   | Max | Min | Max  |      |

| t <sub>PD1</sub> | Input to non-registered output        | C1 = 35 pF     |       | 5.0     |     | 6.0     |       | 7.5 |     | 10.0 | ns   |

| t <sub>PD2</sub> | I/O input to non-registered output    | C1 = 35 pF     |       | 5.0     |     | 6.0     |       | 7.5 |     | 10.0 | ns   |

| t <sub>SU</sub>  | Global clock setup time               |                | 2.9   |         | 3.6 |         | 6.0   |     | 7.0 |      | ns   |

| t <sub>H</sub>   | Global clock hold time                |                | 0.0   |         | 0.0 |         | 0.0   |     | 0.0 |      | ns   |

| t <sub>FSU</sub> | Global clock setup time of fast input |                | 2.5   |         | 2.5 |         | 3.0   |     | 3.0 |      | ns   |

| t <sub>FH</sub>  | Global clock hold time of fast input  |                | 0.0   |         | 0.0 |         | 0.5   |     | 0.5 |      | ns   |

| t <sub>CO1</sub> | Global clock to output delay          | C1 = 35 pF     |       | 3.2     |     | 4.0     |       | 4.5 |     | 5.0  | ns   |

| t <sub>CH</sub>  | Global clock high time                |                | 2.0   |         | 2.5 |         | 3.0   |     | 4.0 |      | ns   |

| t <sub>CL</sub>  | Global clock low time                 |                | 2.0   |         | 2.5 |         | 3.0   |     | 4.0 |      | ns   |

| t <sub>ASU</sub> | Array clock setup time                |                | 0.7   |         | 0.9 |         | 3.0   |     | 2.0 |      | ns   |

| t <sub>AH</sub>  | Array clock hold time                 |                | 1.8   |         | 2.1 |         | 2.0   |     | 3.0 |      | ns   |

Tables 31 and 32 show the EPM7128S AC operating conditions.

| Table 3           | 11. EPM7128\$ External Time              | ing Parameters | : No        | te (1) |       |     |       |      |       |      |     |

|-------------------|------------------------------------------|----------------|-------------|--------|-------|-----|-------|------|-------|------|-----|

| Symbol            | Parameter                                | Conditions     | Speed Grade |        |       |     |       |      |       |      |     |

|                   |                                          |                | -6          |        | -7    |     | -10   |      | -15   |      |     |

|                   |                                          |                | Min         | Max    | Min   | Max | Min   | Max  | Min   | Max  |     |

| t <sub>PD1</sub>  | Input to non-registered output           | C1 = 35 pF     |             | 6.0    |       | 7.5 |       | 10.0 |       | 15.0 | ns  |

| t <sub>PD2</sub>  | I/O input to non-registered output       | C1 = 35 pF     |             | 6.0    |       | 7.5 |       | 10.0 |       | 15.0 | ns  |

| t <sub>SU</sub>   | Global clock setup time                  |                | 3.4         |        | 6.0   |     | 7.0   |      | 11.0  |      | ns  |

| t <sub>H</sub>    | Global clock hold time                   |                | 0.0         |        | 0.0   |     | 0.0   |      | 0.0   |      | ns  |

| t <sub>FSU</sub>  | Global clock setup time of fast input    |                | 2.5         |        | 3.0   |     | 3.0   |      | 3.0   |      | ns  |

| t <sub>FH</sub>   | Global clock hold time of fast input     |                | 0.0         |        | 0.5   |     | 0.5   |      | 0.0   |      | ns  |

| t <sub>CO1</sub>  | Global clock to output delay             | C1 = 35 pF     |             | 4.0    |       | 4.5 |       | 5.0  |       | 8.0  | ns  |

| t <sub>CH</sub>   | Global clock high time                   |                | 3.0         |        | 3.0   |     | 4.0   |      | 5.0   |      | ns  |

| t <sub>CL</sub>   | Global clock low time                    |                | 3.0         |        | 3.0   |     | 4.0   |      | 5.0   |      | ns  |

| t <sub>ASU</sub>  | Array clock setup time                   |                | 0.9         |        | 3.0   |     | 2.0   |      | 4.0   |      | ns  |

| t <sub>AH</sub>   | Array clock hold time                    |                | 1.8         |        | 2.0   |     | 5.0   |      | 4.0   |      | ns  |

| t <sub>ACO1</sub> | Array clock to output delay              | C1 = 35 pF     |             | 6.5    |       | 7.5 |       | 10.0 |       | 15.0 | ns  |

| t <sub>ACH</sub>  | Array clock high time                    |                | 3.0         |        | 3.0   |     | 4.0   |      | 6.0   |      | ns  |

| t <sub>ACL</sub>  | Array clock low time                     |                | 3.0         |        | 3.0   |     | 4.0   |      | 6.0   |      | ns  |

| t <sub>CPPW</sub> | Minimum pulse width for clear and preset | (2)            | 3.0         |        | 3.0   |     | 4.0   |      | 6.0   |      | ns  |

| t <sub>ODH</sub>  | Output data hold time after clock        | C1 = 35 pF (3) | 1.0         |        | 1.0   |     | 1.0   |      | 1.0   |      | ns  |

| t <sub>CNT</sub>  | Minimum global clock period              |                |             | 6.8    |       | 8.0 |       | 10.0 |       | 13.0 | ns  |

| f <sub>CNT</sub>  | Maximum internal global clock frequency  | (4)            | 147.1       |        | 125.0 |     | 100.0 |      | 76.9  |      | MHz |

| t <sub>ACNT</sub> | Minimum array clock period               |                |             | 6.8    |       | 8.0 |       | 10.0 |       | 13.0 | ns  |

| f <sub>ACNT</sub> | Maximum internal array clock frequency   | (4)            | 147.1       |        | 125.0 |     | 100.0 |      | 76.9  |      | MHz |

| f <sub>MAX</sub>  | Maximum clock frequency                  | (5)            | 166.7       |        | 166.7 |     | 125.0 |      | 100.0 |      | MHz |

| Symbol            | Parameter                         | Conditions     | Speed Grade |      |     |      |     |      |     |      |    |

|-------------------|-----------------------------------|----------------|-------------|------|-----|------|-----|------|-----|------|----|

|                   |                                   |                | -6          |      | -7  |      | -10 |      | -15 |      |    |

|                   |                                   |                | Min         | Max  | Min | Max  | Min | Max  | Min | Max  | -  |

| t <sub>IN</sub>   | Input pad and buffer delay        |                |             | 0.2  |     | 0.5  |     | 0.5  |     | 2.0  | ns |

| t <sub>IO</sub>   | I/O input pad and buffer delay    |                |             | 0.2  |     | 0.5  |     | 0.5  |     | 2.0  | ns |

| t <sub>FIN</sub>  | Fast input delay                  |                |             | 2.6  |     | 1.0  |     | 1.0  |     | 2.0  | ns |

| t <sub>SEXP</sub> | Shared expander delay             |                |             | 3.7  |     | 4.0  |     | 5.0  |     | 8.0  | ns |

| t <sub>PEXP</sub> | Parallel expander delay           |                |             | 1.1  |     | 0.8  |     | 0.8  |     | 1.0  | ns |

| $t_{LAD}$         | Logic array delay                 |                |             | 3.0  |     | 3.0  |     | 5.0  |     | 6.0  | ns |

| $t_{LAC}$         | Logic control array delay         |                |             | 3.0  |     | 3.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>IOE</sub>  | Internal output enable delay      |                |             | 0.7  |     | 2.0  |     | 2.0  |     | 3.0  | ns |

| t <sub>OD1</sub>  | Output buffer and pad delay       | C1 = 35 pF     |             | 0.4  |     | 2.0  |     | 1.5  |     | 4.0  | ns |

| t <sub>OD2</sub>  | Output buffer and pad delay       | C1 = 35 pF (6) |             | 0.9  |     | 2.5  |     | 2.0  |     | 5.0  | ns |

| t <sub>OD3</sub>  | Output buffer and pad delay       | C1 = 35 pF     |             | 5.4  |     | 7.0  |     | 5.5  |     | 8.0  | ns |

| t <sub>ZX1</sub>  | Output buffer enable delay        | C1 = 35 pF     |             | 4.0  |     | 4.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>ZX2</sub>  | Output buffer enable delay        | C1 = 35 pF (6) |             | 4.5  |     | 4.5  |     | 5.5  |     | 7.0  | ns |

| $t_{ZX3}$         | Output buffer enable delay        | C1 = 35 pF     |             | 9.0  |     | 9.0  |     | 9.0  |     | 10.0 | ns |

| $t_{XZ}$          | Output buffer disable delay       | C1 = 5 pF      |             | 4.0  |     | 4.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>SU</sub>   | Register setup time               |                | 1.0         |      | 3.0 |      | 2.0 |      | 4.0 |      | ns |

| t <sub>H</sub>    | Register hold time                |                | 1.7         |      | 2.0 |      | 5.0 |      | 4.0 |      | ns |

| t <sub>FSU</sub>  | Register setup time of fast input |                | 1.9         |      | 3.0 |      | 3.0 |      | 2.0 |      | ns |

| t <sub>FH</sub>   | Register hold time of fast input  |                | 0.6         |      | 0.5 |      | 0.5 |      | 1.0 |      | ns |

| $t_{RD}$          | Register delay                    |                |             | 1.4  |     | 1.0  |     | 2.0  |     | 1.0  | ns |

| t <sub>COMB</sub> | Combinatorial delay               |                |             | 1.0  |     | 1.0  |     | 2.0  |     | 1.0  | ns |

| t <sub>IC</sub>   | Array clock delay                 |                |             | 3.1  |     | 3.0  |     | 5.0  |     | 6.0  | ns |

| t <sub>EN</sub>   | Register enable time              |                |             | 3.0  |     | 3.0  |     | 5.0  |     | 6.0  | ns |

| $t_{GLOB}$        | Global control delay              |                |             | 2.0  |     | 1.0  |     | 1.0  |     | 1.0  | ns |

| t <sub>PRE</sub>  | Register preset time              |                |             | 2.4  |     | 2.0  |     | 3.0  |     | 4.0  | ns |

| t <sub>CLR</sub>  | Register clear time               |                |             | 2.4  |     | 2.0  |     | 3.0  |     | 4.0  | ns |

| $t_{PIA}$         | PIA delay                         | (7)            |             | 1.4  |     | 1.0  |     | 1.0  |     | 2.0  | ns |

| $t_{LPA}$         | Low-power adder                   | (8)            |             | 11.0 |     | 10.0 |     | 11.0 |     | 13.0 | ns |

| Table 3           | Table 36. EPM7192S Internal Timing Parameters (Part 2 of 2) Note (1) |            |     |      |       |       |     |      |      |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------|------------|-----|------|-------|-------|-----|------|------|--|--|--|--|--|

| Symbol            | Parameter                                                            | Conditions |     |      | Speed | Grade |     |      | Unit |  |  |  |  |  |

|                   |                                                                      |            | -7  |      | -10   |       | -15 |      |      |  |  |  |  |  |

|                   |                                                                      |            | Min | Max  | Min   | Max   | Min | Max  |      |  |  |  |  |  |

| t <sub>H</sub>    | Register hold time                                                   |            | 1.7 |      | 3.0   |       | 4.0 |      | ns   |  |  |  |  |  |

| t <sub>FSU</sub>  | Register setup time of fast input                                    |            | 2.3 |      | 3.0   |       | 2.0 |      | ns   |  |  |  |  |  |

| t <sub>FH</sub>   | Register hold time of fast input                                     |            | 0.7 |      | 0.5   |       | 1.0 |      | ns   |  |  |  |  |  |

| t <sub>RD</sub>   | Register delay                                                       |            |     | 1.4  |       | 2.0   |     | 1.0  | ns   |  |  |  |  |  |

| t <sub>COMB</sub> | Combinatorial delay                                                  |            |     | 1.2  |       | 2.0   |     | 1.0  | ns   |  |  |  |  |  |

| $t_{IC}$          | Array clock delay                                                    |            |     | 3.2  |       | 5.0   |     | 6.0  | ns   |  |  |  |  |  |

| t <sub>EN</sub>   | Register enable time                                                 |            |     | 3.1  |       | 5.0   |     | 6.0  | ns   |  |  |  |  |  |

| $t_{GLOB}$        | Global control delay                                                 |            |     | 2.5  |       | 1.0   |     | 1.0  | ns   |  |  |  |  |  |

| t <sub>PRE</sub>  | Register preset time                                                 |            |     | 2.7  |       | 3.0   |     | 4.0  | ns   |  |  |  |  |  |

| t <sub>CLR</sub>  | Register clear time                                                  |            |     | 2.7  |       | 3.0   |     | 4.0  | ns   |  |  |  |  |  |

| t <sub>PIA</sub>  | PIA delay                                                            | (7)        |     | 2.4  |       | 1.0   |     | 2.0  | ns   |  |  |  |  |  |

| $t_{LPA}$         | Low-power adder                                                      | (8)        |     | 10.0 |       | 11.0  |     | 13.0 | ns   |  |  |  |  |  |

#### Notes to tables:

- These values are specified under the recommended operating conditions shown in Table 14. See Figure 13 for more information on switching waveforms.

- (2) This minimum pulse width for preset and clear applies for both global clear and array controls. The t<sub>LPA</sub> parameter must be added to this minimum width if the clear or reset signal incorporates the t<sub>LAD</sub> parameter into the signal path.

- (3) This parameter is a guideline that is sample-tested only and is based on extensive device characterization. This parameter applies for both global and array clocking.

- (4) These parameters are measured with a 16-bit loadable, enabled, up/down counter programmed into each LAB.

- (5) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- (6) Operating conditions:  $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial and industrial use.

- (7) For EPM7064S-5, EPM7064S-6, EPM7128S-6, EPM7160S-6, EPM7160S-7, EPM7192S-7, and EPM7256S-7 devices, these values are specified for a PIA fan-out of one LAB (16 macrocells). For each additional LAB fan-out in these devices, add an additional 0.1 ns to the PIA timing value.

- (8) The  $t_{LPA}$  parameter must be added to the  $t_{LAD}$ ,  $t_{LAC}$ ,  $t_{IC}$ ,  $t_{EN}$ ,  $t_{SEXP}$ ,  $\mathbf{t_{ACL}}$ , and  $\mathbf{t_{CPPW}}$  parameters for macrocells running in the low-power mode.

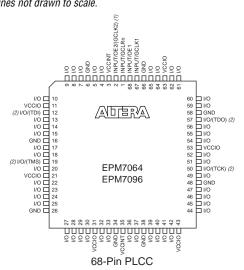

Figure 17. 68-Pin Package Pin-Out Diagram

Package outlines not drawn to scale.

### Notes:

- The pin functions shown in parenthesis are only available in MAX 7000E and MAX 7000S devices.

- (2) JTAG ports are available in MAX 7000S devices only.

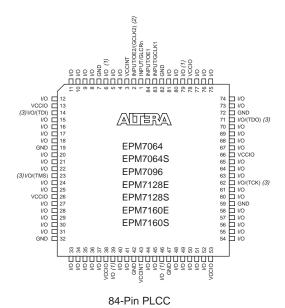

### Figure 18. 84-Pin Package Pin-Out Diagram

Package outline not drawn to scale.

### Notes:

- (1) Pins 6, 39, 46, and 79 are no-connect (N.C.) pins on EPM7096, EPM7160E, and EPM7160S devices.

- (2) The pin functions shown in parenthesis are only available in MAX 7000E and MAX 7000S devices.

- (3) JTAG ports are available in MAX 7000S devices only.

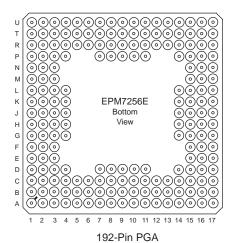

## Figure 21. 192-Pin Package Pin-Out Diagram

Package outline not drawn to scale.

# Figure 22. 208-Pin Package Pin-Out Diagram

Package outline not drawn to scale.