# E·XFL

#### Intel - 5AGXBA3D4F27C5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 7362                                                       |

| Number of Logic Elements/Cells | 156000                                                     |

| Total RAM Bits                 | 11746304                                                   |

| Number of I/O                  | 336                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 672-BBGA, FCBGA                                            |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxba3d4f27c5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| I/O Standard        | V <sub>IL</sub> | <sub>.(DC)</sub> (V)    | V <sub>IH(D</sub>       | <sub>C)</sub> (V)        | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)    | V <sub>OH</sub> (V)     | I <sub>OL</sub> <sup>(14)</sup> | I <sub>OH</sub> <sup>(14)</sup> (mA) |

|---------------------|-----------------|-------------------------|-------------------------|--------------------------|-------------------------|-------------------------|------------------------|-------------------------|---------------------------------|--------------------------------------|

|                     | Min             | Max                     | Min                     | Max                      | Max                     | Min                     | Max                    | Min                     | (mA)                            |                                      |

| HSTL-15<br>Class II | —               | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$         | —                        | V <sub>REF</sub> – 0.2  | $V_{REF} + 0.2$         | 0.4                    | V <sub>CCIO</sub> – 0.4 | 16                              | -16                                  |

| HSTL-12<br>Class I  | -0.15           | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$  | 8                               | -8                                   |

| HSTL-12<br>Class II | -0.15           | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$  | 16                              | -16                                  |

| HSUL-12             | —               | V <sub>REF</sub> - 0.13 | V <sub>REF</sub> + 0.13 | _                        | V <sub>REF</sub> – 0.22 | $V_{REF} + 0.22$        | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$   |                                 | _                                    |

#### **Differential SSTL I/O Standards**

Table 1-17: Differential SSTL I/O Standards for Arria V Devices

| I/O Standard           | O Standard |      |       | V <sub>SW</sub> | <sub>ING(DC)</sub> (V) | V <sub>X(AC)</sub> (V)          |                      |                                 | V <sub>SWING(AC)</sub> (V)                    |                           |

|------------------------|------------|------|-------|-----------------|------------------------|---------------------------------|----------------------|---------------------------------|-----------------------------------------------|---------------------------|

|                        | Min        | Тур  | Max   | Min             | Мах                    | Min                             | Тур                  | Мах                             | Min                                           | Max                       |

| SSTL-2<br>Class I, II  | 2.375      | 2.5  | 2.625 | 0.3             | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 – 0.2      | _                    | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$          |

| SSTL-18<br>Class I, II | 1.71       | 1.8  | 1.89  | 0.25            | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 –<br>0.175 | _                    | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | $V_{CCIO} + 0.6$          |

| SSTL-15<br>Class I, II | 1.425      | 1.5  | 1.575 | 0.2             | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | —                    | V <sub>CCIO</sub> /2<br>+ 0.15  | $2(V_{IH(AC)} - V_{REF})$                     | $2(V_{IL(AC)} - V_{REF})$ |

| SSTL-135               | 1.283      | 1.35 | 1.45  | 0.18            | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |

<sup>&</sup>lt;sup>(14)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

$<sup>^{(15)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

| Symbol/Description                                                                 | Condition -        | Transceiver Speed Grade 4 |     |     | Transc | Unit |     |      |

|------------------------------------------------------------------------------------|--------------------|---------------------------|-----|-----|--------|------|-----|------|

|                                                                                    |                    | Min                       | Тур | Max | Min    | Тур  | Max | Onit |

| Inter-transceiver block<br>transmitter channel-to-<br>channel skew <sup>(39)</sup> | ×N PMA bonded mode | _                         | _   | 500 | _      | _    | 500 | ps   |

#### Table 1-24: CMU PLL Specifications for Arria V GX and SX Devices

| Symbol/Description        | Transceiver S | peed Grade 4 | Transceiver S | peed Grade 6 | Unit |

|---------------------------|---------------|--------------|---------------|--------------|------|

| Symbol/Description        | Min           | Мах          | Min           | Мах          | Onit |

| Supported data range      | 611           | 6553.6       | 611           | 3125         | Mbps |

| fPLL supported data range | 611           | 3125         | 611           | 3125         | Mbps |

#### Table 1-25: Transceiver-FPGA Fabric Interface Specifications for Arria V GX and SX Devices

| Symbol/Description                  | Transceiver Spee | ed Grade 4 and 6 | Unit |

|-------------------------------------|------------------|------------------|------|

| Symbol/Description                  | Min              | Мах              | Unit |

| Interface speed (single-width mode) | 25               | 187.5            | MHz  |

| Interface speed (double-width mode) | 25               | 163.84           | MHz  |

#### **Related Information**

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 1-35

- CTLE Response at Data Rates  $\leq$  3.25 Gbps across Supported AC Gain and DC Gain on page 1-36

- Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines Provides more information about the power supply connection for different data rates.

<sup>&</sup>lt;sup>(39)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

#### 1-40 Transceiver Compliance Specification

| Quartus Prime 1st                 |             |             | Quar        | tus Prime V <sub>OD</sub> Se | etting      |             |              | 11   |

|-----------------------------------|-------------|-------------|-------------|------------------------------|-------------|-------------|--------------|------|

| Post Tap Pre-<br>Emphasis Setting | 10 (200 mV) | 20 (400 mV) | 30 (600 mV) | 35 (700 mV)                  | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) | Unit |

| 16                                | _           | _           | 9.56        | 7.73                         | 6.49        |             | _            | dB   |

| 17                                | _           | _           | 10.43       | 8.39                         | 7.02        |             | _            | dB   |

| 18                                | _           |             | 11.23       | 9.03                         | 7.52        |             | _            | dB   |

| 19                                | _           |             | 12.18       | 9.7                          | 8.02        |             | _            | dB   |

| 20                                | _           | _           | 13.17       | 10.34                        | 8.59        | _           | _            | dB   |

| 21                                | _           | _           | 14.2        | 11.1                         | —           | _           | _            | dB   |

| 22                                | _           |             | 15.38       | 11.87                        |             |             | _            | dB   |

| 23                                | _           | _           | —           | 12.67                        | —           |             | _            | dB   |

| 24                                | _           |             |             | 13.48                        | _           |             | _            | dB   |

| 25                                | _           |             |             | 14.37                        | —           |             | _            | dB   |

| 26                                | _           | _           | _           |                              | _           | _           | _            | dB   |

| 27                                | _           |             |             |                              | _           |             | _            | dB   |

| 28                                |             |             |             |                              |             |             | _            | dB   |

| 29                                | _           |             |             |                              | —           |             | _            | dB   |

| 30                                | _           |             |             |                              | _           |             | _            | dB   |

| 31                                |             |             |             |                              |             |             | —            | dB   |

#### **Related Information**

#### SPICE Models for Altera Devices

Provides the Arria V HSSI HSPICE models.

#### **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Arria V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Altera Sales Representative.

## **DLL Frequency Range Specifications**

#### Table 1-43: DLL Frequency Range Specifications for Arria V Devices

| Parameter                     | -I3, -C4  | -I5, -C5  | -C6       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 200 - 667 | 200 - 667 | 200 - 667 | MHz  |

## DQS Logic Block Specifications

#### Table 1-44: DQS Phase Shift Error Specifications for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Arria V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -I3, -C4 | –I5, –C5 | -C6 | Unit |

|----------------------------|----------|----------|-----|------|

| 2                          | 40       | 80       | 80  | ps   |

#### **Memory Output Clock Jitter Specifications**

#### Table 1-45: Memory Output Clock Jitter Specifications for Arria V Devices

The memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2/DDR3 SDRAM standard. The memory output clock jitter is applicable when an input jitter of 30 ps (p-p) is applied with bit error rate (BER)  $10^{-12}$ , equivalent to 14 sigma. Altera recommends using the UniPHY intellectual property (IP) with PHYCLK connections for better jitter performance.

| Parameter                    | Clock Network Symbol |                       | -I3, -C4 |     | –I5, –C5 |     | -C6 |     | Unit |

|------------------------------|----------------------|-----------------------|----------|-----|----------|-----|-----|-----|------|

|                              |                      | Symbol                | Min      | Max | Min      | Max | Min | Max | Unit |

| Clock period jitter          | PHYCLK               | t <sub>JIT(per)</sub> | -41      | 41  | -50      | 50  | -55 | 55  | ps   |

| Cycle-to-cycle period jitter | PHYCLK               | t <sub>JIT(cc)</sub>  | 6        | 3   | 9        | 0   | 9   | 4   | ps   |

## **OCT Calibration Block Specifications**

#### Table 1-46: OCT Calibration Block Specifications for Arria V Devices

| Symbol                | Description                                                                                                                                           | Min | Тур  | Max | Unit   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by OCT calibration blocks                                                                                                              |     |      | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of octus<br>RCLK clock cycles required for $R_S$ OCT/ $R_T$ OCT calibration                                                                    |     | 1000 |     | Cycles |

| T <sub>OCTSHIFT</sub> | Number of octusrclk clock cycles required for oct code to shift out                                                                                   |     | 32   |     | Cycles |

| T <sub>RS_RT</sub>    | Time required between the dyn_term_ctrl and oe signal transitions in a bidirectional I/O buffer to dynamically switch between $R_S$ OCT and $R_T$ OCT | _   | 2.5  | _   | ns     |

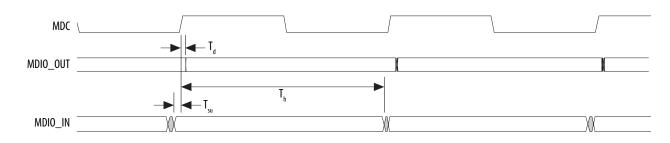

## Figure 1-15: MDIO Timing Diagram

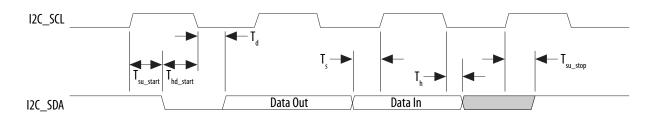

## I<sup>2</sup>C Timing Characteristics

## Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Symbol                | Description                                       | Standar | d Mode | Fast | Mode | Unit |

|-----------------------|---------------------------------------------------|---------|--------|------|------|------|

| Symbol                | Description                                       | Min     | Max    | Min  | Max  | Onic |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10      | —      | 2.5  | _    | μs   |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7     | —      | 0.6  |      | μs   |

| T <sub>clklow</sub>   | SCL low time                                      | 4       | _      | 1.3  |      | μs   |

| T <sub>s</sub>        | Setup time for serial data line (SDA) data to SCL | 0.25    | —      | 0.1  | —    | μs   |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0       | 3.45   | 0    | 0.9  | μs   |

| T <sub>d</sub>        | SCL to SDA output data delay                      | —       | 0.2    | _    | 0.2  | μs   |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7     | _      | 0.6  | _    | μs   |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4       | —      | 0.6  | _    | μs   |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4       | —      | 0.6  | —    | μs   |

#### Figure 1-16: I<sup>2</sup>C Timing Diagram

## **NAND Timing Characteristics**

#### Table 1-60: NAND ONFI 1.0 Timing Requirements for Arria V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the c4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                             | Description                                     | Min | Max | Unit |

|------------------------------------|-------------------------------------------------|-----|-----|------|

| T <sub>wp</sub> <sup>(89)</sup>    | Write enable pulse width                        | 10  | _   | ns   |

| T <sub>wh</sub> <sup>(89)</sup>    | Write enable hold time                          | 7   |     | ns   |

| T <sub>rp</sub> <sup>(89)</sup>    | Read enable pulse width                         | 10  |     | ns   |

| T <sub>reh</sub> <sup>(89)</sup>   | Read enable hold time                           | 7   |     | ns   |

| T <sub>clesu</sub> <sup>(89)</sup> | Command latch enable to write enable setup time | 10  |     | ns   |

| T <sub>cleh</sub> <sup>(89)</sup>  | Command latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>cesu</sub> <sup>(89)</sup>  | Chip enable to write enable setup time          | 15  |     | ns   |

| T <sub>ceh</sub> <sup>(89)</sup>   | Chip enable to write enable hold time           | 5   |     | ns   |

| T <sub>alesu</sub> <sup>(89)</sup> | Address latch enable to write enable setup time | 10  |     | ns   |

| T <sub>aleh</sub> <sup>(89)</sup>  | Address latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>dsu</sub> <sup>(89)</sup>   | Data to write enable setup time                 | 10  |     | ns   |

<sup>(89)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

|            |             |       | Active Serial <sup>(108)</sup> |                                      |       | Fast Passive Parallel <sup>(109)</sup> |                                    |  |  |

|------------|-------------|-------|--------------------------------|--------------------------------------|-------|----------------------------------------|------------------------------------|--|--|

| Variant    | Member Code | Width | DCLK (MHz)                     | Minimum Configura-<br>tion Time (ms) | Width | DCLK (MHz)                             | Minimum Configuration Time<br>(ms) |  |  |

|            | A1          | 4     | 100                            | 178                                  | 16    | 125                                    | 36                                 |  |  |

|            | A3          | 4     | 100                            | 178                                  | 16    | 125                                    | 36                                 |  |  |

|            | A5          | 4     | 100                            | 255                                  | 16    | 125                                    | 51                                 |  |  |

| Arria V GX | A7          | 4     | 100                            | 255                                  | 16    | 125                                    | 51                                 |  |  |

| Allia v GA | B1          | 4     | 100                            | 344                                  | 16    | 125                                    | 69                                 |  |  |

|            | B3          | 4     | 100                            | 344                                  | 16    | 125                                    | 69                                 |  |  |

|            | B5          | 4     | 100                            | 465                                  | 16    | 125                                    | 93                                 |  |  |

|            | B7          | 4     | 100                            | 465                                  | 16    | 125                                    | 93                                 |  |  |

|            | C3          | 4     | 100                            | 178                                  | 16    | 125                                    | 36                                 |  |  |

| Arria V GT | C7          | 4     | 100                            | 255                                  | 16    | 125                                    | 51                                 |  |  |

| Allia v Gi | D3          | 4     | 100                            | 344                                  | 16    | 125                                    | 69                                 |  |  |

|            | D7          | 4     | 100                            | 465                                  | 16    | 125                                    | 93                                 |  |  |

| Arria V SX | В3          | 4     | 100                            | 465                                  | 16    | 125                                    | 93                                 |  |  |

| Allia V SA | B5          | 4     | 100                            | 465                                  | 16    | 125                                    | 93                                 |  |  |

| Arria V ST | D3          | 4     | 100                            | 465                                  | 16    | 125                                    | 93                                 |  |  |

|            | D5          | 4     | 100                            | 465                                  | 16    | 125                                    | 93                                 |  |  |

**Related Information Configuration Files** on page 1-83

(108) DCLK frequency of 100 MHz using external CLKUSR.

(109) Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

#### 1-98 Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.8     | <ul> <li>Added a note in Table 3, Table 4, and Table 5: The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.</li> <li>Updated V<sub>CC_HPS</sub> specification in Table 5.</li> <li>Added a note in Table 19: Differential inputs are powered by V<sub>CCPD</sub> which requires 2.5 V.</li> <li>Updated "Minimum differential eye opening at the receiver serial input pins" specification in Table 20 and Table 21.</li> <li>Updated description in "HPS PLL Specifications" section.</li> <li>Updated VCO range maximum specification in Table 39.</li> <li>Updated T<sub>h</sub> and T<sub>h</sub> specifications in Table 45.</li> <li>Added T<sub>h</sub> specification in Table 47 and Figure 13.</li> <li>Updated a note in Figure 20, Figure 21, and Figure 23 as follows: Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.</li> <li>Removed "Remote update only in AS mode" specification in Table 58.</li> <li>Added DCLK device initialization clock source specification in Table 60.</li> <li>Added description in "Configuration Files" section: The IOCSR .rbf size is specifically for the Configuration via Protocol (CvP) feature.</li> <li>Removed f<sub>MAX_RU_CLK</sub> specification in Table 63.</li> </ul> |

| February 2014 | 3.7     | <ul> <li>Updated V<sub>CCRSTCLK_HPS</sub> maximum specification in Table 1.</li> <li>Added V<sub>CC_AUX_SHARED</sub> specification in Table 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| December 2013 | 3.6     | <ul> <li>Added "HPS PLL Specifications".</li> <li>Added Table 24, Table 39, and Table 40.</li> <li>Updated Table 1, Table 3, Table 5, Table 19, Table 20, Table 21, Table 38, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, Table 50, Table 51, Table 55, Table 56, and Table 59.</li> <li>Updated Figure 7, Figure 13, Figure 15, Figure 16, and Figure 19.</li> <li>Removed table: GPIO Pulse Width for Arria V Devices.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### 1-100 Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2012 | 3.0     | <ul> <li>Updated Table 2, Table 4, Table 9, Table 14, Table 16, Table 17, Table 20, Table 21, Table 25, Table 29, Table 36, Table 56, Table 57, and Table 60.</li> <li>Removed table: Transceiver Block Jitter Specifications for Arria V Devices.</li> <li>Added HPS information: <ul> <li>Added "HPS Specifications" section.</li> <li>Added Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, and Table 50.</li> <li>Added Figure 7, Figure 8, Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, Figure 14, Figure 15, Figure 16, Figure 17, Figure 18, and Figure 19.</li> <li>Updated Table 3 and Table 5.</li> </ul> </li> </ul> |

| October 2012  | 2.4     | <ul> <li>Updated Arria V GX V<sub>CCR_GXBL/R</sub>, V<sub>CCT_GXBL/R</sub>, and V<sub>CCL_GXBL/R</sub> minimum and maximum values, and data rate in Table 4.</li> <li>Added receiver V<sub>ICM</sub> (AC coupled) and V<sub>ICM</sub> (DC coupled) values, and transmitter V<sub>OCM</sub> (AC coupled) and V<sub>OCM</sub> (DC coupled) values in Table 20 and Table 21.</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| August 2012   | 2.3     | Updated the SERDES factor condition in Table 30.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| July 2012     | 2.2     | <ul> <li>Updated the maximum voltage for V<sub>I</sub> (DC input voltage) in Table 1.</li> <li>Updated Table 20 to include the Arria V GX -I3 speed grade.</li> <li>Updated the minimum value of the fixedclk clock frequency in Table 20 and Table 21.</li> <li>Updated the SERDES factor condition in Table 30.</li> <li>Updated Table 50 to include the IOE programmable delay settings for the Arria V GX -I3 speed grade.</li> </ul>                                                                                                                                                                                                                                                                        |

| June 2012     | 2.1     | Updated $V_{CCR\_GXBL/R}$ , $V_{CCT\_GXBL/R}$ , and $V_{CCL\_GXBL/R}$ values in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Symbol            | Description                    | Condition    | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-------------------|--------------------------------|--------------|--------------------------|---------|--------------------------|------|

| VI                | DC input voltage               | —            | -0.5                     | _       | 3.6                      | V    |

| Vo                | Output voltage                 |              | 0                        |         | V <sub>CCIO</sub>        | V    |

| TI                | Operating junction temperature | Commercial   | 0                        |         | 85                       | °C   |

| Ij                | Operating junction temperature | Industrial   | -40                      |         | 100                      | °C   |

| t                 | Power supply ramp time         | Standard POR | 200 µs                   | _       | 100 ms                   | _    |

| t <sub>RAMP</sub> |                                | Fast POR     | 200 µs                   | —       | 4 ms                     | —    |

#### **Recommended Transceiver Power Supply Operating Conditions**

#### Table 2-6: Recommended Transceiver Power Supply Operating Conditions for Arria V GZ Devices

| Symbol                                                       | Description                                       | Minimum <sup>(118)</sup> | Typical | Maximum <sup>(118)</sup> | Unit |

|--------------------------------------------------------------|---------------------------------------------------|--------------------------|---------|--------------------------|------|

| V <sub>CCA_GXBL</sub>                                        | Transceiver channel PLL power supply (left side)  | 2.85                     | 3.0     | 3.15                     | V    |

| (119), (120)                                                 |                                                   | 2.375                    | 2.5     | 2.625                    | v    |

| V <sub>CCA</sub> _                                           | Transceiver channel PLL power supply (right side) | 2.85                     | 3.0     | 3.15                     | V    |

| V <sub>CCA</sub><br>GXBR <sup>(119)</sup> , <sup>(120)</sup> |                                                   | 2.375                    | 2.5     | 2.625                    | v    |

| V <sub>CCHIP_L</sub>                                         | Transceiver hard IP power supply (left side)      | 0.82                     | 0.85    | 0.88                     | V    |

| V <sub>CCHSSI_L</sub>                                        | Transceiver PCS power supply (left side)          | 0.82                     | 0.85    | 0.88                     | V    |

| V <sub>CCHSSI_R</sub>                                        | Transceiver PCS power supply (right side)         | 0.82                     | 0.85    | 0.88                     | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(120)</sup> When using ATX PLLs, the supply must be 3.0 V.

<sup>(119)</sup> This supply must be connected to 3.0 V if the CMU PLL, receiver CDR, or both, are configured at a base data rate > 6.5 Gbps. Up to 6.5 Gbps, you can connect this supply to either 3.0 V or 2.5 V.

#### **Transceiver Power Supply Requirements**

#### Table 2-7: Transceiver Power Supply Voltage Requirements for Arria V GZ Devices

| Conditions                                                                                                                                | VCCR_GXB and VCCT_GXB <sup>(122)</sup> | VCCA_GXB | VCCH_GXB | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------|----------|------|

| If BOTH of the following conditions are true:                                                                                             | 1.05                                   |          |          |      |

| <ul> <li>Data rate &gt; 10.3 Gbps.</li> <li>DFE is used.</li> </ul>                                                                       |                                        |          |          |      |

| If ANY of the following conditions are true <sup>(123)</sup> :                                                                            | 1.0                                    | 3.0      |          |      |

| <ul> <li>ATX PLL is used.</li> <li>Data rate &gt; 6.5Gbps.</li> <li>DFE (data rate ≤ 10.3 Gbps), AEQ, or EyeQ feature is used.</li> </ul> |                                        |          | 1.5      | V    |

| If ALL of the following conditions are true:                                                                                              | 0.85                                   | 2.5      |          |      |

| <ul> <li>ATX PLL is not used.</li> <li>Data rate ≤ 6.5Gbps.</li> <li>DFE, AEQ, and EyeQ are not used.</li> </ul>                          |                                        |          |          |      |

## **DC Characteristics**

#### **Supply Current**

Standby current is the current drawn from the respective power rails used for power budgeting.

Use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design because these currents vary greatly with the resources you use.

Send Feedback

<sup>&</sup>lt;sup>(122)</sup> If the VCCR\_GXB and VCCT\_GXB supplies are set to 1.0 V or 1.05 V, they cannot be shared with the VCC core supply. If the VCCR\_GXB and VCCT\_GXB are set to 0.85 V, they can be shared with the VCC core supply.

<sup>&</sup>lt;sup>(123)</sup> Choose this power supply voltage requirement option if you plan to upgrade your design later with any of the listed conditions.

| Symbol               | Description                                                            | Conditions                 | Resistance | Unit   |   |

|----------------------|------------------------------------------------------------------------|----------------------------|------------|--------|---|

| Symbol               | Description                                                            | Conditions                 | C3, I3L    | C4, I4 |   |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | % |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | % |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | % |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | % |

| 100-Ω R <sub>D</sub> | Internal differential termination (100- $\Omega$ setting)              | $V_{CCIO} = 2.5 V$         | ±25        | ±25    | % |

#### Figure 2-1: OCT Variation Without Re-Calibration for Arria V GZ Devices

$$\mathbf{R}_{\text{OCT}} = \mathbf{R}_{\text{SCAL}} \left( 1 + \left( \frac{dR}{dT} \times \bigtriangleup T \right) \pm \left( \frac{dR}{dV} \times \bigtriangleup V \right) \right)$$

Notes:

1. The  $R_{oct}$  value shows the range of OCT resistance with the variation of temperature and  $V_{ccio}$ . 2.  $R_{scAL}$  is the OCT resistance value at power-up. 3.  $\Delta T$  is the variation of temperature with respect to the temperature at power-up. 4.  $\Delta V$  is the variation of voltage with respect to the  $V_{ccio}$  at power-up. 5. dR/dT is the percentage change of  $R_{scAL}$  with temperature. 6. dR/dV is the percentage change of  $R_{scAL}$  with voltage

6. dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

#### Table 2-12: OCT Variation after Power-Up Calibration for Arria V GZ Devices

Valid for a V<sub>CCIO</sub> range of  $\pm$ 5% and a temperature range of 0° to 85°C.

| Symbol/Description                           | Conditions                                              | Transceiver Speed Grade 2 |     |     | Transceiver Speed Grade 3 |     |     | – Unit |

|----------------------------------------------|---------------------------------------------------------|---------------------------|-----|-----|---------------------------|-----|-----|--------|

| Symbol/Description                           | Conditions                                              | Min                       | Тур | Мах | Min                       | Тур | Мах |        |

|                                              | $V_{CCR\_GXB} = 0.85 V$<br>full bandwidth               | _                         | 600 | _   | _                         | 600 | _   | mV     |

| V (AC and DC coupled)                        | $V_{CCR_{GXB}} = 0.85 V$<br>half bandwidth              | _                         | 600 |     |                           | 600 | _   | mV     |

| $\rm V_{ICM}$ (AC and DC coupled)            | $V_{CCR_{GXB}} = 1.0 V$<br>full bandwidth               |                           | 700 | _   |                           | 700 | _   | mV     |

|                                              | $V_{CCR_{GXB}} = 1.0 V$<br>half bandwidth               |                           | 700 | _   |                           | 700 | _   | mV     |

| t <sub>LTR</sub> <sup>(149)</sup>            | —                                                       | _                         | _   | 10  | _                         | _   | 10  | μs     |

| t <sub>LTD</sub> <sup>(150)</sup>            | _                                                       | 4                         |     |     | 4                         | _   |     | μs     |

| t <sub>LTD_manual</sub> <sup>(151)</sup>     | —                                                       | 4                         | _   |     | 4                         | _   |     | μs     |

| t <sub>LTR_LTD_manual</sub> <sup>(152)</sup> | _                                                       | 15                        |     |     | 15                        | _   |     | μs     |

| Programmable equalization (AC Gain)          | Full bandwidth (6.25 GHz)<br>Half bandwidth (3.125 GHz) |                           |     | 16  |                           | _   | 16  | dB     |

2-26

Receiver

$<sup>^{(149)}</sup>$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

$<sup>^{(150)}</sup>$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

<sup>(151)</sup>  $t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{\text{LTR\_LTD\_manual}}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

| Symbol/Description                          | Conditions                | Transceiver Speed Grade 2 |     |       | Transceiver Speed Grade 3 |     |         | - Unit |

|---------------------------------------------|---------------------------|---------------------------|-----|-------|---------------------------|-----|---------|--------|

| Symbol/Description                          | Conditions                | Min                       | Тур | Max   | Min                       | Тур | Max     | Onit   |

|                                             | VCO post-divider<br>L = 2 | 8000                      |     | 12500 | 8000                      | _   | 10312.5 | Mbps   |

| Supported data rate range                   | L = 4                     | 4000                      |     | 6600  | 4000                      |     | 6600    | Mbps   |

|                                             | $L = 8^{(155)}$           | 2000                      |     | 3300  | 2000                      | _   | 3300    | Mbps   |

| t <sub>pll_powerdown</sub> <sup>(156)</sup> | _                         | 1                         |     |       | 1                         |     |         | μs     |

| t <sub>pll_lock</sub> <sup>(157)</sup>      | _                         |                           |     | 10    | _                         |     | 10      | μs     |

#### **Related Information**

- Arria V Device Overview For more information about device ordering codes.

- Transceiver Clocking in Arria V Devices For more information about clocking ATX PLLs.

- **Dynamic Reconfiguration in Arria V Devices** For more information about reconfiguring ATX PLLs.

#### **Fractional PLL**

#### Table 2-28: Fractional PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

<sup>(155)</sup> This clock can be further divided by central or local clock dividers making it possible to use ATX PLL for data rates < 1 Gbps. For more information about ATX PLLs, refer to the Transceiver Clocking in Arria V Devices chapter and the Dynamic Reconfiguration in Arria V Devices chapter.

$t_{pll_powerdown}$  is the PLL powerdown minimum pulse width.

<sup>(157)</sup>  $t_{pll \ lock}$  is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

## **Core Performance Specifications**

## **Clock Tree Specifications**

#### Table 2-33: Clock Tree Performance for Arria V GZ Devices

| Symbol                    | Perfor  | Unit   |      |

|---------------------------|---------|--------|------|

| Symbol                    | C3, I3L | C4, I4 | Onit |

| Global and Regional Clock | 650     | 580    | MHz  |

| Periphery Clock           | 500     | 500    | MHz  |

## **PLL Specifications**

## Table 2-34: PLL Specifications for Arria V GZ Devices

| Symbol                            | Parameter                                               | Min | Тур | Max  | Unit |

|-----------------------------------|---------------------------------------------------------|-----|-----|------|------|

| f <sub>IN</sub> <sup>(167)</sup>  | Input clock frequency (C3, I3L speed grade)             | 5   | _   | 800  | MHz  |

| IIN                               | Input clock frequency (C4, I4 speed grade)              | 5   | _   | 650  | MHz  |

| f <sub>INPFD</sub>                | Input frequency to the PFD                              | 5   |     | 325  | MHz  |

| f <sub>FINPFD</sub>               | Fractional Input clock frequency to the PFD             | 50  | _   | 160  | MHz  |

| f <sub>VCO</sub> <sup>(168)</sup> | PLL VCO operating range (C3, I3L speed grade)           | 600 |     | 1600 | MHz  |

| IVCO                              | PLL VCO operating range (C4, I4 speed grade)            | 600 | _   | 1300 | MHz  |

| t <sub>EINDUTY</sub>              | Input clock or external feedback clock input duty cycle | 40  |     | 60   | %    |

<sup>(167)</sup> This specification is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

<sup>(168)</sup> The VCO frequency reported by the Quartus II software in the **PLL Usage Summary** section of the compilation report takes into consideration the VCO post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the f<sub>VCO</sub> specification.

Arria V GZ Device Datasheet

#### 2-44 Periphery Performance

| Description           | Min   | Тур   | Max   | Unit |

|-----------------------|-------|-------|-------|------|

| Diode ideality factor | 1.006 | 1.008 | 1.010 | —    |

## **Periphery Performance**

I/O performance supports several system interfaces, such as the **LVDS** high-speed I/O interface, external memory interface, and the **PCI/PCI-X** bus interface. General-purpose I/O standards such as 3.3-, 2.5-, 1.8-, and 1.5-**LVTTL/LVCMOS** are capable of a typical 167 MHz and 1.2-**LVCMOS** at 100 MHz interfacing frequency with a 10 pF load.

**Note:** The actual achievable frequency depends on design- and system-specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

#### High-Speed I/O Specification

**High-Speed Clock Specifications**

#### Table 2-39: High-Speed Clock Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

For LVDS applications, you must use the PLLs in integer PLL mode.

Arria V GZ devices support the following output standards using true LVDS output buffer types on all I/O banks.

- True RSDS output standard with data rates of up to 230 Mbps

- True mini-LVDS output standard with data rates of up to 340 Mbps

| Number of DQS Delay Buffers | C3, I3L | C4, I4 | Unit |

|-----------------------------|---------|--------|------|

| 4                           | 120     | 128    | ps   |

## **Memory Output Clock Jitter Specifications**

#### Table 2-50: Memory Output Clock Jitter Specification for Arria V GZ Devices

The clock jitter specification applies to the memory output clock pins generated using differential signal-splitter and DDIO circuits clocked by a PLL output routed on a PHY, regional, or global clock network as specified. Altera recommends using PHY clock networks whenever possible.

The clock jitter specification applies to the memory output clock pins clocked by an integer PLL.

The memory output clock jitter is applicable when an input jitter of 30 ps peak-to-peak is applied with bit error rate (BER) -12, equivalent to 14 sigma.

| Clock Network Parameter                                                                                                                           |                              | Symbol                 | C3, I3L |      | C4, I4 |      | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------|---------|------|--------|------|------|

| CIOCK NELWOIK                                                                                                                                     | ralameter                    | Symbol                 | Min     | Мах  | Min    | Мах  | Onic |

|                                                                                                                                                   | Clock period jitter          | t <sub>JIT(per)</sub>  | -55     | 55   | -55    | 55   | ps   |

| Regional                                                                                                                                          | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -110    | 110  | -110   | 110  | ps   |

|                                                                                                                                                   | Duty cycle jitter            | t <sub>JIT(duty)</sub> | -82.5   | 82.5 | -82.5  | 82.5 | ps   |

|                                                                                                                                                   | Clock period jitter          | t <sub>JIT(per)</sub>  | -82.5   | 82.5 | -82.5  | 82.5 | ps   |

| Global                                                                                                                                            | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -165    | 165  | -165   | 165  | ps   |

|                                                                                                                                                   | Duty cycle jitter            | t <sub>JIT(duty)</sub> | -90     | 90   | -90    | 90   | ps   |

|                                                                                                                                                   | Clock period jitter          | t <sub>JIT(per)</sub>  | -30     | 30   | -35    | 35   | ps   |

| $\begin{array}{ c c c } PHY \ Clock & Cycle-to-cycle \ period \ jitter & t_{JIT(cc)} \\ \hline Duty \ cycle \ jitter & t_{JIT(duty)} \end{array}$ |                              | t <sub>JIT(cc)</sub>   | -60     | 60   | -70    | 70   | ps   |

|                                                                                                                                                   |                              | t <sub>JIT(duty)</sub> | -45     | 45   | -56    | 56   | ps   |

#### Table 2-52: Worst-Case DCD on Arria V GZ I/O Pins

The DCD numbers do not cover the core clock network.

| Symbol            | C3, I3L |     | C4, 14 |     | Unit |  |

|-------------------|---------|-----|--------|-----|------|--|

| зушы              | Min     | Мах | Min    | Мах | Onit |  |

| Output Duty Cycle | 45      | 55  | 45     | 55  | %    |  |

## **Configuration Specification**

## **POR Specifications**

#### Table 2-53: Fast and Standard POR Delay Specification for Arria V GZ Devices

Select the POR delay based on the MSEL setting as described in the "Configuration Schemes for Arria V Devices" table in the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

| POR Delay | Minimum (ms) | Maximum (ms) |

|-----------|--------------|--------------|

| Fast      | 4            | 12 (202)     |

| Standard  | 100          | 300          |

**Related Information**

Configuration, Design Security, and Remote System Upgrades in Arria V Devices

**Altera Corporation**

<sup>&</sup>lt;sup>(202)</sup> The maximum pulse width of the fast POR delay is 12 ms, providing enough time for the PCIe hard IP to initialize after the POR trip.

| Term               | Definition                                                                                                                                                       |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OCM</sub>   | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                        |

| V <sub>OD</sub>    | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. |

| V <sub>SWING</sub> | Differential input voltage                                                                                                                                       |

| V <sub>X</sub>     | Input differential cross point voltage                                                                                                                           |

| V <sub>OX</sub>    | Output differential cross point voltage                                                                                                                          |

| W                  | High-speed I/O block—clock boost factor                                                                                                                          |

# **Document Revision History**

| Date          | Version    | Changes                                                                                                                                                                      |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2017 | 2017.02.10 | • Changed the minimum value for t <sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is 1" table.                          |

|               |            | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the<br/>DCLK-to-DATA[] Ratio is &gt;1" table.</li> </ul> |

|               |            | • Changed the minimum value for t <sub>CD2UMC</sub> in the "AS Timing Parameters for AS x1 and AS x4 Configurations in Arria V GZ Devices" table.                            |

|               |            | • Changed the minimum value for t <sub>CD2UMC</sub> in the "PS Timing Parameters for Arria V GZ Devices" table.                                                              |

|               |            | <ul> <li>Changed the minimum number of clock cycles value in the "Initialization Clock Source Option and the<br/>Maximum Frequency for Arria V GZ Devices" table.</li> </ul> |