Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 7362                                                       |

| Number of Logic Elements/Cells | 156000                                                     |

| Total RAM Bits                 | 11746304                                                   |

| Number of I/O                  | 416                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 896-BBGA, FCBGA                                            |

| Supplier Device Package        | 896-FBGA (31x31)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxba3d4f31i5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

|                                                             | 1-  |

|-------------------------------------------------------------|-----|

| Electrical Characteristics                                  |     |

| Operating Conditions                                        |     |

| Switching Characteristics                                   | 1-2 |

| Transceiver Performance Specifications                      | 1-2 |

| Core Performance Specifications                             |     |

| Periphery Performance                                       |     |

| HPS Specifications                                          |     |

| Configuration Specifications                                | 1-7 |

| POR Specifications                                          | 1-7 |

| FPGA JTAG Configuration Timing                              |     |

| FPP Configuration Timing                                    |     |

| AS Configuration Timing                                     | 1-8 |

| DCLK Frequency Specification in the AS Configuration Scheme | 1-8 |

| PS Configuration Timing                                     |     |

| Initialization                                              | 1-8 |

| Configuration Files                                         | 1-8 |

| Minimum Configuration Time Estimation                       | 1-8 |

| Remote System Upgrades                                      | 1-8 |

| User Watchdog Internal Oscillator Frequency Specifications  | 1-8 |

| I/O Timing                                                  | 1-8 |

| Programmable IOE Delay                                      | 1-8 |

| Programmable Output Buffer Delay                            | 1-8 |

| Glossary                                                    | 1-8 |

| Document Revision History                                   | 1-9 |

| Operating Conditions                                                                                                                                                                                                               | 2-1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Operating Conditions  Switching Characteristics  Transceiver Performance Specifications  Core Performance Specifications  Periphery Performance  Configuration Specification  POR Specifications  TAC Configuration Specifications | 2-21 |

| Transceiver Performance Specifications                                                                                                                                                                                             | 2-21 |

| Core Performance Specifications                                                                                                                                                                                                    | 2-37 |

| Periphery Performance                                                                                                                                                                                                              | 2-44 |

| Configuration Specification                                                                                                                                                                                                        | 2-56 |

| POR Specifications                                                                                                                                                                                                                 | 2-56 |

| JTAG Configuration Specifications                                                                                                                                                                                                  | 2-57 |

| Fast Passive Parallel (FPP) Configuration Timing                                                                                                                                                                                   | 2-57 |

| Active Serial Configuration Timing                                                                                                                                                                                                 | 2-65 |

| Active Serial Configuration Timing Passive Serial Configuration Timing                                                                                                                                                             | 2-67 |

| Initialization                                                                                                                                                                                                                     | 2-69 |

| Initialization                                                                                                                                                                                                                     | 2-69 |

| Remote System Upgrades Circuitry Timing Specification                                                                                                                                                                              | 2-70 |

| User Watchdog Internal Oscillator Frequency Specification                                                                                                                                                                          | 2-71 |

| User Watchdog Internal Oscillator Frequency Specification                                                                                                                                                                          | 2-71 |

| Programmable IOE Delay                                                                                                                                                                                                             | 2-72 |

| Programmable Output Buffer Delay                                                                                                                                                                                                   | 272. |

| Glossary                                                                                                                                                                                                                           | 2-73 |

| Document Revision History                                                                                                                                                                                                          | 2-78 |

|                                                                                                                                                                                                                                    |      |

# Arria V GX, GT, SX, and ST Device Datasheet

1

2017.02.10

AV-51002

This datasheet describes the electrical characteristics, switching characteristics, configuration specifications, and I/O timing for Arria<sup>®</sup> V devices.

Arria V devices are offered in commercial and industrial grades. Commercial devices are offered in -C4 (fastest), -C5, and -C6 speed grades. Industrial grade devices are offered in the -I3 and -I5 speed grades.

#### **Related Information**

**Arria V Device Overview**

Provides more information about the densities and packages of devices in the Arria V family.

## **Electrical Characteristics**

The following sections describe the operating conditions and power consumption of Arria V devices.

## **Operating Conditions**

Arria V devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Arria V devices, you must consider the operating requirements described in this section.

### **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Arria V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms.

The functional operation of the device is not implied for these conditions.

© 2017 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, NIOS, Quartus and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

| I/O Standard  |      | V <sub>CCIO</sub> (V) |      |      | $V_{SWING(DC)}(V)$ $V_{X(AC)}(V)$ |                             | V <sub>SWING(DC)</sub> (V) |                                | V <sub>X(AC)</sub> (V)                        |                           | V <sub>SI</sub> | <sub>WING(AC)</sub> (V) |

|---------------|------|-----------------------|------|------|-----------------------------------|-----------------------------|----------------------------|--------------------------------|-----------------------------------------------|---------------------------|-----------------|-------------------------|

| i/O Stalldard | Min  | Тур                   | Max  | Min  | Max                               | Min                         | Тур                        | Max                            | Min                                           | Max                       |                 |                         |

| SSTL-125      | 1.19 | 1.25                  | 1.31 | 0.18 | (15)                              | V <sub>CCIO</sub> /2 - 0.15 | V <sub>CCIO</sub> /2       | V <sub>CCIO</sub> /2<br>+ 0.15 | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |                 |                         |

### Differential HSTL and HSUL I/O Standards

Table 1-18: Differential HSTL and HSUL I/O Standards for Arria V Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>DI</sub> | <sub>F(DC)</sub> (V)    |                                                                     | $V_{X(AC)}(V)$ $V_{CM(DC)}(V)$ |                                                                     |                                                           | V <sub>DIF(AC)</sub> (V)  |                            |      |                          |

|------------------------|-------|-----------------------|-------|-----------------|-------------------------|---------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------|---------------------------|----------------------------|------|--------------------------|

| i/O Stailualu          | Min   | Тур                   | Max   | Min             | Max                     | Min                                                                 | Тур                            | Max                                                                 | Min                                                       | Тур                       | Max                        | Min  | Max                      |

| HSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.2             | _                       | 0.78                                                                | _                              | 1.12                                                                | 0.78                                                      | _                         | 1.12                       | 0.4  | _                        |

| HSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.2             | _                       | 0.68                                                                | _                              | 0.9                                                                 | 0.68                                                      | _                         | 0.9                        | 0.4  |                          |

| HSTL-12<br>Class I, II | 1.14  | 1.2                   | 1.26  | 0.16            | V <sub>CCIO</sub> + 0.3 | _                                                                   | $0.5 \times V_{\rm CCIO}$      | _                                                                   | $\begin{array}{c} 0.4 \times \\ V_{\rm CCIO} \end{array}$ | $0.5 \times V_{\rm CCIO}$ | $0.6 \times V_{\rm CCIO}$  | 0.3  | V <sub>CCIO</sub> + 0.48 |

| HSUL-12                | 1.14  | 1.2                   | 1.3   | 0.26            | 0.26                    | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} - \\ 0.12 \end{array}$ | $0.5 \times V_{\rm CCIO}$      | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} \\ + 0.12 \end{array}$ | $\begin{array}{c} 0.4 \times \\ V_{\rm CCIO} \end{array}$ | $0.5 \times V_{\rm CCIO}$ | 0.6 ×<br>V <sub>CCIO</sub> | 0.44 | 0.44                     |

### **Differential I/O Standard Specifications**

### Table 1-19: Differential I/O Standard Specifications for Arria V Devices

Differential inputs are powered by  $\rm V_{\rm CCPD}$  which requires 2.5 V.

# Transceiver Specifications for Arria V GT and ST Devices

Table 1-26: Reference Clock Specifications for Arria V GT and ST Devices

| Symbol/Description                         | Condition                                                | Tran            | sceiver Speed Gra | ide 3                           | Unit           |

|--------------------------------------------|----------------------------------------------------------|-----------------|-------------------|---------------------------------|----------------|

| 3ymbol/Description                         | Condition                                                | Min             | Тур               | Max                             | Offic          |

| Supported I/O standards                    | 1.2 V PCML, 1.4 VPCML,                                   | 1.5 V PCML, 2.5 | V PCML, Differe   | ential LVPECL <sup>(40)</sup> , | HCSL, and LVDS |

| Input frequency from REFCLK input pins     | _                                                        | 27              | _                 | 710                             | MHz            |

| Rise time                                  | Measure at ±60 mV of differential signal <sup>(41)</sup> | _               | _                 | 400                             | ps             |

| Fall time                                  | Measure at ±60 mV of differential signal <sup>(41)</sup> | _               | _                 | 400                             | ps             |

| Duty cycle                                 | _                                                        | 45              | _                 | 55                              | %              |

| Peak-to-peak differential input voltage    | _                                                        | 200             | _                 | 300 <sup>(42)</sup> /2000       | mV             |

| Spread-spectrum modulating clock frequency | PCI Express (PCIe)                                       | 30              | _                 | 33                              | kHz            |

| Spread-spectrum downspread                 | PCIe                                                     | _               | 0 to -0.5%        | _                               | _              |

| On-chip termination resistors              | _                                                        | _               | 100               | _                               | Ω              |

| V <sub>ICM</sub> (AC coupled)              | _                                                        | _               | 1.2               | _                               | V              |

| V <sub>ICM</sub> (DC coupled)              | HCSL I/O standard for the PCIe reference clock           | 250             | _                 | 550                             | mV             |

Send Feedback

<sup>(40)</sup> Differential LVPECL signal levels must comply to the minimum and maximum peak-to-peak differential input voltage specified in this table.

<sup>(41)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

<sup>(42)</sup> The maximum peak-to peak differential input voltage of 300 mV is allowed for DC coupled link.

| Symbol/Description                                                                                  | Condition                 | Т     | ransceiver Speed Gr      | Unit    |       |

|-----------------------------------------------------------------------------------------------------|---------------------------|-------|--------------------------|---------|-------|

| Symbol/Description                                                                                  | Condition                 | Min   | Тур                      | Max     | Offic |

| Data rate (10-Gbps transceiver) <sup>(44)</sup>                                                     | _                         | 0.611 | _                        | 10.3125 | Gbps  |

| Absolute V <sub>MAX</sub> for a receiver pin <sup>(45)</sup>                                        | _                         | _     | _                        | 1.2     | V     |

| Absolute V <sub>MIN</sub> for a receiver pin                                                        | _                         | -0.4  | _                        | _       | V     |

| Maximum peak-to-peak differential input voltage $V_{\rm ID}$ (diff p-p) before device configuration | _                         | _     | _                        | 1.6     | V     |

| Maximum peak-to-peak differential input voltage $V_{\rm ID}$ (diff p-p) after device configuration  | _                         | _     | _                        | 2.2     | V     |

| Minimum differential eye opening at the receiver serial input pins (46)                             | _                         | 100   | _                        | _       | mV    |

| V <sub>ICM</sub> (AC coupled)                                                                       | _                         | _     | 750 <sup>(47)</sup> /800 | _       | mV    |

| V <sub>ICM</sub> (DC coupled)                                                                       | ≤ 3.2Gbps <sup>(48)</sup> | 670   | 700                      | 730     | mV    |

|                                                                                                     | 85-Ω setting              |       | 85                       |         | Ω     |

| Differential on-chip termination                                                                    | 100-Ω setting             |       | 100                      |         | Ω     |

| resistors                                                                                           | 120-Ω setting             |       | 120                      |         | Ω     |

|                                                                                                     | 150- $\Omega$ setting     |       | 150                      |         | Ω     |

| t <sub>LTR</sub> <sup>(49)</sup>                                                                    | _                         | _     | _                        | 10      | μs    |

| $t_{\mathrm{LTD}}^{(50)}$                                                                           | _                         | 4     | _                        | _       | μs    |

<sup>(45)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

<sup>(46)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the **Receiver Equalization** feature. If you enable the **Receiver Equalization** feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

$<sup>^{(47)}\,</sup>$  The AC coupled  $V_{ICM}$  is 750 mV for PCIe mode only.

<sup>(48)</sup> For standard protocol compliance, use AC coupling.

$t_{LTR}$  is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

<sup>(50)</sup> t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

| Quartus Prime 1st                 |             |             | Quar        | tus Prime V <sub>OD</sub> Se | etting      |             |              |      |

|-----------------------------------|-------------|-------------|-------------|------------------------------|-------------|-------------|--------------|------|

| Post Tap Pre-<br>Emphasis Setting | 10 (200 mV) | 20 (400 mV) | 30 (600 mV) | 35 (700 mV)                  | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) | Unit |

| 16                                | _           | _           | 9.56        | 7.73                         | 6.49        | _           | _            | dB   |

| 17                                | _           | _           | 10.43       | 8.39                         | 7.02        | _           | _            | dB   |

| 18                                | _           | _           | 11.23       | 9.03                         | 7.52        | _           | _            | dB   |

| 19                                | _           | _           | 12.18       | 9.7                          | 8.02        | _           | _            | dB   |

| 20                                | _           | _           | 13.17       | 10.34                        | 8.59        | _           | _            | dB   |

| 21                                | _           | _           | 14.2        | 11.1                         | _           | _           | _            | dB   |

| 22                                | _           | _           | 15.38       | 11.87                        | _           | _           | _            | dB   |

| 23                                | _           | _           | _           | 12.67                        | _           | _           | _            | dB   |

| 24                                | _           | _           | _           | 13.48                        | _           | _           | _            | dB   |

| 25                                | _           | _           | _           | 14.37                        | _           | _           | _            | dB   |

| 26                                | _           | _           | _           | _                            | _           | _           | _            | dB   |

| 27                                | _           | _           | _           | _                            | _           | _           | _            | dB   |

| 28                                | _           | _           | _           | _                            | _           | _           | _            | dB   |

| 29                                | _           | _           | _           | _                            | _           | _           | _            | dB   |

| 30                                | _           | _           | _           | _                            | _           | _           | _            | dB   |

| 31                                | _           | _           | _           | _                            | _           | _           | _            | dB   |

#### **Related Information**

**SPICE Models for Altera Devices**

Provides the Arria V HSSI HSPICE models.

## **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Arria V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Altera Sales Representative.

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

| Protocol                             | Sub-protocol      | Data Rate (Mbps) |

|--------------------------------------|-------------------|------------------|

|                                      | CPRI E6LV         | 614.4            |

|                                      | CPRI E6HV         | 614.4            |

|                                      | CPRI E6LVII       | 614.4            |

|                                      | CPRI E12LV        | 1,228.8          |

|                                      | CPRI E12HV        | 1,228.8          |

|                                      | CPRI E12LVII      | 1,228.8          |

| Common Public Radio Interface (CPRI) | CPRI E24LV        | 2,457.6          |

|                                      | CPRI E24LVII      | 2,457.6          |

|                                      | CPRI E30LV        | 3,072            |

|                                      | CPRI E30LVII      | 3,072            |

|                                      | CPRI E48LVII      | 4,915.2          |

|                                      | CPRI E60LVII      | 6,144            |

|                                      | CPRI E96LVIII(60) | 9,830.4          |

| Gbps Ethernet (GbE)                  | GbE 1250          | 1,250            |

|                                      | OBSAI 768         | 768              |

| OBSAI                                | OBSAI 1536        | 1,536            |

| OBSAI                                | OBSAI 3072        | 3,072            |

|                                      | OBSAI 6144        | 6,144            |

|                                      | SDI 270 SD        | 270              |

| Serial digital interface (SDI)       | SDI 1485 HD       | 1,485            |

|                                      | SDI 2970 3G       | 2,970            |

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

<sup>(60)</sup> You can achieve compliance with TX channel restriction of one HSSI channel per six-channel transceiver bank.

| Symbol                                                                                                                                       | Condition                                                |      | −l3, −C4 |      |      | −l5, −C5 |      | -C6  |     |      | Unit  |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|----------|------|------|----------|------|------|-----|------|-------|

| Зупірої                                                                                                                                      | Condition                                                | Min  | Тур      | Max  | Min  | Тур      | Max  | Min  | Тур | Max  | Offic |

|                                                                                                                                              | SERDES factor $J \ge 8^{(76)(78)}$ , LVDS TX with RX DPA | (77) | _        | 1600 | (77) | _        | 1500 | (77) | _   | 1250 | Mbps  |

|                                                                                                                                              | SERDES factor J = 1<br>to 2, Uses DDR<br>Registers       | (77) | _        | (79) | (77) | _        | (79) | (77) | _   | (79) | Mbps  |

| Emulated Differential I/<br>O Standards with Three<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup> | SERDES factor J = 4<br>to 10 <sup>(81)</sup>             | (77) | _        | 945  | (77) | _        | 945  | (77) | _   | 945  | Mbps  |

| Emulated Differential I/<br>O Standards with One<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup>   | SERDES factor J = 4<br>to 10 <sup>(81)</sup>             | (77) | _        | 200  | (77) | _        | 200  | (77) | _   | 200  | Mbps  |

| t <sub>x Jitter</sub> -True Differential<br>I/O Standards                                                                                    | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps    | _    | _        | 160  | _    | _        | 160  | _    | _   | 160  | ps    |

| 1/O Standards                                                                                                                                | Total Jitter for Data<br>Rate < 600 Mbps                 | _    | _        | 0.1  | _    | _        | 0.1  | _    | _   | 0.1  | UI    |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

$<sup>^{(78)}\,</sup>$  The  $V_{CC}$  and  $V_{CCP}$  must be on a separate power layer and a maximum load of 5 pF for chip-to-chip interface.

<sup>(79)</sup> The maximum ideal data rate is the SERDES factor (J) x the PLL maximum output frequency (f<sub>OUT</sub>), provided you can close the design timing and the signal integrity simulation is clean.

You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine the leftover timing margin.

<sup>(81)</sup> When using True LVDS RX channels for emulated LVDS TX channel, only serialization factors 1 and 2 are supported.

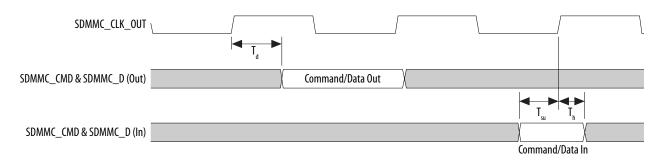

After the Boot ROM code exits and control is passed to the preloader, software can adjust the value of drvsel and smplsel via the system manager. drvsel can be set from 1 to 7 and smplsel can be set from 0 to 7. While the preloader is executing, the values for SDMMC\_CLK and SDMMC\_CLK\_OUT increase to a maximum of 200 MHz and 50 MHz respectively.

The SD/MMC interface calibration support will be available in a future release of the preloader through the SoC EDS software update.

| Symbol                                         | Description                                      | Min                                                          | Max                                                                                       | Unit |

|------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|

|                                                | SDMMC_CLK clock period (Identification mode)     | 20                                                           | _                                                                                         | ns   |

| $T_{sdmmc\_clk}$ (internal reference clock)    | SDMMC_CLK clock period (Default speed mode)      | 5                                                            | _                                                                                         | ns   |

|                                                | SDMMC_CLK clock period (High speed mode)         | 5                                                            | _                                                                                         | ns   |

|                                                | SDMMC_CLK_OUT clock period (Identification mode) | 2500                                                         | _                                                                                         | ns   |

| $T_{sdmmc\_clk\_out}$ (interface output clock) | SDMMC_CLK_OUT clock period (Default speed mode)  | 40                                                           | _                                                                                         | ns   |

|                                                | SDMMC_CLK_OUT clock period (High speed mode)     | 20                                                           | _                                                                                         | ns   |

| $T_{ m dutycycle}$                             | SDMMC_CLK_OUT duty cycle                         | 45                                                           | 55                                                                                        | %    |

| $T_d$                                          | SDMMC_CMD/SDMMC_D output delay                   | $(T_{sdmmc\_clk} \times \texttt{drvsel})/2 - 1.23^{(87)}$    | $\begin{array}{c} (T_{sdmmc\_clk} \times \texttt{drvsel})/2 \\ + 1.69^{(87)} \end{array}$ | ns   |

| $\mathrm{T_{su}}$                              | Input setup time                                 | $1.05 - (T_{\rm sdmmc\_clk} \times \\ \rm smplsel)/2^{(88)}$ | _                                                                                         | ns   |

| $T_{\mathrm{h}}$                               | Input hold time                                  | $(T_{sdmmc\_clk} \times smplsel)/ 2^{(88)}$                  | _                                                                                         | ns   |

$<sup>^{(87)}</sup>$  drysel is the drive clock phase shift select value.

<sup>(88)</sup> smplsel is the sample clock phase shift select value.

Figure 1-11: SD/MMC Timing Diagram

#### **Related Information**

Booting and Configuration Chapter, Arria V Hard Processor System Technical Reference Manual

Provides more information about CSEL pin settings in the SD/MMC Controller CSEL Pin Settings table.

### **USB Timing Characteristics**

PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.

Table 1-55: USB Timing Requirements for Arria V Devices

| Symbol    | Description                                  | Min | Тур   | Max | Unit |

|-----------|----------------------------------------------|-----|-------|-----|------|

| $T_{clk}$ | USB CLK clock period                         | _   | 16.67 | _   | ns   |

| $T_d$     | CLK to USB_STP/USB_DATA[7:0] output delay    | 4.4 | _     | 11  | ns   |

| $T_{su}$  | Setup time for USB_DIR/USB_NXT/USB_DATA[7:0] | 2   | _     | _   | ns   |

| $T_h$     | Hold time for USB_DIR/USB_NXT/USB_DATA[7:0]  | 1   | _     | _   | ns   |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

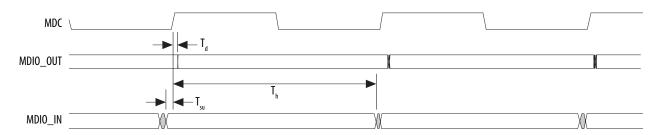

Figure 1-15: MDIO Timing Diagram

# I<sup>2</sup>C Timing Characteristics

Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Cumbal                | Description -                                     | Standaı | d Mode | Fast I | Mode | - Unit |  |

|-----------------------|---------------------------------------------------|---------|--------|--------|------|--------|--|

| Symbol                | Description                                       | Min     | Max    | Min    | Max  | Onit   |  |

| $T_{clk}$             | Serial clock (SCL) clock period                   | 10      | _      | 2.5    | _    | μs     |  |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7     | _      | 0.6    | _    | μs     |  |

| $T_{clklow}$          | SCL low time                                      | 4       | _      | 1.3    | _    | μs     |  |

| $T_s$                 | Setup time for serial data line (SDA) data to SCL | 0.25    | _      | 0.1    | _    | μs     |  |

| $T_{h}$               | Hold time for SCL to SDA data                     | 0       | 3.45   | 0      | 0.9  | μs     |  |

| $T_d$                 | SCL to SDA output data delay                      | _       | 0.2    | _      | 0.2  | μs     |  |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7     | _      | 0.6    | _    | μs     |  |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4       | _      | 0.6    | _    | μs     |  |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4       | _      | 0.6    | _    | μs     |  |

AV-51002 2017.02.10

| Term                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Definition                  |              |                     |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------|---------------------|--|--|--|

| Single-ended voltage referenced I/O standard | The JEDEC standard for the SSTL and HSTL I/O defines both the AC and DC input signal values. The AC values indicate the voltage levels at which the receiver must meet its timing specifications. The DC values indicate the voltage levels at which the final logic state of the receiver is unambiguously defined. After the receiver input has crossed the AC value, the receiver changes to the new logic state.  The new logic state is then maintained as long as the input stays beyond the DC threshold. This approach is intended to provide predictable receiver timing in the presence of input waveform ringing.  Single-Ended Voltage Referenced I/O Standard |                             |              |                     |  |  |  |

|                                              | Single-Ended voltage Referenced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1/O Standard                |              |                     |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |              | V <sub>CC10</sub>   |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |              |                     |  |  |  |

|                                              | V <sub>OH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |              | V <sub>IH(AC)</sub> |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |              | V <sub>IH(DC)</sub> |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V REF                       |              | V <sub>IL(DC)</sub> |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |              | V IL(AC)            |  |  |  |

|                                              | V <sub>0L</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |              |                     |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |              | V <sub>SS</sub>     |  |  |  |

| $t_{\rm C}$                                  | High-speed receiver/transmitter in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nput and output clock perio | od.          |                     |  |  |  |

| TCCS (channel-to-channel-skew)               | The timing difference between the fastest and slowest output edges, including the t <sub>CO</sub> variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table).                                                                                                                                                                                                                                                                                                                                                                                             |                             |              |                     |  |  |  |

| $t_{ m DUTY}$                                | High-speed I/O block—Duty cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e on high-speed transmitte  | r output clo | ock.                |  |  |  |

Arria V GX, GT, SX, and ST Device Datasheet **Altera Corporation**

| Symbol                      | Description                                                            | Conditions                        | Resistance | - Unit |       |  |

|-----------------------------|------------------------------------------------------------------------|-----------------------------------|------------|--------|-------|--|

| Зушьог                      | Description                                                            | Conditions                        | C3, I3L    | C4, I4 | Offic |  |

| 25- $\Omega$ R <sub>S</sub> | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 and 1.5 V | ±40        | ±40    | %     |  |

| 25-Ω R <sub>S</sub>         | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO} = 1.2 \text{ V}$        | ±50        | ±50    | %     |  |

| 50-Ω R <sub>S</sub>         | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 and 1.5 V | ±40        | ±40    | %     |  |

| 50-Ω R <sub>S</sub>         | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO} = 1.2 \text{ V}$        | ±50        | ±50    | %     |  |

| 100-Ω R <sub>D</sub>        | Internal differential termination (100- $\Omega$ setting)              | $V_{CCIO} = 2.5 \text{ V}$        | ±25        | ±25    | %     |  |

Figure 2-1: OCT Variation Without Re-Calibration for Arria V GZ Devices

$$R_{OCT} = R_{SCAL} \left( 1 + \left( \frac{dR}{dT} \times \triangle T \right) \pm \left( \frac{dR}{dV} \times \triangle V \right) \right)$$

#### Notes:

- 1. The  $R_{OCT}$  value shows the range of OCT resistance with the variation of temperature and  $V_{CCIO}$ .

- 2.  $R_{SCAI}$  is the OCT resistance value at power-up.

- 3.  $\Delta T$  is the variation of temperature with respect to the temperature at power-up.

- 4.  $\Delta V$  is the variation of voltage with respect to the  $V_{CCIO}$  at power-up.

- 5. dR/dT is the percentage change of  $R_{\text{SCAL}}$  with temperature.

- 6. dR/dV is the percentage change of  $R_{SCAI}$  with voltage.

### Table 2-12: OCT Variation after Power-Up Calibration for Arria V GZ Devices

Valid for a  $V_{CCIO}$  range of ±5% and a temperature range of 0° to 85°C.

Altera Corporation Arria V GZ Device Datasheet

### **Hot Socketing**

Table 2-14: Hot Socketing Specifications for Arria V GZ Devices

| Symbol                    | Description                                | Maximum               |

|---------------------------|--------------------------------------------|-----------------------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                     | 300 μΑ                |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                     | 8 mA <sup>(124)</sup> |

| I <sub>XCVR-TX (DC)</sub> | DC current per transceiver transmitter pin | 100 mA                |

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver pin    | 50 mA                 |

### **Internal Weak Pull-Up Resistor**

### Table 2-15: Internal Weak Pull-Up Resistor for Arria V GZ Devices

All I/O pins have an option to enable the weak pull-up resistor except the configuration, test, and JTAG pins. The internal weak pull-down feature is only available for the JTAG TCK pin. The typical value for this internal weak pull-down resistor is approximately 25 k $\Omega$ .

| Symbol   | Description                                                                                                   | V <sub>CCIO</sub> Conditions (V) (125) | Value (126) | Unit |

|----------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------|------|

|          |                                                                                                               | 3.0 ±5%                                | 25          | kΩ   |

|          |                                                                                                               | 2.5 ±5%                                | 25          | kΩ   |

|          | Value of the I/O pin pull-up resistor                                                                         | 1.8 ±5%                                | 25          | kΩ   |

| $R_{PU}$ | before and during configuration, as well as user mode if you enable the programmable pull-up resistor option. | 1.5 ±5%                                | 25          | kΩ   |

|          |                                                                                                               | 1.35 ±5%                               | 25          | kΩ   |

|          |                                                                                                               | 1.25 ±5%                               | 25          | kΩ   |

|          |                                                                                                               | 1.2 ±5%                                | 25          | kΩ   |

The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{\rm IOPIN}| = C \, dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

Altera Corporation

Arria V GZ Device Datasheet

The pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{\rm CCIO}$ .

$<sup>^{(126)}</sup>$  These specifications are valid with a  $\pm 10\%$  tolerance to cover changes over PVT.

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>DIF</sub> | V <sub>DIF(DC)</sub> (V) |                         | $V_{X(AC)}(V)$                       |                       | V <sub>CM(DC)</sub> (V)             |                           |                                   | V <sub>DIF(AC)</sub> (V)     |      |                             |

|------------------------|-----------------------|-----|------------------|--------------------------|-------------------------|--------------------------------------|-----------------------|-------------------------------------|---------------------------|-----------------------------------|------------------------------|------|-----------------------------|

| i/O Standard           | Min                   | Тур | Max              | Min                      | Max                     | Min                                  | Тур                   | Max                                 | Min                       | Тур                               | Max                          | Min  | Max                         |

| HSTL-12 Class<br>I, II | 1.14                  | 1.2 | 1.26             | 0.16                     | V <sub>CCIO</sub> + 0.3 | _                                    | $0.5 \times V_{CCIO}$ | _                                   | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub><br>IO | $0.6 \times V_{\text{CCIO}}$ | 0.3  | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14                  | 1.2 | 1.3              | 0.26                     | 0.26                    | 0.5 ×<br>V <sub>CCIO</sub> –<br>0.12 | $0.5 \times V_{CCIO}$ | $0.5 \times V_{\rm CCIO} \\ + 0.12$ | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub>       | 0.6 ×<br>V <sub>CCIO</sub>   | 0.44 | 0.44                        |

Table 2-21: Differential I/O Standard Specifications for Arria V GZ Devices

| I/O Standard             | V <sub>CCIO</sub> (V) <sup>(128)</sup>                                                                               |                              | V <sub>ID</sub> (mV) <sup>(129)</sup> |      | V <sub>ICM(DC)</sub> (V)    |                                | V <sub>OD</sub> (V) <sup>(130)</sup> |           | V <sub>OCM</sub> (V) <sup>(130)</sup> |       |       |       |       |     |     |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------|------|-----------------------------|--------------------------------|--------------------------------------|-----------|---------------------------------------|-------|-------|-------|-------|-----|-----|

| i/O Standard             | Min                                                                                                                  | Тур                          | Max                                   | Min  | Condition                   | Max                            | Min                                  | Condition | Max                                   | Min   | Тур   | Max   | Min   | Тур | Max |

| PCML                     | receiver, and reference clock I/O pin specifications, refer to the "Transceiver Performance Specifications" section. |                              |                                       |      |                             |                                |                                      |           |                                       |       |       |       |       |     |     |

| 2.5 V<br>LVDS<br>(131) 2 | 2.375 2.5 2.625                                                                                                      | 100 V <sub>CM</sub> = 1.25 V | V <sub>CM</sub> =                     | _    | 0.05                        | D <sub>MAX</sub> ≤<br>700 Mbps | 1.8                                  | 0.247     | _                                     | 0.6   | 1.125 | 1.25  | 1.375 |     |     |

|                          |                                                                                                                      |                              | _                                     | 1.05 | D <sub>MAX</sub> > 700 Mbps | 1.55                           | 0.247                                | _         | 0.6                                   | 1.125 | 1.25  | 1.375 |       |     |     |

| BLVDS<br>(132)           | 2.375                                                                                                                | 2.5                          | 2.625                                 | 100  | _                           | _                              | _                                    | _         | _                                     | _     | _     | _     | _     | _   | _   |

$<sup>^{\</sup>left(128\right)}\,$  Differential inputs are powered by VCCPD which requires 2.5 V.

Arria V GZ Device Datasheet

Altera Corporation

<sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>(130)</sup> RL range:  $90 \le RL \le 110 \Omega$ .

<sup>(131)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.6 V for data rates above 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

<sup>(132)</sup> There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

| Symbol                       | Parameter                                                                                                 | Min | Тур | Max | Unit |

|------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $ m f_{OUT}$ $^{(169)}$      | Output frequency for an internal global or regional clock (C3, I3L speed grade)                           | _   | _   | 650 | MHz  |

| TOUT                         | Output frequency for an internal global or regional clock (C4, I4 speed grade)                            | _   | _   | 580 | MHz  |

| $ m f_{OUT\_EXT}$ $^{(169)}$ | Output frequency for an external clock output (C3, I3L speed grade)                                       | _   | _   | 667 | MHz  |

| TOUT_EXT                     | Output frequency for an external clock output (C4, I4 speed grade)                                        | _   | _   | 533 | MHz  |

| t <sub>OUTDUTY</sub>         | Duty cycle for a dedicated external clock output (when set to 50%)                                        | 45  | 50  | 55  | %    |

| $t_{FCOMP}$                  | External feedback clock compensation time                                                                 | _   | _   | 10  | ns   |

| f <sub>DYCONFIGCLK</sub>     | Dynamic configuration clock for mgmt_clk and scanclk                                                      | _   | _   | 100 | MHz  |

| t <sub>LOCK</sub>            | Time required to lock from the end-of-device configuration or deassertion of areset                       | _   | _   | 1   | ms   |

| t <sub>DLOCK</sub>           | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/ delays) |     | _   | 1   | ms   |

|                              | PLL closed-loop low bandwidth                                                                             | _   | 0.3 | _   | MHz  |

| $f_{CLBW}$                   | PLL closed-loop medium bandwidth                                                                          | _   | 1.5 | _   | MHz  |

|                              | PLL closed-loop high bandwidth (170)                                                                      | _   | 4   | _   | MHz  |

| t <sub>PLL_PSERR</sub>       | Accuracy of PLL phase shift                                                                               | _   | _   | ±50 | ps   |

| t <sub>ARESET</sub>          | Minimum pulse width on the areset signal                                                                  | 10  | _   | _   | ns   |

This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $f_{OUT}$  of the PLL. High bandwidth PLL settings are not supported in external feedback mode.

Arria V GZ Device Datasheet **Altera Corporation**

| Momory        | Mode -                                                                                           | Resour | rces Used |            |     | - Unit |     |      |

|---------------|--------------------------------------------------------------------------------------------------|--------|-----------|------------|-----|--------|-----|------|

| Memory        | Mode                                                                                             | ALUTs  | Memory    | <b>C</b> 3 | C4  | I3L    | 14  | Onit |

|               | Single-port, all supported widths                                                                | 0      | 1         | 650        | 550 | 500    | 450 | MHz  |

|               | Simple dual-port, all supported widths                                                           | 0      | 1         | 650        | 550 | 500    | 450 | MHz  |

|               | Simple dual-port with the read-during-write option set to <b>Old Data</b> , all supported widths | 0      | 1         | 455        | 400 | 455    | 400 | MHz  |

| M20K<br>Block | Simple dual-port with ECC enabled, $512 \times 32$                                               | 0      | 1         | 400        | 350 | 400    | 350 | MHz  |

|               | Simple dual-port with ECC and optional pipeline registers enabled, $512 \times 32$               | 0      | 1         | 500        | 450 | 500    | 450 | MHz  |

|               | True dual port, all supported widths                                                             | 0      | 1         | 650        | 550 | 500    | 450 | MHz  |

|               | ROM, all supported widths                                                                        | 0      | 1         | 650        | 550 | 500    | 450 | MHz  |

# **Temperature Sensing Diode Specifications**

Table 2-37: Internal Temperature Sensing Diode Specification

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate  | Conversion Time | Resolution | Minimum Resolution<br>with no Missing<br>Codes |

|-------------------|----------|-----------------------------|----------------|-----------------|------------|------------------------------------------------|

| −40°C to 100°C    | ±8°C     | No                          | 1 MHz, 500 kHz | < 100 ms        | 8 bits     | 8 bits                                         |

## Table 2-38: External Temperature Sensing Diode Specifications for Arria V GZ Devices

| Description                              | Min | Тур | Max | Unit |

|------------------------------------------|-----|-----|-----|------|

| I <sub>bias</sub> , diode source current | 8   | _   | 200 | μΑ   |

| V <sub>bias</sub> , voltage across diode | 0.3 | _   | 0.9 | V    |

| Series resistance                        | _   | _   | < 1 | Ω    |

Arria V GZ Device Datasheet

Altera Corporation

### **Duty Cycle Distortion (DCD) Specifications**

### Table 2-52: Worst-Case DCD on Arria V GZ I/O Pins

The DCD numbers do not cover the core clock network.

| Symbol            | С   | 3, I3L | C   | Unit |       |

|-------------------|-----|--------|-----|------|-------|

| Symbol            | Min | Max    | Min | Max  | Offic |

| Output Duty Cycle | 45  | 55     | 45  | 55   | %     |

# **Configuration Specification**

# **POR Specifications**

### Table 2-53: Fast and Standard POR Delay Specification for Arria V GZ Devices

Select the POR delay based on the MSEL setting as described in the "Configuration Schemes for Arria V Devices" table in the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

| POR Delay | Minimum (ms) | Maximum (ms) |

|-----------|--------------|--------------|

| Fast      | 4            | 12 (202)     |

| Standard  | 100          | 300          |

#### **Related Information**

Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Altera Corporation Arria V GZ Device Datasheet

<sup>(202)</sup> The maximum pulse width of the fast POR delay is 12 ms, providing enough time for the PCIe hard IP to initialize after the POR trip.

| Term               | Definition                                                                                                                                                       |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $V_{OCM}$          | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                        |  |

| V <sub>OD</sub>    | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. |  |

| V <sub>SWING</sub> | Differential input voltage                                                                                                                                       |  |

| $V_{X}$            | Input differential cross point voltage                                                                                                                           |  |

| V <sub>OX</sub>    | Output differential cross point voltage                                                                                                                          |  |

| W                  | High-speed I/O block—clock boost factor                                                                                                                          |  |

# **Document Revision History**

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2017 | 2017.02.10 | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is 1" table.</li> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is &gt;1" table.</li> </ul>                                                                                                                     |

|               |            | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "AS Timing Parameters for AS x1 and AS x4 Configurations in Arria V GZ Devices" table.</li> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "PS Timing Parameters for Arria V GZ Devices" table.</li> <li>Changed the minimum number of clock cycles value in the "Initialization Clock Source Option and the Maximum Frequency for Arria V GZ Devices" table.</li> </ul> |

Altera Corporation Arria V GZ Device Datasheet