# E·XFL

#### Intel - 5AGXBA5D4F27C5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 8962                                                       |

| Number of Logic Elements/Cells | 190000                                                     |

| Total RAM Bits                 | 13284352                                                   |

| Number of I/O                  | 336                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 672-BBGA, FCBGA                                            |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxba5d4f27c5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Caution:** Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

#### Table 1-1: Absolute Maximum Ratings for Arria V Devices

| Symbol                    | Description                                                                                                      | Minimum | Maximum | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>           | Core voltage power supply                                                                                        | -0.50   | 1.43    | V    |

| V <sub>CCP</sub>          | Periphery circuitry, PCIe <sup>®</sup> hardIP block, and transceiver physical coding sublayer (PCS) power supply | -0.50   | 1.43    | V    |

| V <sub>CCPGM</sub>        | Configuration pins power supply                                                                                  | -0.50   | 3.90    | V    |

| V <sub>CC_AUX</sub>       | Auxiliary supply                                                                                                 | -0.50   | 3.25    | V    |

| V <sub>CCBAT</sub>        | Battery back-up power supply for design security volatile key register                                           | -0.50   | 3.90    | V    |

| V <sub>CCPD</sub>         | I/O pre-driver power supply                                                                                      | -0.50   | 3.90    | V    |

| V <sub>CCIO</sub>         | I/O power supply                                                                                                 | -0.50   | 3.90    | V    |

| V <sub>CCD_FPLL</sub>     | Phase-locked loop (PLL) digital power supply                                                                     | -0.50   | 1.80    | V    |

| V <sub>CCA_FPLL</sub>     | PLL analog power supply                                                                                          | -0.50   | 3.25    | V    |

| V <sub>CCA_GXB</sub>      | Transceiver high voltage power                                                                                   | -0.50   | 3.25    | V    |

| V <sub>CCH_GXB</sub>      | Transmitter output buffer power                                                                                  | -0.50   | 1.80    | V    |

| V <sub>CCR_GXB</sub>      | Receiver power                                                                                                   | -0.50   | 1.50    | V    |

| V <sub>CCT_GXB</sub>      | Transmitter power                                                                                                | -0.50   | 1.50    | V    |

| V <sub>CCL_GXB</sub>      | Transceiver clock network power                                                                                  | -0.50   | 1.50    | V    |

| VI                        | DC input voltage                                                                                                 | -0.50   | 3.80    | V    |

| V <sub>CC_HPS</sub>       | HPS core voltage and periphery circuitry power supply                                                            | -0.50   | 1.43    | V    |

| V <sub>CCPD_HPS</sub>     | HPS I/O pre-driver power supply                                                                                  | -0.50   | 3.90    | V    |

| V <sub>CCIO_HPS</sub>     | HPS I/O power supply                                                                                             | -0.50   | 3.90    | V    |

| V <sub>CCRSTCLK_HPS</sub> | HPS reset and clock input pins power supply                                                                      | -0.50   | 3.90    | V    |

| Symbol                           | Description                                | Condition    | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|----------------------------------|--------------------------------------------|--------------|------------------------|---------|------------------------|------|

|                                  |                                            | 3.3 V        | 3.135                  | 3.3     | 3.465                  | V    |

|                                  |                                            | 3.0 V        | 2.85                   | 3.0     | 3.15                   | V    |

|                                  |                                            | 2.5 V        | 2.375                  | 2.5     | 2.625                  | V    |

| V                                | I/O buffers power supply                   | 1.8 V        | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CCIO</sub>                | 1/O builets power supply                   | 1.5 V        | 1.425                  | 1.5     | 1.575                  | V    |

|                                  |                                            | 1.35 V       | 1.283                  | 1.35    | 1.418                  | V    |

|                                  |                                            | 1.25 V       | 1.19                   | 1.25    | 1.31                   | V    |

|                                  |                                            | 1.2 V        | 1.14                   | 1.2     | 1.26                   | V    |

| V <sub>CCD_FPLL</sub>            | PLL digital voltage regulator power supply | _            | 1.425                  | 1.5     | 1.575                  | V    |

| V <sub>CCA_FPLL</sub>            | PLL analog voltage regulator power supply  | _            | 2.375                  | 2.5     | 2.625                  | V    |

| VI                               | DC input voltage                           | —            | -0.5                   |         | 3.6                    | V    |

| V <sub>O</sub>                   | Output voltage                             | —            | 0                      |         | V <sub>CCIO</sub>      | V    |

|                                  | Operating junction temperature             | Commercial   | 0                      |         | 85                     | °C   |

| TJ                               |                                            | Industrial   | -40                    |         | 100                    | °C   |

| <b>t</b> (4)                     | Power supply ramp time                     | Standard POR | 200 µs                 |         | 100 ms                 | _    |

| t <sub>RAMP</sub> <sup>(4)</sup> |                                            | Fast POR     | 200 µs                 |         | 4 ms                   |      |

<sup>&</sup>lt;sup>(1)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(4)</sup> This is also applicable to HPS power supply. For HPS power supply, refer to  $t_{RAMP}$  specifications for standard POR when HPS\_PORSEL = 0 and  $t_{RAMP}$  specifications for fast POR when HPS\_PORSEL = 1.

#### Figure 1-1: Equation for OCT Variation Without Recalibration

$$R_{OCT} = R_{SCAL} \left( 1 + \left( \frac{dR}{dT} \times \Delta T \right) \pm \left( \frac{dR}{dV} \times \Delta V \right) \right)$$

The definitions for the equation are as follows:

- The R<sub>OCT</sub> value calculated shows the range of OCT resistance with the variation of temperature and V<sub>CCIO</sub>.

- R<sub>SCAL</sub> is the OCT resistance value at power-up.

- $\Delta T$  is the variation of temperature with respect to the temperature at power up.

- $\Delta V$  is the variation of voltage with respect to the V<sub>CCIO</sub> at power up.

- dR/dT is the percentage change of R<sub>SCAL</sub> with temperature.

- dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

#### OCT Variation after Power-Up Calibration

#### Table 1-10: OCT Variation after Power-Up Calibration for Arria V Devices

This table lists OCT variation with temperature and voltage after power-up calibration. The OCT variation is valid for a  $V_{CCIO}$  range of  $\pm 5\%$  and a temperature range of 0°C to 85°C.

| Symbol | Description                                      | V <sub>CCIO</sub> (V) | Value | Unit |

|--------|--------------------------------------------------|-----------------------|-------|------|

|        |                                                  | 3.0                   | 0.100 |      |

|        |                                                  | 2.5                   | 0.100 |      |

|        | OCT variation with voltage without recalibration | 1.8                   | 0.100 |      |

| dR/dV  |                                                  | 1.5                   | 0.100 | %/mV |

|        |                                                  | 1.35                  | 0.150 |      |

|        |                                                  | 1.25                  | 0.150 |      |

|        |                                                  | 1.2                   | 0.150 |      |

AV-51002 2017.02.10

#### I/O Standard Specifications

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Arria V devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

#### Single-Ended I/O Standards

| I/O Standard    |       | V <sub>CCIO</sub> (V) |       |      | V <sub>IL</sub> (V)    | V <sub>IH</sub> (V)    |                  | V <sub>OL</sub> (V)    | V <sub>OH</sub> (V)      | I <sub>OL</sub> <sup>(13)</sup> | I <sub>OH</sub> <sup>(13)</sup> (mA) |

|-----------------|-------|-----------------------|-------|------|------------------------|------------------------|------------------|------------------------|--------------------------|---------------------------------|--------------------------------------|

| I/O Stanuaru    | Min   | Тур                   | Max   | Min  | Мах                    | Min                    | Мах              | Мах                    | Min                      | (mA)                            | IOH, (IIIA)                          |

| 3.3-V<br>LVTTL  | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.45                   | 2.4                      | 4                               | -4                                   |

| 3.3-V<br>LVCMOS | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.2                    | V <sub>CCIO</sub> – 0.2  | 2                               | -2                                   |

| 3.0-V<br>LVTTL  | 2.85  | 3                     | 3.15  | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.4                    | 2.4                      | 2                               | -2                                   |

| 3.0-V<br>LVCMOS | 2.85  | 3                     | 3.15  | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.2                    | V <sub>CCIO</sub> – 0.2  | 0.1                             | -0.1                                 |

| 3.0-V PCI       | 2.85  | 3                     | 3.15  | _    | $0.3 \times V_{CCIO}$  | $0.5 \times V_{CCIO}$  | $V_{CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$    | 1.5                             | -0.5                                 |

| 3.0-V<br>PCI-X  | 2.85  | 3                     | 3.15  |      | $0.35 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$  | $V_{CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$    | 1.5                             | -0.5                                 |

| 2.5 V           | 2.375 | 2.5                   | 2.625 | -0.3 | 0.7                    | 1.7                    | 3.6              | 0.4                    | 2                        | 1                               | -1                                   |

| 1.8 V           | 1.71  | 1.8                   | 1.89  | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | 0.45                   | V <sub>CCIO</sub> – 0.45 | 2                               | -2                                   |

| 1.5 V           | 1.425 | 1.5                   | 1.575 | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$   | 2                               | -2                                   |

| 1.2 V           | 1.14  | 1.2                   | 1.26  | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$   | 2                               | -2                                   |

Table 1-14: Single-Ended I/O Standards for Arria V Devices

(13) To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification (4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

| Symbol/Description                                                                              | Condition                       | Т     | ransceiver Speed Gra     | Unit    |      |

|-------------------------------------------------------------------------------------------------|---------------------------------|-------|--------------------------|---------|------|

| Symbol/Description                                                                              | Condition                       | Min   | Тур                      | Мах     | Onit |

| Data rate (10-Gbps transceiver) <sup>(44)</sup>                                                 | _                               | 0.611 | —                        | 10.3125 | Gbps |

| Absolute $V_{MAX}$ for a receiver pin <sup>(45)</sup>                                           | _                               |       | _                        | 1.2     | V    |

| Absolute $\mathrm{V}_{\mathrm{MIN}}$ for a receiver pin                                         | _                               | -0.4  | _                        | _       | V    |

| Maximum peak-to-peak differential input voltage $V_{ID}$ (diff p-p) before device configuration | —                               | —     | _                        | 1.6     | V    |

| Maximum peak-to-peak differential input voltage $V_{ID}$ (diff p-p) after device configuration  | _                               |       |                          | 2.2     | V    |

| Minimum differential eye opening at the receiver serial input pins <sup>(46)</sup>              | _                               | 100   |                          |         | mV   |

| V <sub>ICM</sub> (AC coupled)                                                                   | _                               | _     | 750 <sup>(47)</sup> /800 |         | mV   |

| V <sub>ICM</sub> (DC coupled)                                                                   | $\leq 3.2 \mathrm{Gbps}^{(48)}$ | 670   | 700                      | 730     | mV   |

|                                                                                                 | 85- $\Omega$ setting            |       | 85                       |         | Ω    |

| Differential on-chip termination                                                                | 100-Ω setting                   |       | 100                      |         | Ω    |

| resistors                                                                                       | 120-Ω setting                   |       | 120                      |         | Ω    |

|                                                                                                 | 150-Ω setting                   |       | 150                      |         | Ω    |

| t <sub>LTR</sub> <sup>(49)</sup>                                                                | _                               | _     | _                        | 10      | μs   |

| t <sub>LTD</sub> <sup>(50)</sup>                                                                | _                               | 4     |                          |         | μs   |

<sup>&</sup>lt;sup>(45)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

<sup>&</sup>lt;sup>(46)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the **Receiver Equalization** feature. If you enable the **Receiver Equalization** feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

$<sup>^{(47)}</sup>$  The AC coupled  $V_{\rm ICM}$  is 750 mV for PCIe mode only.

<sup>&</sup>lt;sup>(48)</sup> For standard protocol compliance, use AC coupling.

$<sup>^{(49)}</sup>$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

<sup>&</sup>lt;sup>(50)</sup> t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

| Symbol/Description                          | Condition                                                     | Т                                                                                                                                                                                                                                                                     | Transceiver Speed Grade 3 |     |      |  |  |  |

|---------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|------|--|--|--|

| Symbol/Description                          | Min Typ                                                       |                                                                                                                                                                                                                                                                       | Тур                       | Мах | Unit |  |  |  |

| t <sub>LTD_manual</sub> <sup>(51)</sup>     | —                                                             | 4                                                                                                                                                                                                                                                                     | —                         | _   | μs   |  |  |  |

| t <sub>LTR_LTD_manual</sub> <sup>(52)</sup> | _                                                             | 15                                                                                                                                                                                                                                                                    | μs                        |     |      |  |  |  |

| Programmable ppm detector <sup>(53)</sup>   | _                                                             | ±62.5, 100                                                                                                                                                                                                                                                            | ppm                       |     |      |  |  |  |

| Run length                                  | —                                                             | _                                                                                                                                                                                                                                                                     | _                         | 200 | UI   |  |  |  |

| Programmable equalization AC and DC gain    | AC gain setting = 0 to $3^{(54)}$<br>DC gain setting = 0 to 1 | Refer to CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gai<br>and DC Gain for Arria V GX, GT, SX, and ST Devices and CTLE Response a<br>Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain for Arria V<br>GX, GT, SX, and ST Devices diagrams. |                           |     |      |  |  |  |

#### Table 1-29: Transmitter Specifications for Arria V GT and ST Devices

| Symbol/Description              | Condition                       | Tran       | Unit |         |      |  |  |  |  |  |

|---------------------------------|---------------------------------|------------|------|---------|------|--|--|--|--|--|

|                                 | Condition                       | Min        | Тур  | Max     |      |  |  |  |  |  |

| Supported I/O standards         |                                 | 1.5 V PCML |      |         |      |  |  |  |  |  |

| Data rate (6-Gbps transceiver)  | —                               | 611        |      | 6553.6  | Mbps |  |  |  |  |  |

| Data rate (10-Gbps transceiver) | _                               | 0.611      |      | 10.3125 | Gbps |  |  |  |  |  |

| V <sub>OCM</sub> (AC coupled)   | —                               |            | 650  |         | mV   |  |  |  |  |  |

| V <sub>OCM</sub> (DC coupled)   | $\leq$ 3.2 Gbps <sup>(48)</sup> | 670        | 700  | 730     | mV   |  |  |  |  |  |

<sup>(53)</sup> The rate match FIFO supports only up to  $\pm 300$  ppm.

<sup>(54)</sup> The Quartus Prime software allows AC gain setting = 3 for design with data rate between 611 Mbps and 1.25 Gbps only.

$<sup>^{(51)}</sup>$  t<sub>LTD\_manual</sub> is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

<sup>(52)</sup> t<sub>LTR\_LTD\_manual</sub> is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

| Symbol | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|--------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|        | 25                                      | 500                        | 53                                      | 1060                       |

|        | 26                                      | 520                        | 54                                      | 1080                       |

|        | 27                                      | 540                        | 55                                      | 1100                       |

|        | 28                                      | 560                        | 56                                      | 1120                       |

|        | 29                                      | 580                        | 57                                      | 1140                       |

|        | 30                                      | 600                        | 58                                      | 1160                       |

|        | 31                                      | 620                        | 59                                      | 1180                       |

|        | 32                                      | 640                        | 60                                      | 1200                       |

|        | 33                                      | 660                        |                                         |                            |

#### **Transmitter Pre-Emphasis Levels**

The following table lists the simulation data on the transmitter pre-emphasis levels in dB for the first post tap under the following conditions:

- Low-frequency data pattern—five 1s and five 0s

- Data rate—2.5 Gbps

The levels listed are a representation of possible pre-emphasis levels under the specified conditions only and the pre-emphasis levels may change with data pattern and data rate.

Arria V devices only support 1st post tap pre-emphasis with the following conditions:

- The 1st post tap pre-emphasis settings must satisfy  $|B| + |C| \le 60$  where  $|B| = V_{OD}$  setting with termination value,  $R_{TERM} = 100 \Omega$  and |C| = 1st post tap pre-emphasis setting.

- |B| |C| > 5 for data rates < 5 Gbps and |B| |C| > 8.25 for data rates > 5 Gbps.

- $(V_{MAX}/V_{MIN} 1)\% < 600\%$ , where  $V_{MAX} = |B| + |C|$  and  $V_{MIN} = |B| |C|$ .

Exception for PCIe Gen2 design:  $V_{OD}$  setting = 43 and pre-emphasis setting = 19 are allowed for PCIe Gen2 design with transmit de-emphasis – 6dB setting (pipe\_txdeemp = 1'b0) using Altera PCIe Hard IP and PIPE IP cores.

<sup>&</sup>lt;sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

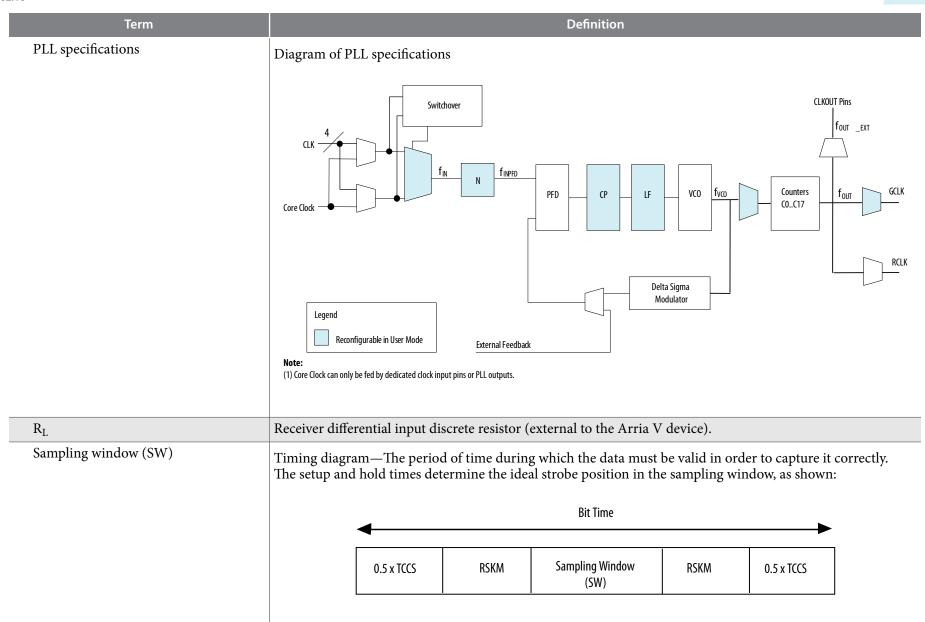

| 1-44 | PLL Specifications |

|------|--------------------|

|------|--------------------|

| Symbol                           | Parameter                                                           | Condition      | Min | Тур | Max                 | Unit |

|----------------------------------|---------------------------------------------------------------------|----------------|-----|-----|---------------------|------|

|                                  |                                                                     | -3 speed grade | 5   | _   | 800 <sup>(61)</sup> | MHz  |

| f <sub>IN</sub>                  | Input clock frequency                                               | -4 speed grade | 5   | _   | 800 <sup>(61)</sup> | MHz  |

| IIN                              | input clock frequency                                               | -5 speed grade | 5   | _   | 750 <sup>(61)</sup> | MHz  |

|                                  |                                                                     | -6 speed grade | 5   | _   | 625 <sup>(61)</sup> | MHz  |

| f <sub>INPFD</sub>               | Integer input clock frequency to the phase frequency detector (PFD) |                | 5   | _   | 325                 | MHz  |

| f <sub>FINPFD</sub>              | Fractional input clock frequency to the PFD                         | _              | 50  | _   | 160                 | MHz  |

|                                  |                                                                     | -3 speed grade | 600 | _   | 1600                | MHz  |

| f <sub>VCO</sub> <sup>(62)</sup> | PLL voltage-controlled oscillator                                   | -4 speed grade | 600 | _   | 1600                | MHz  |

| IVCO                             | (VCO) operating range                                               | -5 speed grade | 600 | _   | 1600                | MHz  |

|                                  |                                                                     | -6 speed grade | 600 | _   | 1300                | MHz  |

| t <sub>EINDUTY</sub>             | Input clock or external feedback clock input duty cycle             | _              | 40  | _   | 60                  | %    |

|                                  |                                                                     | -3 speed grade | _   | _   | 500 <sup>(63)</sup> | MHz  |

| f                                | Output frequency for internal global or                             | -4 speed grade | _   | _   | 500 <sup>(63)</sup> | MHz  |

| f <sub>OUT</sub>                 | regional clock                                                      | -5 speed grade | _   | -   | 500 <sup>(63)</sup> | MHz  |

|                                  |                                                                     | -6 speed grade | _   | _   | 400 <sup>(63)</sup> | MHz  |

<sup>&</sup>lt;sup>(61)</sup> This specification is limited in the Quartus Prime software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

<sup>&</sup>lt;sup>(62)</sup> The VCO frequency reported by the Quartus Prime software takes into consideration the VCO post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the  $f_{VCO}$  specification.

<sup>&</sup>lt;sup>(63)</sup> This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $F_{OUT}$  of the PLL.

AV-51002 2017.02.10

| Symbol                                                                                                                                       | Condition                                                           |      | -I3, -C4 |      |      | -l5, -C5 |      |      | -C6 |      | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|----------|------|------|----------|------|------|-----|------|------|

| Symbol                                                                                                                                       | Condition                                                           | Min  | Тур      | Max  | Min  | Тур      | Max  | Min  | Тур | Max  | Unit |

|                                                                                                                                              | SERDES factor J ≥<br>8 <sup>(76)(78)</sup> , LVDS TX with<br>RX DPA | (77) |          | 1600 | (77) |          | 1500 | (77) | _   | 1250 | Mbps |

|                                                                                                                                              | SERDES factor J = 1<br>to 2, Uses DDR<br>Registers                  | (77) |          | (79) | (77) |          | (79) | (77) | _   | (79) | Mbps |

| Emulated Differential I/<br>O Standards with Three<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup> | SERDES factor $J = 4$<br>to $10^{(81)}$                             | (77) |          | 945  | (77) |          | 945  | (77) |     | 945  | Mbps |

| Emulated Differential I/<br>O Standards with One<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup>   | SERDES factor $J = 4$<br>to $10^{(81)}$                             | (77) |          | 200  | (77) |          | 200  | (77) |     | 200  | Mbps |

| t <sub>x Jitter</sub> -True Differential<br>I/O Standards                                                                                    | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps               |      |          | 160  |      |          | 160  |      | _   | 160  | ps   |

|                                                                                                                                              | Total Jitter for Data<br>Rate < 600 Mbps                            |      |          | 0.1  | _    | _        | 0.1  | —    | _   | 0.1  | UI   |

$<sup>^{(78)}</sup>$  The V<sub>CC</sub> and V<sub>CCP</sub> must be on a separate power layer and a maximum load of 5 pF for chip-to-chip interface.

<sup>&</sup>lt;sup>(79)</sup> The maximum ideal data rate is the SERDES factor (J) x the PLL maximum output frequency (f<sub>OUT</sub>), provided you can close the design timing and the signal integrity simulation is clean.

<sup>&</sup>lt;sup>(80)</sup> You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine the leftover timing margin.

<sup>&</sup>lt;sup>(81)</sup> When using True LVDS RX channels for emulated LVDS TX channel, only serialization factors 1 and 2 are supported.

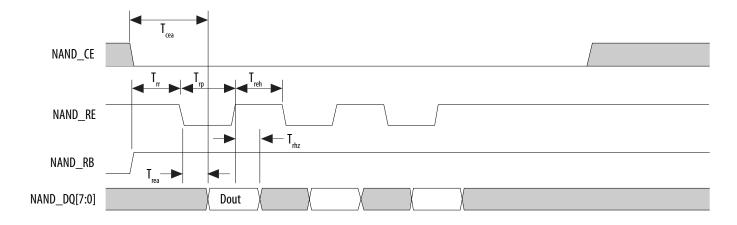

| Symbol                          | Description                        | Min | Мах | Unit |

|---------------------------------|------------------------------------|-----|-----|------|

| T <sub>dh</sub> <sup>(89)</sup> | Data to write enable hold time     | 5   | —   | ns   |

| T <sub>cea</sub>                | Chip enable to data access time    |     | 25  | ns   |

| T <sub>rea</sub>                | Read enable to data access time    |     | 16  | ns   |

| T <sub>rhz</sub>                | Read enable to data high impedance |     | 100 | ns   |

| T <sub>rr</sub>                 | Ready to read enable low           | 20  |     | ns   |

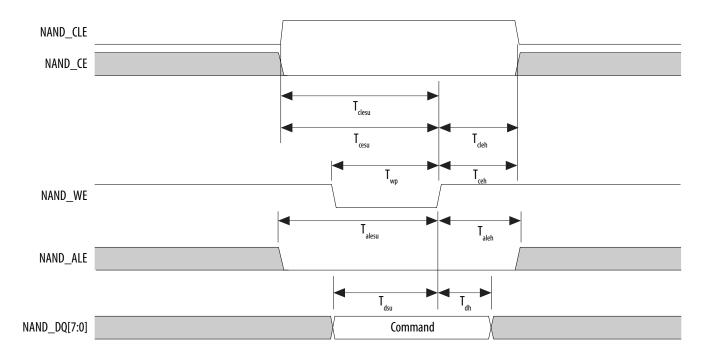

## Figure 1-17: NAND Command Latch Timing Diagram

#### Figure 1-20: NAND Data Read Timing Diagram

#### **ARM Trace Timing Characteristics**

#### Table 1-61: ARM Trace Timing Requirements for Arria V Devices

Most debugging tools have a mechanism to adjust the capture point of trace data.

| Description                     | Min  | Мах | Unit |

|---------------------------------|------|-----|------|

| CLK clock period                | 12.5 | —   | ns   |

| CLK maximum duty cycle          | 45   | 55  | %    |

| CLK to D0 –D7 output data delay | -1   | 1   | ns   |

#### **UART Interface**

The maximum UART baud rate is 6.25 megasymbols per second.

#### **GPIO Interface**

The minimum detectable general-purpose I/O (GPIO) pulse width is 2 µs. The pulse width is based on a debounce clock frequency of 1 MHz.

#### **HPS JTAG Timing Specifications**

| Symbol                  | Description                              | Min | Мах                | Unit |

|-------------------------|------------------------------------------|-----|--------------------|------|

| t <sub>JCP</sub>        | TCK clock period                         | 30  |                    | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14  |                    | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14  |                    | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2   |                    | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3   |                    | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5   |                    | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |     | 12 <sup>(90)</sup> | ns   |

| t <sub>JPZX</sub>       | JTAG port high impedance to valid output |     | 14 <sup>(90)</sup> | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | _   | 14 <sup>(90)</sup> | ns   |

#### Table 1-62: HPS JTAG Timing Parameters and Values for Arria V Devices

## **Configuration Specifications**

This section provides configuration specifications and timing for Arria V devices.

## **POR Specifications**

#### Table 1-63: Fast and Standard POR Delay Specification for Arria V Devices

| POR Delay | Minimum | Maximum            | Unit |

|-----------|---------|--------------------|------|

| Fast      | 4       | 12 <sup>(91)</sup> | ms   |

<sup>&</sup>lt;sup>(90)</sup> A 1-ns adder is required for each  $V_{CCIO\_HPS}$  voltage step down from 3.0 V. For example,  $t_{JPCO}$ = 13 ns if  $V_{CCIO\_HPS}$  of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

<sup>&</sup>lt;sup>(91)</sup> The maximum pulse width of the fast POR delay is 12 ms, providing enough time for the PCIe hard IP to initialize after the POR trip.

#### 1-76 FPGA JTAG Configuration Timing

| POR Delay | Minimum | Maximum | Unit |

|-----------|---------|---------|------|

| Standard  | 100     | 300     | ms   |

#### **Related Information**

#### **MSEL Pin Settings**

Provides more information about POR delay based on MSEL pin settings for each configuration scheme.

## **FPGA JTAG Configuration Timing**

#### Table 1-64: FPGA JTAG Timing Parameters and Values for Arria V Devices

| Symbol                  | Description                              | Min                            | Мах                | Unit |

|-------------------------|------------------------------------------|--------------------------------|--------------------|------|

| t <sub>JCP</sub>        | TCK clock period                         | <b>30, 167</b> <sup>(92)</sup> | _                  | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14                             |                    | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14                             |                    | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2                              |                    | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3                              |                    | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5                              |                    | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |                                | 12 <sup>(93)</sup> | ns   |

| t <sub>JPZX</sub>       | JTAG port high impedance to valid output |                                | 14 <sup>(93)</sup> | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | _                              | 14 <sup>(93)</sup> | ns   |

<sup>&</sup>lt;sup>(92)</sup> The minimum TCK clock period is 167 ns if  $V_{CCBAT}$  is within the range 1.2 V – 1.5 V when you perform the volatile key programming.

<sup>&</sup>lt;sup>(93)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

AV-51002 2017.02.10

The Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

#### Arria V I/O Timing Spreadsheet

Provides the Arria V Excel-based I/O timing spreadsheet.

## Programmable IOE Delay

| Parameter <sup>(112</sup> Available Minimum |          |                         | Fast Model |            | Slow Model |       |       |              | - Unit |      |

|---------------------------------------------|----------|-------------------------|------------|------------|------------|-------|-------|--------------|--------|------|

| )                                           | Settings | Offset <sup>(113)</sup> | Industrial | Commercial | -C4        | -C5   | -C6   | - <b>I</b> 3 | -15    | Onic |

| D1                                          | 32       | 0                       | 0.508      | 0.517      | 0.870      | 1.063 | 1.063 | 0.872        | 1.057  | ns   |

| D3                                          | 8        | 0                       | 1.763      | 1.795      | 2.999      | 3.496 | 3.571 | 3.031        | 3.643  | ns   |

| D4                                          | 32       | 0                       | 0.508      | 0.518      | 0.869      | 1.063 | 1.063 | 1.063        | 1.057  | ns   |

| D5                                          | 32       | 0                       | 0.508      | 0.517      | 0.870      | 1.063 | 1.063 | 0.872        | 1.057  | ns   |

#### Table 1-76: I/O element (IOE) Programmable Delay for Arria V Devices

## Programmable Output Buffer Delay

#### Table 1-77: Programmable Output Buffer Delay for Arria V Devices

This table lists the delay chain settings that control the rising and falling edge delays of the output buffer.

You can set the programmable output buffer delay in the Quartus Prime software by setting the **Output Buffer Delay Control** assignment to either positive, negative, or both edges, with the specific values stated here (in ps) for the **Output Buffer Delay** assignment.

<sup>&</sup>lt;sup>(112)</sup> You can set this value in the Quartus Prime software by selecting **D1**, **D3**, **D4**, and **D5** in the **Assignment Name** column of **Assignment Editor**.

<sup>&</sup>lt;sup>(113)</sup> Minimum offset does not include the intrinsic delay.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

#### 1-96 Document Revision History

| Date      | Version    | Changes                                                                                                                                                                                                                                                                                                                                 |

|-----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2015 | 2015.06.16 | • Added the supported data rates for the following output standards using true LVDS output buffer types in the High-Speed I/O Specifications for Arria V Devices table:                                                                                                                                                                 |

|           |            | True RSDS output standard: data rates of up to 360 Mbps                                                                                                                                                                                                                                                                                 |

|           |            | True mini-LVDS output standard: data rates of up to 400 Mbps                                                                                                                                                                                                                                                                            |

|           |            | <ul> <li>Added note in the condition for Transmitter—Emulated Differential I/O Standards f<sub>HSDR</sub> data rate parameter<br/>in the High-Speed I/O Specifications for Arria V Devices table. Note: When using True LVDS RX channels<br/>for emulated LVDS TX channel, only serialization factors 1 and 2 are supported.</li> </ul> |

|           |            | Changed Queued Serial Peripheral Interface (QSPI) to Quad Serial Peripheral Interface (SPI) Flash.                                                                                                                                                                                                                                      |

|           |            | Updated T <sub>h</sub> location in I <sup>2</sup> C Timing Diagram.                                                                                                                                                                                                                                                                     |

|           |            | Updared T <sub>wp</sub> location in NAND Address Latch Timing Diagram.                                                                                                                                                                                                                                                                  |

|           |            | <ul> <li>Corrected the unit for t<sub>DH</sub> from ns to s in FPP Timing Parameters When DCLK-to-DATA[] Ratio is &gt;1 for<br/>Arria V Devices table.</li> </ul>                                                                                                                                                                       |

|           |            | • Updated the maximum value for t <sub>CO</sub> from 4 ns to 2 ns in AS Timing Parameters for AS ×1 and ×4 Configurations in Arria V Devices table.                                                                                                                                                                                     |

|           |            | • Moved the following timing diagrams to the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.                                                                                                                                                                                                     |

|           |            | FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is 1                                                                                                                                                                                                                                                                        |

|           |            | <ul> <li>FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is &gt;1</li> </ul>                                                                                                                                                                                                                                                |

|           |            | AS Configuration Timing Waveform                                                                                                                                                                                                                                                                                                        |

|           |            | PS Configuration Timing Waveform                                                                                                                                                                                                                                                                                                        |

| Memory        | Mode                                                                                             | Resources Used |        | Performance |     |     |     | Unit |  |

|---------------|--------------------------------------------------------------------------------------------------|----------------|--------|-------------|-----|-----|-----|------|--|

| wentory       | imoue                                                                                            | ALUTs          | Memory | C3          | C4  | I3L | 14  | Unit |  |

|               | Single-port, all supported widths                                                                | 0              | 1      | 650         | 550 | 500 | 450 | MHz  |  |

|               | Simple dual-port, all supported widths                                                           | 0              | 1      | 650         | 550 | 500 | 450 | MHz  |  |

| option        | Simple dual-port with the read-during-write option set to <b>Old Data</b> , all supported widths | 0              | 1      | 455         | 400 | 455 | 400 | MHz  |  |

| M20K<br>Block | Simple dual-port with ECC enabled, $512 \times 32$                                               | 0              | 1      | 400         | 350 | 400 | 350 | MHz  |  |

| S<br>p        | Simple dual-port with ECC and optional pipeline registers enabled, 512 × 32                      | 0              | 1      | 500         | 450 | 500 | 450 | MHz  |  |

|               | True dual port, all supported widths                                                             | 0              | 1      | 650         | 550 | 500 | 450 | MHz  |  |

|               | ROM, all supported widths                                                                        | 0              | 1      | 650         | 550 | 500 | 450 | MHz  |  |

### **Temperature Sensing Diode Specifications**

#### Table 2-37: Internal Temperature Sensing Diode Specification

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate  | Conversion Time | Resolution | Minimum Resolution<br>with no Missing<br>Codes |

|-------------------|----------|-----------------------------|----------------|-----------------|------------|------------------------------------------------|

| -40°C to 100°C    | ±8°C     | No                          | 1 MHz, 500 kHz | < 100 ms        | 8 bits     | 8 bits                                         |

#### Table 2-38: External Temperature Sensing Diode Specifications for Arria V GZ Devices

| Description                              | Min | Тур | Max | Unit |

|------------------------------------------|-----|-----|-----|------|

| I <sub>bias</sub> , diode source current | 8   | —   | 200 | μΑ   |

| V <sub>bias,</sub> voltage across diode  | 0.3 | _   | 0.9 | V    |

| Series resistance                        |     |     | < 1 | Ω    |

#### **Related Information**

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices For more information about the reconfiguration input for the ALTREMOTE\_UPDATE IP core, refer to the "User Watchdog Timer" section.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices For more information about the reset\_timer input for the ALTREMOTE\_UPDATE IP core, refer to the "Remote System Upgrade State Machine" section.

## User Watchdog Internal Oscillator Frequency Specification

#### Table 2-65: User Watchdog Internal Oscillator Frequency Specifications

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O Timing and the Quartus II Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Quartus II Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete placeand-route.

#### **Related Information**

## **Arria V Devices Documentation page**

For the Excel-based I/O Timing spreadsheet

#### Arria V GZ Device Datasheet

Altera Corporation

<sup>&</sup>lt;sup>(226)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "Remote System Upgrade State Machine" section in the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

<sup>&</sup>lt;sup>(227)</sup> This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "User Watchdog Timer" section in the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

# Glossary

#### Table 2-68: Glossary

| Term                               | Definition                                                                                                                                                                                                                                                                 |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>C</sub>                     | High-speed receiver and transmitter input and output clock period.                                                                                                                                                                                                         |

| TCCS (channel-to-<br>channel-skew) | The timing difference between the fastest and slowest output edges, including t <sub>CO</sub> variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table). |

| t <sub>DUTY</sub>                  | High-speed I/O block—Duty cycle on the high-speed transmitter output clock.                                                                                                                                                                                                |

| t <sub>FALL</sub>                  | Signal high-to-low transition time (80-20%)                                                                                                                                                                                                                                |

| t <sub>INCCJ</sub>                 | Cycle-to-cycle jitter tolerance on the PLL clock input.                                                                                                                                                                                                                    |

| t <sub>OUTPJ_IO</sub>              | Period jitter on the general purpose I/O driven by a PLL.                                                                                                                                                                                                                  |

| t <sub>OUTPJ_DC</sub>              | Period jitter on the dedicated clock output driven by a PLL.                                                                                                                                                                                                               |

| t <sub>RISE</sub>                  | Signal low-to-high transition time (20-80%)                                                                                                                                                                                                                                |

| Timing Unit Interval<br>(TUI)      | The timing budget allowed for skew, propagation delays, and the data sampling window.<br>(TUI = $1/(\text{receiver input clock frequency multiplication factor}) = t_C/w)$                                                                                                 |

| V <sub>CM(DC)</sub>                | DC common mode input voltage.                                                                                                                                                                                                                                              |

| V <sub>ICM</sub>                   | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                                                                                                                      |

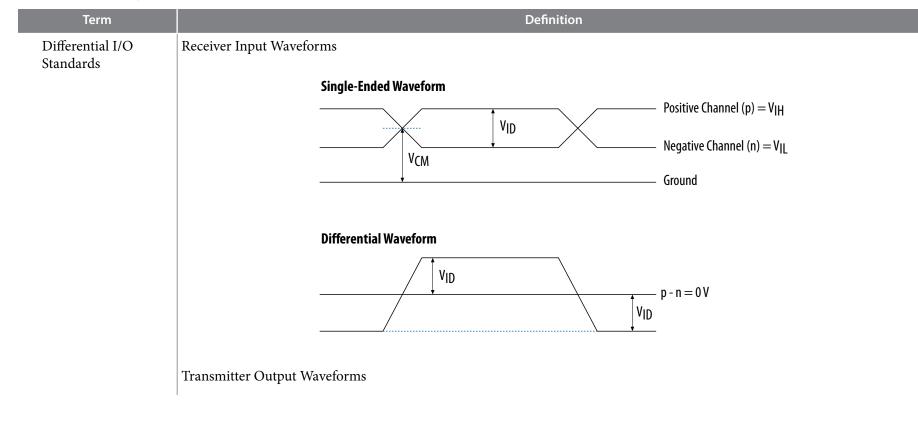

| V <sub>ID</sub>                    | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                                                                                               |

| V <sub>DIF(AC)</sub>               | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                                                                                                                                |

| V <sub>DIF(DC)</sub>               | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                                                                                                                               |

| V <sub>IH</sub>                    | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                                                                                                                      |

| V <sub>IH(AC)</sub>                | High-level AC input voltage                                                                                                                                                                                                                                                |

| V <sub>IH(DC)</sub>                | High-level DC input voltage                                                                                                                                                                                                                                                |

| V <sub>IL</sub>                    | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                                                                                                                        |

| V <sub>IL(AC)</sub>                | Low-level AC input voltage                                                                                                                                                                                                                                                 |

| V <sub>IL(DC)</sub>                | Low-level DC input voltage                                                                                                                                                                                                                                                 |

Altera Corporation