# E·XFL

#### Intel - 5AGXBA5D4F27I5N Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 8962                                                       |

| Number of Logic Elements/Cells | 190000                                                     |

| Total RAM Bits                 | 13284352                                                   |

| Number of I/O                  | 336                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 672-BBGA, FCBGA                                            |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxba5d4f27i5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications

| I/O Standard        | V <sub>II</sub> | <sub>-(DC)</sub> (V)     | V <sub>IH(D</sub>        | <sub>C)</sub> (V) | V <sub>IL(AC)</sub> (V)  | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)     | V <sub>OH</sub> (V)       | I <sub>OL</sub> <sup>(14)</sup> | I <sub>OH</sub> <sup>(14)</sup> (mA) |

|---------------------|-----------------|--------------------------|--------------------------|-------------------|--------------------------|--------------------------|-------------------------|---------------------------|---------------------------------|--------------------------------------|

| i/O Stanuaru        | Min             | Мах                      | Min                      | Мах               | Max                      | Min                      | Мах                     | Min                       | (mA)                            | IOH, (IIIIA)                         |

| SSTL-2<br>Class I   | -0.3            | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | $V_{CCIO} + 0.3$  | V <sub>REF</sub> – 0.31  | V <sub>REF</sub> + 0.31  | V <sub>TT</sub> – 0.608 | V <sub>TT</sub> + 0.608   | 8.1                             | -8.1                                 |

| SSTL-2<br>Class II  | -0.3            | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | $V_{CCIO} + 0.3$  | V <sub>REF</sub> – 0.31  | V <sub>REF</sub> + 0.31  | V <sub>TT</sub> – 0.81  | V <sub>TT</sub> + 0.81    | 16.2                            | -16.2                                |

| SSTL-18<br>Class I  | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | $V_{CCIO} + 0.3$  | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | V <sub>TT</sub> – 0.603 | V <sub>TT</sub> + 0.603   | 6.7                             | -6.7                                 |

| SSTL-18<br>Class II | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | $V_{CCIO} + 0.3$  | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | 0.28                    | V <sub>CCIO</sub> – 0.28  | 13.4                            | -13.4                                |

| SSTL-15<br>Class I  | —               | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                 | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$     | 8                               | -8                                   |

| SSTL-15<br>Class II | —               | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   |                   | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$     | 16                              | -16                                  |

| SSTL-135            | —               | $V_{REF}$ – 0.09         | $V_{REF} + 0.09$         |                   | V <sub>REF</sub> – 0.16  | $V_{REF} + 0.16$         | $0.2 \times V_{CCIO}$   | $0.8 \times V_{\rm CCIO}$ |                                 | —                                    |

| SSTL-125            | —               | $V_{REF} - 0.85$         | $V_{REF} + 0.85$         |                   | V <sub>REF</sub> – 0.15  | $V_{REF} + 0.15$         | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$     | —                               | —                                    |

| HSTL-18<br>Class I  |                 | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                 | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                     | V <sub>CCIO</sub> – 0.4   | 8                               | -8                                   |

| HSTL-18<br>Class II |                 | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   |                   | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                     | V <sub>CCIO</sub> – 0.4   | 16                              | -16                                  |

| HSTL-15<br>Class I  |                 | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   |                   | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                     | V <sub>CCIO</sub> – 0.4   | 8                               | -8                                   |

<sup>&</sup>lt;sup>(14)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

| Symbol | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|--------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|        | 25                                      | 500                        | 53                                      | 1060                       |

|        | 26                                      | 520                        | 54                                      | 1080                       |

|        | 27                                      | 540                        | 55                                      | 1100                       |

|        | 28                                      | 560                        | 56                                      | 1120                       |

|        | 29                                      | 580                        | 57                                      | 1140                       |

|        | 30                                      | 600                        | 58                                      | 1160                       |

|        | 31                                      | 620                        | 59                                      | 1180                       |

|        | 32                                      | 640                        | 60                                      | 1200                       |

|        | 33                                      | 660                        |                                         |                            |

#### **Transmitter Pre-Emphasis Levels**

The following table lists the simulation data on the transmitter pre-emphasis levels in dB for the first post tap under the following conditions:

- Low-frequency data pattern—five 1s and five 0s

- Data rate—2.5 Gbps

The levels listed are a representation of possible pre-emphasis levels under the specified conditions only and the pre-emphasis levels may change with data pattern and data rate.

Arria V devices only support 1st post tap pre-emphasis with the following conditions:

- The 1st post tap pre-emphasis settings must satisfy  $|B| + |C| \le 60$  where  $|B| = V_{OD}$  setting with termination value,  $R_{TERM} = 100 \Omega$  and |C| = 1st post tap pre-emphasis setting.

- |B| |C| > 5 for data rates < 5 Gbps and |B| |C| > 8.25 for data rates > 5 Gbps.

- $(V_{MAX}/V_{MIN} 1)\% < 600\%$ , where  $V_{MAX} = |B| + |C|$  and  $V_{MIN} = |B| |C|$ .

Exception for PCIe Gen2 design:  $V_{OD}$  setting = 43 and pre-emphasis setting = 19 are allowed for PCIe Gen2 design with transmit de-emphasis – 6dB setting (pipe\_txdeemp = 1'b0) using Altera PCIe Hard IP and PIPE IP cores.

<sup>&</sup>lt;sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

#### Table 1-34: Transceiver Compliance Specification for All Supported Protocol for Arria V GX, GT, SX, and ST Devices

| Protocol                           | Sub-protocol | Data Rate (Mbps) |  |  |

|------------------------------------|--------------|------------------|--|--|

|                                    | PCIe Gen1    | 2,500            |  |  |

| PCIe                               | PCIe Gen2    | 5,000            |  |  |

|                                    | PCIe Cable   | 2,500            |  |  |

| XAUI                               | XAUI 2135    | 3,125            |  |  |

|                                    | SRIO 1250 SR | 1,250            |  |  |

|                                    | SRIO 1250 LR | 1,250            |  |  |

|                                    | SRIO 2500 SR | 2,500<br>2,500   |  |  |

|                                    | SRIO 2500 LR |                  |  |  |

|                                    | SRIO 3125 SR | 3,125            |  |  |

| Serial RapidIO <sup>®</sup> (SRIO) | SRIO 3125 LR | 3,125            |  |  |

| Serial Rapidio (SRIO)              | SRIO 5000 SR | 5,000            |  |  |

|                                    | SRIO 5000 MR | 5,000            |  |  |

|                                    | SRIO 5000 LR | 5,000            |  |  |

|                                    | SRIO_6250_SR | 6,250            |  |  |

|                                    | SRIO_6250_MR | 6,250            |  |  |

|                                    | SRIO_6250_LR | 6,250            |  |  |

| Protocol                             | Sub-protocol                  | Data Rate (Mbps) |

|--------------------------------------|-------------------------------|------------------|

|                                      | CPRI E6LV                     | 614.4            |

|                                      | CPRI E6HV                     | 614.4            |

|                                      | CPRI E6LVII                   | 614.4            |

|                                      | CPRI E12LV                    | 1,228.8          |

|                                      | CPRI E12HV                    | 1,228.8          |

|                                      | CPRI E12LVII                  | 1,228.8          |

| Common Public Radio Interface (CPRI) | CPRI E24LV                    | 2,457.6          |

|                                      | CPRI E24LVII                  | 2,457.6          |

|                                      | CPRI E30LV                    | 3,072            |

|                                      | CPRI E30LVII                  | 3,072            |

|                                      | CPRI E48LVII                  | 4,915.2          |

|                                      | CPRI E60LVII                  | 6,144            |

|                                      | CPRI E96LVIII <sup>(60)</sup> | 9,830.4          |

| Gbps Ethernet (GbE)                  | GbE 1250                      | 1,250            |

|                                      | OBSAI 768                     | 768              |

| OBSAI                                | OBSAI 1536                    | 1,536            |

| OBSAI                                | OBSAI 3072                    | 3,072            |

|                                      | OBSAI 6144                    | 6,144            |

|                                      | SDI 270 SD                    | 270              |

| Serial digital interface (SDI)       | SDI 1485 HD                   | 1,485            |

|                                      | SDI 2970 3G                   | 2,970            |

<sup>&</sup>lt;sup>(60)</sup> You can achieve compliance with TX channel restriction of one HSSI channel per six-channel transceiver bank.

| Symbol                                                                                                           | Condition                                                                                    | -I3, -C4 |     | –I5, –C5 |     | -C6 |      |     | Unit |      |      |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------|-----|----------|-----|-----|------|-----|------|------|------|

| Symbol                                                                                                           | Condition                                                                                    | Min      | Тур | Max      | Min | Тур | Мах  | Min | Тур  | Max  | Unit |

| t <sub>x Jitter</sub> -Emulated<br>Differential I/O<br>Standards with Three                                      | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps                                        | _        | -   | 260      |     | _   | 300  | _   | _    | 350  | ps   |

| External Output Resistor<br>Network                                                                              | Total Jitter for Data<br>Rate < 600 Mbps                                                     | —        | _   | 0.16     |     | _   | 0.18 | _   |      | 0.21 | UI   |

| t <sub>x Jitter</sub> -Emulated<br>Differential I/O<br>Standards with One<br>External Output<br>Resistor Network | _                                                                                            |          |     | 0.15     |     |     | 0.15 |     |      | 0.15 | UI   |

| t <sub>DUTY</sub>                                                                                                | TX output clock duty<br>cycle for both True<br>and Emulated<br>Differential I/O<br>Standards | 45       | 50  | 55       | 45  | 50  | 55   | 45  | 50   | 55   | %    |

|                                                                                                                  | True Differential I/O<br>Standards <sup>(82)</sup>                                           | _        | _   | 160      |     |     | 180  | _   |      | 200  | ps   |

| t <sub>RISE</sub> and t <sub>FALL</sub>                                                                          | Emulated Differential<br>I/O Standards with<br>Three External Output<br>Resistor Network     | _        |     | 250      |     |     | 250  |     |      | 300  | ps   |

|                                                                                                                  | Emulated Differential<br>I/O Standards with<br>One External Output<br>Resistor Network       |          |     | 500      |     | _   | 500  |     |      | 500  | ps   |

$<sup>^{(82)}\,</sup>$  This applies to default pre-emphasis and  $V_{OD}$  settings only.

| Symbol               | Description          | Min                                                  | Тур | Max | Unit |

|----------------------|----------------------|------------------------------------------------------|-----|-----|------|

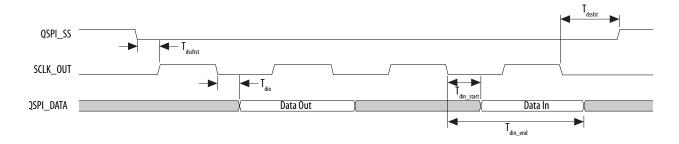

| T <sub>din_end</sub> | Input data valid end | $(2 + R_{delay}) \times T_{qspi\_clk} - 1.21^{(85)}$ |     | _   | ns   |

#### Figure 1-8: Quad SPI Flash Timing Diagram

This timing diagram illustrates clock polarity mode 0 and clock phase mode 0.

#### **Related Information**

## Quad SPI Flash Controller Chapter, Arria V Hard Processor System Technical Reference Manual

Provides more information about Rdelay.

#### **SPI Timing Characteristics**

#### Table 1-52: SPI Master Timing Requirements for Arria V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol           | Description                               | Min       | Max | Unit |

|------------------|-------------------------------------------|-----------|-----|------|

| T <sub>clk</sub> | CLK clock period                          | 16.67     | _   | ns   |

| T <sub>su</sub>  | SPI Master-in slave-out (MISO) setup time | 8.35 (86) |     | ns   |

$<sup>^{(85)}</sup>$  R<sub>delay</sub> is set by programming the register <code>qspiregs.rddatacap</code>. For the SoC EDS software version 13.1 and later, Altera provides automatic Quad SPI calibration in the preloader. For more information about R<sub>delay</sub>, refer to the Quad SPI Flash Controller chapter in the Arria V Hard Processor System Technical Reference Manual.

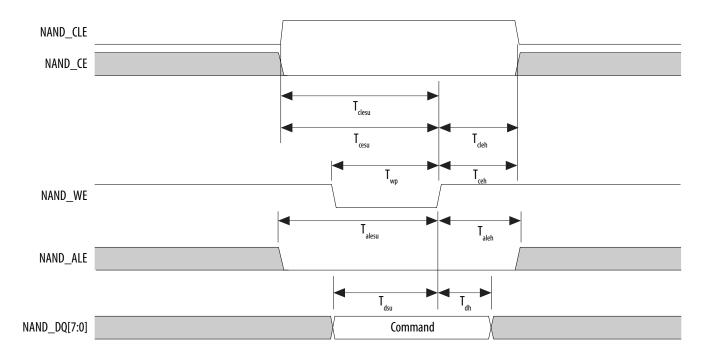

| Symbol                          | Description                        | Min | Мах | Unit |

|---------------------------------|------------------------------------|-----|-----|------|

| T <sub>dh</sub> <sup>(89)</sup> | Data to write enable hold time     | 5   | —   | ns   |

| T <sub>cea</sub>                | Chip enable to data access time    |     | 25  | ns   |

| T <sub>rea</sub>                | Read enable to data access time    |     | 16  | ns   |

| T <sub>rhz</sub>                | Read enable to data high impedance |     | 100 | ns   |

| T <sub>rr</sub>                 | Ready to read enable low           | 20  |     | ns   |

## Figure 1-17: NAND Command Latch Timing Diagram

## **FPP Configuration Timing**

#### DCLK-to-DATA[] Ratio (r) for FPP Configuration

Fast passive parallel (FPP) configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the DATA[] rate in byte per second (Bps) or word per second (Wps). For example, in FPP  $\times 16$  where the *r* is 2, the DCLK frequency must be 2 times the DATA[] rate in Wps.

#### Table 1-65: DCLK-to-DATA[] Ratio for Arria V Devices

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

|                      | Off        | Off         | 1                        |

| FPP (8-bit wide)     | On         | Off         | 1                        |

| rrr (o-on wide)      | Off        | On          | 2                        |

|                      | On         | On          | 2                        |

|                      | Off        | Off         | 1                        |

| FPP (16-bit wide)    | On         | Off         | 2                        |

| FFF (10-bit wide)    | Off        | On          | 4                        |

|                      | On         | On          | 4                        |

#### FPP Configuration Timing when DCLK-to-DATA[] = 1

When you enable decompression or the design security feature, the DCLK-to-DATA[] ratio varies for FPP ×8 and FPP ×16. For the respective DCLKto-DATA[] ratio, refer to the DCLK-to-DATA[] Ratio for Arria V Devices table.

#### Table 1-66: FPP Timing Parameters When DCLK-to-DATA[] Ratio is 1 for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum | Unit |

|---------------------|------------------------------|---------|---------|------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | _       | 600     | ns   |

| t <sub>CF2ST0</sub> | nCONFIG low to nSTATUS low   |         | 600     | ns   |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       | _       | μs   |

#### Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

### FPP Configuration Timing when DCLK-to-DATA[] >1

#### Table 1-67: FPP Timing Parameters When DCLK-to-DATA[] Ratio is >1 for Arria V Devices

Use these timing parameters when you use the decompression and design security features.

| Symbol                              | Parameter                                    | Minimum                      | Maximum              | Unit |

|-------------------------------------|----------------------------------------------|------------------------------|----------------------|------|

| t <sub>CF2CD</sub>                  | nconfig low to conf_done low                 | —                            | 600                  | ns   |

| t <sub>CF2ST0</sub>                 | nconfig low to nstatus low                   | —                            | 600                  | ns   |

| t <sub>CFG</sub>                    | nCONFIG low pulse width                      | 2                            | _                    | μs   |

| t <sub>STATUS</sub>                 | nSTATUS low pulse width                      | 268                          | 1506 <sup>(98)</sup> | μs   |

| t <sub>CF2ST1</sub>                 | nCONFIG high to nSTATUS high                 |                              | 1506 <sup>(99)</sup> | μs   |

| t <sub>CF2CK</sub> <sup>(100)</sup> | nCONFIG high to first rising edge on DCLK    | 1506                         | _                    | μs   |

| t <sub>ST2CK</sub> <sup>(100)</sup> | nSTATUS high to first rising edge of DCLK    | 2                            | _                    | μs   |

| t <sub>DSU</sub>                    | DATA[] setup time before rising edge on DCLK | 5.5                          | _                    | ns   |

| t <sub>DH</sub>                     | DATA[] hold time after rising edge on DCLK   | $N - 1/f_{\rm DCLK}^{(101)}$ | _                    | s    |

| t <sub>CH</sub>                     | DCLK high time                               | $0.45 \times 1/f_{MAX}$      | _                    | S    |

| t <sub>CL</sub>                     | DCLK low time                                | $0.45 \times 1/f_{MAX}$      | _                    | S    |

| t <sub>CLK</sub>                    | DCLK period                                  | 1/f <sub>MAX</sub>           | _                    | S    |

| f <sub>MAX</sub>                    | DCLK frequency (FPP ×8/ ×16)                 | _                            | 125                  | MHz  |

| t <sub>R</sub>                      | Input rise time                              | —                            | 40                   | ns   |

| t <sub>F</sub>                      | Input fall time                              | _                            | 40                   | ns   |

| t <sub>CD2UM</sub>                  | CONF_DONE high to user mode <sup>(102)</sup> | 175                          | 437                  | μs   |

<sup>(98)</sup> This value can be obtained if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>&</sup>lt;sup>(99)</sup> This value can be obtained if you do not delay configuration by externally holding nSTATUS low.

$<sup>^{(100)}</sup>$  If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

<sup>&</sup>lt;sup>(101)</sup> N is the DCLK-to-DATA[] ratio and  $f_{DCLK}$  is the DCLK frequency of the system.

<sup>&</sup>lt;sup>(102)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

#### **Related Information**

- PS Configuration Timing on page 1-81

- AS Configuration Timing

Provides the AS configuration timing waveform.

## **DCLK Frequency Specification in the AS Configuration Scheme**

#### Table 1-69: DCLK Frequency Specification in the AS Configuration Scheme

This table lists the internal clock frequency specification for the AS configuration scheme. The DCLK frequency specification applies when you use the internal oscillator as the configuration clock source. The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

| Parameter                                  | Minimum | Typical | Maximum | Unit |

|--------------------------------------------|---------|---------|---------|------|

|                                            | 5.3     | 7.9     | 12.5    | MHz  |

| DCLK frequency in AS configuration scheme  | 10.6    | 15.7    | 25.0    | MHz  |

| Bellk frequency in AS configuration scheme | 21.3    | 31.4    | 50.0    | MHz  |

|                                            | 42.6    | 62.9    | 100.0   | MHz  |

## **PS Configuration Timing**

#### Table 1-70: PS Timing Parameters for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum               | Unit |

|---------------------|------------------------------|---------|-----------------------|------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | _       | 600                   | ns   |

| t <sub>CF2ST0</sub> | nCONFIG low to nSTATUS low   |         | 600                   | ns   |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       | _                     | μs   |

| t <sub>STATUS</sub> | nSTATUS low pulse width      | 268     | 1506 <sup>(103)</sup> | μs   |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high | _       | 1506(104)             | μs   |

$<sup>^{(103)}\,</sup>$  You can obtain this value if you do not delay configuration by extending the <code>nCONFIG</code> or <code>nSTATUS</code> low pulse width.

<sup>&</sup>lt;sup>(104)</sup> You can obtain this value if you do not delay configuration by externally holding nSTATUS low.

| Symbol                            | Description                                                              | Condition | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-----------------------------------|--------------------------------------------------------------------------|-----------|--------------------------|---------|--------------------------|------|

| V <sub>CCPT</sub>                 | Power supply for programmable power technology                           | _         | 1.45                     | 1.50    | 1.55                     | V    |

| V <sub>CC_AUX</sub>               | Auxiliary supply for the programmable power technology                   | _         | 2.375                    | 2.5     | 2.625                    | V    |

| V <sub>CCPD</sub> <sup>(116</sup> | I/O pre-driver (3.0 V) power supply                                      |           | 2.85                     | 3.0     | 3.15                     | V    |

| )                                 | I/O pre-driver (2.5 V) power supply                                      |           | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | I/O buffers (3.0 V) power supply                                         | _         | 2.85                     | 3.0     | 3.15                     | V    |

|                                   | I/O buffers (2.5 V) power supply                                         |           | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | I/O buffers (1.8 V) power supply                                         |           | 1.71                     | 1.8     | 1.89                     | V    |

| V <sub>CCIO</sub>                 | I/O buffers (1.5 V) power supply                                         | _         | 1.425                    | 1.5     | 1.575                    | V    |

|                                   | I/O buffers (1.35 V) power supply                                        | _         | 1.283                    | 1.35    | 1.45                     | V    |

|                                   | I/O buffers (1.25 V) power supply                                        | _         | 1.19                     | 1.25    | 1.31                     | V    |

|                                   | I/O buffers (1.2 V) power supply                                         | _         | 1.14                     | 1.2     | 1.26                     | V    |

|                                   | Configuration pins (3.0 V) power supply                                  | _         | 2.85                     | 3.0     | 3.15                     | V    |

| V <sub>CCPGM</sub>                | Configuration pins (2.5 V) power supply                                  | _         | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | Configuration pins (1.8 V) power supply                                  | _         | 1.71                     | 1.8     | 1.89                     | V    |

| V <sub>CCA</sub> _                | PLL analog voltage regulator power supply                                | _         | 2.375                    | 2.5     | 2.625                    | V    |

| V <sub>CCD</sub><br>FPLL          | PLL digital voltage regulator power supply                               | _         | 1.45                     | 1.5     | 1.55                     | V    |

| V <sub>CCBAT</sub> (117           | Battery back-up power supply (For design security volatile key register) | _         | 1.2                      | —       | 3.0                      | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements.

Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(116)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25 or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.

<sup>(117)</sup> If you do not use the design security feature in Arria V GZ devices, connect V<sub>CCBAT</sub> to a 1.2- to 3.0-V power supply. Arria V GZ power-on-reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V GZ devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

| Symbol                                                                                    | Description                                                                                                                            | Conditions                                    | Calibration Ac | curacy        | Unit |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------|---------------|------|

| Symbol                                                                                    | Description                                                                                                                            | Conditions                                    | C3, I3L        | C4, I4        | Onic |

| 25-Ω R <sub>S</sub>                                                                       | Internal series termination with calibration (25- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

| 50-Ω R <sub>S</sub>                                                                       | Internal series termination with calibration (50- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

| 34- $\Omega$ and 40- $\Omega$ R <sub>S</sub>                                              | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                   | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2 V    | ±15            | ±15           | %    |

| 48-Ω, 60-Ω, 80-Ω, and<br>240-Ω R <sub>S</sub>                                             | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting)                  | $V_{CCIO} = 1.2 V$                            | ±15            | ±15           | %    |

| 50-Ω R <sub>T</sub>                                                                       | Internal parallel termination with calibration (50- $\Omega$ setting)                                                                  | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2 V      | -10 to +40     | -10 to<br>+40 | %    |

| 20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ $R_{\rm T}$ | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25 V         | -10 to +40     | -10 to<br>+40 | %    |

| 60- $\Omega$ and 120- $\Omega$ $R_{\rm T}$                                                | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                | $V_{CCIO} = 1.2$                              | -10 to +40     | -10 to<br>+40 | %    |

| 25- $\Omega R_{S\_left\_shift}$                                                           | Internal left shift series termination with calibration (25- $\Omega$ R <sub>S_left_shift</sub> setting)                               | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

#### Table 2-11: OCT Without Calibration Resistance Tolerance Specifications for Arria V GZ Devices

| Symbol | Description                                                            | Conditions                        | Resistance | Unit   |      |  |

|--------|------------------------------------------------------------------------|-----------------------------------|------------|--------|------|--|

| Symbol | Symbol Description                                                     |                                   | C3, I3L    | C4, I4 | Onic |  |

| - 8    | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0 and 2.5 V | ±40        | ±40    | %    |  |

#### Table 2-19: Differential SSTL I/O Standards for Arria V GZ Devices

| I/O Standard            |       | V <sub>CCIO</sub> (V) |       | V <sub>SWIN</sub> | <sub>G(DC)</sub> (V)       |                                 | $V_{X(AC)}(V)$       |                                 |                                               | V <sub>SWING(AC)</sub> (V) |

|-------------------------|-------|-----------------------|-------|-------------------|----------------------------|---------------------------------|----------------------|---------------------------------|-----------------------------------------------|----------------------------|

|                         | Min   | Тур                   | Max   | Min               | Max                        | Min                             | Тур                  | Max                             | Min                                           | Мах                        |

| SSTL-2 Class I,<br>II   | 2.375 | 2.5                   | 2.625 | 0.3               | V <sub>CCIO</sub><br>+ 0.6 | V <sub>CCIO</sub> /2<br>- 0.2   | _                    | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$           |

| SSTL-18 Class I,<br>II  | 1.71  | 1.8                   | 1.89  | 0.25              | V <sub>CCIO</sub><br>+ 0.6 | V <sub>CCIO</sub> /2<br>- 0.175 |                      | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | V <sub>CCIO</sub> + 0.6    |

| SSTL-15 Class I,<br>II  | 1.425 | 1.5                   | 1.575 | 0.2               | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  |                      | V <sub>CCIO</sub> /2<br>+ 0.15  | 0.35                                          | _                          |

| SSTL-135<br>Class I, II | 1.283 | 1.35                  | 1.45  | 0.2               | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub><br>- V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$  |

| SSTL-125<br>Class I, II | 1.19  | 1.25                  | 1.31  | 0.18              | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub><br>- V <sub>REF</sub> ) | _                          |

| SSTL-12<br>Class I, II  | 1.14  | 1.2                   | 1.26  | 0.18              | —                          | V <sub>REF</sub><br>-0.15       | V <sub>CCIO</sub> /2 | V <sub>REF</sub><br>+ 0.15      | -0.30                                         | 0.30                       |

#### Table 2-20: Differential HSTL and HSUL I/O Standards for Arria V GZ Devices

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>DIF(DC)</sub> (V) |     |     | V <sub>X(AC)</sub> (V) |     | V <sub>CM(DC)</sub> (V) |      |     | V <sub>DIF(AC)</sub> (V) |     |     |

|------------------------|-----------------------|-----|--------------------------|-----|-----|------------------------|-----|-------------------------|------|-----|--------------------------|-----|-----|

|                        | Min                   | Тур | Max                      | Min | Max | Min                    | Тур | Max                     | Min  | Тур | Max                      | Min | Max |

| HSTL-18 Class<br>I, II | 1.71                  | 1.8 | 1.89                     | 0.2 | _   | 0.78                   |     | 1.12                    | 0.78 | _   | 1.12                     | 0.4 | _   |

| HSTL-15 Class<br>I, II | 1.425                 | 1.5 | 1.575                    | 0.2 | _   | 0.68                   |     | 0.9                     | 0.68 | _   | 0.9                      | 0.4 | —   |

$<sup>^{(127)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

## **Switching Characteristics**

## **Transceiver Performance Specifications**

#### **Reference Clock**

#### Table 2-22: Reference Clock Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                               | Conditions                    | Transceiver Speed Grade 2                            |     |     | Transceiver Speed Grade 3 |     |     | Unit |  |  |

|------------------------------------------------------------------|-------------------------------|------------------------------------------------------|-----|-----|---------------------------|-----|-----|------|--|--|

| Symbol/Description                                               | Conditions                    | Min                                                  | Тур | Max | Min                       | Тур | Max | Onit |  |  |

| Reference Clock                                                  |                               |                                                      |     |     |                           |     |     |      |  |  |

| Supported I/O Standards                                          | Dedicated reference clock pin |                                                      |     |     |                           |     |     |      |  |  |

|                                                                  | RX reference clock pin        | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |     |     |                           |     |     |      |  |  |

| Input Reference Clock<br>Frequency<br>(CMU PLL) <sup>(137)</sup> | _                             | 40                                                   | _   | 710 | 40                        | _   | 710 | MHz  |  |  |

| Input Reference Clock<br>Frequency<br>(ATX PLL) <sup>(137)</sup> | _                             | 100                                                  | _   | 710 | 100                       | _   | 710 | MHz  |  |  |

<sup>(137)</sup> The input reference clock frequency options depend on the data rate and the device speed grade.

#### Table 2-26: CMU PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the Arria V Device Overview.

| Symbol/Description                          | Conditions | Trans | ceiver Spee | d Grade 2 | Transc | Unit |         |      |

|---------------------------------------------|------------|-------|-------------|-----------|--------|------|---------|------|

| Symbol/Description                          | Conditions | Min   | Тур         | Max       | Min    | Тур  | Мах     |      |

| Supported data range                        | _          | 600   | _           | 12500     | 600    | _    | 10312.5 | Mbps |

| t <sub>pll_powerdown</sub> <sup>(153)</sup> | _          | 1     | _           |           | 1      | _    |         | μs   |

| t <sub>pll_lock</sub> <sup>(154)</sup>      | _          |       | —           | 10        | _      |      | 10      | μs   |

#### **Related Information**

#### Arria V Device Overview

For more information about device ordering codes.

#### ATX PLL

#### Table 2-27: ATX PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the Arria V Device Overview.

Arria V GZ Device Datasheet

**Altera Corporation**

$t_{pll\_powerdown}$  is the PLL powerdown minimum pulse width. (153)

<sup>(154)</sup>  $t_{\text{pll} \text{ lock}}$  is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

| Symbol/Description                          | Conditions                | Trans | ceiver Spee | d Grade 2 | Transc | Unit |         |      |

|---------------------------------------------|---------------------------|-------|-------------|-----------|--------|------|---------|------|

| Symbol/Description                          |                           | Min   | Тур         | Max       | Min    | Тур  | Мах     |      |

|                                             | VCO post-divider<br>L = 2 | 8000  |             | 12500     | 8000   | _    | 10312.5 | Mbps |

| Supported data rate range                   | L = 4                     | 4000  |             | 6600      | 4000   |      | 6600    | Mbps |

|                                             | $L = 8^{(155)}$           | 2000  |             | 3300      | 2000   | _    | 3300    | Mbps |

| t <sub>pll_powerdown</sub> <sup>(156)</sup> | _                         | 1     |             |           | 1      |      |         | μs   |

| t <sub>pll_lock</sub> <sup>(157)</sup>      | _                         |       |             | 10        |        |      | 10      | μs   |

#### **Related Information**

- Arria V Device Overview For more information about device ordering codes.

- Transceiver Clocking in Arria V Devices For more information about clocking ATX PLLs.

- **Dynamic Reconfiguration in Arria V Devices** For more information about reconfiguring ATX PLLs.

#### **Fractional PLL**

#### Table 2-28: Fractional PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

<sup>(155)</sup> This clock can be further divided by central or local clock dividers making it possible to use ATX PLL for data rates < 1 Gbps. For more information about ATX PLLs, refer to the Transceiver Clocking in Arria V Devices chapter and the Dynamic Reconfiguration in Arria V Devices chapter.

$t_{pll_powerdown}$  is the PLL powerdown minimum pulse width.

<sup>(157)</sup>  $t_{pll \ lock}$  is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

AV-51002 2017.02.10

| Symbol                                                 | Parameter                                                                                              | Min  | Тур | Мах                                            | Unit      |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|-----|------------------------------------------------|-----------|

| t <sub>INCCJ</sub> <sup>(171)</sup> , <sup>(172)</sup> | Input clock cycle-to-cycle jitter (f_{REF} $\geq 100~MHz)$                                             | —    | _   | 0.15                                           | UI (p-p)  |

| 'INCCJ , , , , , ,                                     | Input clock cycle-to-cycle jitter ( $f_{REF} < 100 \text{ MHz}$ )                                      | -750 |     | +750                                           | ps (p-p)  |

| (173)                                                  | Period Jitter for dedicated clock output in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )              | _    | _   | 175                                            | ps (p-p)  |

| t <sub>OUTPJ_DC</sub> <sup>(173)</sup>                 | Period Jitter for dedicated clock output in integer<br>PLL (f <sub>OUT</sub> < 100 Mhz)                | _    |     | 17.5                                           | mUI (p-p) |

| t <sub>foutpj_dc</sub> <sup>(173)</sup>                | Period Jitter for dedicated clock output in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )           | _    |     | $250^{(176)}, \\ 175^{(174)}$                  | ps (p-p)  |

| 4FOUTPJ_DC                                             | Period Jitter for dedicated clock output in fractional<br>PLL (f <sub>OUT</sub> < 100 MHz)             | —    |     | $25^{(176)}$ ,<br>17.5 <sup>(174)</sup>        | mUI (p-p) |

| tournoon = c (173)                                     | Cycle-to-cycle Jitter for a dedicated clock output in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )    | —    |     | 175                                            | ps (p-p)  |

| t <sub>OUTCCJ_DC</sub> <sup>(173)</sup>                | Cycle-to-cycle Jitter for a dedicated clock output in integer PLL ( $f_{OUT} < 100 \text{ MHz}$ )      | _    |     | 17.5                                           | mUI (p-p) |

| (173)                                                  | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ ) | —    |     | 250 <sup>(176)</sup> ,<br>175 <sup>(174)</sup> | ps (p-p)  |

| t <sub>FOUTCCJ_DC</sub> <sup>(173)</sup>               | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{OUT} < 100 \text{ MHz}$ )   |      |     | $25^{(176)}$ ,<br>17.5 <sup>(174)</sup>        | mUI (p-p) |

<sup>(171)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps. <sup>(172)</sup> The  $f_{REF}$  is fIN/N specification applies when N = 1.

<sup>(174)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.20–0.80 must be  $\geq$  1200 MHz.

<sup>(173)</sup> Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.999999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a different measurement method and are available in the "Worst-Case DCD on Arria V GZ I/O Pins" table.

| Symbol                                                                                                                             | Conditions                                                                | C3, I3L |     |       | C4, I4 |     |       | Unit |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------|-----|-------|--------|-----|-------|------|

|                                                                                                                                    |                                                                           | Min     | Тур | Мах   | Min    | Тур | Max   | Onit |

| True Differential I/O<br>Standards - f <sub>HSDR</sub> (data rate)                                                                 | SERDES factor J = 3 to 10<br>(182), (183)                                 | (184)   | _   | 1250  | (184)  | _   | 1050  | Mbps |

|                                                                                                                                    | SERDES factor $J \ge 4$<br>LVDS TX with DPA<br>(185), (186), (187), (188) | (184)   |     | 1600  | (184)  |     | 1250  | Mbps |

|                                                                                                                                    | SERDES factor J = 2,<br>uses DDR Registers                                | (184)   |     | (189) | (184)  |     | (189) | Mbps |

|                                                                                                                                    | SERDES factor J = 1,<br>uses SDR Register                                 | (184)   | _   | (189) | (184)  |     | (189) | Mbps |

| Emulated Differential I/O<br>Standards with Three<br>External Output Resistor<br>Networks - f <sub>HSDR</sub> (data rate)<br>(190) | SERDES factor J = 4 to 10 $^{(191)}$                                      | (184)   |     | 840   | (184)  |     | 840   | Mbps |

<sup>&</sup>lt;sup>(182)</sup> If the receiver with DPA enabled and transmitter are using shared PLLs, the minimum data rate is 150 Mbps.

- <sup>(185)</sup> Arria V GZ RX LVDS will need DPA. For Arria V GZ TX LVDS, the receiver side component must have DPA.

- Requires package skew compensation with PCB trace length. (186)

- (187)Do not mix single-ended I/O buffer within LVDS I/O bank.

- Chip-to-chip communication only with a maximum load of 5 pF. (188)

- <sup>(189)</sup> The maximum ideal data rate is the SERDES factor (J) x the PLL maximum output frequency (fOUT) provided you can close the design timing and the signal integrity simulation is clean.

- <sup>(190)</sup> You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine leftover timing margin.

- <sup>(191)</sup> When using True LVDS RX channels for emulated LVDS TX channel, only serialization factors 1 and 2 are supported.

<sup>&</sup>lt;sup>(183)</sup> The  $F_{MAX}$  specification is based on the fast clock used for serial data. The interface  $F_{MAX}$  is also dependent on the parallel clock domain which is design dependent and requires timing analysis.

<sup>&</sup>lt;sup>(184)</sup> The minimum specification depends on the clock source (for example, the PLL and clock pin) and the clock routing resource (global, regional, or local) that you use. The I/O differential buffer and input register do not have a minimum toggle rate.

# Glossary

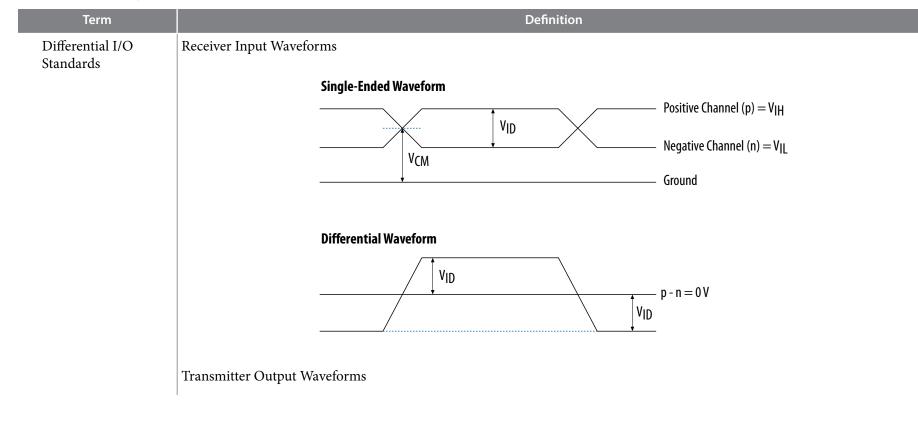

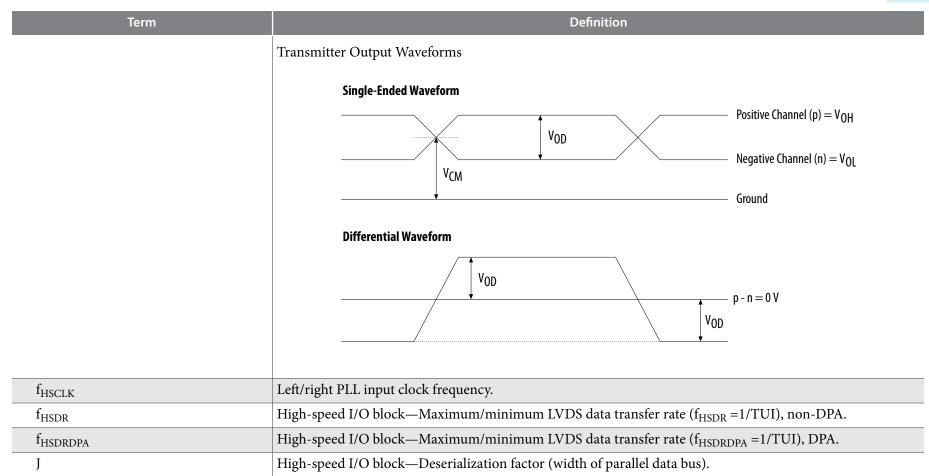

#### Table 2-68: Glossary