Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Number of LABs/CLBs8962Number of Logic Elements/Cells190000Total RAM Bits13284352Number of I/O384Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case896-FBGA (31x31)                | Details                        |                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------|

| Number of Logic Elements/Cells190000Total RAM Bits13284352Number of I/O384Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case896-BBGA, FCBGASupplier Device Package896-FBGA (31x31) | Product Status                 | Obsolete                                                   |

| Total RAM Bits13284352Number of I/O384Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case896-BBGA, FCBGASupplier Device Package896-FBGA (31x31)                                     | Number of LABs/CLBs            | 8962                                                       |

| Number of I/O384Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case896-BBGA, FCBGASupplier Device Package896-FBGA (31x31)                                                           | Number of Logic Elements/Cells | 190000                                                     |

| Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case896-BBGA, FCBGASupplier Device Package896-FBGA (31x31)                                                                           | Total RAM Bits                 | 13284352                                                   |

| Voltage - Supply1.07V ~ 1.13VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case896-BBGA, FCBGASupplier Device Package896-FBGA (31x31)                                                                                           | Number of I/O                  | 384                                                        |

| Mounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ)Package / Case896-BBGA, FCBGASupplier Device Package896-FBGA (31x31)                                                                                                                        | Number of Gates                | -                                                          |

| Operating Temperature-40°C ~ 100°C (TJ)Package / Case896-BBGA, FCBGASupplier Device Package896-FBGA (31x31)                                                                                                                                                  | Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Package / Case     896-BBGA, FCBGA       Supplier Device Package     896-FBGA (31x31)                                                                                                                                                                        | Mounting Type                  | Surface Mount                                              |

| Supplier Device Package     896-FBGA (31x31)                                                                                                                                                                                                                 | Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

|                                                                                                                                                                                                                                                              | Package / Case                 | 896-BBGA, FCBGA                                            |

| Purchase URL https://www.e-xfl.com/product-detail/intel/5agxba5d4f31i5n                                                                                                                                                                                      | Supplier Device Package        | 896-FBGA (31x31)                                           |

|                                                                                                                                                                                                                                                              | Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxba5d4f31i5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol                     | Description                    | Minimum | Maximum | Unit |

|----------------------------|--------------------------------|---------|---------|------|

| V <sub>CCPLL_HPS</sub>     | HPS PLL analog power supply    | -0.50   | 3.25    | V    |

| V <sub>CC_AUX_SHARED</sub> | HPS auxiliary power supply     | -0.50   | 3.25    | V    |

| I <sub>OUT</sub>           | DC output current per pin      | -25     | 40      | mA   |

| T <sub>J</sub>             | Operating junction temperature | -55     | 125     | °C   |

| T <sub>STG</sub>           | Storage temperature (no bias)  | -65     | 150     | °C   |

#### Maximum Allowed Overshoot and Undershoot Voltage

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 4.00 V can only be at 4.00 V for ~15% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 1.5 years.

#### Table 1-2: Maximum Allowed Overshoot During Transitions for Arria V Devices

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime.

1-3

#### **Transceiver Power Supply Operating Conditions**

| Table 1-4: Transceiver Power Supply Operating Conditions for Arria V Device | es |

|-----------------------------------------------------------------------------|----|

|-----------------------------------------------------------------------------|----|

| Symbol                | Description                                           | Minimum <sup>(5)</sup> | Typical                 | Maximum <sup>(5)</sup> | Unit |  |

|-----------------------|-------------------------------------------------------|------------------------|-------------------------|------------------------|------|--|

| V <sub>CCA_GXBL</sub> | Transceiver high voltage power (left side)            | 2.375                  | 2.500                   | 2.625                  | V    |  |

| V <sub>CCA_GXBR</sub> | Transceiver high voltage power (right side)           | 2.373                  | 2.300                   | 2.025                  | v    |  |

| V <sub>CCR_GXBL</sub> | GX and SX speed grades—receiver power (left side)     | 1.08/1.12              | 1.1/1.15 <sup>(6)</sup> | 1.14/1.18              | V    |  |

| V <sub>CCR_GXBR</sub> | GX and SX speed grades—receiver power (right side)    | 1.00/1.12              | 1.1/1.13                | 1.14/1.10              | v    |  |

| V <sub>CCR_GXBL</sub> | GT and ST speed grades—receiver power (left side)     | - 1.17                 | 1.20                    | 1.23                   | V    |  |

| V <sub>CCR_GXBR</sub> | GT and ST speed grades—receiver power (right side)    | 1.17                   | 1.20                    | 1.23                   | v    |  |

| V <sub>CCT_GXBL</sub> | GX and SX speed grades—transmitter power (left side)  | 1.08/1.12              | $1.1/1.15^{(6)}$        | 1.14/1.18              | V    |  |

| V <sub>CCT_GXBR</sub> | GX and SX speed grades—transmitter power (right side) | 1.00/1.12              | 1.1/1.13                | 1.14/1.10              | v    |  |

| V <sub>CCT_GXBL</sub> | GT and ST speed grades—transmitter power (left side)  | 1.17                   | 1.20                    | 1.23                   | V    |  |

| V <sub>CCT_GXBR</sub> | GT and ST speed grades—transmitter power (right side) | 1.17                   | 1.20                    | 1.23                   | v    |  |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power (left side)           | 1.425                  | 1.500                   | 1.575                  | V    |  |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power (right side)          | 1.423                  | 1.300                   | 1.373                  | V    |  |

<sup>(5)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(6)</sup> For data rate <=3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub>, V<sub>CCT\_GXBL/R</sub>, or V<sub>CCL\_GXBL/R</sub> to either 1.1-V or 1.15-V power supply. For data rate >3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub>, V<sub>CCT\_GXBL/R</sub>, or V<sub>CCL\_GXBL/R</sub> to a 1.15-V power supply. For details, refer to the Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines.

| I/O Standard        | V <sub>IL(DC)</sub> (V) |                         | V <sub>IH(DC)</sub> (V) |                          | $V_{IL(AC)}(V)$ $V_{IH(AC)}(V)$ |                         | V <sub>OL</sub> (V) V <sub>OH</sub> (V) |                         | I <sub>OL</sub> <sup>(14)</sup> | I <sub>OH</sub> <sup>(14)</sup> (mA) |

|---------------------|-------------------------|-------------------------|-------------------------|--------------------------|---------------------------------|-------------------------|-----------------------------------------|-------------------------|---------------------------------|--------------------------------------|

|                     | Min                     | Max                     | Min                     | Max                      | Max                             | Min                     | Max                                     | Min                     | (mA)                            | .он (,                               |

| HSTL-15<br>Class II | —                       | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$         | —                        | V <sub>REF</sub> – 0.2          | $V_{REF} + 0.2$         | 0.4                                     | V <sub>CCIO</sub> – 0.4 | 16                              | -16                                  |

| HSTL-12<br>Class I  | -0.15                   | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15         | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$                  | $0.75 \times V_{CCIO}$  | 8                               | -8                                   |

| HSTL-12<br>Class II | -0.15                   | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15         | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$                  | $0.75 \times V_{CCIO}$  | 16                              | -16                                  |

| HSUL-12             | —                       | V <sub>REF</sub> - 0.13 | V <sub>REF</sub> + 0.13 | _                        | V <sub>REF</sub> – 0.22         | $V_{REF} + 0.22$        | $0.1 \times V_{CCIO}$                   | $0.9 \times V_{CCIO}$   |                                 | _                                    |

#### **Differential SSTL I/O Standards**

Table 1-17: Differential SSTL I/O Standards for Arria V Devices

| I/O Standard           | V <sub>CCIO</sub> (V) |      |       | V <sub>SW</sub> | <sub>ING(DC)</sub> (V) | V <sub>X(AC)</sub> (V)          |                      |                                 | V <sub>SV</sub>                               | <sub>VING(AC)</sub> (V)   |

|------------------------|-----------------------|------|-------|-----------------|------------------------|---------------------------------|----------------------|---------------------------------|-----------------------------------------------|---------------------------|

|                        | Min                   | Тур  | Max   | Min             | Мах                    | Min                             | Тур                  | Мах                             | Min                                           | Max                       |

| SSTL-2<br>Class I, II  | 2.375                 | 2.5  | 2.625 | 0.3             | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 – 0.2      | _                    | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$          |

| SSTL-18<br>Class I, II | 1.71                  | 1.8  | 1.89  | 0.25            | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 –<br>0.175 | _                    | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | $V_{CCIO} + 0.6$          |

| SSTL-15<br>Class I, II | 1.425                 | 1.5  | 1.575 | 0.2             | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | —                    | V <sub>CCIO</sub> /2<br>+ 0.15  | $2(V_{IH(AC)} - V_{REF})$                     | $2(V_{IL(AC)} - V_{REF})$ |

| SSTL-135               | 1.283                 | 1.35 | 1.45  | 0.18            | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |

<sup>&</sup>lt;sup>(14)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

$<sup>^{(15)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

| I/O Standard                       |                                                                                                                                                                                                                                                          | V <sub>CCIO</sub> (V) | )     |     | V <sub>ID</sub> (mV) <sup>(16)</sup> |     |       | $V_{ICM(DC)}(V)$                |       | ١     | / <sub>OD</sub> (V) <sup>(17</sup> |     | V <sub>OCM</sub> (V) <sup>(17)(18)</sup> |      | 17)(18) |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----|--------------------------------------|-----|-------|---------------------------------|-------|-------|------------------------------------|-----|------------------------------------------|------|---------|

|                                    | Min                                                                                                                                                                                                                                                      | Тур                   | Мах   | Min | Condition                            | Мах | Min   | Condition                       | Мах   | Min   | Тур                                | Max | Min                                      | Тур  | Max     |

| PCML                               | Transmitter, receiver, and input reference clock pins of high-speed transceivers use the PCML I/O star<br>reference clock I/O pin specifications, refer to Transceiver Specifications for Arria V GX and SX Dev<br>for Arria V GT and ST Devices tables. |                       |       |     |                                      |     |       |                                 |       |       |                                    |     |                                          |      |         |

| 2.5 V                              | 2.375                                                                                                                                                                                                                                                    | 2.5                   | 2.625 | 100 | V <sub>CM</sub> =                    |     | 0.05  | D <sub>MAX</sub> ≤<br>1.25 Gbps | 1.80  | 0.247 |                                    | 0.6 | 1.125                                    | 1.25 | 1.375   |

| LVDS <sup>(19)</sup>               | 2.375                                                                                                                                                                                                                                                    | 2.3                   | 2.023 | 100 | 1.25 V                               |     | 1.05  | D <sub>MAX</sub> ><br>1.25 Gbps | 1.55  | 0.247 | _                                  | 0.0 | 1.125                                    | 1.23 | 1.575   |

| RSDS<br>(HIO) <sup>(20)</sup>      | 2.375                                                                                                                                                                                                                                                    | 2.5                   | 2.625 | 100 | V <sub>CM</sub> =<br>1.25 V          |     | 0.25  |                                 | 1.45  | 0.1   | 0.2                                | 0.6 | 0.5                                      | 1.2  | 1.4     |

| Mini-LVDS<br>(HIO) <sup>(21)</sup> | 2.375                                                                                                                                                                                                                                                    | 2.5                   | 2.625 | 200 |                                      | 600 | 0.300 |                                 | 1.425 | 0.25  | _                                  | 0.6 | 1                                        | 1.2  | 1.4     |

| LVPECL <sup>(22)</sup>             |                                                                                                                                                                                                                                                          |                       |       | 300 |                                      |     | 0.60  | D <sub>MAX</sub> ≤<br>700 Mbps  | 1.80  |       |                                    |     |                                          | _    | _       |

|                                    |                                                                                                                                                                                                                                                          | _                     |       | 500 |                                      |     | 1.00  | D <sub>MAX</sub> ><br>700 Mbps  | 1.60  |       | _                                  |     |                                          |      |         |

#### **Related Information**

- Transceiver Specifications for Arria V GX and SX Devices on page 1-23 Provides the specifications for transmitter, receiver, and reference clock I/O pin.

- $^{(16)}$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

- <sup>(17)</sup>  $R_{\rm L}$  range:  $90 \le R_{\rm L} \le 110 \ \Omega$ .

- <sup>(18)</sup> This applies to default pre-emphasis setting only.

- <sup>(19)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rates above 1.25 Gbps and 0 V to 1.85 V for data rates below 1.25 Gbps.

- <sup>(20)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

- <sup>(21)</sup> For optimized Mini-LVDS receiver performance, the receiver voltage input range must be within 0.3 V to 1.425 V.

- <sup>(22)</sup> For optimized LVPECL receiver performance, the receiver voltage input range must be within 0.85 V to 1.75 V for data rates above 700 Mbps and 0.45 V to 1.95 V for data rates below 700 Mbps.

| Sumbol/Decovintion                                                                       | Condition                     | Transc                                            | eiver Speed G                    | irade 4 | Transc | eiver Speed G                    | Grade 6 | Unit |

|------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------|----------------------------------|---------|--------|----------------------------------|---------|------|

| Symbol/Description                                                                       | Condition                     | Min                                               | Тур                              | Max     | Min    | Тур                              | Max     | Onit |

| Minimum differential eye<br>opening at the receiver<br>serial input pins <sup>(30)</sup> | _                             | 100                                               | _                                | _       | 100    | _                                | _       | mV   |

| V <sub>ICM</sub> (AC coupled)                                                            | _                             | _                                                 | 0.7/0.75/<br>0.8 <sup>(31)</sup> | _       | _      | 0.7/0.75/<br>0.8 <sup>(31)</sup> |         | mV   |

| V <sub>ICM</sub> (DC coupled)                                                            | $\leq 3.2 \text{Gbps}^{(32)}$ | 670                                               | 700                              | 730     | 670    | 700                              | 730     | mV   |

|                                                                                          | 85- $\Omega$ setting          |                                                   | 85                               | —       | _      | 85                               | _       | Ω    |

| Differential on-chip                                                                     | 100- $\Omega$ setting         |                                                   | 100                              | _       |        | 100                              |         | Ω    |

| termination resistors                                                                    | 120-Ω setting                 |                                                   | 120                              | —       |        | 120                              |         | Ω    |

|                                                                                          | 150-Ω setting                 |                                                   | 150                              | _       |        | 150                              |         | Ω    |

| t <sub>LTR</sub> <sup>(33)</sup>                                                         |                               | _                                                 | _                                | 10      | _      | _                                | 10      | μs   |

| $t_{LTD}^{(34)}$                                                                         | _                             | 4                                                 | _                                | _       | 4      | _                                | _       | μs   |

| t <sub>LTD_manual</sub> <sup>(35)</sup>                                                  | _                             | 4                                                 | _                                | —       | 4      | _                                | _       | μs   |

| t <sub>LTR_LTD_manual</sub> <sup>(36)</sup>                                              |                               | 15                                                | _                                |         | 15     |                                  |         | μs   |

| Programmable ppm<br>detector <sup>(37)</sup>                                             | _                             | ±62.5, 100, 125, 200, 250, 300, 500, and 1000 ppm |                                  |         |        |                                  |         |      |

<sup>(30)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the **Receiver Equalization** feature. If you enable the **Receiver Equalization** feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

(31) The AC coupled  $V_{ICM} = 700 \text{ mV}$  for Arria V GX and SX in PCIe mode only. The AC coupled  $V_{ICM} = 750 \text{ mV}$  for Arria V GT and ST in PCIe mode only.

<sup>(32)</sup> For standard protocol compliance, use AC coupling.

$^{(33)}$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

$^{(34)}$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

$^{(35)}$  t<sub>LTD\_manual</sub> is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{\text{LTR\_LTD\_manual}}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

| 1-46 | PLL Specifications |

|------|--------------------|

|------|--------------------|

| Symbol                                          | Parameter                                 | Condition                     | Min | Тур | Max                                       | Unit      |

|-------------------------------------------------|-------------------------------------------|-------------------------------|-----|-----|-------------------------------------------|-----------|

| <b>+</b> (67)                                   | Period jitter for dedicated clock output  | $F_{OUT} \ge 100 \text{ MHz}$ | —   | _   | 175                                       | ps (p-p)  |

| t <sub>outpj_dc</sub> <sup>(67)</sup>           | in integer PLL                            | $F_{OUT} < 100 \text{ MHz}$   | —   | _   | 17.5                                      | mUI (p-p) |

| t(67)                                           | Period jitter for dedicated clock output  | $F_{OUT} \ge 100 \text{ MHz}$ |     |     | 250 <sup>(68)</sup> , 175 <sup>(69)</sup> | ps (p-p)  |

| t <sub>foutpj_dc</sub> <sup>(67)</sup>          | in fractional PLL                         | $F_{OUT} < 100 \text{ MHz}$   |     |     | 25 <sup>(68)</sup> , 17.5 <sup>(69)</sup> | mUI (p-p) |

| t                                               | Cycle-to-cycle jitter for dedicated clock | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 175                                       | ps (p-p)  |

| t <sub>OUTCCJ_DC</sub> <sup>(67)</sup>          | output in integer PLL                     | $F_{OUT} < 100 \text{ MHz}$   | _   |     | 17.5                                      | mUI (p-p) |

| + (67)                                          | Cycle-to-cycle jitter for dedicated clock | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 250 <sup>(68)</sup> , 175 <sup>(69)</sup> | ps (p-p)  |

| t <sub>FOUTCCJ_DC</sub> <sup>(67)</sup>         | output in fractional PLL                  | $F_{OUT} < 100 \text{ MHz}$   | —   |     | 25 <sup>(68)</sup> , 17.5 <sup>(69)</sup> | mUI (p-p) |

| t <sub>OUTPJ_IO</sub> <sup>(67)(70)</sup>       | Period jitter for clock output on a       | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 600                                       | ps (p-p)  |

| OUTPJ_IO                                        | regular I/O in integer PLL                | $F_{OUT} < 100 MHz$           | _   | _   | 60                                        | mUI (p-p) |

| t <sub>FOUTPJ_IO</sub> <sup>(67)(68)(70)</sup>  | Period jitter for clock output on a       | $F_{OUT} \ge 100 \text{ MHz}$ | —   |     | 600                                       | ps (p-p)  |

| FOUTPJ_IO                                       | regular I/O in fractional PLL             | $F_{OUT} < 100 \text{ MHz}$   |     |     | 60                                        | mUI (p-p) |

| <b>t</b> (67)(70)                               | Cycle-to-cycle jitter for clock output on | $F_{OUT} \ge 100 \text{ MHz}$ |     |     | 600                                       | ps (p-p)  |

| t <sub>OUTCCJ_IO</sub> <sup>(67)(70)</sup>      | a regular I/O in integer PLL              | $F_{OUT} < 100 \text{ MHz}$   | —   | _   | 60                                        | mUI (p-p) |

| <b>t</b> (67)(68)(70)                           | Cycle-to-cycle jitter for clock output on | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 600                                       | ps (p-p)  |

| t <sub>FOUTCCJ_IO</sub> <sup>(67)(68)(70)</sup> | a regular I/O in fractional PLL           | $F_{OUT} < 100 \text{ MHz}$   |     |     | 60                                        | mUI (p-p) |

<sup>(67)</sup> Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.99999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a different measurement method and are available in Memory Output Clock Jitter Specification for Arria V Devices table.

<sup>&</sup>lt;sup>(68)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.05–0.95 must be  $\geq$  1000 MHz.

<sup>&</sup>lt;sup>(69)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.20–0.80 must be  $\geq$  1200 MHz.

<sup>&</sup>lt;sup>(70)</sup> External memory interface clock output jitter specifications use a different measurement method, which are available in Memory Output Clock Jitter Specification for Arria V Devices table.

#### Table 1-38: Memory Block Performance Specifications for Arria V Devices

| Memory | Mode                                                                                                    | Resourc | es Used |          | Performance |     | Unit |  |

|--------|---------------------------------------------------------------------------------------------------------|---------|---------|----------|-------------|-----|------|--|

| Memory | Mode                                                                                                    | ALUTs   | Memory  | -I3, -C4 | –I5, –C5    | -C6 | Onit |  |

|        | Single port, all supported widths                                                                       | 0       | 1       | 500      | 450         | 400 | MHz  |  |

|        | Simple dual-port, all supported widths                                                                  | 0       | 1       | 500      | 450         | 400 | MHz  |  |

|        | Simple dual-port with read and write at the same address                                                | 0       | 1       | 400      | 350         | 300 | MHz  |  |

|        | ROM, all supported width                                                                                | —       |         | 500      | 450         | 400 | MHz  |  |

|        | Single-port, all supported widths                                                                       | 0       | 1       | 400      | 350         | 285 | MHz  |  |

|        | Simple dual-port, all supported widths                                                                  | 0       | 1       | 400      | 350         | 285 | MHz  |  |

| Block  | Simple dual-port with the read-during-<br>write option set to <b>Old Data</b> , all supported<br>widths | 0       | 1       | 315      | 275         | 240 | MHz  |  |

|        | True dual port, all supported widths                                                                    | 0       | 1       | 400      | 350         | 285 | MHz  |  |

|        | ROM, all supported widths                                                                               | 0       | 1       | 400      | 350         | 285 | MHz  |  |

#### **Internal Temperature Sensing Diode Specifications**

#### Table 1-39: Internal Temperature Sensing Diode Specifications for Arria V Devices

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate | Conversion<br>Time | Resolution | Minimum Resolution with no<br>Missing Codes |

|-------------------|----------|-----------------------------|---------------|--------------------|------------|---------------------------------------------|

| -40 to 100°C      | ±8°C     | No                          | 1 MHz         | < 100 ms           | 8 bits     | 8 bits                                      |

# **Periphery Performance**

This section describes the periphery performance, high-speed I/O, and external memory interface.

Actual achievable frequency depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

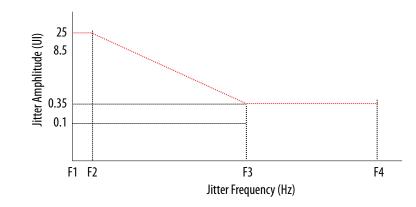

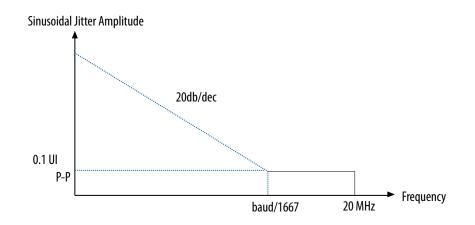

#### LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specifications

#### Table 1-42: LVDS Soft-CDR/DPA Sinusoidal Jitter Mask Values for a Data Rate Equal to 1.25 Gbps

| Jitter Frequency (Hz) |            | Sinusoidal Jitter (UI) |

|-----------------------|------------|------------------------|

| F1                    | 10,000     | 25.000                 |

| F2                    | 17,565     | 25.000                 |

| F3                    | 1,493,000  | 0.350                  |

| F4                    | 50,000,000 | 0.350                  |

## **DLL Frequency Range Specifications**

#### Table 1-43: DLL Frequency Range Specifications for Arria V Devices

| Parameter                     | -I3, -C4  | -I5, -C5  | -C6       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 200 - 667 | 200 - 667 | 200 - 667 | MHz  |

## DQS Logic Block Specifications

#### Table 1-44: DQS Phase Shift Error Specifications for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Arria V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -I3, -C4 | –I5, –C5 | -C6 | Unit |

|----------------------------|----------|----------|-----|------|

| 2                          | 40       | 80       | 80  | ps   |

#### 1-62 SPI Timing Characteristics

| Symbol                 | Description                                       | Min | Мах | Unit |

|------------------------|---------------------------------------------------|-----|-----|------|

| T <sub>h</sub>         | SPI MISO hold time                                | 1   | _   | ns   |

| T <sub>dutycycle</sub> | SPI_CLK duty cycle                                | 45  | 55  | %    |

| T <sub>dssfrst</sub>   | Output delay SPI_SS valid before first clock edge | 8   |     | ns   |

| T <sub>dsslst</sub>    | Output delay SPI_SS valid after last clock edge   | 8   |     | ns   |

| T <sub>dio</sub>       | Master-out slave-in (MOSI) output delay           | -1  | 1   | ns   |

**Altera Corporation**

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(86)</sup> This value is based on rx\_sample\_dly = 1 and spi\_m\_clk = 120 MHz. spi\_m\_clk is the internal clock that is used by SPI Master to derive it's SCLK\_OUT. These timings are based on rx\_sample\_dly of 1. This delay can be adjusted as needed to accommodate slower response times from the slave. Note that a delay of 0 is not allowed. The setup time can be used as a reference starting point. It is very crucial to do a calibration to get the correct rx\_sample\_dly value because each SPI slave device may have different output delay and each application board may have different path delay. For more information about rx\_sample\_delay, refer to the SPI Controller chapter in the Hard Processor System Technical Reference Manual.

After the Boot ROM code exits and control is passed to the preloader, software can adjust the value of drvsel and smplsel via the system manager. drvsel can be set from 1 to 7 and smplsel can be set from 0 to 7. While the preloader is executing, the values for SDMMC\_CLK and SDMMC\_CLK\_OUT increase to a maximum of 200 MHz and 50 MHz respectively.

The SD/MMC interface calibration support will be available in a future release of the preloader through the SoC EDS software update.

| Symbol                                              | Description                                         | Min                                                         | Мах                                                                                                  | Unit |

|-----------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|

|                                                     | SDMMC_CLK clock period (Identification mode)        | 20                                                          | _                                                                                                    | ns   |

| T <sub>sdmmc_clk</sub> (internal reference clock)   | SDMMC_CLK clock period<br>(Default speed mode)      | 5                                                           | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK clock period<br>(High speed mode)         | 5                                                           | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK_OUT clock<br>period (Identification mode) | 2500                                                        | _                                                                                                    | ns   |

| T <sub>sdmmc_clk_out</sub> (interface output clock) | SDMMC_CLK_OUT clock period (Default speed mode)     | 40                                                          | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK_OUT clock<br>period (High speed mode)     | 20                                                          | _                                                                                                    | ns   |

| T <sub>dutycycle</sub>                              | SDMMC_CLK_OUT duty cycle                            | 45                                                          | 55                                                                                                   | %    |

| T <sub>d</sub>                                      | SDMMC_CMD/SDMMC_D<br>output delay                   | $\frac{(T_{sdmmc\_clk} \times drvsel)/2}{-1.23}$            | $\begin{array}{c} (\mathrm{T}_{sdmmc\_clk} \times \texttt{drvsel})/2 \\ + 1.69^{\ (87)} \end{array}$ | ns   |

| T <sub>su</sub>                                     | Input setup time                                    | $1.05 - (T_{sdmmc_clk} \times smplsel)/2^{(88)}$            |                                                                                                      | ns   |

| T <sub>h</sub>                                      | Input hold time                                     | $\frac{(T_{sdmmc\_clk} \times \texttt{smplsel})}{2^{(88)}}$ | —                                                                                                    | ns   |

<sup>&</sup>lt;sup>(87)</sup> drvsel is the drive clock phase shift select value.

<sup>&</sup>lt;sup>(88)</sup> smplsel is the sample clock phase shift select value.

#### 2-2 Absolute Maximum Ratings

Lower number refers to faster speed grade.

L = Low power devices.

| Transceiver Speed Grade | Core Speed Grade |     |     |     |  |

|-------------------------|------------------|-----|-----|-----|--|

| Transceiver Speeu Graue | C3               | C4  | I3L | 14  |  |

| 2                       | Yes              | _   | Yes | -   |  |

| 3                       |                  | Yes |     | Yes |  |

#### **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Arria V GZ devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied for these conditions.

**Caution:** Conditions other than those listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

#### Table 2-2: Absolute Maximum Ratings for Arria V GZ Devices

| Symbol                | Description                                                            | Minimum | Maximum | Unit |

|-----------------------|------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>       | Power supply for core voltage and periphery circuitry                  | -0.5    | 1.35    | V    |

| V <sub>CCPT</sub>     | Power supply for programmable power technology                         | -0.5    | 1.8     | V    |

| V <sub>CCPGM</sub>    | Power supply for configuration pins                                    | -0.5    | 3.9     | V    |

| V <sub>CC_AUX</sub>   | Auxiliary supply for the programmable power technology                 | -0.5    | 3.4     | V    |

| V <sub>CCBAT</sub>    | Battery back-up power supply for design security volatile key register | -0.5    | 3.9     | V    |

| V <sub>CCPD</sub>     | I/O pre-driver power supply                                            | -0.5    | 3.9     | V    |

| V <sub>CCIO</sub>     | I/O power supply                                                       | -0.5    | 3.9     | V    |

| V <sub>CCD_FPLL</sub> | PLL digital power supply                                               | -0.5    | 1.8     | V    |

| V <sub>CCA_FPLL</sub> | PLL analog power supply                                                | -0.5    | 3.4     | V    |

#### **Transceiver Power Supply Requirements**

#### Table 2-7: Transceiver Power Supply Voltage Requirements for Arria V GZ Devices

| Conditions                                                                                                                                | VCCR_GXB and VCCT_GXB <sup>(122)</sup> | VCCA_GXB | VCCH_GXB | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------|----------|------|

| If BOTH of the following conditions are true:                                                                                             | 1.05                                   |          |          |      |

| <ul> <li>Data rate &gt; 10.3 Gbps.</li> <li>DFE is used.</li> </ul>                                                                       |                                        |          |          |      |

| If ANY of the following conditions are true <sup>(123)</sup> :                                                                            | 1.0                                    | 3.0      |          |      |

| <ul> <li>ATX PLL is used.</li> <li>Data rate &gt; 6.5Gbps.</li> <li>DFE (data rate ≤ 10.3 Gbps), AEQ, or EyeQ feature is used.</li> </ul> |                                        |          | 1.5      | V    |

| If ALL of the following conditions are true:                                                                                              | 0.85                                   | 2.5      |          |      |

| <ul> <li>ATX PLL is not used.</li> <li>Data rate ≤ 6.5Gbps.</li> <li>DFE, AEQ, and EyeQ are not used.</li> </ul>                          |                                        |          |          |      |

## **DC Characteristics**

#### **Supply Current**

Standby current is the current drawn from the respective power rails used for power budgeting.

Use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design because these currents vary greatly with the resources you use.

Send Feedback

<sup>&</sup>lt;sup>(122)</sup> If the VCCR\_GXB and VCCT\_GXB supplies are set to 1.0 V or 1.05 V, they cannot be shared with the VCC core supply. If the VCCR\_GXB and VCCT\_GXB are set to 0.85 V, they can be shared with the VCC core supply.

<sup>&</sup>lt;sup>(123)</sup> Choose this power supply voltage requirement option if you plan to upgrade your design later with any of the listed conditions.

| Symbol               | Description                                                            | Conditions                 | Resistance | Unit   |   |

|----------------------|------------------------------------------------------------------------|----------------------------|------------|--------|---|

| Symbol               | Description                                                            | Description Conditions     |            | C4, I4 |   |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | % |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | % |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | % |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | % |

| 100-Ω R <sub>D</sub> | Internal differential termination (100- $\Omega$ setting)              | $V_{CCIO} = 2.5 V$         | ±25        | ±25    | % |

#### Figure 2-1: OCT Variation Without Re-Calibration for Arria V GZ Devices

$$\mathbf{R}_{\text{OCT}} = \mathbf{R}_{\text{SCAL}} \left( 1 + \left( \frac{dR}{dT} \times \bigtriangleup T \right) \pm \left( \frac{dR}{dV} \times \bigtriangleup V \right) \right)$$

Notes:

1. The  $R_{oct}$  value shows the range of OCT resistance with the variation of temperature and  $V_{ccio}$ . 2.  $R_{scAL}$  is the OCT resistance value at power-up. 3.  $\Delta T$  is the variation of temperature with respect to the temperature at power-up. 4.  $\Delta V$  is the variation of voltage with respect to the  $V_{ccio}$  at power-up. 5. dR/dT is the percentage change of  $R_{scAL}$  with temperature. 6. dR/dV is the percentage change of  $R_{scAL}$  with voltage

6. dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

#### Table 2-12: OCT Variation after Power-Up Calibration for Arria V GZ Devices

Valid for a V<sub>CCIO</sub> range of  $\pm$ 5% and a temperature range of 0° to 85°C.

#### **Hot Socketing**

#### Table 2-14: Hot Socketing Specifications for Arria V GZ Devices

| Symbol                    | Description                                | Maximum               |

|---------------------------|--------------------------------------------|-----------------------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                     | 300 µA                |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                     | 8 mA <sup>(124)</sup> |

| I <sub>XCVR-TX (DC)</sub> | DC current per transceiver transmitter pin | 100 mA                |

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver pin    | 50 mA                 |

#### Internal Weak Pull-Up Resistor

#### Table 2-15: Internal Weak Pull-Up Resistor for Arria V GZ Devices

All I/O pins have an option to enable the weak pull-up resistor except the configuration, test, and JTAG pins. The internal weak pull-down feature is only available for the JTAG TCK pin. The typical value for this internal weak pull-down resistor is approximately 25 k $\Omega$ .

| Symbol                                                                                                                              | Description                           | V <sub>CCIO</sub> Conditions (V) <sup>(125)</sup> | Value <sup>(126)</sup> | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------|------------------------|------|

|                                                                                                                                     | 3.0 ±5%                               | 25                                                | kΩ                     |      |

|                                                                                                                                     | 2.5 ±5%                               | 25                                                | kΩ                     |      |

|                                                                                                                                     | Value of the I/O pin pull-up resistor | 1.8 ±5%                                           | 25                     | kΩ   |

| R <sub>PU</sub> before and during configuration, as well as<br>user mode if you enable the<br>programmable pull-up resistor option. | 1.5 ±5%                               | 25                                                | kΩ                     |      |

|                                                                                                                                     | 1.35 ±5%                              | 25                                                | kΩ                     |      |

|                                                                                                                                     | 1.25 ±5%                              | 25                                                | kΩ                     |      |

|                                                                                                                                     |                                       | 1.2 ±5%                                           | 25                     | kΩ   |

<sup>(124)</sup> The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

$<sup>^{(125)}</sup>$  The pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

$<sup>^{(126)}</sup>$  These specifications are valid with a ±10% tolerance to cover changes over PVT.

# **Switching Characteristics**

# **Transceiver Performance Specifications**

#### **Reference Clock**

#### Table 2-22: Reference Clock Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                                                                                          | Conditions             | Transceiver Speed Grade 2                            |     | Transceiver Speed Grade 3 |     |     | Unit |      |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------|-----|---------------------------|-----|-----|------|------|

|                                                                                                                             | Conditions             | Min                                                  | Тур | Max                       | Min | Тур | Max  | Onit |

| Reference Clock                                                                                                             |                        |                                                      |     |                           |     |     |      |      |

| Supported I/O StandardsDedicated reference clock1.2-V PCML, 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, Differential LV<br>and HCSL |                        |                                                      |     | PECL, LVDS,               |     |     |      |      |

|                                                                                                                             | RX reference clock pin | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |     |                           |     |     |      |      |

| Input Reference Clock<br>Frequency<br>(CMU PLL) <sup>(137)</sup>                                                            | _                      | 40                                                   | _   | 710                       | 40  | _   | 710  | MHz  |

| Input Reference Clock<br>Frequency<br>(ATX PLL) <sup>(137)</sup>                                                            | _                      | 100                                                  | _   | 710                       | 100 | _   | 710  | MHz  |

<sup>(137)</sup> The input reference clock frequency options depend on the data rate and the device speed grade.

| Sumbol/Description                         | Conditions -                                              | Transceiver Speed Grade 2 |      | Transceiver Speed Grade 3 |                   |      | Unit |      |

|--------------------------------------------|-----------------------------------------------------------|---------------------------|------|---------------------------|-------------------|------|------|------|

| Symbol/Description                         |                                                           | Min                       | Тур  | Max                       | Min               | Тур  | Max  | Unit |

| Rise time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> | _                         | _    | 400                       | _                 | _    | 400  | 20   |

| Fall time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> |                           | _    | 400                       | _                 |      | 400  | ps   |

| Duty cycle                                 | —                                                         | 45                        | _    | 55                        | 45                |      | 55   | %    |

| Spread-spectrum modulating clock frequency | PCI Express <sup>®</sup> (PCIe)                           | 30                        | _    | 33                        | 30                |      | 33   | kHz  |

| Spread-spectrum downspread                 | PCIe                                                      |                           | 0 to | _                         | _                 | 0 to | _    | %    |

|                                            |                                                           |                           | -0.5 |                           |                   | -0.5 |      |      |

| On-chip termination resistors              | —                                                         |                           | 100  | _                         | _                 | 100  | _    | Ω    |

| Absolute V <sub>MAX</sub>                  | Dedicated reference clock pin                             |                           | _    | 1.6                       | _                 |      | 1.6  | V    |

|                                            | RX reference clock pin                                    |                           | _    | 1.2                       | _                 |      | 1.2  |      |

| Absolute V <sub>MIN</sub>                  | —                                                         | -0.4                      | _    | _                         | -0.4              | _    | _    | V    |

| Peak-to-peak differential input<br>voltage | -                                                         | 200                       | -    | 1600                      | 200               | _    | 1600 | mV   |

| V <sub>ICM</sub> (AC coupled)              | Dedicated reference clock pin                             | 1000/900/850 (139)        |      | 1000/900/850 (139)        |                   |      | mV   |      |

|                                            | RX reference clock pin                                    | 1.0/0.9/0.85 (140)        |      |                           | 1.0/0.9/0.85(140) |      |      | mV   |

| V <sub>ICM</sub> (DC coupled)              | HCSL I/O standard for<br>PCIe reference clock             | 250                       | _    | 550                       | 250               |      | 550  | mV   |

<sup>(138)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

(139) The reference clock common mode voltage is equal to the V<sub>CCR\_GXB</sub> power supply level.

(140) This supply follows VCCR\_GXB

AV-51002 2017.02.10

| Symbol                                                 | Parameter                                                                                              | Min  | Тур | Мах                                            | Unit      |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|-----|------------------------------------------------|-----------|

| t <sub>INCCJ</sub> <sup>(171)</sup> , <sup>(172)</sup> | Input clock cycle-to-cycle jitter ( $f_{REF} \ge 100 \text{ MHz}$ )                                    | —    | _   | 0.15                                           | UI (p-p)  |

|                                                        | Input clock cycle-to-cycle jitter ( $f_{REF} < 100 \text{ MHz}$ )                                      | -750 |     | +750                                           | ps (p-p)  |

| t <sub>OUTPJ_DC</sub> <sup>(173)</sup>                 | Period Jitter for dedicated clock output in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )              | _    | _   | 175                                            | ps (p-p)  |

|                                                        | Period Jitter for dedicated clock output in integer<br>PLL (f <sub>OUT</sub> < 100 Mhz)                | _    |     | 17.5                                           | mUI (p-p) |

| t <sub>FOUTPJ_DC</sub> <sup>(173)</sup>                | Period Jitter for dedicated clock output in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )           | _    |     | $250^{(176)}, \\ 175^{(174)}$                  | ps (p-p)  |

|                                                        | Period Jitter for dedicated clock output in fractional<br>PLL (f <sub>OUT</sub> < 100 MHz)             | _    | _   | $25^{(176)},$<br>17.5 <sup>(174)</sup>         | mUI (p-p) |

| t <sub>OUTCCJ_DC</sub> <sup>(173)</sup>                | Cycle-to-cycle Jitter for a dedicated clock output in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )    | _    | _   | 175                                            | ps (p-p)  |

|                                                        | Cycle-to-cycle Jitter for a dedicated clock output in integer PLL (f <sub>OUT</sub> < 100 MHz)         | _    |     | 17.5                                           | mUI (p-p) |

| t <sub>FOUTCCJ_DC</sub> <sup>(173)</sup>               | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ ) | —    |     | 250 <sup>(176)</sup> ,<br>175 <sup>(174)</sup> | ps (p-p)  |

|                                                        | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{OUT} < 100 \text{ MHz}$ )   |      |     | $25^{(176)}, \\ 17.5^{(174)}$                  | mUI (p-p) |

<sup>(171)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps. <sup>(172)</sup> The  $f_{REF}$  is fIN/N specification applies when N = 1.

<sup>(174)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.20–0.80 must be  $\geq$  1200 MHz.

<sup>(173)</sup> Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.999999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a different measurement method and are available in the "Worst-Case DCD on Arria V GZ I/O Pins" table.

## **OCT Calibration Block Specifications**

#### Table 2-51: OCT Calibration Block Specifications for Arria V GZ Devices

| Symbol                | Description                                                                                                                                                               | Min | Тур  | Мах | Unit   |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by the OCT calibration blocks                                                                                                                              | _   |      | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of OCTUSRCLK clock cycles required for OCT R <sub>S</sub> /R <sub>T</sub> calibration                                                                              | _   | 1000 |     | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for the OCT code to shift out                                                                                                   | _   | 32   |     | Cycles |

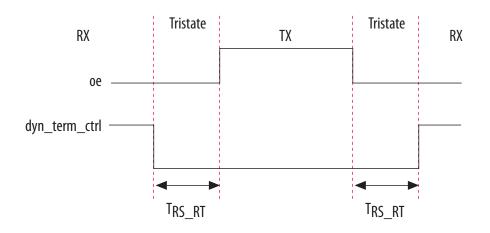

| T <sub>RS_RT</sub>    | Time required between the dyn_term_ctrl and oe signal transitions in a bidirectional I/O buffer to dynamically switch between OCT $R_S$ and $R_T$ (See the figure below.) |     | 2.5  |     | ns     |

## Figure 2-6: Timing Diagram for oe and dyn\_term\_ctrl Signals

#### Table 2-57: FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is >1

Use these timing parameters when you use the decompression and design security features.

| Symbol                              | Parameter                                    | Minimum                                | Maximum     | Unit |

|-------------------------------------|----------------------------------------------|----------------------------------------|-------------|------|

| t <sub>CF2CD</sub>                  | nconfig low to conf_done low                 | -                                      | 600         | ns   |

| t <sub>CF2ST0</sub>                 | nconfig low to nstatus low                   | -                                      | 600         | ns   |

| t <sub>CFG</sub>                    | nCONFIG low pulse width                      | 2                                      | _           | μs   |

| t <sub>STATUS</sub>                 | nSTATUS low pulse width                      | 268                                    | 1,506 (210) | μs   |

| t <sub>CF2ST1</sub>                 | nCONFIG high to nSTATUS high                 | —                                      | 1,506 (211) | μs   |

| t <sub>CF2CK</sub> (212)            | nCONFIG high to first rising edge on DCLK    | 1,506                                  | _           | μs   |

| t <sub>ST2CK</sub> <sup>(212)</sup> | nSTATUS high to first rising edge of DCLK    | 2                                      | _           | μs   |

| t <sub>DSU</sub>                    | DATA[] setup time before rising edge on DCLK | 5.5                                    | _           | ns   |

| t <sub>DH</sub>                     | DATA[] hold time after rising edge on DCLK   | N-1/f <sub>DCLK</sub> <sup>(213)</sup> | _           | S    |

| t <sub>CH</sub>                     | DCLK high time                               | $0.45 	imes 1/f_{MAX}$                 | _           | S    |

| t <sub>CL</sub>                     | DCLK low time                                | $0.45 \times 1/f_{MAX}$                | _           | S    |

| t <sub>CLK</sub>                    | DCLK period                                  | 1/f <sub>MAX</sub>                     | —           | S    |

| £                                   | DCLK frequency (FPP ×8/×16)                  | -                                      | 125         | MHz  |

| $f_{MAX}$                           | DCLK frequency (FPP ×32)                     | —                                      | 100         | MHz  |

| t <sub>R</sub>                      | Input rise time                              | -                                      | 40          | ns   |

| t <sub>F</sub>                      | Input fall time                              | -                                      | 40          | ns   |

| t <sub>CD2UM</sub>                  | CONF_DONE high to user mode <sup>(214)</sup> | 175                                    | 437         | μs   |

<sup>(210)</sup> You can obtain this value if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>(211)</sup> You can obtain this value if you do not delay configuration by externally holding the nSTATUS low.

$^{(212)}$  If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

$^{(213)}$  N is the DCLK-to-DATA ratio and  $f_{DCLK}$  is the DCLK frequency the system is operating.

<sup>(214)</sup> The minimum and maximum numbers apply only if you use the internal oscillator as the clock source for initializing the device.

Arria V GZ Device Datasheet

**Altera Corporation**