### Intel - 5AGXBA7D6F35C6N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 11460                                                      |

| Number of Logic Elements/Cells | 242000                                                     |

| Total RAM Bits                 | 15470592                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxba7d6f35c6n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Caution:** Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

## Table 1-1: Absolute Maximum Ratings for Arria V Devices

| Symbol                    | Description                                                                                                      | Minimum | Maximum | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>           | Core voltage power supply                                                                                        | -0.50   | 1.43    | V    |

| V <sub>CCP</sub>          | Periphery circuitry, PCIe <sup>®</sup> hardIP block, and transceiver physical coding sublayer (PCS) power supply | -0.50   | 1.43    | V    |

| V <sub>CCPGM</sub>        | Configuration pins power supply                                                                                  | -0.50   | 3.90    | V    |

| V <sub>CC_AUX</sub>       | Auxiliary supply                                                                                                 | -0.50   | 3.25    | V    |

| V <sub>CCBAT</sub>        | Battery back-up power supply for design security volatile key register                                           | -0.50   | 3.90    | V    |

| V <sub>CCPD</sub>         | I/O pre-driver power supply                                                                                      | -0.50   | 3.90    | V    |

| V <sub>CCIO</sub>         | I/O power supply                                                                                                 | -0.50   | 3.90    | V    |

| V <sub>CCD_FPLL</sub>     | Phase-locked loop (PLL) digital power supply                                                                     | -0.50   | 1.80    | V    |

| V <sub>CCA_FPLL</sub>     | PLL analog power supply                                                                                          | -0.50   | 3.25    | V    |

| V <sub>CCA_GXB</sub>      | Transceiver high voltage power                                                                                   | -0.50   | 3.25    | V    |

| V <sub>CCH_GXB</sub>      | Transmitter output buffer power                                                                                  | -0.50   | 1.80    | V    |

| V <sub>CCR_GXB</sub>      | Receiver power                                                                                                   | -0.50   | 1.50    | V    |

| V <sub>CCT_GXB</sub>      | Transmitter power                                                                                                | -0.50   | 1.50    | V    |

| V <sub>CCL_GXB</sub>      | Transceiver clock network power                                                                                  | -0.50   | 1.50    | V    |

| VI                        | DC input voltage                                                                                                 | -0.50   | 3.80    | V    |

| V <sub>CC_HPS</sub>       | HPS core voltage and periphery circuitry power supply                                                            | -0.50   | 1.43    | V    |

| V <sub>CCPD_HPS</sub>     | HPS I/O pre-driver power supply                                                                                  | -0.50   | 3.90    | V    |

| V <sub>CCIO_HPS</sub>     | HPS I/O power supply                                                                                             | -0.50   | 3.90    | V    |

| V <sub>CCRSTCLK_HPS</sub> | HPS reset and clock input pins power supply                                                                      | -0.50   | 3.90    | V    |

AV-51002 2017.02.10

1-5

| Symbol                            | Description                                 | Condition          | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|-----------------------------------|---------------------------------------------|--------------------|------------------------|---------|------------------------|------|

| V <sub>CC</sub>                   | Core veltage power supply                   | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| V <sub>CC</sub>                   | Core voltage power supply                   | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

| V                                 | Periphery circuitry, PCIe hard IP block,    | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| V <sub>CCP</sub>                  | and transceiver PCS power supply            | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

|                                   |                                             | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| V                                 | Configuration pins power supply             | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

| V <sub>CCPGM</sub>                |                                             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

|                                   |                                             | 1.8 V              | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CC_AUX</sub>               | Auxiliary supply                            | —                  | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCBAT</sub> <sup>(2)</sup> | Battery back-up power supply                | _                  | 1.2                    | _       | 3.0                    | V    |

|                                   | (For design security volatile key register) |                    |                        |         |                        |      |

|                                   |                                             | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| V <sub>CCPD</sub> <sup>(3)</sup>  | I/O pre-driver power supply                 | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

|                                   |                                             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

<sup>(1)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

(2) If you do not use the design security feature in Arria V devices, connect V<sub>CCBAT</sub> to a 1.5-V, 2.5-V, or 3.0-V power supply. Arria V power-on reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

<sup>&</sup>lt;sup>(3)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25, or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.  $V_{CCPD}$  must be 3.3 V when  $V_{CCIO}$  is 3.3 V.

## Table 1-31: Transceiver-FPGA Fabric Interface Specifications for Arria V GT and ST Devices

| Symbol/Description                  | Transceiver S | peed Grade 3                                | Unit |

|-------------------------------------|---------------|---------------------------------------------|------|

| Symbol/Description                  | Min           | Мах                                         | Unit |

| Interface speed (PMA direct mode)   | 50            | 153.6 <sup>(56)</sup> , 161 <sup>(57)</sup> | MHz  |

| Interface speed (single-width mode) | 25            | 187.5                                       | MHz  |

| Interface speed (double-width mode) | 25            | 163.84                                      | MHz  |

**Related Information**

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 1-35

- CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain on page 1-36

<sup>&</sup>lt;sup>(56)</sup> The maximum frequency when core transceiver local routing is selected.

<sup>&</sup>lt;sup>(57)</sup> The maximum frequency when core transceiver network routing (GCLK, RCLK, or PCLK) is selected.

| Protocol                             | Sub-protocol                  | Data Rate (Mbps) |

|--------------------------------------|-------------------------------|------------------|

|                                      | CPRI E6LV                     | 614.4            |

|                                      | CPRI E6HV                     | 614.4            |

|                                      | CPRI E6LVII                   | 614.4            |

|                                      | CPRI E12LV                    | 1,228.8          |

|                                      | CPRI E12HV                    | 1,228.8          |

|                                      | CPRI E12LVII                  | 1,228.8          |

| Common Public Radio Interface (CPRI) | CPRI E24LV                    | 2,457.6          |

|                                      | CPRI E24LVII                  | 2,457.6          |

|                                      | CPRI E30LV                    | 3,072            |

|                                      | CPRI E30LVII                  | 3,072            |

|                                      | CPRI E48LVII                  | 4,915.2          |

|                                      | CPRI E60LVII                  | 6,144            |

|                                      | CPRI E96LVIII <sup>(60)</sup> | 9,830.4          |

| Gbps Ethernet (GbE)                  | GbE 1250                      | 1,250            |

|                                      | OBSAI 768                     | 768              |

| OBSAI                                | OBSAI 1536                    | 1,536            |

| OBSAI                                | OBSAI 3072                    | 3,072            |

|                                      | OBSAI 6144                    | 6,144            |

|                                      | SDI 270 SD                    | 270              |

| Serial digital interface (SDI)       | SDI 1485 HD                   | 1,485            |

|                                      | SDI 2970 3G                   | 2,970            |

<sup>&</sup>lt;sup>(60)</sup> You can achieve compliance with TX channel restriction of one HSSI channel per six-channel transceiver bank.

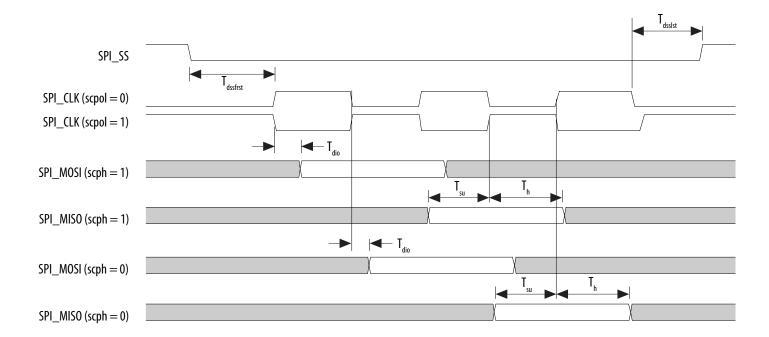

### Figure 1-9: SPI Master Timing Diagram

#### Table 1-53: SPI Slave Timing Requirements for Arria V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol            | Description                                     | Min | Max | Unit |

|-------------------|-------------------------------------------------|-----|-----|------|

| T <sub>clk</sub>  | CLK clock period                                | 20  |     | ns   |

| T <sub>s</sub>    | MOSI Setup time                                 | 5   |     | ns   |

| T <sub>h</sub>    | MOSI Hold time                                  | 5   |     | ns   |

| T <sub>suss</sub> | Setup time SPI_SS valid before first clock edge | 8   |     | ns   |

| T <sub>hss</sub>  | Hold time SPI_SS valid after last clock edge    | 8   |     | ns   |

| T <sub>d</sub>    | MISO output delay                               |     | 6   | ns   |

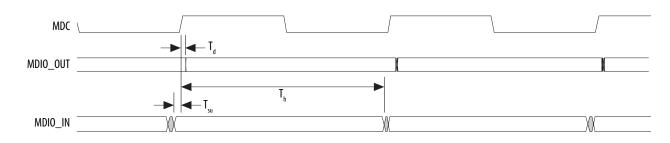

## Figure 1-15: MDIO Timing Diagram

# I<sup>2</sup>C Timing Characteristics

# Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Symbol                | Description                                       | Standar | d Mode | Fast | Mode | Unit |

|-----------------------|---------------------------------------------------|---------|--------|------|------|------|

| Symbol                | Description                                       | Min     | Max    | Min  | Max  | Onit |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10      | —      | 2.5  | _    | μs   |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7     | —      | 0.6  |      | μs   |

| T <sub>clklow</sub>   | SCL low time                                      | 4       | _      | 1.3  |      | μs   |

| T <sub>s</sub>        | Setup time for serial data line (SDA) data to SCL | 0.25    | —      | 0.1  | —    | μs   |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0       | 3.45   | 0    | 0.9  | μs   |

| T <sub>d</sub>        | SCL to SDA output data delay                      | —       | 0.2    | _    | 0.2  | μs   |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7     | _      | 0.6  | _    | μs   |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4       | —      | 0.6  | _    | μs   |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4       | —      | 0.6  | —    | μs   |

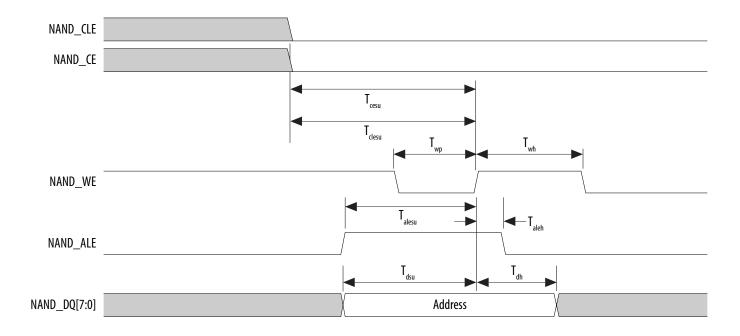

## Figure 1-18: NAND Address Latch Timing Diagram

### 1-76 FPGA JTAG Configuration Timing

| POR Delay | Minimum | Maximum | Unit |  |

|-----------|---------|---------|------|--|

| Standard  | 100     | 300     | ms   |  |

### **Related Information**

## **MSEL Pin Settings**

Provides more information about POR delay based on MSEL pin settings for each configuration scheme.

# **FPGA JTAG Configuration Timing**

## Table 1-64: FPGA JTAG Timing Parameters and Values for Arria V Devices

| Symbol                  | Description                              | Min                            | Мах                | Unit |

|-------------------------|------------------------------------------|--------------------------------|--------------------|------|

| t <sub>JCP</sub>        | TCK clock period                         | <b>30, 167</b> <sup>(92)</sup> | _                  | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14                             |                    | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14                             |                    | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2                              |                    | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3                              |                    | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5                              |                    | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |                                | 12 <sup>(93)</sup> | ns   |

| t <sub>JPZX</sub>       | JTAG port high impedance to valid output |                                | 14 <sup>(93)</sup> | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | _                              | 14 <sup>(93)</sup> | ns   |

<sup>&</sup>lt;sup>(92)</sup> The minimum TCK clock period is 167 ns if  $V_{CCBAT}$  is within the range 1.2 V – 1.5 V when you perform the volatile key programming.

<sup>&</sup>lt;sup>(93)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

### **Related Information**

- PS Configuration Timing on page 1-81

- AS Configuration Timing

Provides the AS configuration timing waveform.

# **DCLK Frequency Specification in the AS Configuration Scheme**

### Table 1-69: DCLK Frequency Specification in the AS Configuration Scheme

This table lists the internal clock frequency specification for the AS configuration scheme. The DCLK frequency specification applies when you use the internal oscillator as the configuration clock source. The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

| Parameter                                 | Minimum | Typical | Maximum | Unit |

|-------------------------------------------|---------|---------|---------|------|

|                                           | 5.3     | 7.9     | 12.5    | MHz  |

| DCLK frequency in AS configuration scheme | 10.6    | 15.7    | 25.0    | MHz  |

| Delk frequency in AS configuration scheme | 21.3    | 31.4    | 50.0    | MHz  |

|                                           | 42.6    | 62.9    | 100.0   | MHz  |

# **PS Configuration Timing**

### Table 1-70: PS Timing Parameters for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum               | Unit |

|---------------------|------------------------------|---------|-----------------------|------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | _       | 600                   | ns   |

| t <sub>CF2ST0</sub> | nCONFIG low to nSTATUS low   |         | 600                   | ns   |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       | _                     | μs   |

| t <sub>STATUS</sub> | nSTATUS low pulse width      | 268     | 1506 <sup>(103)</sup> | μs   |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high | _       | 1506(104)             | μs   |

$<sup>^{(103)}\,</sup>$  You can obtain this value if you do not delay configuration by extending the <code>nCONFIG</code> or <code>nSTATUS</code> low pulse width.

<sup>&</sup>lt;sup>(104)</sup> You can obtain this value if you do not delay configuration by externally holding nSTATUS low.

AV-51002 2017.02.10

The Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

### **Related Information**

## Arria V I/O Timing Spreadsheet

Provides the Arria V Excel-based I/O timing spreadsheet.

# Programmable IOE Delay

| Parameter <sup>(112</sup> Available |                                  | Minimum    | Fast I     | Model | Slow Model |       |       |       | Unit  |    |

|-------------------------------------|----------------------------------|------------|------------|-------|------------|-------|-------|-------|-------|----|

| ) Settings Of                       | Settings Offset <sup>(113)</sup> | Industrial | Commercial | -C4   | -C5        | -C6   | -13   | -15   | Unit  |    |

| D1                                  | 32                               | 0          | 0.508      | 0.517 | 0.870      | 1.063 | 1.063 | 0.872 | 1.057 | ns |

| D3                                  | 8                                | 0          | 1.763      | 1.795 | 2.999      | 3.496 | 3.571 | 3.031 | 3.643 | ns |

| D4                                  | 32                               | 0          | 0.508      | 0.518 | 0.869      | 1.063 | 1.063 | 1.063 | 1.057 | ns |

| D5                                  | 32                               | 0          | 0.508      | 0.517 | 0.870      | 1.063 | 1.063 | 0.872 | 1.057 | ns |

## Table 1-76: I/O element (IOE) Programmable Delay for Arria V Devices

# Programmable Output Buffer Delay

## Table 1-77: Programmable Output Buffer Delay for Arria V Devices

This table lists the delay chain settings that control the rising and falling edge delays of the output buffer.

You can set the programmable output buffer delay in the Quartus Prime software by setting the **Output Buffer Delay Control** assignment to either positive, negative, or both edges, with the specific values stated here (in ps) for the **Output Buffer Delay** assignment.

<sup>&</sup>lt;sup>(112)</sup> You can set this value in the Quartus Prime software by selecting **D1**, **D3**, **D4**, and **D5** in the **Assignment Name** column of **Assignment Editor**.

<sup>&</sup>lt;sup>(113)</sup> Minimum offset does not include the intrinsic delay.

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2012     | 2.0     | <ul> <li>Updated for the Quartus II software v12.0 release:</li> <li>Restructured document.</li> <li>Updated "Supply Current and Power Consumption" section.</li> <li>Updated Table 20, Table 21, Table 24, Table 25, Table 26, Table 35, Table 39, Table 43, and Table 52.</li> <li>Added Table 22, Table 23, and Table 33.</li> <li>Added Figure 1–1 and Figure 1–2.</li> <li>Added "Initialization" and "Configuration Files" sections.</li> </ul> |

| February 2012 | 1.3     | <ul> <li>Updated Table 2–1.</li> <li>Updated Transceiver-FPGA Fabric Interface rows in Table 2–20.</li> <li>Updated V<sub>CCP</sub> description.</li> </ul>                                                                                                                                                                                                                                                                                           |

| December 2011 | 1.2     | Updated Table 2–1 and Table 2–3.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| November 2011 | 1.1     | <ul> <li>Updated Table 2–1, Table 2–19, Table 2–26, and Table 2–36.</li> <li>Added Table 2–5.</li> <li>Added Figure 2–4.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| August 2011   | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Date         | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2015 | 2015.01.30 | Updated the description for V <sub>CC_AUX_SHARED</sub> to "HPS auxiliary power supply" in the following tables:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |            | <ul> <li>Absolute Maximum Ratings for Arria V Devices</li> <li>HPS Power Supply Operating Conditions for Arria V SX and ST Devices</li> <li>Added statement in I/O Standard Specifications: You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.</li> <li>Updated the conditions for transceiver reference clock rise time and fall time: Measure at ±60 mV of differential signal. Added a note to the conditions: REFCLKperformance requires to meet transmitter REFCLK phase noise specification.</li> <li>Updated the description in Periphery Performance Specifications to mention that proper timing closure is</li> </ul>                                                                                                                                                                                                                                                                   |

|              |            | <ul> <li>required in design.</li> <li>Updated HPS Clock Performance main_base_clk specifications from 525 MHz (for -I3 speed grade) and 462 MHz (for -C4 speed grade) to 400 MHz.</li> <li>Updated HPS PLL VCO maximum frequency to 1,600 MHz (for -C5, -I5, and -C6 speed grades), 1,850 MHz (for -C4 speed grade), and 2,100 MHz (for -I3 speed grade).</li> <li>Changed the symbol for HPS PLL input jitter divide value from NR to N.</li> <li>Removed "Slave select pulse width (Texas Instruments SSP mode)" parameter from the following tables:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                       |

|              |            | <ul> <li>SPI Master Timing Requirements for Arria V Devices</li> <li>SPI Slave Timing Requirements for Arria V Devices</li> <li>Added descriptions to USB Timing Characteristics section in HPS Specifications: PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.</li> <li>Added HPS JTAG timing specifications.</li> <li>Updated FPGA JTAG timing specifications note as follows: A 1-ns adder is required for each V<sub>CCIO</sub> voltage step down from 3.0 V. For example, t<sub>JPCO</sub> = 13 ns if V<sub>CCIO</sub> of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.</li> <li>Updated the value in the V<sub>ICM</sub> (AC Coupled) row and in note 6 from 650 mV to 750 mV in the Transceiver Specifications for Arria V GT and ST Devices table.</li> </ul> |

#### 2-4 Recommended Operating Conditions

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% of the duty cycle.

For example, a signal that overshoots to 3. V can be at 3. V for only 21% over the lifetime of the device for a device lifetime of 10 years, the overshoot duration amounts to 2 years.

| Symbol  | Description      | Condition (V) | Overshoot Duration as $\% @ T_J = 100^{\circ}C$ | Unit |

|---------|------------------|---------------|-------------------------------------------------|------|

|         |                  | 3.⊠           | 100                                             | %    |

|         |                  | 3.5           | 64                                              | %    |

|         |                  | 3.⊠           | 36                                              | %    |

|         |                  | 3.5           | 21                                              | %    |

| Vi (AC) | AC input voltage | 4             | 12                                              | %    |

|         |                  | 4.05          |                                                 | %    |

|         |                  | 4.1           | 4                                               | %    |

|         |                  | 4.15          | 2                                               | %    |

|         |                  | 4.2           | 1                                               | %    |

# **Recommended Operating Conditions**

### Table 2-5: Recommended Operating Conditions for Arria V GZ Devices

### Power supply ramps must all be strictly monotonic, without plateaus.

| Symbol          | Description                                                        | Condition | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-----------------|--------------------------------------------------------------------|-----------|--------------------------|---------|--------------------------|------|

| V <sub>CC</sub> | Core voltage and periphery circuitry power supply <sup>(115)</sup> |           | 0.2                      | 0.8     | 0.⊠                      | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements.

Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(115)</sup> The V<sub>CC</sub> core supply must be set to 0.<sup>(115)</sup> If the PartialReconfiguration (PR) feature is used.

| Symbol              | Description                                                   | Conditions                     | Resistance | Unit   |     |  |

|---------------------|---------------------------------------------------------------|--------------------------------|------------|--------|-----|--|

| Symbol              | Description Conditions                                        |                                | C3, I3L    | C4, I4 | omt |  |

| 25- R s             | Internal series termination without calibration (25- setting) | V <sub>CCIO</sub> ⊠.⊠and 1.5 V | 40         | 40     | %   |  |

| 25- R s             | Internal series termination without calibration (25- setting) | V <sub>CCIO</sub> ⊠.2 V        | 50         | 50     | %   |  |

| 50- R <sub>s</sub>  | Internal series termination without calibration (50- setting) | V <sub>CCIO</sub> ⊠.⊠and 1.5 V | 40         | 40     | %   |  |

| 50- R <sub>s</sub>  | Internal series termination without calibration (50- setting) | V <sub>CCIO</sub> ⊠.2 V        | 50         | 50     | %   |  |

| 100- R <sub>D</sub> | Internal differential termination (100-<br>setting)           | V <sub>CCIO</sub> ⊠.5 V        | 25         | 25     | %   |  |

Figure 2-1: OCT Variation Without Re-Calibration for Arria V GZ Devices

$$\mathbf{R}_{\mathsf{OCT}} = \mathbf{R}_{\mathsf{SCAL}} \left( 1 + \left( \frac{dR}{dT} \times \bigtriangleup T \right) \pm \left( \frac{dR}{dV} \times \bigtriangleup V \right) \right)$$

Notes:

1. The R<sub>oct</sub> value shows the range of OCT resistance with the variation of temperature and V<sub>cclo</sub>. 2. R<sub>scAL</sub> is the OCT resistance value at power-up. 3.  $\Delta$ T is the variation of temperature with respect to the temperature at power-up. 4.  $\Delta$ V is the variation of voltage with respect to the V<sub>cclo</sub> at power-up. 5. dR/dT is the percentage change of R<sub>scAL</sub> with temperature. 6. dR/dV is the percentage change of R<sub>scAL</sub> with voltage.

### Table 2-12: OCT Variation after Power-Up Calibration for Arria V GZ Devices

Valid for a V<sub>CCIO</sub> range of 5% and a temperature range of 0 to SC.

### 2-70 Remote System Upgrades Circuitry Timing Speci cation

### Table 2-62: Uncompressed .rbf Sizes for Arria V GZ Devices

| Variant    | Member Code Conguration.rbf Size (bits) |       | IOCSR .rbf Size (bits) (223) |  |

|------------|-----------------------------------------|-------|------------------------------|--|

|            | E1                                      | 13,55 | 562,20🛛                      |  |

| Arria V GZ | E3                                      | 13,55 | 562,20🛛                      |  |

|            | E5                                      | 213,  | 561,80                       |  |

|            | EX                                      | 213,  | 561,80                       |  |

## Table 2-63: Minimum Con gurationTime Estimation for Arria V GZ Devices

|            |             | Active Serial <sup>(224)</sup> |            |                        | Fast Passive Parallel <sup>(225)</sup> |            |                       |

|------------|-------------|--------------------------------|------------|------------------------|----------------------------------------|------------|-----------------------|

| Variant    | Member Code | Width                          | DCLK (MHz) | Min Con g Time<br>(ms) | Width                                  | DCLK (MHz) | Min Cong Time<br>(ms) |

| Arria V GZ | E1          | 4                              | 100        | 344                    | 32                                     | 100        | 43                    |

|            | E3          | 4                              | 100        | 344                    | 32                                     | 100        | 43                    |

|            | E5          | 4                              | 100        | 534                    | 32                                     | 100        | 6⊠                    |

|            | EX          | 4                              | 100        | 534                    | 32                                     | 100        | 6⊠                    |

# Remote System Upgrades Circuitry Timing Speci cation

## Table 2-64: Remote System Upgrade Circuitry Timing Speci cations

| Parameter                    | Minimum | Maximum | Unit |

|------------------------------|---------|---------|------|

| t <sub>RUNCONFIG</sub> (226) | 250     |         | ns   |

| t <sub>RUMRSTIMER</sub> (22) | 250     |         | ns   |

<sup>(223)</sup> The IOCSR rbf size is specifically for the Configuration via Protocol (CvP) feature.

<sup>(224)</sup> DCLK frequency of 100 MHz using elernal CLKUSR.

<sup>(225)</sup> MaxPGA FPP bandwidth may exeed bandwidth available from some exernal storage or control logic.