Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Product StatusObsoleteNumber of LABs/CLBs17110Number of Logic Elements/Cells362000Total RAM Bits19822592Number of I/O384Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface MountOperating Temperature-40°C ~ 100°C (TJ) |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of Logic Elements/Cells362000Total RAM Bits19822592Number of I/O384Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface Mount                                                                                      |  |

| Total RAM Bits19822592Number of I/O384Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface Mount                                                                                                                          |  |

| Number of I/O384Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface Mount                                                                                                                                                |  |

| Number of Gates-Voltage - Supply1.07V ~ 1.13VMounting TypeSurface Mount                                                                                                                                                                |  |

| Voltage - Supply1.07V ~ 1.13VMounting TypeSurface Mount                                                                                                                                                                                |  |

| Mounting Type     Surface Mount                                                                                                                                                                                                        |  |

|                                                                                                                                                                                                                                        |  |

| Operating Temperature $-40^{\circ}C \sim 100^{\circ}C (TJ)$                                                                                                                                                                            |  |

|                                                                                                                                                                                                                                        |  |

| Package / Case 896-BBGA, FCBGA                                                                                                                                                                                                         |  |

| Supplier Device Package896-FBGA (31x31)                                                                                                                                                                                                |  |

| Purchase URL https://www.e-xfl.com/product-detail/intel/5agxbb3d4f31i5n                                                                                                                                                                |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

AV-51002 2017.02.10

| Symbol                               | Description                                                  | Condition             | Minimum <sup>(7)</sup> | Typical | Maximum <sup>(7)</sup>                                                                                                                                                                                         | Unit |

|--------------------------------------|--------------------------------------------------------------|-----------------------|------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                      | HPS I/O                                                      | 3.3 V                 | 3.135                  | 3.3     | 3.465                                                                                                                                                                                                          | V    |

| V <sub>CCPD_HPS</sub> <sup>(8)</sup> | pre-driver<br>power                                          | 3.0 V                 | 2.85                   | 3.0     | 3.15                                                                                                                                                                                                           | V    |

| V <sub>CCPD_HPS</sub> <sup>(8)</sup> | supply                                                       | 2.5 V                 | 2.375                  | 2.5     | 2.625                                                                                                                                                                                                          | V    |

|                                      |                                                              | 3.3 V                 | 3.135                  | 3.3     | 3.465                                                                                                                                                                                                          | V    |

|                                      |                                                              | 3.0 V                 | 2.85                   | 3.0     | 3.15                                                                                                                                                                                                           | V    |

|                                      | HPS I/O                                                      | 2.5 V                 | 2.375                  | 2.5     | 2.625                                                                                                                                                                                                          | V    |

| V <sub>CCIO_HPS</sub>                | buffers<br>power                                             | 1.8 V                 | 1.71                   | 1.8     | 1.89                                                                                                                                                                                                           | V    |

|                                      | supply                                                       | 1.5 V                 | 1.425                  | 1.5     | 1.575                                                                                                                                                                                                          | V    |

|                                      |                                                              | 1.35 V <sup>(9)</sup> | 1.283                  | 1.35    | 1.418                                                                                                                                                                                                          | V    |

|                                      |                                                              | 1.2 V                 | 1.14                   | 1.2     | 1.26                                                                                                                                                                                                           | V    |

|                                      | HPS reset                                                    | 3.3 V                 | 3.135                  | 3.3     | 3.465                                                                                                                                                                                                          | V    |

| X7                                   | and clock                                                    | 3.0 V                 | 2.85                   | 3.0     | 3.15                                                                                                                                                                                                           | V    |

| V <sub>CCRSTCLK_HPS</sub>            | input pins<br>power                                          | 2.5 V                 | 2.375                  | 2.5     | 2.625                                                                                                                                                                                                          | V    |

|                                      | supply                                                       | 1.8 V                 | 1.71                   | 1.8     | 3.15       V         2.625       V         3.465       V         3.15       V         2.625       V         1.89       V         1.575       V         1.418       V         1.26       V         3.15       V | V    |

| V <sub>CCPLL_HPS</sub>               | HPS PLL<br>analog<br>voltage<br>regulator<br>power<br>supply | _                     | 2.375                  | 2.5     | 2.625                                                                                                                                                                                                          | V    |

<sup>&</sup>lt;sup>(7)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(8)</sup> V<sub>CCPD\_HPS</sub> must be 2.5 V when V<sub>CCIO\_HPS</sub> is 2.5, 1.8, 1.5, or 1.2 V. V<sub>CCPD\_HPS</sub> must be 3.0 V when V<sub>CCIO\_HPS</sub> is 3.0 V. V<sub>CCPD\_HPS</sub> must be 3.3 V when V<sub>CCIO\_HPS</sub> is 3.3 V.

$<sup>^{(9)}</sup>$  V<sub>CCIO\_HPS</sub> 1.35 V is supported for HPS row I/O bank only.

| I/O Standard                       | V <sub>CCIO</sub> (V)                                                                                                                                                            |     | )     |     | $V_{ID} (mV)^{(16)}$ $V_{ICM(DC)} (V)$ $V_{C}$ |     | / <sub>OD</sub> (V) <sup>(17</sup> |                                 | ١     | V <sub>OCM</sub> (V) <sup>(</sup> | 17)(18) |     |       |      |       |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------------------------------------------------|-----|------------------------------------|---------------------------------|-------|-----------------------------------|---------|-----|-------|------|-------|

| I/O Standard                       | Min                                                                                                                                                                              | Тур | Мах   | Min | Condition                                      | Мах | Min                                | Condition                       | Мах   | Min                               | Тур     | Max | Min   | Тур  | Max   |

| PCML                               | reference clock I/O pin specifications, refer to Transceiver Specifications for Arria V GX and SX Devices and Transceiver Specification<br>for Arria V GT and ST Devices tables. |     |       |     |                                                |     |                                    |                                 |       |                                   |         |     |       |      |       |

| 2.5 V                              | 2.375                                                                                                                                                                            | 2.5 | 2.625 | 100 | V <sub>CM</sub> =                              |     | 0.05                               | D <sub>MAX</sub> ≤<br>1.25 Gbps | 1.80  | 0.247                             |         | 0.6 | 1.125 | 1.25 | 1.375 |

| LVDS <sup>(19)</sup>               | 2.375                                                                                                                                                                            | 2.3 | 2.023 | 100 | 1.25 V                                         |     | 1.05                               | D <sub>MAX</sub> ><br>1.25 Gbps | 1.55  | 0.247                             |         | 0.0 | 1.125 | 1.25 | 1.575 |

| RSDS<br>(HIO) <sup>(20)</sup>      | 2.375                                                                                                                                                                            | 2.5 | 2.625 | 100 | V <sub>CM</sub> =<br>1.25 V                    |     | 0.25                               |                                 | 1.45  | 0.1                               | 0.2     | 0.6 | 0.5   | 1.2  | 1.4   |

| Mini-LVDS<br>(HIO) <sup>(21)</sup> | 2.375                                                                                                                                                                            | 2.5 | 2.625 | 200 |                                                | 600 | 0.300                              |                                 | 1.425 | 0.25                              | _       | 0.6 | 1     | 1.2  | 1.4   |

| LVPECL <sup>(22)</sup>             |                                                                                                                                                                                  |     |       | 200 |                                                |     | 0.60                               | D <sub>MAX</sub> ≤<br>700 Mbps  | 1.80  |                                   |         |     |       |      |       |

|                                    |                                                                                                                                                                                  | _   |       | 300 |                                                |     | 1.00                               | D <sub>MAX</sub> ><br>700 Mbps  | 1.60  |                                   | _       |     |       |      |       |

#### **Related Information**

- Transceiver Specifications for Arria V GX and SX Devices on page 1-23 Provides the specifications for transmitter, receiver, and reference clock I/O pin.

- $^{(16)}$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

- <sup>(17)</sup>  $R_{\rm L}$  range:  $90 \le R_{\rm L} \le 110 \ \Omega$ .

- <sup>(18)</sup> This applies to default pre-emphasis setting only.

- <sup>(19)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rates above 1.25 Gbps and 0 V to 1.85 V for data rates below 1.25 Gbps.

- <sup>(20)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

- <sup>(21)</sup> For optimized Mini-LVDS receiver performance, the receiver voltage input range must be within 0.3 V to 1.425 V.

- <sup>(22)</sup> For optimized LVPECL receiver performance, the receiver voltage input range must be within 0.85 V to 1.75 V for data rates above 700 Mbps and 0.45 V to 1.95 V for data rates below 700 Mbps.

#### Table 1-21: Transceiver Clocks Specifications for Arria V GX and SX Devices

| Symbol/Description                                                                | Condition            | Transceiver Speed Grade 4 |     |     | Transceiver Speed Grade 6 |     |     | Unit |

|-----------------------------------------------------------------------------------|----------------------|---------------------------|-----|-----|---------------------------|-----|-----|------|

| Symbol/Description                                                                | Condition            | Min                       | Тур | Мах | Min                       | Тур | Max |      |

| fixedclk clock frequency                                                          | PCIe Receiver Detect | —                         | 125 | —   | —                         | 125 | _   | MHz  |

| Transceiver Reconfigura-<br>tion Controller IP (mgmt_<br>clk_clk) clock frequency | _                    | 75                        | _   | 125 | 75                        | _   | 125 | MHz  |

## Table 1-22: Receiver Specifications for Arria V GX and SX Devices

| Sumbol/Doccription                                                                                              | Condition | Transceiver Speed Grade 4 |             |             | Transceiver Speed Grade 6 |        |      | Unit |

|-----------------------------------------------------------------------------------------------------------------|-----------|---------------------------|-------------|-------------|---------------------------|--------|------|------|

| Symbol/Description                                                                                              | Condition | Min                       | Тур         | Max         | Min                       | Тур    | Max  | Onit |

| Supported I/O standards                                                                                         |           | ]                         | 1.5 V PCML, | 2.5 V PCML, | LVPECL, an                | d LVDS |      |      |

| Data rate <sup>(28)</sup>                                                                                       | _         | 611                       | _           | 6553.6      | 611                       | _      | 3125 | Mbps |

| Absolute $V_{MAX}$ for a receiver pin <sup>(29)</sup>                                                           | _         |                           | _           | 1.2         | _                         | _      | 1.2  | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                                    | _         | -0.4                      | _           | _           | -0.4                      | _      | _    | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) before device<br>configuration | _         |                           |             | 1.6         |                           |        | 1.6  | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) after device<br>configuration  | _         |                           |             | 2.2         |                           |        | 2.2  | V    |

<sup>&</sup>lt;sup>(28)</sup> To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>(29)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

AV-51002 2017.02.10

| Symbol/Description                            | Condition                                                        | Transceiver Speed Grade 4 |                                |                                                                | Transceiver Speed Grade 6 |                           |                     | Unit |

|-----------------------------------------------|------------------------------------------------------------------|---------------------------|--------------------------------|----------------------------------------------------------------|---------------------------|---------------------------|---------------------|------|

| Symbol/Description                            | Condition                                                        | Min                       | Тур                            | Max                                                            | Min                       | Тур                       | Max                 | Onic |

| Run length                                    | —                                                                | —                         | _                              | 200                                                            | _                         | _                         | 200                 | UI   |

| Programmable equaliza-<br>tion AC and DC gain | AC gain setting = 0 to<br>$3^{(38)}$<br>DC gain setting = 0 to 1 | Gain and<br>Response      | l DC Gain for<br>at Data Rates | se at Data Rat<br>Arria V GX,<br>s ≤ 3.25 Gbps<br>V GX, GT, S2 | GT, SX, and across Supp   | ST Devices a orted AC Gai | nd CTLE<br>n and DC | dB   |

#### Table 1-23: Transmitter Specifications for Arria V GX and SX Devices

| Symbol/Description                                                 | Condition                                                | Transceiver Speed Grade 4 |     |          | Transceiver Speed Grade 6 |     |      | Unit |

|--------------------------------------------------------------------|----------------------------------------------------------|---------------------------|-----|----------|---------------------------|-----|------|------|

| Symbol/Description                                                 | Condition                                                | Min                       | Тур | Max      | Min                       | Тур | Max  | onic |

| Supported I/O standards                                            |                                                          |                           |     | 1.5 V PC | ML                        |     |      |      |

| Data rate                                                          | _                                                        | 611                       | _   | 6553.6   | 611                       |     | 3125 | Mbps |

| V <sub>OCM</sub> (AC coupled)                                      |                                                          |                           | 650 | _        |                           | 650 |      | mV   |

| V <sub>OCM</sub> (DC coupled)                                      | $\leq$ 3.2Gbps <sup>(32)</sup>                           | 670                       | 700 | 730      | 670                       | 700 | 730  | mV   |

|                                                                    | 85- $\Omega$ setting                                     | —                         | 85  | _        |                           | 85  |      | Ω    |

| Differential on-chip                                               | 100- $\Omega$ setting                                    | —                         | 100 | _        |                           | 100 |      | Ω    |

| termination resistors                                              | 120- $\Omega$ setting                                    | —                         | 120 | _        |                           | 120 |      | Ω    |

|                                                                    | 150-Ω setting                                            | —                         | 150 | _        |                           | 150 |      | Ω    |

| Intra-differential pair skew                                       | TX $V_{CM}$ = 0.65 V (AC coupled) and slew rate of 15 ps |                           | _   | 15       |                           |     | 15   | ps   |

| Intra-transceiver block<br>transmitter channel-to-<br>channel skew | ×6 PMA bonded mode                                       |                           |     | 180      |                           |     | 180  | ps   |

<sup>(37)</sup> The rate match FIFO supports only up to ±300 parts per million (ppm).

<sup>(38)</sup> The Quartus Prime software allows AC gain setting = 3 for design with data rate between 611 Mbps and 1.25 Gbps only.

| Symbol/Description                                                          | Condition                                                   | Tran | sceiver Speed Gra | de 3 | Unit |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------|------|-------------------|------|------|--|

| Symbol/Description                                                          | Condition                                                   | Min  | Тур               | Max  | Ont  |  |

|                                                                             | 85-Ω setting                                                | —    | 85                | —    | Ω    |  |

| Differential on-chip termination resistors                                  | 100- $\Omega$ setting                                       |      | 100               |      | Ω    |  |

|                                                                             | 120-Ω setting                                               | —    | 120               |      | Ω    |  |

|                                                                             | 150-Ω setting                                               |      | 150               |      | Ω    |  |

| Intra-differential pair skew                                                | TX $V_{CM}$ = 0.65 V (AC coupled)<br>and slew rate of 15 ps |      |                   | 15   | ps   |  |

| Intra-transceiver block transmitter channel-to-channel skew                 | ×6 PMA bonded mode                                          |      |                   | 180  | ps   |  |

| Inter-transceiver block transmitter channel-to-channel skew <sup>(55)</sup> | × <i>N</i> PMA bonded mode                                  |      |                   | 500  | ps   |  |

## Table 1-30: CMU PLL Specifications for Arria V GT and ST Devices

| Symbol/Description        | Transceiver S | peed Grade 3 | Unit |

|---------------------------|---------------|--------------|------|

| Symbol/Description        | Min           | Max          | Onit |

| Supported data range      | 0.611         | 10.3125      | Gbps |

| fPLL supported data range | 611           | 3125         | Mbps |

<sup>(55)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

For example, when  $V_{OD}$  = 800 mV, the corresponding  $V_{OD}$  value setting is 40. The following conditions show that the 1st post tap pre-emphasis setting = 2 is valid:

- $|B| + |C| \le 60 \Rightarrow 40 + 2 = 42$ ٠

- $|B| |C| > 5 \rightarrow 40 2 = 38$

- $(V_{MAX}/V_{MIN} 1)\% < 600\% \Rightarrow (42/38 1)\% = 10.52\%$

To predict the pre-emphasis level for your specific data rate and pattern, run simulations using the Arria V HSSI HSPICE models.

#### Table 1-33: Transmitter Pre-Emphasis Levels for Arria V Devices

| Quartus Prime 1st                 |             |             | Quar        | tus Prime V <sub>OD</sub> Se | etting      |             |              |      |

|-----------------------------------|-------------|-------------|-------------|------------------------------|-------------|-------------|--------------|------|

| Post Tap Pre-<br>Emphasis Setting | 10 (200 mV) | 20 (400 mV) | 30 (600 mV) | 35 (700 mV)                  | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) | Unit |

| 0                                 | 0           | 0           | 0           | 0                            | 0           | 0           | 0            | dB   |

| 1                                 | 1.97        | 0.88        | 0.43        | 0.32                         | 0.24        | 0.19        | 0.13         | dB   |

| 2                                 | 3.58        | 1.67        | 0.95        | 0.76                         | 0.61        | 0.5         | 0.41         | dB   |

| 3                                 | 5.35        | 2.48        | 1.49        | 1.2                          | 1           | 0.83        | 0.69         | dB   |

| 4                                 | 7.27        | 3.31        | 2           | 1.63                         | 1.36        | 1.14        | 0.96         | dB   |

| 5                                 | _           | 4.19        | 2.55        | 2.1                          | 1.76        | 1.49        | 1.26         | dB   |

| 6                                 | _           | 5.08        | 3.11        | 2.56                         | 2.17        | 1.83        | 1.56         | dB   |

| 7                                 | _           | 5.99        | 3.71        | 3.06                         | 2.58        | 2.18        | 1.87         | dB   |

| 8                                 | _           | 6.92        | 4.22        | 3.47                         | 2.93        | 2.48        | 2.11         | dB   |

| 9                                 | _           | 7.92        | 4.86        | 4                            | 3.38        | 2.87        | 2.46         | dB   |

| 10                                | _           | 9.04        | 5.46        | 4.51                         | 3.79        | 3.23        | 2.77         | dB   |

| 11                                | _           | 10.2        | 6.09        | 5.01                         | 4.23        | 3.61        | —            | dB   |

| 12                                | _           | 11.56       | 6.74        | 5.51                         | 4.68        | 3.97        | —            | dB   |

| 13                                | _           | 12.9        | 7.44        | 6.1                          | 5.12        | 4.36        | —            | dB   |

| 14                                | _           | 14.44       | 8.12        | 6.64                         | 5.57        | 4.76        | _            | dB   |

| 15                                | _           | _           | 8.87        | 7.21                         | 6.06        | 5.14        | —            | dB   |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

| 1-44 | PLL Specifications |

|------|--------------------|

|------|--------------------|

| Symbol                           | Parameter                                                           | Condition                                              | Min                 | Тур | Max                 | Unit |

|----------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|---------------------|-----|---------------------|------|

|                                  |                                                                     | -3 speed grade                                         | 5                   | _   | 800 <sup>(61)</sup> | MHz  |

| f <sub>IN</sub>                  | Input clock frequency                                               | -4 speed grade                                         | 5                   | _   | 800 <sup>(61)</sup> | MHz  |

| IIN                              | input clock frequency                                               | -5 speed grade                                         | 5                   | _   | 750 <sup>(61)</sup> | MHz  |

|                                  |                                                                     | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ | 625 <sup>(61)</sup> | MHz |                     |      |

| f <sub>INPFD</sub>               | Integer input clock frequency to the phase frequency detector (PFD) |                                                        | 5                   | _   | 325                 | MHz  |

| f <sub>FINPFD</sub>              | Fractional input clock frequency to the PFD                         | _                                                      | 50                  | _   | 160                 | MHz  |

|                                  |                                                                     | -3 speed grade                                         | 600                 | _   | 1600                | MHz  |

| f <sub>VCO</sub> <sup>(62)</sup> | PLL voltage-controlled oscillator                                   | -4 speed grade                                         | 600                 | _   | 1600                | MHz  |

| IVCO                             | (VCO) operating range                                               | -5 speed grade                                         | 600                 | _   | 1600                | MHz  |

|                                  |                                                                     | -6 speed grade                                         | 600                 | _   | 1300                | MHz  |

| t <sub>EINDUTY</sub>             | Input clock or external feedback clock input duty cycle             | _                                                      | 40                  | _   | 60                  | %    |

|                                  |                                                                     | -3 speed grade                                         | _                   | _   | 500 <sup>(63)</sup> | MHz  |

| f                                | Output frequency for internal global or                             | -4 speed grade                                         | _                   | _   | 500 <sup>(63)</sup> | MHz  |

| f <sub>OUT</sub>                 | regional clock                                                      | -5 speed grade                                         | _                   | -   | 500 <sup>(63)</sup> | MHz  |

|                                  |                                                                     | -6 speed grade                                         | _                   | _   | 400 <sup>(63)</sup> | MHz  |

<sup>&</sup>lt;sup>(61)</sup> This specification is limited in the Quartus Prime software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

<sup>&</sup>lt;sup>(62)</sup> The VCO frequency reported by the Quartus Prime software takes into consideration the VCO post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the  $f_{VCO}$  specification.

<sup>&</sup>lt;sup>(63)</sup> This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $F_{OUT}$  of the PLL.

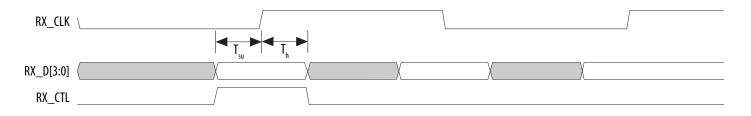

#### Table 1-57: RGMII RX Timing Requirements for Arria V Devices

| Symbol                        | Description            | Min | Тур | Unit |

|-------------------------------|------------------------|-----|-----|------|

| T <sub>clk</sub> (1000Base-T) | RX_CLK clock period    |     | 8   | ns   |

| T <sub>clk</sub> (100Base-T)  | RX_CLK clock period    |     | 40  | ns   |

| T <sub>clk</sub> (10Base-T)   | RX_CLK clock period    |     | 400 | ns   |

| T <sub>su</sub>               | RX_D/RX_CTL setup time | 1   |     | ns   |

| T <sub>h</sub>                | RX_D/RX_CTL hold time  | 1   | —   | ns   |

# Figure 1-14: RGMII RX Timing Diagram

#### Table 1-58: Management Data Input/Output (MDIO) Timing Requirements for Arria V Devices

| Symbol           | Description                   | Min | Тур | Мах | Unit |

|------------------|-------------------------------|-----|-----|-----|------|

| T <sub>clk</sub> | MDC clock period              | _   | 400 | _   | ns   |

| T <sub>d</sub>   | MDC to MDIO output data delay | 10  |     | 20  | ns   |

| T <sub>s</sub>   | Setup time for MDIO data      | 10  |     | _   | ns   |

| T <sub>h</sub>   | Hold time for MDIO data       | 0   | _   |     | ns   |

# **FPP Configuration Timing**

#### DCLK-to-DATA[] Ratio (r) for FPP Configuration

Fast passive parallel (FPP) configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the DATA[] rate in byte per second (Bps) or word per second (Wps). For example, in FPP  $\times 16$  where the *r* is 2, the DCLK frequency must be 2 times the DATA[] rate in Wps.

#### Table 1-65: DCLK-to-DATA[] Ratio for Arria V Devices

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

|                      | Off        | Off         | 1                        |

| FPP (8-bit wide)     | On         | Off         | 1                        |

| rrr (o-on wide)      | Off        | On          | 2                        |

|                      | On         | On          | 2                        |

|                      | Off        | Off         | 1                        |

| FPP (16-bit wide)    | On         | Off         | 2                        |

| rrr (10-on wide)     | Off        | On          | 4                        |

|                      | On         | On          | 4                        |

## FPP Configuration Timing when DCLK-to-DATA[] = 1

When you enable decompression or the design security feature, the DCLK-to-DATA[] ratio varies for FPP ×8 and FPP ×16. For the respective DCLKto-DATA[] ratio, refer to the DCLK-to-DATA[] Ratio for Arria V Devices table.

#### Table 1-66: FPP Timing Parameters When DCLK-to-DATA[] Ratio is 1 for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum | Unit |

|---------------------|------------------------------|---------|---------|------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | _       | 600     | ns   |

| t <sub>CF2ST0</sub> | nconfig low to nstatus low   | _       | 600     | ns   |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       |         | μs   |

#### Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

AV-51002 2017.02.10

The Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

#### Arria V I/O Timing Spreadsheet

Provides the Arria V Excel-based I/O timing spreadsheet.

# Programmable IOE Delay

| Parameter <sup>(112</sup> Available | Minimum  | Fast Model              |            |            | - Unit |       |       |       |       |      |

|-------------------------------------|----------|-------------------------|------------|------------|--------|-------|-------|-------|-------|------|

| )                                   | Settings | Offset <sup>(113)</sup> | Industrial | Commercial | -C4    | -C5   | -C6   | -13   | -15   | Onit |

| D1                                  | 32       | 0                       | 0.508      | 0.517      | 0.870  | 1.063 | 1.063 | 0.872 | 1.057 | ns   |

| D3                                  | 8        | 0                       | 1.763      | 1.795      | 2.999  | 3.496 | 3.571 | 3.031 | 3.643 | ns   |

| D4                                  | 32       | 0                       | 0.508      | 0.518      | 0.869  | 1.063 | 1.063 | 1.063 | 1.057 | ns   |

| D5                                  | 32       | 0                       | 0.508      | 0.517      | 0.870  | 1.063 | 1.063 | 0.872 | 1.057 | ns   |

#### Table 1-76: I/O element (IOE) Programmable Delay for Arria V Devices

# Programmable Output Buffer Delay

#### Table 1-77: Programmable Output Buffer Delay for Arria V Devices

This table lists the delay chain settings that control the rising and falling edge delays of the output buffer.

You can set the programmable output buffer delay in the Quartus Prime software by setting the **Output Buffer Delay Control** assignment to either positive, negative, or both edges, with the specific values stated here (in ps) for the **Output Buffer Delay** assignment.

<sup>&</sup>lt;sup>(112)</sup> You can set this value in the Quartus Prime software by selecting **D1**, **D3**, **D4**, and **D5** in the **Assignment Name** column of **Assignment Editor**.

<sup>&</sup>lt;sup>(113)</sup> Minimum offset does not include the intrinsic delay.

| Symbol                                 | Description                                         | Minimum <sup>(118)</sup> | Typical | Maximum <sup>(118)</sup> | Unit |

|----------------------------------------|-----------------------------------------------------|--------------------------|---------|--------------------------|------|

|                                        |                                                     | 0.82                     | 0.85    | 0.88                     |      |

| V <sub>CCR_GXBL</sub> <sup>(121)</sup> | Receiver analog power supply (left side)            | 0.97                     | 1.0     | 1.03                     | V    |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |

|                                        |                                                     | 0.82                     | 0.85    | 0.88                     |      |

| V <sub>CCR_GXBR</sub> <sup>(121)</sup> | Receiver analog power supply (right side)           | 0.97                     | 1.0     | 1.03                     | V    |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |

|                                        |                                                     | 0.82                     | 0.85    | 0.88                     |      |

| V <sub>CCT_GXBL</sub> <sup>(121)</sup> | Transmitter analog power supply (left side)         | 0.97                     | 1.0     | 1.03                     | V    |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |

|                                        |                                                     | 0.82                     | 0.85    | 0.88                     |      |

| V <sub>CCT_GXBR</sub> <sup>(121)</sup> | Transmitter analog power supply (right side)        | 0.97                     | 1.0     | 1.03                     | V    |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |

| V <sub>CCH_GXBL</sub>                  | Transmitter output buffer power supply (left side)  | 1.425                    | 1.5     | 1.575                    | V    |

| V <sub>CCH_GXBR</sub>                  | Transmitter output buffer power supply (right side) | 1.425                    | 1.5     | 1.575                    | V    |

<sup>&</sup>lt;sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(121)</sup> This supply must be connected to 1.0 V if the transceiver is configured at a data rate > 6.5 Gbps, and to 1.05 V if configured at a data rate > 10.3 Gbps when DFE is used. For data rate up to 6.5 Gbps, you can connect this supply to 0.85 V.

| I/O Standard           |      | ۷ <sub>CCIO</sub> (۱ | /)   | V <sub>DIF</sub> | <sub>(DC)</sub> (V)        |                                  | $V_{X(AC)}(V)$        |                              | V <sub>CN</sub>           | <sub>1(DC)</sub> (V               | <b>)</b>              | ٧ <sub>נ</sub> | DIF(AC) (V)                 |

|------------------------|------|----------------------|------|------------------|----------------------------|----------------------------------|-----------------------|------------------------------|---------------------------|-----------------------------------|-----------------------|----------------|-----------------------------|

|                        | Min  | Тур                  | Max  | Min              | Max                        | Min                              | Тур                   | Max                          | Min                       | Тур                               | Max                   | Min            | Max                         |

| HSTL-12 Class<br>I, II | 1.14 | 1.2                  | 1.26 | 0.16             | V <sub>CCIO</sub><br>+ 0.3 |                                  | $0.5 \times V_{CCIO}$ |                              | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub><br>IO | $0.6 \times V_{CCIO}$ | 0.3            | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14 | 1.2                  | 1.3  | 0.26             | 0.26                       | $0.5 \times V_{\rm CCIO} - 0.12$ | $0.5 \times V_{CCIO}$ | $0.5 \times V_{CCIO} + 0.12$ | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub><br>IO | $0.6 \times V_{CCIO}$ | 0.44           | 0.44                        |

#### Table 2-21: Differential I/O Standard Specifications for Arria V GZ Devices

| I/O Standard   | Vc    | . <sub>CIO</sub> (V) <sup>(</sup> | 128)  |     | V <sub>ID</sub> (mV) <sup>(129)</sup> |     |      | V <sub>ICM(DC)</sub> (V)          |      | Vol   | <sub>D</sub> (V) <sup>(13</sup> | 0)  | V     | <sub>OCM</sub> (V) <sup>(13</sup> | 0)    |

|----------------|-------|-----------------------------------|-------|-----|---------------------------------------|-----|------|-----------------------------------|------|-------|---------------------------------|-----|-------|-----------------------------------|-------|

|                | Min   | Тур                               | Max   | Min | Condition                             | Max | Min  | Condition                         | Max  | Min   | Тур                             | Max | Min   | Тур                               | Max   |

| PCML           |       |                                   |       |     |                                       |     |      | speed transceiv<br>Transceiver Pe |      |       |                                 |     |       | nitter,                           |       |

| 2.5 V<br>LVDS  | 2.375 | 2.5                               | 2.625 | 100 | V <sub>CM</sub> =                     |     | 0.05 | D <sub>MAX</sub> ≤<br>700 Mbps    | 1.8  | 0.247 |                                 | 0.6 | 1.125 | 1.25                              | 1.375 |

| (131)          | 2.373 | 2.3                               | 2.025 | 100 | 1.25 V                                | _   | 1.05 | D <sub>MAX</sub> ><br>700 Mbps    | 1.55 | 0.247 | —                               | 0.6 | 1.125 | 1.25                              | 1.375 |

| BLVDS<br>(132) | 2.375 | 2.5                               | 2.625 | 100 |                                       |     |      |                                   |      |       |                                 |     |       |                                   |       |

<sup>&</sup>lt;sup>(128)</sup> Differential inputs are powered by VCCPD which requires 2.5 V.

<sup>&</sup>lt;sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>&</sup>lt;sup>(130)</sup> RL range:  $90 \le \text{RL} \le 110 \Omega$ .

<sup>&</sup>lt;sup>(131)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.6 V for data rates above 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

$<sup>^{(132)}</sup>$  There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

# **Switching Characteristics**

# **Transceiver Performance Specifications**

## **Reference Clock**

#### Table 2-22: Reference Clock Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                               | Conditions                    | Transc                                               | eiver Speed  | Grade 2      | Transce    | Unit       |               |             |  |  |  |

|------------------------------------------------------------------|-------------------------------|------------------------------------------------------|--------------|--------------|------------|------------|---------------|-------------|--|--|--|

| Symbol/Description                                               | Conditions                    | Min                                                  | Тур          | Max          | Min        | Тур        | Max           | Onit        |  |  |  |

| Reference Clock                                                  |                               |                                                      |              |              |            |            |               |             |  |  |  |

| Supported I/O Standards                                          | Dedicated reference clock pin | 1.2-V PCM<br>and HCSL                                | IL, 1.4-V PC | CML, 1.5-V F | CML, 2.5-V | ' PCML, Di | fferential LV | PECL, LVDS, |  |  |  |

|                                                                  | RX reference clock pin        | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |              |              |            |            |               |             |  |  |  |

| Input Reference Clock<br>Frequency<br>(CMU PLL) <sup>(137)</sup> | _                             | 40                                                   | _            | 710          | 40         | _          | 710           | MHz         |  |  |  |

| Input Reference Clock<br>Frequency<br>(ATX PLL) <sup>(137)</sup> | _                             | 100                                                  | _            | 710          | 100        | _          | 710           | MHz         |  |  |  |

<sup>(137)</sup> The input reference clock frequency options depend on the data rate and the device speed grade.

| Symbol/Description                         | Conditions                                                | Transc | eiver Speed | Grade 2 | Transce | eiver Speed   | Grade 3 | - Unit |

|--------------------------------------------|-----------------------------------------------------------|--------|-------------|---------|---------|---------------|---------|--------|

| Symbol/Description                         | Conditions                                                | Min    | Тур         | Max     | Min     | Тур           | Мах     | Unit   |

| Rise time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> | _      | _           | 400     | _       | _             | 400     | 20     |

| Fall time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> |        | _           | 400     |         |               | 400     | ps     |

| Duty cycle                                 | —                                                         | 45     | _           | 55      | 45      |               | 55      | %      |

| Spread-spectrum modulating clock frequency | PCI Express <sup>®</sup> (PCIe)                           | 30     | _           | 33      | 30      |               | 33      | kHz    |

| Spread-spectrum downspread                 | PCIe                                                      |        | 0 to        | _       | _       | 0 to          | —       | %      |

|                                            |                                                           |        | -0.5        |         |         | -0.5          |         |        |

| On-chip termination resistors              | —                                                         |        | 100         | _       |         | 100           |         | Ω      |

| Absolute V <sub>MAX</sub>                  | Dedicated reference clock pin                             |        | _           | 1.6     |         |               | 1.6     | V      |

|                                            | RX reference clock pin                                    |        | _           | 1.2     |         |               | 1.2     |        |

| Absolute V <sub>MIN</sub>                  | —                                                         | -0.4   | _           | _       | -0.4    |               |         | V      |

| Peak-to-peak differential input<br>voltage | -                                                         | 200    | -           | 1600    | 200     |               | 1600    | mV     |

| V <sub>ICM</sub> (AC coupled)              | Dedicated reference clock pin                             | 10     | 00/900/850  | (139)   | 10      | 00/900/850    | (139)   | mV     |

| · • ·                                      | RX reference clock pin                                    | 1.     | .0/0.9/0.85 | 140)    | 1.      | .0/0.9/0.85(1 | mV      |        |

| V <sub>ICM</sub> (DC coupled)              | HCSL I/O standard for<br>PCIe reference clock             | 250    | _           | 550     | 250     |               | 550     | mV     |

<sup>(138)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

(139) The reference clock common mode voltage is equal to the V<sub>CCR\_GXB</sub> power supply level.

(140) This supply follows VCCR\_GXB

# **Typical VOD Settings**

| The tolerance is +/-20% for all VOD settings ex | cept for settings 2 and below | r.                         |                         |                            |

|-------------------------------------------------|-------------------------------|----------------------------|-------------------------|----------------------------|

| Symbol                                          | V <sub>OD</sub> Setting       | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |

|                                                 | 0 (166)                       | 0                          | 32                      | 640                        |

|                                                 | 1 <sup>(166)</sup>            | 20                         | 33                      | 660                        |

|                                                 | 2(166)                        | 40                         | 34                      | 680                        |

|                                                 | 3(166)                        | 60                         | 35                      | 700                        |

|                                                 | 4 <sup>(166)</sup>            | 80                         | 36                      | 720                        |

|                                                 | 5 <sup>(166)</sup>            | 100                        | 37                      | 740                        |

|                                                 | 6                             | 120                        | 38                      | 760                        |

| $ m V_{OD}$ differential peak to peak typical   | 7                             | 140                        | 39                      | 780                        |

|                                                 | 8                             | 160                        | 40                      | 800                        |

|                                                 | 9                             | 180                        | 41                      | 820                        |

|                                                 | 10                            | 200                        | 42                      | 840                        |

|                                                 | 11                            | 220                        | 43                      | 860                        |

|                                                 | 12                            | 240                        | 44                      | 880                        |

|                                                 | 13                            | 260                        | 45                      | 900                        |

|                                                 | 14                            | 280                        | 46                      | 920                        |

<sup>(166)</sup> If TX termination resistance = 100  $\Omega$ , this VOD setting is illegal.

| Symbol                                                       | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |

|--------------------------------------------------------------|-------------------------|----------------------------|-------------------------|----------------------------|

|                                                              | 15                      | 300                        | 47                      | 940                        |

|                                                              | 16                      | 320                        | 48                      | 960                        |

|                                                              | 17                      | 340                        | 49                      | 980                        |

|                                                              | 18                      | 360                        | 50                      | 1000                       |

|                                                              | 19                      | 380                        | 51                      | 1020                       |

|                                                              | 20                      | 400                        | 52                      | 1040                       |

|                                                              | 21                      | 420                        | 53                      | 1060                       |

|                                                              | 22                      | 440                        | 54                      | 1080                       |

| $\mathrm{V}_{\mathrm{OD}}$ differential peak to peak typical | 23                      | 460                        | 55                      | 1100                       |

|                                                              | 24                      | 480                        | 56                      | 1120                       |

|                                                              | 25                      | 500                        | 57                      | 1140                       |

|                                                              | 26                      | 520                        | 58                      | 1160                       |

|                                                              | 27                      | 540                        | 59                      | 1180                       |

|                                                              | 28                      | 560                        | 60                      | 1200                       |

|                                                              | 29                      | 580                        | 61                      | 1220                       |

|                                                              | 30                      | 600                        | 62                      | 1240                       |

|                                                              | 31                      | 620                        | 63                      | 1260                       |

| Symbol             | Parameter                                                     | Min    | Тур     | Мах        | Unit |

|--------------------|---------------------------------------------------------------|--------|---------|------------|------|

| k <sub>VALUE</sub> | Numerator of Fraction                                         | 128    | 8388608 | 2147483648 | _    |

| f <sub>RES</sub>   | Resolution of VCO frequency ( $f_{INPFD} = 100 \text{ MHz}$ ) | 390625 | 5.96    | 0.023      | Hz   |

#### **Related Information**

- Duty Cycle Distortion (DCD) Specifications on page 2-56

- DLL Range Specifications on page 2-53

## **DSP Block Specifications**

## Table 2-35: DSP Block Performance Specifications for Arria V GZ Devices

| Mode                                                           | Performar | nce   |         | – Unit |  |

|----------------------------------------------------------------|-----------|-------|---------|--------|--|

| mode                                                           | C3, I3L   | C4 I4 |         |        |  |

| Modes using One DSP Block                                      |           |       |         |        |  |

| Three 9 × 9                                                    | 480       | 42    | 20      | MHz    |  |

| One 18 × 18                                                    | 480       | 420   | 400     | MHz    |  |

| Two partial $18 \times 18$ (or $16 \times 16$ )                | 480       | 420   | 420 400 |        |  |

| One 27 × 27                                                    | 400       | 350   |         | MHz    |  |

| One 36 × 18                                                    | 400       | 350   |         | MHz    |  |

| One sum of two $18 \times 18$ (One sum of two $16 \times 16$ ) | 400       | 350   |         | MHz    |  |

| One sum of square                                              | 400       | 350   |         | MHz    |  |

| One $18 \times 18$ plus $36 (a \times b) + c$                  | 400       | 350   |         | MHz    |  |

| Modes using Two DSP Blocks                                     | ·         |       |         |        |  |

| Three 18 × 18                                                  | 400       | 350   |         | MHz    |  |

| One sum of four 18 × 18                                        | 380       | 30    | MHz     |        |  |

| Number of DQS Delay Buffers | C3, I3L | C4, I4 | Unit |  |

|-----------------------------|---------|--------|------|--|

| 4                           | 120     | 128    | ps   |  |

## **Memory Output Clock Jitter Specifications**

#### Table 2-50: Memory Output Clock Jitter Specification for Arria V GZ Devices

The clock jitter specification applies to the memory output clock pins generated using differential signal-splitter and DDIO circuits clocked by a PLL output routed on a PHY, regional, or global clock network as specified. Altera recommends using PHY clock networks whenever possible.

The clock jitter specification applies to the memory output clock pins clocked by an integer PLL.

The memory output clock jitter is applicable when an input jitter of 30 ps peak-to-peak is applied with bit error rate (BER) -12, equivalent to 14 sigma.

| Clock Network     | Parameter                    | Symbol                 | C3, I3L |      | C4, I4 |      | - Unit |

|-------------------|------------------------------|------------------------|---------|------|--------|------|--------|

| Clock Network     |                              |                        | Min     | Мах  | Min    | Мах  | Onit   |

|                   | Clock period jitter          | t <sub>JIT(per)</sub>  | -55     | 55   | -55    | 55   | ps     |

| Regional          | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -110    | 110  | -110   | 110  | ps     |

| Duty cycle jitter |                              | t <sub>JIT(duty)</sub> | -82.5   | 82.5 | -82.5  | 82.5 | ps     |

|                   | Clock period jitter          | t <sub>JIT(per)</sub>  | -82.5   | 82.5 | -82.5  | 82.5 | ps     |

| Global            | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -165    | 165  | -165   | 165  | ps     |

|                   | Duty cycle jitter            | t <sub>JIT(duty)</sub> | -90     | 90   | -90    | 90   | ps     |

|                   | Clock period jitter          | t <sub>JIT(per)</sub>  | -30     | 30   | -35    | 35   | ps     |

| PHY Clock         | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -60     | 60   | -70    | 70   | ps     |

|                   | Duty cycle jitter            | t <sub>JIT(duty)</sub> | -45     | 45   | -56    | 56   | ps     |

#### Table 2-52: Worst-Case DCD on Arria V GZ I/O Pins

The DCD numbers do not cover the core clock network.

| Symbol            | C3, I3L |     | C   | Unit |     |

|-------------------|---------|-----|-----|------|-----|

| зупто             | Min     | Мах | Min | Мах  | Ont |

| Output Duty Cycle | 45      | 55  | 45  | 55   | %   |

# **Configuration Specification**

# **POR Specifications**

#### Table 2-53: Fast and Standard POR Delay Specification for Arria V GZ Devices

Select the POR delay based on the MSEL setting as described in the "Configuration Schemes for Arria V Devices" table in the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

| POR Delay | Minimum (ms) | Maximum (ms) |

|-----------|--------------|--------------|

| Fast      | 4            | 12 (202)     |

| Standard  | 100          | 300          |

**Related Information**

Configuration, Design Security, and Remote System Upgrades in Arria V Devices

**Altera Corporation**

<sup>&</sup>lt;sup>(202)</sup> The maximum pulse width of the fast POR delay is 12 ms, providing enough time for the PCIe hard IP to initialize after the POR trip.

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2016     | 2016.06.20 | <ul> <li>Changed column heading from "Value" to "Maximum" in the "Pin Capacitance for Arria V GZ Devices" table.</li> <li>Changed the minimum supported data rate range values from "1000" to "2000" in the "ATX PLL Specifications for Arria V GZ Devices" table.</li> <li>Added the supported data rates for the following output standards using true LVDS output buffer types in the "High-Speed Clock Specifications for Arria V GZ Devices" table:</li> <li>True RSDS output standard: data rates of up to 230 Mbps</li> <li>True mini-LVDS output standard: data rates of up to 340 Mbps</li> </ul> |

| December 2015 | 2015.12.16 | <ul> <li>Removed the CDR ppm tolerance specification from the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Removed transmitter rise and fall time specifications from the "Transmitter Specifications for Arria V GZ Devices" table.</li> <li>Changed the .rbf sizes in the "Uncompressed .rbf Sizes for Arria V GZ Devices" table.</li> <li>Added a footnote to the "Transmitter High-Speed I/O Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                              |

| June 2015     | 2015.06.16 | <ul> <li>Changed the conditions for the reference clock rise and fall time and added a note to the condition in the<br/>"Reference Clock Specifications for Arria V GZ Devices" table.</li> <li>Added a note to the "Minimum differential eye opening at receiver serial input pins" specification in the<br/>"Receiver Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                           |

| January 2015  | 2015.01.30 | <ul> <li>Added 240-Ω to the "OCT Calibration Accuracy Specifications for Arria V GZ Devices" table.</li> <li>Changed the CDR PPM tolerance spec in the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Added additional max data rate for fPLL in the "Fractional PLL Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                                                            |