Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 17110                                                     |

| Number of Logic Elements/Cells | 362000                                                    |

| Total RAM Bits                 | 19822592                                                  |

| Number of I/O                  | 704                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.07V ~ 1.13V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 1517-BBGA                                                 |

| Supplier Device Package        | 1517-FBGA (40x40)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxbb3d4f40i5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Caution:** Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

Table 1-1: Absolute Maximum Ratings for Arria V Devices

| Symbol                    | Description                                                                                          | Minimum | Maximum | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------|---------|---------|------|

| $V_{CC}$                  | Core voltage power supply                                                                            | -0.50   | 1.43    | V    |

| V <sub>CCP</sub>          | Periphery circuitry, PCIe® hardIP block, and transceiver physical coding sublayer (PCS) power supply | -0.50   | 1.43    | V    |

| V <sub>CCPGM</sub>        | Configuration pins power supply                                                                      | -0.50   | 3.90    | V    |

| V <sub>CC_AUX</sub>       | Auxiliary supply                                                                                     | -0.50   | 3.25    | V    |

| V <sub>CCBAT</sub>        | Battery back-up power supply for design security volatile key register                               | -0.50   | 3.90    | V    |

| V <sub>CCPD</sub>         | I/O pre-driver power supply                                                                          | -0.50   | 3.90    | V    |

| V <sub>CCIO</sub>         | I/O power supply                                                                                     | -0.50   | 3.90    | V    |

| V <sub>CCD_FPLL</sub>     | Phase-locked loop (PLL) digital power supply                                                         | -0.50   | 1.80    | V    |

| V <sub>CCA_FPLL</sub>     | PLL analog power supply                                                                              | -0.50   | 3.25    | V    |

| V <sub>CCA_GXB</sub>      | Transceiver high voltage power                                                                       | -0.50   | 3.25    | V    |

| V <sub>CCH_GXB</sub>      | Transmitter output buffer power                                                                      | -0.50   | 1.80    | V    |

| V <sub>CCR_GXB</sub>      | Receiver power                                                                                       | -0.50   | 1.50    | V    |

| V <sub>CCT_GXB</sub>      | Transmitter power                                                                                    | -0.50   | 1.50    | V    |

| V <sub>CCL_GXB</sub>      | Transceiver clock network power                                                                      | -0.50   | 1.50    | V    |

| $\overline{V_{I}}$        | DC input voltage                                                                                     | -0.50   | 3.80    | V    |

| V <sub>CC_HPS</sub>       | HPS core voltage and periphery circuitry power supply                                                | -0.50   | 1.43    | V    |

| V <sub>CCPD_HPS</sub>     | HPS I/O pre-driver power supply                                                                      | -0.50   | 3.90    | V    |

| V <sub>CCIO_HPS</sub>     | HPS I/O power supply                                                                                 | -0.50   | 3.90    | V    |

| V <sub>CCRSTCLK_HPS</sub> | HPS reset and clock input pins power supply                                                          | -0.50   | 3.90    | V    |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

| Symbol                | Description                                | Condition    | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|-----------------------|--------------------------------------------|--------------|------------------------|---------|------------------------|------|

|                       |                                            | 3.3 V        | 3.135                  | 3.3     | 3.465                  | V    |

|                       |                                            | 3.0 V        | 2.85                   | 3.0     | 3.15                   | V    |

|                       |                                            | 2.5 V        | 2.375                  | 2.5     | 2.625                  | V    |

| <b>1</b> 7            | I/O buffers power supply                   | 1.8 V        | 1.71                   | 1.8     | 1.89                   | V    |

| $V_{CCIO}$            | 1/O bullers power supply                   | 1.5 V        | 1.425                  | 1.5     | 1.575                  | V    |

|                       |                                            | 1.35 V       | 1.283                  | 1.35    | 1.418                  | V    |

|                       |                                            | 1.25 V       | 1.19                   | 1.25    | 1.31                   | V    |

|                       |                                            | 1.2 V        | 1.14                   | 1.2     | 1.26                   | V    |

| V <sub>CCD_FPLL</sub> | PLL digital voltage regulator power supply | _            | 1.425                  | 1.5     | 1.575                  | V    |

| V <sub>CCA_FPLL</sub> | PLL analog voltage regulator power supply  | _            | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>I</sub>        | DC input voltage                           | _            | -0.5                   | _       | 3.6                    | V    |

| V <sub>O</sub>        | Output voltage                             | _            | 0                      | _       | V <sub>CCIO</sub>      | V    |

| Т                     | Operating junction temperature             | Commercial   | 0                      | _       | 85                     | °C   |

| $T_{J}$               | Operating junction temperature             | Industrial   | -40                    | _       | 100                    | °C   |

| $t_{RAMP}^{(4)}$      | Power supply ramp time                     | Standard POR | 200 μs                 | _       | 100 ms                 | _    |

| 'RAMP'                | Tower supply ramp time                     | Fast POR     | 200 μs                 | _       | 4 ms                   | _    |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(1)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

This is also applicable to HPS power supply. For HPS power supply, refer to  $t_{RAMP}$  specifications for standard POR when HPS\_PORSEL = 0 and  $t_{RAMP}$  specifications for fast POR when HPS\_PORSEL = 1.

# **I/O Standard Specifications**

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Arria V devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

#### Single-Ended I/O Standards

Table 1-14: Single-Ended I/O Standards for Arria V Devices

| I/O Standard    |       | V <sub>CCIO</sub> (V) |       | V <sub>IL</sub> (V) |                        | V <sub>IH</sub>        | V <sub>IH</sub> (V)  |                        | V <sub>OH</sub> (V)          | I <sub>OL</sub> <sup>(13)</sup> | I <sub>OH</sub> <sup>(13)</sup> (mA) |

|-----------------|-------|-----------------------|-------|---------------------|------------------------|------------------------|----------------------|------------------------|------------------------------|---------------------------------|--------------------------------------|

| i/O Standard    | Min   | Тур                   | Max   | Min                 | Max                    | Min                    | Max                  | Max                    | Min                          | (mA)                            | IOH. (IIIA)                          |

| 3.3-V<br>LVTTL  | 3.135 | 3.3                   | 3.465 | -0.3                | 0.8                    | 1.7                    | 3.6                  | 0.45                   | 2.4                          | 4                               | -4                                   |

| 3.3-V<br>LVCMOS | 3.135 | 3.3                   | 3.465 | -0.3                | 0.8                    | 1.7                    | 3.6                  | 0.2                    | V <sub>CCIO</sub> - 0.2      | 2                               | -2                                   |

| 3.0-V<br>LVTTL  | 2.85  | 3                     | 3.15  | -0.3                | 0.8                    | 1.7                    | 3.6                  | 0.4                    | 2.4                          | 2                               | -2                                   |

| 3.0-V<br>LVCMOS | 2.85  | 3                     | 3.15  | -0.3                | 0.8                    | 1.7                    | 3.6                  | 0.2                    | V <sub>CCIO</sub> - 0.2      | 0.1                             | -0.1                                 |

| 3.0-V PCI       | 2.85  | 3                     | 3.15  | _                   | $0.3 \times V_{CCIO}$  | $0.5 \times V_{CCIO}$  | $V_{\rm CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{\text{CCIO}}$ | 1.5                             | -0.5                                 |

| 3.0-V<br>PCI-X  | 2.85  | 3                     | 3.15  | _                   | $0.35 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$  | $V_{\rm CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$        | 1.5                             | -0.5                                 |

| 2.5 V           | 2.375 | 2.5                   | 2.625 | -0.3                | 0.7                    | 1.7                    | 3.6                  | 0.4                    | 2                            | 1                               | -1                                   |

| 1.8 V           | 1.71  | 1.8                   | 1.89  | -0.3                | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | 0.45                   | V <sub>CCIO</sub> - 0.45     | 2                               | -2                                   |

| 1.5 V           | 1.425 | 1.5                   | 1.575 | -0.3                | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$       | 2                               | -2                                   |

| 1.2 V           | 1.14  | 1.2                   | 1.26  | -0.3                | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$       | 2                               | -2                                   |

To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification (4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

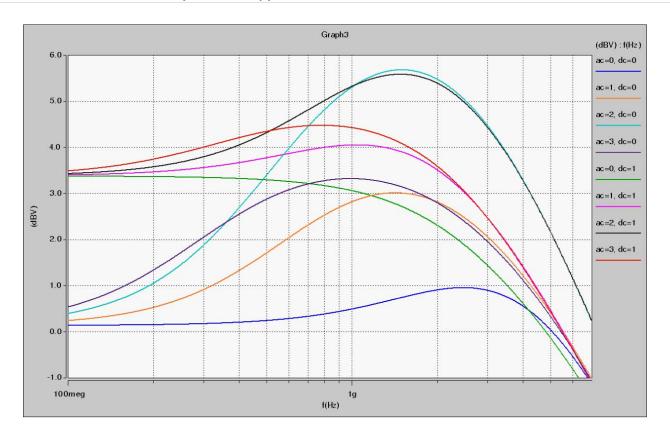

# CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain

Figure 1-3: CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

Table 1-34: Transceiver Compliance Specification for All Supported Protocol for Arria V GX, GT, SX, and ST Devices

| Protocol               | Sub-protocol | Data Rate (Mbps) |

|------------------------|--------------|------------------|

|                        | PCIe Gen1    | 2,500            |

| PCIe                   | PCIe Gen2    | 5,000            |

|                        | PCIe Cable   | 2,500            |

| XAUI                   | XAUI 2135    | 3,125            |

|                        | SRIO 1250 SR | 1,250            |

|                        | SRIO 1250 LR | 1,250            |

|                        | SRIO 2500 SR | 2,500            |

|                        | SRIO 2500 LR | 2,500            |

|                        | SRIO 3125 SR | 3,125            |

| Serial RapidIO® (SRIO) | SRIO 3125 LR | 3,125            |

| Serial Rapidio (SRIO)  | SRIO 5000 SR | 5,000            |

|                        | SRIO 5000 MR | 5,000            |

|                        | SRIO 5000 LR | 5,000            |

|                        | SRIO_6250_SR | 6,250            |

|                        | SRIO_6250_MR | 6,250            |

|                        | SRIO_6250_LR | 6,250            |

## **High-Speed I/O Specifications**

### Table 1-40: High-Speed I/O Specifications for Arria V Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block. When J = 1 or 2, bypass the SERDES block.

For LVDS applications, you must use the PLLs in integer PLL mode.

The Arria V devices support the following output standards using true LVDS output buffer types on all I/O banks.

- True RSDS output standard with data rates of up to 360 Mbps

- True mini-LVDS output standard with data rates of up to 400 Mbps

|                                                                                             | Symbol                                                                |                                                   |      | −I3, −C4 |                     |      | −I5, −C5 |                     |      | -C6 |                     | Unit  |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------|------|----------|---------------------|------|----------|---------------------|------|-----|---------------------|-------|

|                                                                                             | Зупьоі                                                                | Condition                                         | Min  | Тур      | Max                 | Min  | Тур      | Max                 | Min  | Тур | Max                 | Offic |

| f <sub>HSCLK_in</sub> (input clock frequency) True<br>Differential I/O Standards            |                                                                       | Clock boost factor W = $1 \text{ to } 40^{(72)}$  | 5    | _        | 800                 | 5    | _        | 750                 | 5    | _   | 625                 | MHz   |

| f <sub>HSCLK_in</sub> (input clock frequency)<br>Single-Ended I/O Standards <sup>(73)</sup> |                                                                       | Clock boost factor W<br>= 1 to 40 <sup>(72)</sup> | 5    | _        | 625                 | 5    | _        | 625                 | 5    | _   | 500                 | MHz   |

| f <sub>HSCLK_in</sub> (inp<br>Single-Ended                                                  | out clock frequency)<br>I/O Standards <sup>(74)</sup>                 | Clock boost factor W<br>= 1 to 40 <sup>(72)</sup> | 5    | _        | 420                 | 5    | _        | 420                 | 5    | _   | 420                 | MHz   |

| f <sub>HSCLK_OUT</sub> (d                                                                   | f <sub>HSCLK_OUT</sub> (output clock frequency)                       |                                                   | 5    | _        | 625 <sup>(75)</sup> | 5    | _        | 625 <sup>(75)</sup> | 5    | _   | 500 <sup>(75)</sup> | MHz   |

| Transmitter                                                                                 | True Differential I/O<br>Standards - f <sub>HSDR</sub> (data<br>rate) | SERDES factor $J = 3$ to $10^{(76)}$              | (77) | _        | 1250                | (77) | _        | 1250                | (77) |     | 1050                | Mbps  |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(72)</sup> Clock boost factor (W) is the ratio between the input data rate and the input clock rate.

<sup>(73)</sup> This applies to DPA and soft-CDR modes only.

<sup>(74)</sup> This applies to non-DPA mode only.

<sup>(75)</sup> This is achieved by using the LVDS clock network.

<sup>(76)</sup> The F<sub>max</sub> specification is based on the fast clock used for serial data. The interface F<sub>max</sub> is also dependent on the parallel clock domain which is design dependent and requires timing analysis.

The minimum specification depends on the clock source (for example, the PLL and clock pin) and the clock routing resource (global, regional, or local) that you use. The I/O differential buffer and input register do not have a minimum toggle rate.

|                  | Symbol                                                    | Condition                                            |      | −I3, −C4 |       | −l5, −C5 |     |       | -C6  |     |       | Unit  |

|------------------|-----------------------------------------------------------|------------------------------------------------------|------|----------|-------|----------|-----|-------|------|-----|-------|-------|

|                  | Symbol                                                    | Condition                                            | Min  | Тур      | Max   | Min      | Тур | Max   | Min  | Тур | Max   | Offic |

|                  | TCCS                                                      | True Differential I/O<br>Standards                   | _    | _        | 150   | _        | _   | 150   | _    | _   | 150   | ps    |

|                  | 1003                                                      | Emulated Differential I/O Standards                  |      | _        | 300   | _        | _   | 300   | _    | _   | 300   | ps    |

|                  | True Differential I/O<br>Standards - f <sub>HSDRDPA</sub> | SERDES factor J =3 to 10 <sup>(76)</sup>             | 150  | _        | 1250  | 150      | _   | 1250  | 150  | _   | 1050  | Mbps  |

|                  | (data rate)                                               | SERDES factor $J \ge 8$ with DPA <sup>(76)(78)</sup> | 150  | _        | 1600  | 150      | _   | 1500  | 150  | _   | 1250  | Mbps  |

| Receiver         |                                                           | SERDES factor J = 3<br>to 10                         | (77) | _        | (83)  | (77)     | _   | (83)  | (77) | _   | (83)  | Mbps  |

|                  | f <sub>HSDR</sub> (data rate)                             | SERDES factor J = 1<br>to 2, uses DDR<br>registers   | (77) | _        | (79)  | (77)     | _   | (79)  | (77) | _   | (79)  | Mbps  |

| DPA Mode         | DPA run length                                            | _                                                    | _    | _        | 10000 | _        | _   | 10000 | _    | _   | 10000 | UI    |

| Soft-CDR<br>Mode | Soft-CDR ppm tolerance                                    | _                                                    | _    | _        | 300   | _        | _   | 300   | _    | _   | 300   | ±ppm  |

| Non-DPA<br>Mode  | Sampling Window                                           | _                                                    | _    | _        | 300   | _        | _   | 300   | _    | _   | 300   | ps    |

You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

| Symbol           | Description                        | Min | Max | Unit |

|------------------|------------------------------------|-----|-----|------|

| $T_{dh}^{(89)}$  | Data to write enable hold time     | 5   | _   | ns   |

| T <sub>cea</sub> | Chip enable to data access time    | _   | 25  | ns   |

| T <sub>rea</sub> | Read enable to data access time    | _   | 16  | ns   |

| $T_{rhz}$        | Read enable to data high impedance |     | 100 | ns   |

| T <sub>rr</sub>  | Ready to read enable low           | 20  | _   | ns   |

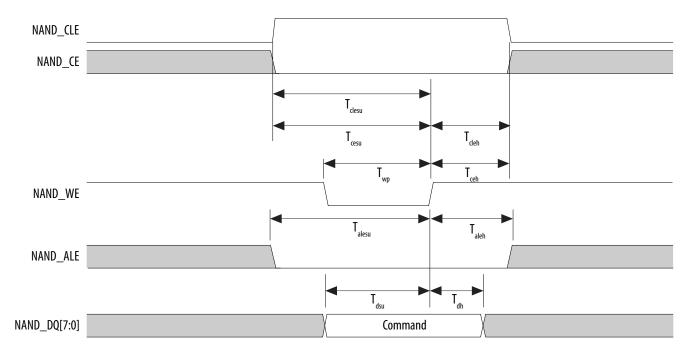

Figure 1-17: NAND Command Latch Timing Diagram

| Symbol                             | Parameter                                                 | Minimum                                       | Maximum              | Unit   |

|------------------------------------|-----------------------------------------------------------|-----------------------------------------------|----------------------|--------|

| t <sub>STATUS</sub>                | nstatus low pulse width                                   | 268                                           | 1506(94)             | μs     |

| t <sub>CF2ST1</sub>                | nconfig high to nstatus high                              | _                                             | 1506 <sup>(95)</sup> | μs     |

| t <sub>CF2CK</sub> <sup>(96)</sup> | nconfig high to first rising edge on DCLK                 | 1506                                          | _                    | μs     |

| t <sub>ST2CK</sub> <sup>(96)</sup> | nstatus high to first rising edge of DCLK                 | 2                                             | _                    | μs     |

| $t_{ m DSU}$                       | DATA[] setup time before rising edge on DCLK              | 5.5                                           | _                    | ns     |

| $t_{ m DH}$                        | DATA[] hold time after rising edge on DCLK                | 0                                             | _                    | ns     |

| t <sub>CH</sub>                    | DCLK high time                                            | $0.45 \times 1/f_{MAX}$                       | _                    | s      |

| $t_{\mathrm{CL}}$                  | DCLK low time                                             | $0.45 \times 1/f_{MAX}$                       | _                    | S      |

| t <sub>CLK</sub>                   | DCLK period                                               | 1/f <sub>MAX</sub>                            | _                    | S      |

| $f_{MAX}$                          | DCLK frequency (FPP ×8/ ×16)                              | _                                             | 125                  | MHz    |

| t <sub>CD2UM</sub>                 | CONF_DONE high to user mode <sup>(97)</sup>               | 175                                           | 437                  | μs     |

| t <sub>CD2CU</sub>                 | CONF_DONE high to CLKUSR enabled                          | 4× maximum DCLK period                        | _                    | _      |

| t <sub>CD2UMC</sub>                | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU} + (T_{init} \times CLKUSR period)$ | _                    | _      |

| $T_{init}$                         | Number of clock cycles required for device initialization | 8,576                                         | _                    | Cycles |

#### **Related Information**

### **FPP Configuration Timing**

Provides the FPP configuration timing waveforms.

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(94)</sup> You can obtain this value if you do not delay configuration by extending the nconfig or the nstatus low pulse width.

<sup>(95)</sup> You can obtain this value if you do not delay configuration by externally holding the nSTATUS low.

$<sup>^{(96)}</sup>$  If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

<sup>(97)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

| Term                 | Definition                                                                                        |

|----------------------|---------------------------------------------------------------------------------------------------|

|                      | Transmitter Output Waveforms                                                                      |

|                      | Single-Ended Waveform  Positive Channel (p) = $V_{OH}$ Negative Channel (n) = $V_{OL}$ Ground     |

|                      | Differential Waveform                                                                             |

| $f_{ m HSCLK}$       | Left/right PLL input clock frequency.                                                             |

| $f_{HSDR}$           | High-speed I/O block—Maximum/minimum LVDS data transfer rate (f <sub>HSDR</sub> =1/TUI), non-DPA. |

| f <sub>HSDRDPA</sub> | High-speed I/O block—Maximum/minimum LVDS data transfer rate (f <sub>HSDRDPA</sub> =1/TUI), DPA.  |

| J                    | High-speed I/O block—Deserialization factor (width of parallel data bus).                         |

Arria V GX, GT, SX, and ST Device Datasheet **Altera Corporation**

AV-51002 2017.02.10

| Term                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Definition                    |            |                     |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|---------------------|--|--|--|

| Single-ended voltage referenced I/O standard | The JEDEC standard for the SSTL and HSTL I/O defines both the AC and DC input signal values. The AC values indicate the voltage levels at which the receiver must meet its timing specifications. The DC values indicate the voltage levels at which the final logic state of the receiver is unambiguously defined. After the receiver input has crossed the AC value, the receiver changes to the new logic state.  The new logic state is then maintained as long as the input stays beyond the DC threshold. This approach is intended to provide predictable receiver timing in the presence of input waveform ringing.  Single-Ended Voltage Referenced I/O Standard |                               |            |                     |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |            | Vana                |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |            | V <sub>CCI0</sub>   |  |  |  |

|                                              | V <sub>0H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |            | V <sub>IH(AC)</sub> |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |            | V <sub>IH(DC)</sub> |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>REF</sub>              |            | V <sub>IL(DC)</sub> |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |            | VIL(AC)             |  |  |  |

|                                              | V <sub>0L</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |            |                     |  |  |  |

|                                              | V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |            |                     |  |  |  |

| $t_{\rm C}$                                  | High-speed receiver/transmitter input and output clock period.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |            |                     |  |  |  |

| TCCS (channel-to-channel-skew)               | The timing difference between the fastest and slowest output edges, including the $t_{CO}$ variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table).                                                                                                                                                                                                                                                                                                                                                                                                    |                               |            |                     |  |  |  |

| t <sub>DUTY</sub>                            | High-speed I/O block—Duty cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e on high-speed transmitter o | output clo | ck.                 |  |  |  |

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

| Term                       | Definition                                                                                                                                                            |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{ m FALL}$              | Signal high-to-low transition time (80–20%)                                                                                                                           |

| t <sub>INCCJ</sub>         | Cycle-to-cycle jitter tolerance on the PLL clock input                                                                                                                |

| t <sub>OUTPJ_IO</sub>      | Period jitter on the GPIO driven by a PLL                                                                                                                             |

| t <sub>OUTPJ_DC</sub>      | Period jitter on the dedicated clock output driven by a PLL                                                                                                           |

| $t_{ m RISE}$              | Signal low-to-high transition time (20–80%)                                                                                                                           |

| Timing Unit Interval (TUI) | The timing budget allowed for skew, propagation delays, and the data sampling window. (TUI = $1/(Receiver\ Input\ Clock\ Frequency\ Multiplication\ Factor) = t_C/w)$ |

| V <sub>CM(DC)</sub>        | DC common mode input voltage.                                                                                                                                         |

| V <sub>ICM</sub>           | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                 |

| $ m V_{ID}$                | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.          |

| V <sub>DIF(AC)</sub>       | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                           |

| V <sub>DIF(DC)</sub>       | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                          |

| $ m V_{IH}$                | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                 |

| V <sub>IH(AC)</sub>        | High-level AC input voltage                                                                                                                                           |

| V <sub>IH(DC)</sub>        | High-level DC input voltage                                                                                                                                           |

| $ m V_{IL}$                | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                   |

| V <sub>IL(AC)</sub>        | Low-level AC input voltage                                                                                                                                            |

| V <sub>IL(DC)</sub>        | Low-level DC input voltage                                                                                                                                            |

| V <sub>OCM</sub>           | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                             |

| V <sub>OD</sub>            | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission line at the transmitter. |

| V <sub>SWING</sub>         | Differential input voltage                                                                                                                                            |

| $V_X$                      | Input differential cross point voltage                                                                                                                                |

Arria V GX, GT, SX, and ST Device Datasheet

Altera Corporation

| Symbol           | Description                    | Minimum | Maximum | Unit |

|------------------|--------------------------------|---------|---------|------|

| $V_{I}$          | DC input voltage               | -0.5    | 3.8     | V    |

| $T_{J}$          | Operating junction temperature | -55     | 125     | °C   |

| $T_{STG}$        | Storage temperature (No bias)  | -65     | 150     | °C   |

| I <sub>OUT</sub> | DC output current per pin      | -25     | 40      | mA   |

Table 2-3: Transceiver Power Supply Absolute Conditions for Arria V GZ Devices

| Symbol                | Description                                         | Minimum | Maximum | Unit |

|-----------------------|-----------------------------------------------------|---------|---------|------|

| $V_{CCA\_GXBL}$       | Transceiver channel PLL power supply (left side)    | -0.5    | 3.75    | V    |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (right side)   | -0.5    | 3.75    | V    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left side)        | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS power supply (left side)            | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS power supply (right side)           | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBL</sub> | Receiver analog power supply (left side)            | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBR</sub> | Receiver analog power supply (right side)           | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left side)         | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBR</sub> | Transmitter analog power supply (right side)        | -0.5    | 1.35    | V    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power supply (left side)  | -0.5    | 1.8     | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power supply (right side) | -0.5    | 1.8     | V    |

# **Maximum Allowed Overshoot and Undershoot Voltage**

During transitions, input signals may overshoot to the voltage shown in the following table. They may also undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

| Mode <sup>(164)</sup> | Transceiver | PMA Width                   | 20  | 20  | 16   | 16   | 10  | 10   | 8    | 8    |

|-----------------------|-------------|-----------------------------|-----|-----|------|------|-----|------|------|------|

|                       | Speed Grade | PCS/Core Width              | 40  | 20  | 32   | 16   | 20  | 10   | 16   | 8    |

| Register              | 2           | C3, I3L<br>core speed grade | 9.9 | 9   | 7.92 | 7.2  | 4.9 | 4.,5 | 3.92 | 3.6  |

| Register              | 3           | C4, I4<br>core speed grade  | 8.8 | 8.2 | 7.04 | 6.56 | 4.4 | 4.1  | 3.52 | 3.28 |

#### **Related Information**

**Operating Conditions** on page 2-1

#### **10G PCS Data Rate**

Table 2-31: 10G PCS Approximate Maximum Data Rate (Gbps) for Arria V GZ Devices

| Mode <sup>(165)</sup> | Transceiver Speed | PMA Width                  | 64      | 40      | 40    | 40      | 32       | 32    |

|-----------------------|-------------------|----------------------------|---------|---------|-------|---------|----------|-------|

| Mode                  | Grade             | PCS Width                  | 64      | 66/67   | 50    | 40      | 64/66/67 | 32    |

| FIFO                  | 2                 | C3, I3L core speed grade   | 12.5    | 12.5    | 10.69 | 12.5    | 10.88    | 10.88 |

| rirO                  | 3                 | C4, I4 core speed<br>grade | 10.3125 | 10.3125 | 10.69 | 10.3125 | 9.92     | 9.92  |

| Dogistan              | 2                 | C3, I3L core speed grade   | 12.5    | 12.5    | 10.69 | 12.5    | 10.88    | 10.88 |

| Register              | 3                 | C4, I4 core speed<br>grade | 10.3125 | 10.3125 | 10.69 | 10.3125 | 9.92     | 9.92  |

<sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

<sup>(165)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

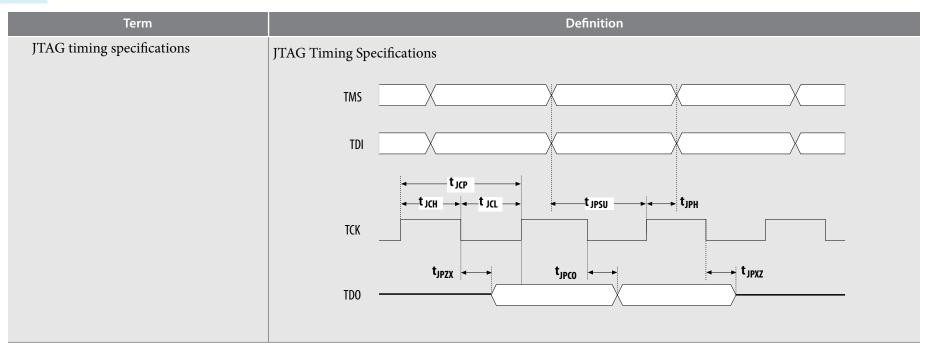

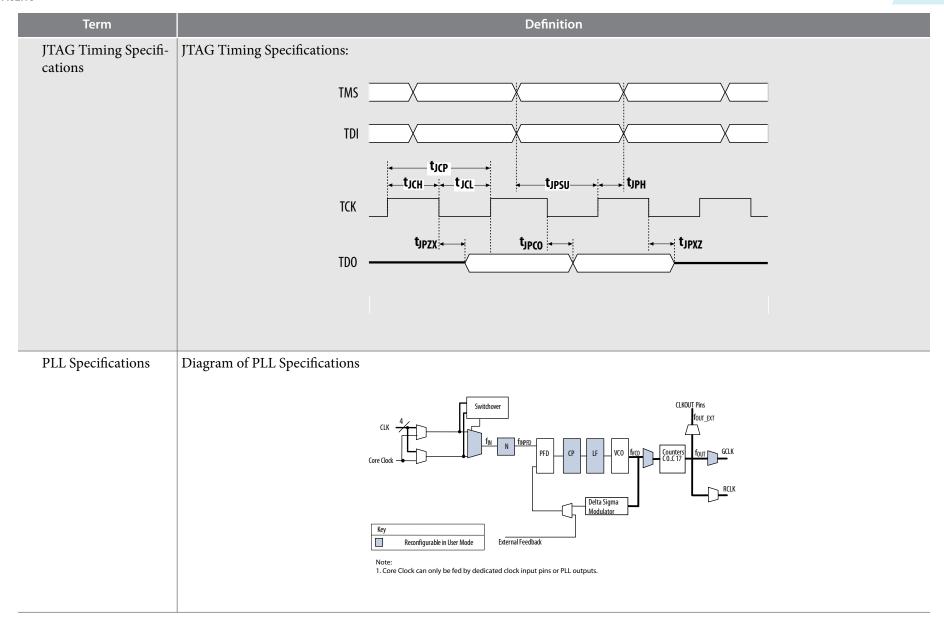

# **JTAG Configuration Specifications**

Table 2-54: JTAG Timing Parameters and Values for Arria V GZ Devices

| Symbol                  | Description                              | Min       | Max          | Unit |

|-------------------------|------------------------------------------|-----------|--------------|------|

| $t_{JCP}$               | TCK clock period                         | 30        | _            | ns   |

| $t_{JCP}$               | TCK clock period                         | 167 (203) | _            | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14        | <del>_</del> | ns   |

| $t_{ m JCL}$            | TCK clock low time                       | 14        | _            | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2         | _            | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3         | _            | ns   |

| $t_{JPH}$               | JTAG port hold time                      | 5         | _            | ns   |

| $t_{ m JPCO}$           | JTAG port clock to output                | _         | 11 (204)     | ns   |

| $t_{ m JPZX}$           | JTAG port high impedance to valid output | _         | 14 (204)     | ns   |

| $t_{JPXZ}$              | JTAG port valid output to high impedance | _         | 14 (204)     | ns   |

# **Fast Passive Parallel (FPP) Configuration Timing**

# DCLK-to-DATA[] Ratio (r) for FPP Configuration

FPP configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

<sup>(203)</sup> The minimum TCK clock period is 167 ns if VCCBAT is within the range 1.2V-1.5V when you perform the volatile key programming.

$<sup>^{(204)}</sup>$  A 1-ns adder is required for each  $V_{CCIO}$  voltage step down from 3.0 V. For example,  $t_{JPCO} = 12$  ns if  $V_{CCIO}$  of the TDO I/O bank = 2.5 V, or 13 ns if it equals 1.8 V.

| Symbol              | Parameter                                         | Minimum                                     | Maximum | Unit |

|---------------------|---------------------------------------------------|---------------------------------------------|---------|------|

| $t_{CO}$            | DCLK falling edge to AS_DATA0/ASDO output         | _                                           | 4       | ns   |

| t <sub>SU</sub>     | Data setup time before falling edge on DCLK       | 1.5                                         | _       | ns   |

| $t_{\rm H}$         | Data hold time after falling edge on DCLK         | 0                                           | _       | ns   |

| $t_{CD2UM}$         | CONF_DONE high to user mode (216)                 | 175                                         | 437     | μs   |

| $t_{\rm CD2CU}$     | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK period                     | _       | _    |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> + (8576 × CLKUSR period) | _       | _    |

### Table 2-59: DCLK Frequency Specification in the AS Configuration Scheme

This applies to the DCLK frequency specification when using the internal oscillator as the configuration clock source.

The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

| 10.6    | 15.7    | 25.0    | MHz  |

| 21.3    | 31.4    | 50.0    | MHz  |

| 42.6    | 62.9    | 100.0   | MHz  |

#### **Related Information**

- Passive Serial Configuration Timing on page 2-67

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Altera Corporation

Arria V GZ Device Datasheet

<sup>(216)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on this pin, refer to the "Initialization" section of the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

## Table 2-60: PS Timing Parameters for Arria V GZ Devices

| Symbol                   | Parameter                                         | Minimum                                                           | Maximum     | Unit |

|--------------------------|---------------------------------------------------|-------------------------------------------------------------------|-------------|------|

| t <sub>CF2CD</sub>       | nconfig low to conf_done low                      | _                                                                 | 600         | ns   |

| t <sub>CF2ST0</sub>      | nconfig low to nstatus low                        | _                                                                 | 600         | ns   |

| t <sub>CFG</sub>         | nconfig low pulse width                           | 2                                                                 | _           | μs   |

| t <sub>STATUS</sub>      | nstatus low pulse width                           | 268                                                               | 1,506 (217) | μs   |

| t <sub>CF2ST1</sub>      | nconfig high to nstatus high                      | _                                                                 | 1,506 (218) | μs   |

| t <sub>CF2CK</sub> (219) | nCONFIG high to first rising edge on DCLK         | 1,506                                                             | _           | μs   |

| t <sub>ST2CK</sub> (219) | nstatus high to first rising edge of DCLK         | 2                                                                 | _           | μs   |

| t <sub>DSU</sub>         | DATA[] setup time before rising edge on DCLK      | 5.5                                                               | _           | ns   |

| t <sub>DH</sub>          | DATA[] hold time after rising edge on DCLK        | 0                                                                 | _           | ns   |

| t <sub>CH</sub>          | DCLK high time                                    | $0.45 \times 1/f_{MAX}$                                           | _           | S    |

| $t_{\rm CL}$             | DCLK low time                                     | $0.45 \times 1/f_{MAX}$                                           | _           | S    |

| $t_{CLK}$                | DCLK period                                       | 1/f <sub>MAX</sub>                                                | _           | S    |

| $f_{MAX}$                | DCLK frequency                                    | _                                                                 | 125         | MHz  |

| t <sub>CD2UM</sub>       | CONF_DONE high to user mode (220)                 | 175                                                               | 437         | μs   |

| t <sub>CD2CU</sub>       | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK period                                           | _           | _    |

| t <sub>CD2UMC</sub>      | CONF_DONE high to user mode with CLKUSR option on | $t_{\text{CD2CU}} + (8576 \times \text{CLKUSR})$<br>period) (221) | _           | _    |

$<sup>^{(217)}</sup>$  This value is applicable if you do not delay configuration by extending the nconfig or nstatus low pulse width.

Altera Corporation

Arria V GZ Device Datasheet

<sup>(218)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>(219)</sup> If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

<sup>(220)</sup> The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

| Term                               | Definition                                                                                                                                                                                                                                                              |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\rm C}$                        | High-speed receiver and transmitter input and output clock period.                                                                                                                                                                                                      |

| TCCS (channel-to-<br>channel-skew) | The timing difference between the fastest and slowest output edges, including $t_{\rm CO}$ variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table). |

| $t_{ m DUTY}$                      | High-speed I/O block—Duty cycle on the high-speed transmitter output clock.                                                                                                                                                                                             |

| $t_{ m FALL}$                      | Signal high-to-low transition time (80-20%)                                                                                                                                                                                                                             |

| t <sub>INCCJ</sub>                 | Cycle-to-cycle jitter tolerance on the PLL clock input.                                                                                                                                                                                                                 |

| t <sub>OUTPJ_IO</sub>              | Period jitter on the general purpose I/O driven by a PLL.                                                                                                                                                                                                               |

| t <sub>OUTPJ_DC</sub>              | Period jitter on the dedicated clock output driven by a PLL.                                                                                                                                                                                                            |

| t <sub>RISE</sub>                  | Signal low-to-high transition time (20-80%)                                                                                                                                                                                                                             |

| Timing Unit Interval (TUI)         | The timing budget allowed for skew, propagation delays, and the data sampling window. $(TUI = 1/(receiver input clock frequency multiplication factor) = t_C/w)$                                                                                                        |

| V <sub>CM(DC)</sub>                | DC common mode input voltage.                                                                                                                                                                                                                                           |

| $ ule{V_{ICM}}$                    | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                                                                                                                   |

| V <sub>ID</sub>                    | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                                                                                            |

| V <sub>DIF(AC)</sub>               | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                                                                                                                             |

| V <sub>DIF(DC)</sub>               | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                                                                                                                            |

| $\overline{ m V_{IH}}$             | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                                                                                                                   |

| V <sub>IH(AC)</sub>                | High-level AC input voltage                                                                                                                                                                                                                                             |

| V <sub>IH(DC)</sub>                | High-level DC input voltage                                                                                                                                                                                                                                             |

| $ m V_{IL}$                        | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                                                                                                                     |

| V <sub>IL(AC)</sub>                | Low-level AC input voltage                                                                                                                                                                                                                                              |

| V <sub>IL(DC)</sub>                | Low-level DC input voltage                                                                                                                                                                                                                                              |