# E·XFL

### Intel - 5AGXBB5D6F40C6N Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 19811                                                      |

| Number of Logic Elements/Cells | 420000                                                     |

| Total RAM Bits                 | 23625728                                                   |

| Number of I/O                  | 704                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1517-BBGA                                                  |

| Supplier Device Package        | 1517-FBGA (40x40)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxbb5d6f40c6n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| I/O Standard        | V <sub>IL</sub> | <sub>.(DC)</sub> (V)    | V <sub>IH(D</sub>       | $V_{\text{IH(DC)}}(V)$ $V_{\text{IL(AC)}}(V)$ $V_{\text{IH(AC)}}(V)$ $V_{\text{OL}}(V)$ |                         |                         |                        | V <sub>OL</sub> (V) V <sub>OH</sub> (V) |      | I <sub>OH</sub> <sup>(14)</sup> (mA) |

|---------------------|-----------------|-------------------------|-------------------------|-----------------------------------------------------------------------------------------|-------------------------|-------------------------|------------------------|-----------------------------------------|------|--------------------------------------|

|                     | Min             | Max                     | Min                     | Max                                                                                     | Max                     | Min                     | Max                    | Min                                     | (mA) | OH (IIII)                            |

| HSTL-15<br>Class II | —               | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$         | —                                                                                       | V <sub>REF</sub> – 0.2  | $V_{REF} + 0.2$         | 0.4                    | V <sub>CCIO</sub> – 0.4                 | 16   | -16                                  |

| HSTL-12<br>Class I  | -0.15           | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15                                                                | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$                  | 8    | -8                                   |

| HSTL-12<br>Class II | -0.15           | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15                                                                | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$                  | 16   | -16                                  |

| HSUL-12             | —               | V <sub>REF</sub> - 0.13 | V <sub>REF</sub> + 0.13 | _                                                                                       | V <sub>REF</sub> – 0.22 | $V_{REF} + 0.22$        | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$                   |      | _                                    |

# **Differential SSTL I/O Standards**

Table 1-17: Differential SSTL I/O Standards for Arria V Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>SW</sub> | <sub>ING(DC)</sub> (V) | V <sub>X(AC)</sub> (V)          |                      |                                 | V <sub>SWING(AC)</sub> (V)                    |                           |  |

|------------------------|-------|-----------------------|-------|-----------------|------------------------|---------------------------------|----------------------|---------------------------------|-----------------------------------------------|---------------------------|--|

|                        | Min   | Тур                   | Max   | Min             | Мах                    | Min                             | Тур                  | Мах                             | Min                                           | Max                       |  |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                   | 2.625 | 0.3             | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 – 0.2      | _                    | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$          |  |

| SSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.25            | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 –<br>0.175 | _                    | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | $V_{CCIO} + 0.6$          |  |

| SSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.2             | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | —                    | V <sub>CCIO</sub> /2<br>+ 0.15  | $2(V_{IH(AC)} - V_{REF})$                     | $2(V_{IL(AC)} - V_{REF})$ |  |

| SSTL-135               | 1.283 | 1.35                  | 1.45  | 0.18            | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |  |

<sup>&</sup>lt;sup>(14)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

$<sup>^{(15)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

| Symbol/Description                                                          | Condition                                                   | Tran | sceiver Speed Gra | Unit |      |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------|------|-------------------|------|------|--|

| Symbol/Description                                                          | Condition                                                   | Min  | Тур               | Max  | Onit |  |

| Differential on-chip termination resistors                                  | 85-Ω setting                                                | —    | 85                | —    | Ω    |  |

|                                                                             | 100- $\Omega$ setting                                       |      | 100               |      | Ω    |  |

|                                                                             | 120-Ω setting                                               | —    | 120               | —    | Ω    |  |

|                                                                             | 150-Ω setting                                               |      | 150               |      | Ω    |  |

| Intra-differential pair skew                                                | TX $V_{CM}$ = 0.65 V (AC coupled)<br>and slew rate of 15 ps |      |                   | 15   | ps   |  |

| Intra-transceiver block transmitter channel-to-channel skew                 | ×6 PMA bonded mode                                          |      |                   | 180  | ps   |  |

| Inter-transceiver block transmitter channel-to-channel skew <sup>(55)</sup> | × <i>N</i> PMA bonded mode                                  |      |                   | 500  | ps   |  |

# Table 1-30: CMU PLL Specifications for Arria V GT and ST Devices

| Symbol/Description        | Transceiver S | peed Grade 3 | Unit |

|---------------------------|---------------|--------------|------|

| Symbol/Description        | Min           | Max          | Onit |

| Supported data range      | 0.611         | 10.3125      | Gbps |

| fPLL supported data range | 611           | 3125         | Mbps |

<sup>(55)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

| Symbol                                 | Parameter                                                                                                      | Condition                     | Min | Тур | Max                 | Unit     |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|---------------------|----------|

|                                        |                                                                                                                | -3 speed grade                | _   | _   | 670 <sup>(63)</sup> | MHz      |

| f                                      | Output frequency for external clock                                                                            | -4 speed grade                | _   | _   | 670 <sup>(63)</sup> | MHz      |

| f <sub>OUT_EXT</sub>                   | output                                                                                                         | –5 speed grade                | _   | _   | 622 <sup>(63)</sup> | MHz      |

|                                        |                                                                                                                | -6 speed grade                |     |     | 500 <sup>(63)</sup> | MHz      |

| t <sub>OUTDUTY</sub>                   | Duty cycle for external clock output<br>(when set to 50%)                                                      |                               | 45  | 50  | 55                  | %        |

| t <sub>FCOMP</sub>                     | External feedback clock compensation time                                                                      | _                             | _   | _   | 10                  | ns       |

| t <sub>DYCONFIGCLK</sub>               | Dynamic configuration clock for mgmt_<br>clk and scanclk                                                       | _                             | _   | _   | 100                 | MHz      |

| t <sub>LOCK</sub>                      | Time required to lock from end-of-<br>device configuration or deassertion of<br>areset                         | _                             | _   |     | 1                   | ms       |

| t <sub>DLOCK</sub>                     | Time required to lock dynamically<br>(after switchover or reconfiguring any<br>non-post-scale counters/delays) | _                             |     |     | 1                   | ms       |

|                                        |                                                                                                                | Low                           | _   | 0.3 | _                   | MHz      |

| f <sub>CLBW</sub>                      | PLL closed-loop bandwidth                                                                                      | Medium                        | _   | 1.5 | _                   | MHz      |

|                                        |                                                                                                                | High <sup>(64)</sup>          | _   | 4   | _                   | MHz      |

| t <sub>PLL_PSERR</sub>                 | Accuracy of PLL phase shift                                                                                    | —                             | _   | _   | ±50                 | ps       |

| t <sub>ARESET</sub>                    | Minimum pulse width on the areset signal                                                                       | _                             | 10  | _   | _                   | ns       |

| + (65)(66)                             | Input dock and to and ittar                                                                                    | $F_{REF} \ge 100 \text{ MHz}$ | _   | _   | 0.15                | UI (p-p) |

| t <sub>INCCJ</sub> <sup>(65)(66)</sup> | Input clock cycle-to-cycle jitter                                                                              | $F_{REF} < 100 \text{ MHz}$   | _   | _   | ±750                | ps (p-p) |

<sup>&</sup>lt;sup>(64)</sup> High bandwidth PLL settings are not supported in external feedback mode.

<sup>&</sup>lt;sup>(65)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps.

<sup>&</sup>lt;sup>(66)</sup>  $F_{\text{REF}}$  is  $f_{\text{IN}}/N$ , specification applies when N = 1.

|                  | Symbol                                                                               | Condition                                               |      | -I3, -C4 |       |      | –I5, –C5 |       | -C6  |     |       | Unit |

|------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------|------|----------|-------|------|----------|-------|------|-----|-------|------|

|                  | Symbol                                                                               | Condition                                               | Min  | Тур      | Max   | Min  | Тур      | Мах   | Min  | Тур | Max   | Onit |

|                  | TCCS                                                                                 | True Differential I/O<br>Standards                      | _    | _        | 150   | _    | _        | 150   | _    | _   | 150   | ps   |

|                  |                                                                                      | Emulated Differential<br>I/O Standards                  | _    | _        | 300   | _    | _        | 300   |      | _   | 300   | ps   |

|                  | True Differential I/O<br>Standards - f <sub>HSDRDPA</sub><br>(data rate)<br>Receiver | SERDES factor J =3 to $10^{(76)}$                       | 150  |          | 1250  | 150  | _        | 1250  | 150  |     | 1050  | Mbps |

|                  |                                                                                      | SERDES factor $J \ge 8$<br>with DPA <sup>(76)(78)</sup> | 150  | _        | 1600  | 150  | _        | 1500  | 150  | _   | 1250  | Mbps |

| Receiver         |                                                                                      | SERDES factor J = 3<br>to 10                            | (77) | _        | (83)  | (77) | _        | (83)  | (77) | _   | (83)  | Mbps |

|                  | f <sub>HSDR</sub> (data rate)                                                        | SERDES factor J = 1<br>to 2, uses DDR<br>registers      | (77) |          | (79)  | (77) |          | (79)  | (77) |     | (79)  | Mbps |

| DPA Mode         | DPA run length                                                                       | _                                                       | —    | _        | 10000 | _    | _        | 10000 | _    | _   | 10000 | UI   |

| Soft-CDR<br>Mode | Soft-CDR ppm tolerance                                                               | _                                                       | _    | _        | 300   | _    | _        | 300   | _    | _   | 300   | ±ppm |

| Non-DPA<br>Mode  | Sampling Window                                                                      | _                                                       |      | _        | 300   | _    | _        | 300   |      | _   | 300   | ps   |

Arria V GX, GT, SX, and ST Device Datasheet

<sup>&</sup>lt;sup>(83)</sup> You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

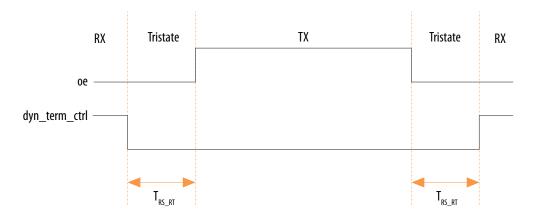

### Figure 1-7: Timing Diagram for oe and dyn\_term\_ctrl Signals

# **Duty Cycle Distortion (DCD) Specifications**

### Table 1-47: Worst-Case DCD on Arria V I/O Pins

The output DCD cycle only applies to the I/O buffer. It does not cover the system DCD.

| Symbol            | –I3, | -C4 | -C5, -I5 |     | -C6 |     | Unit |  |

|-------------------|------|-----|----------|-----|-----|-----|------|--|

|                   | Min  | Мах | Min      | Мах | Min | Мах | Onit |  |

| Output Duty Cycle | 45   | 55  | 45       | 55  | 45  | 55  | %    |  |

# **HPS Specifications**

This section provides HPS specifications and timing for Arria V devices.

For HPS reset, the minimum reset pulse widths for the HPS cold and warm reset signals (HPS\_nRST and HPS\_nPOR) are six clock cycles of HPS\_CLK1.

### **HPS PLL Input Jitter**

Use the following equation to determine the maximum input jitter (peak-to-peak) the HPS PLLs can tolerate. The divide value (N) is the value programmed into the denominator field of the VCO register for each PLL. The PLL input reference clock is divided by this value. The range of the denominator is 1 to 64.

Maximum input jitter = Input clock period × Divide value (N) × 0.02

# Table 1-50: Examples of Maximum Input Jitter

| Input Reference Clock Period | Divide Value (N) | Maximum Jitter | Unit |

|------------------------------|------------------|----------------|------|

| 40 ns                        | 1                | 0.8            | ns   |

| 40 ns                        | 2                | 1.6            | ns   |

| 40 ns                        | 4                | 3.2            | ns   |

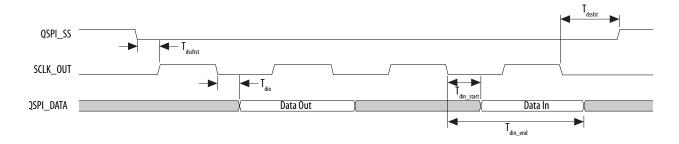

# **Quad SPI Flash Timing Characteristics**

# Table 1-51: Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Arria V Devices

| Symbol                 | Description                                        | Min  | Тур                      | Мах                                                  | Unit |

|------------------------|----------------------------------------------------|------|--------------------------|------------------------------------------------------|------|

| F <sub>clk</sub>       | SCLK_OUT clock frequency (External clock)          | —    | _                        | 108                                                  | MHz  |

| T <sub>qspi_clk</sub>  | QSPI_CLK clock period (Internal reference clock)   | 2.32 | _                        |                                                      | ns   |

| T <sub>dutycycle</sub> | SCLK_OUT duty cycle                                | 45   |                          | 55                                                   | %    |

| T <sub>dssfrst</sub>   | Output delay QSPI_SS valid before first clock edge |      | 1/2 cycle of<br>SCLK_OUT |                                                      | ns   |

| T <sub>dsslst</sub>    | Output delay QSPI_SS valid after last clock edge   | -1   |                          | 1                                                    | ns   |

| T <sub>dio</sub>       | I/O data output delay                              | -1   |                          | 1                                                    | ns   |

| T <sub>din_start</sub> | Input data valid start                             |      |                          | $(2 + R_{delay}) \times T_{qspi\_clk} - 7.52^{(85)}$ | ns   |

| Symbol               | Description          | Min                                                  | Тур | Max | Unit |

|----------------------|----------------------|------------------------------------------------------|-----|-----|------|

| T <sub>din_end</sub> | Input data valid end | $(2 + R_{delay}) \times T_{qspi\_clk} - 1.21^{(85)}$ |     | _   | ns   |

### Figure 1-8: Quad SPI Flash Timing Diagram

This timing diagram illustrates clock polarity mode 0 and clock phase mode 0.

### **Related Information**

# Quad SPI Flash Controller Chapter, Arria V Hard Processor System Technical Reference Manual

Provides more information about Rdelay.

# **SPI Timing Characteristics**

### Table 1-52: SPI Master Timing Requirements for Arria V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol           | Description                               | Min       | Max | Unit |

|------------------|-------------------------------------------|-----------|-----|------|

| T <sub>clk</sub> | CLK clock period                          | 16.67     | _   | ns   |

| T <sub>su</sub>  | SPI Master-in slave-out (MISO) setup time | 8.35 (86) | _   | ns   |

$<sup>^{(85)}</sup>$  R<sub>delay</sub> is set by programming the register <code>qspiregs.rddatacap</code>. For the SoC EDS software version 13.1 and later, Altera provides automatic Quad SPI calibration in the preloader. For more information about R<sub>delay</sub>, refer to the Quad SPI Flash Controller chapter in the Arria V Hard Processor System Technical Reference Manual.

### 1-62 SPI Timing Characteristics

| Symbol                 | Description                                       | Min | Мах | Unit |

|------------------------|---------------------------------------------------|-----|-----|------|

| T <sub>h</sub>         | SPI MISO hold time                                | 1   | _   | ns   |

| T <sub>dutycycle</sub> | SPI_CLK duty cycle                                | 45  | 55  | %    |

| T <sub>dssfrst</sub>   | Output delay SPI_SS valid before first clock edge | 8   |     | ns   |

| T <sub>dsslst</sub>    | Output delay SPI_SS valid after last clock edge   | 8   |     | ns   |

| T <sub>dio</sub>       | Master-out slave-in (MOSI) output delay           | -1  | 1   | ns   |

**Altera Corporation**

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(86)</sup> This value is based on rx\_sample\_dly = 1 and spi\_m\_clk = 120 MHz. spi\_m\_clk is the internal clock that is used by SPI Master to derive it's SCLK\_OUT. These timings are based on rx\_sample\_dly of 1. This delay can be adjusted as needed to accommodate slower response times from the slave. Note that a delay of 0 is not allowed. The setup time can be used as a reference starting point. It is very crucial to do a calibration to get the correct rx\_sample\_dly value because each SPI slave device may have different output delay and each application board may have different path delay. For more information about rx\_sample\_delay, refer to the SPI Controller chapter in the Hard Processor System Technical Reference Manual.

### 1-76 FPGA JTAG Configuration Timing

| POR Delay | Minimum | Maximum | Unit |

|-----------|---------|---------|------|

| Standard  | 100     | 300     | ms   |

### **Related Information**

### **MSEL Pin Settings**

Provides more information about POR delay based on MSEL pin settings for each configuration scheme.

# **FPGA JTAG Configuration Timing**

# Table 1-64: FPGA JTAG Timing Parameters and Values for Arria V Devices

| Symbol                  | Description                              | Min                            | Мах                | Unit |

|-------------------------|------------------------------------------|--------------------------------|--------------------|------|

| t <sub>JCP</sub>        | TCK clock period                         | <b>30, 167</b> <sup>(92)</sup> | _                  | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14                             |                    | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14                             |                    | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2                              |                    | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3                              |                    | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5                              |                    | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |                                | 12 <sup>(93)</sup> | ns   |

| t <sub>JPZX</sub>       | JTAG port high impedance to valid output |                                | 14 <sup>(93)</sup> | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | _                              | 14 <sup>(93)</sup> | ns   |

<sup>&</sup>lt;sup>(92)</sup> The minimum TCK clock period is 167 ns if  $V_{CCBAT}$  is within the range 1.2 V – 1.5 V when you perform the volatile key programming.

<sup>&</sup>lt;sup>(93)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

### **Related Information**

- PS Configuration Timing on page 1-81

- AS Configuration Timing

Provides the AS configuration timing waveform.

# **DCLK Frequency Specification in the AS Configuration Scheme**

### Table 1-69: DCLK Frequency Specification in the AS Configuration Scheme

This table lists the internal clock frequency specification for the AS configuration scheme. The DCLK frequency specification applies when you use the internal oscillator as the configuration clock source. The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

| Parameter                                  | Minimum | Typical | Maximum | Unit |

|--------------------------------------------|---------|---------|---------|------|

|                                            | 5.3     | 7.9     | 12.5    | MHz  |

| DCLK frequency in AS configuration scheme  | 10.6    | 15.7    | 25.0    | MHz  |

| Bellk frequency in AS configuration scheme | 21.3    | 31.4    | 50.0    | MHz  |

|                                            | 42.6    | 62.9    | 100.0   | MHz  |

# **PS Configuration Timing**

### Table 1-70: PS Timing Parameters for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum               | Unit |

|---------------------|------------------------------|---------|-----------------------|------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | _       | 600                   | ns   |

| t <sub>CF2ST0</sub> | nCONFIG low to nSTATUS low   |         | 600                   | ns   |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       | _                     | μs   |

| t <sub>STATUS</sub> | nSTATUS low pulse width      | 268     | 1506 <sup>(103)</sup> | μs   |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high | _       | 1506(104)             | μs   |

$<sup>^{(103)}\,</sup>$  You can obtain this value if you do not delay configuration by extending the <code>nCONFIG</code> or <code>nSTATUS</code> low pulse width.

<sup>&</sup>lt;sup>(104)</sup> You can obtain this value if you do not delay configuration by externally holding nSTATUS low.

### 1-82 PS Configuration Timing

| Symbol                              | Parameter                                                 | Minimum                                                     | Maximum | Unit   |

|-------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------|---------|--------|

| $t_{CF2CK}^{(105)}$                 | nCONFIG high to first rising edge on DCLK                 | 1506                                                        | _       | μs     |

| t <sub>ST2CK</sub> <sup>(105)</sup> | nSTATUS high to first rising edge of DCLK                 | 2                                                           |         | μs     |

| t <sub>DSU</sub>                    | DATA[] setup time before rising edge on DCLK              | 5.5                                                         |         | ns     |

| t <sub>DH</sub>                     | DATA[] hold time after rising edge on DCLK                | 0                                                           | _       | ns     |

| t <sub>CH</sub>                     | DCLK high time                                            | $0.45 \times 1/f_{MAX}$                                     |         | S      |

| t <sub>CL</sub>                     | DCLK low time                                             | $0.45 \times 1/f_{MAX}$                                     |         | S      |

| t <sub>CLK</sub>                    | DCLK period                                               | 1/f <sub>MAX</sub>                                          | _       | S      |

| f <sub>MAX</sub>                    | DCLK frequency                                            | -                                                           | 125     | MHz    |

| t <sub>CD2UM</sub>                  | CONF_DONE high to user mode <sup>(106)</sup>              | 175                                                         | 437     | μs     |

| t <sub>CD2CU</sub>                  | CONF_DONE high to CLKUSR enabled                          | $4 \times \text{maximum DCLK period}$                       |         | _      |

| t <sub>CD2UMC</sub>                 | CONF_DONE high to user mode with CLKUSR option on         | t <sub>CD2CU</sub> + (T <sub>init</sub> × Clkusr<br>period) | _       |        |

| T <sub>init</sub>                   | Number of clock cycles required for device initialization | 8,576                                                       | —       | Cycles |

**Related Information**

**PS Configuration Timing**

Provides the PS configuration timing waveform.

$<sup>^{(105)}</sup>$  If <code>nstatus</code> is monitored, follow the  $t_{ST2CK}$  specification. If <code>nstatus</code> is not monitored, follow the  $t_{CF2CK}$  specification.

<sup>&</sup>lt;sup>(106)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

| Term                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Definition                        |                       |  |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|--|--|--|--|

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Definition                        |                       |  |  |  |  |

| Single-ended voltage referenced I/O<br>standard | <ul> <li>The JEDEC standard for the SSTL and HSTL I/O defines both the AC and DC input signal values. The values indicate the voltage levels at which the receiver must meet its timing specifications. The DC values indicate the voltage levels at which the final logic state of the receiver is unambiguously defined. After receiver input has crossed the AC value, the receiver changes to the new logic state.</li> <li>The new logic state is then maintained as long as the input stays beyond the DC threshold. This appris intended to provide predictable receiver timing in the presence of input waveform ringing.</li> <li>Single-Ended Voltage Referenced I/O Standard</li> </ul> |                                   |                       |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |                       |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |                       |  |  |  |  |

|                                                 | V <sub>0Н</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   | V <sub>IH(AC)</sub>   |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   | VIH(DC)               |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V REF                             | / V <sub>IL(DC)</sub> |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | /                                 | /<br>V il(AC )        |  |  |  |  |

|                                                 | V <sub>0L</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |                       |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   | V <sub>SS</sub>       |  |  |  |  |

| t <sub>C</sub>                                  | High-speed receiver/transmitter input and output clock period.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   |                       |  |  |  |  |

| TCCS (channel-to-channel-skew)                  | The timing difference between the fastest and slowest output edges, including the $t_{CO}$ variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table).                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |                       |  |  |  |  |

| t <sub>DUTY</sub>                               | High-speed I/O block—Duty cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e on high-speed transmitter outpu | t clock.              |  |  |  |  |

| Date          | Version    | Changes                                                                                                                                                                                                                  |

|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2015 | 2015.12.16 | <ul> <li>Updated Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Arria V Devices table.</li> <li>Updated F<sub>clk</sub>, T<sub>dutvcvcle</sub>, and T<sub>dssfrst</sub> specifications.</li> </ul> |

|               |            | • Added $T_{qspi_clk}$ , $T_{din_start}$ , and $T_{din_end}$ specifications.                                                                                                                                             |

|               |            | Removed T <sub>dinmax</sub> specifications.                                                                                                                                                                              |

|               |            | • Updated the minimum specification for T <sub>clk</sub> to 16.67 ns and removed the maximum specification in SPI Master Timing Requirements for Arria V Devices table.                                                  |

|               |            | • Updated Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Arria V Devices table.                                                                                                                        |

|               |            | • Updated T <sub>clk</sub> to T <sub>sdmmc_clk_out</sub> symbol.                                                                                                                                                         |

|               |            | • Updated T <sub>sdmmc_clk_out</sub> and T <sub>d</sub> specifications.                                                                                                                                                  |

|               |            | • Added $T_{sdmmc_clk}$ , $T_{su}$ , and $T_h$ specifications.                                                                                                                                                           |

|               |            | Removed T <sub>dinmax</sub> specifications.                                                                                                                                                                              |

|               |            | Updated the following diagrams:                                                                                                                                                                                          |

|               |            | Quad SPI Flash Timing Diagram                                                                                                                                                                                            |

|               |            | SD/MMC Timing Diagram                                                                                                                                                                                                    |

|               |            | • Updated configuration .rbf sizes for Arria V devices.                                                                                                                                                                  |

|               |            | Changed instances of <i>Quartus II</i> to <i>Quartus Prime</i> .                                                                                                                                                         |

### 1-100 Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2012 | 3.0     | <ul> <li>Updated Table 2, Table 4, Table 9, Table 14, Table 16, Table 17, Table 20, Table 21, Table 25, Table 29, Table 36, Table 56, Table 57, and Table 60.</li> <li>Removed table: Transceiver Block Jitter Specifications for Arria V Devices.</li> <li>Added HPS information: <ul> <li>Added "HPS Specifications" section.</li> <li>Added Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, and Table 50.</li> <li>Added Figure 7, Figure 8, Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, Figure 14, Figure 15, Figure 16, Figure 17, Figure 18, and Figure 19.</li> <li>Updated Table 3 and Table 5.</li> </ul> </li> </ul> |

| October 2012  | 2.4     | <ul> <li>Updated Arria V GX V<sub>CCR_GXBL/R</sub>, V<sub>CCT_GXBL/R</sub>, and V<sub>CCL_GXBL/R</sub> minimum and maximum values, and data rate in Table 4.</li> <li>Added receiver V<sub>ICM</sub> (AC coupled) and V<sub>ICM</sub> (DC coupled) values, and transmitter V<sub>OCM</sub> (AC coupled) and V<sub>OCM</sub> (DC coupled) values in Table 20 and Table 21.</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| August 2012   | 2.3     | Updated the SERDES factor condition in Table 30.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| July 2012     | 2.2     | <ul> <li>Updated the maximum voltage for V<sub>I</sub> (DC input voltage) in Table 1.</li> <li>Updated Table 20 to include the Arria V GX -I3 speed grade.</li> <li>Updated the minimum value of the fixedclk clock frequency in Table 20 and Table 21.</li> <li>Updated the SERDES factor condition in Table 30.</li> <li>Updated Table 50 to include the IOE programmable delay settings for the Arria V GX -I3 speed grade.</li> </ul>                                                                                                                                                                                                                                                                        |

| June 2012     | 2.1     | Updated $V_{CCR\_GXBL/R}$ , $V_{CCT\_GXBL/R}$ , and $V_{CCL\_GXBL/R}$ values in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### **Transceiver Power Supply Requirements**

### Table 2-7: Transceiver Power Supply Voltage Requirements for Arria V GZ Devices

| Conditions                                                                                                                                | VCCR_GXB and VCCT_GXB <sup>(122)</sup> | VCCA_GXB | VCCH_GXB | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------|----------|------|

| If BOTH of the following conditions are true:                                                                                             | 1.05                                   |          |          |      |

| <ul> <li>Data rate &gt; 10.3 Gbps.</li> <li>DFE is used.</li> </ul>                                                                       |                                        |          |          |      |

| If ANY of the following conditions are true <sup>(123)</sup> :                                                                            | 1.0                                    | 3.0      |          |      |

| <ul> <li>ATX PLL is used.</li> <li>Data rate &gt; 6.5Gbps.</li> <li>DFE (data rate ≤ 10.3 Gbps), AEQ, or EyeQ feature is used.</li> </ul> |                                        |          | 1.5      | V    |

| If ALL of the following conditions are true:                                                                                              | 0.85                                   | 2.5      |          |      |

| <ul> <li>ATX PLL is not used.</li> <li>Data rate ≤ 6.5Gbps.</li> <li>DFE, AEQ, and EyeQ are not used.</li> </ul>                          |                                        |          |          |      |

# **DC Characteristics**

### **Supply Current**

Standby current is the current drawn from the respective power rails used for power budgeting.

Use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design because these currents vary greatly with the resources you use.

Send Feedback

<sup>&</sup>lt;sup>(122)</sup> If the VCCR\_GXB and VCCT\_GXB supplies are set to 1.0 V or 1.05 V, they cannot be shared with the VCC core supply. If the VCCR\_GXB and VCCT\_GXB are set to 0.85 V, they can be shared with the VCC core supply.

<sup>&</sup>lt;sup>(123)</sup> Choose this power supply voltage requirement option if you plan to upgrade your design later with any of the listed conditions.

AV-51002 2017.02.10

| Symbol/Description                                            | Conditions Transcei         |     | eiver Speed ( | Grade 2 | Transce | ceiver Speed Grade 3 |      | Unit     |

|---------------------------------------------------------------|-----------------------------|-----|---------------|---------|---------|----------------------|------|----------|

|                                                               | Min                         | Min | Тур           | Max     | Min     | Тур                  | Max  | Onic     |

|                                                               | 100 Hz                      | —   | —             | -70     |         | —                    | -70  | dBc/Hz   |

|                                                               | 1 kHz                       |     | _             | -90     |         |                      | -90  | dBc/Hz   |

| Transmitter REFCLK Phase Noise (622 MHz) <sup>(141)</sup>     | 10 kHz                      |     | _             | -100    |         |                      | -100 | dBc/Hz   |

|                                                               | 100 kHz                     |     | _             | -110    |         |                      | -110 | dBc/Hz   |

|                                                               | ≥1 MHz                      |     | _             | -120    |         |                      | -120 | dBc/Hz   |

| Transmitter REFCLK Phase<br>Jitter (100 MHz) <sup>(142)</sup> | 10 kHz to 1.5 MHz<br>(PCIe) |     | _             | 3       |         |                      | 3    | ps (rms) |

| R <sub>REF</sub>                                              | —                           |     | 1800 ±1%      |         |         | 1800 ±1%             |      | Ω        |

#### **Related Information**

### Arria V Device Overview

For more information about device ordering codes.

# **Transceiver Clocks**

### Table 2-23: Transceiver Clocks Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the Arria V Device Overview.

Arria V GZ Device Datasheet

**Altera Corporation**

$<sup>^{(141)}</sup>$  To calculate the REFCLK phase noise requirement at frequencies other than 622 MHz, use the following formula: REFCLK phase noise at f(MHz) = REFCLK phase noise at 622 MHz + 20 \*log(f/622).

<sup>&</sup>lt;sup>(142)</sup> To calculate the REFCLK rms phase jitter requirement for PCIe at reference clock frequencies other than 100 MHz, use the following formula: REFCLK rms phase jitter at f(MHz) = REFCLK rms phase jitter at 100 MHz  $\times$  100/f.

AV-51002 2017.02.10

| Symbol                                                 | Parameter                                                                                              | Min  | Тур | Мах                                            | Unit      |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|-----|------------------------------------------------|-----------|

| t <sub>INCCJ</sub> <sup>(171)</sup> , <sup>(172)</sup> | Input clock cycle-to-cycle jitter (f_{REF} $\geq 100~MHz)$                                             | —    | _   | 0.15                                           | UI (p-p)  |

| 'INCCJ , , , , ,                                       | Input clock cycle-to-cycle jitter ( $f_{REF} < 100 \text{ MHz}$ )                                      | -750 |     | +750                                           | ps (p-p)  |

| t <sub>outpj_dc</sub> <sup>(173)</sup>                 | Period Jitter for dedicated clock output in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )              | _    | _   | 175                                            | ps (p-p)  |

| COUTPJ_DC                                              | Period Jitter for dedicated clock output in integer<br>PLL (f <sub>OUT</sub> < 100 Mhz)                | _    |     | 17.5                                           | mUI (p-p) |

| t <sub>foutpj_dc</sub> <sup>(173)</sup>                | Period Jitter for dedicated clock output in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )           | _    |     | $250^{(176)}, \\ 175^{(174)}$                  | ps (p-p)  |

|                                                        | Period Jitter for dedicated clock output in fractional<br>PLL (f <sub>OUT</sub> < 100 MHz)             | —    |     | $25^{(176)}$ ,<br>17.5 <sup>(174)</sup>        | mUI (p-p) |

| t <sub>OUTCCJ_DC</sub> <sup>(173)</sup>                | Cycle-to-cycle Jitter for a dedicated clock output in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )    | —    |     | 175                                            | ps (p-p)  |

|                                                        | Cycle-to-cycle Jitter for a dedicated clock output in integer PLL ( $f_{OUT} < 100 \text{ MHz}$ )      | _    |     | 17.5                                           | mUI (p-p) |

| t <sub>FOUTCCJ_DC</sub> <sup>(173)</sup>               | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ ) | —    |     | 250 <sup>(176)</sup> ,<br>175 <sup>(174)</sup> | ps (p-p)  |

|                                                        | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{OUT} < 100 \text{ MHz}$ )   |      |     | $25^{(176)}$ ,<br>17.5 <sup>(174)</sup>        | mUI (p-p) |

<sup>(171)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps. <sup>(172)</sup> The  $f_{REF}$  is fIN/N specification applies when N = 1.

<sup>(174)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.20–0.80 must be  $\geq$  1200 MHz.

<sup>(173)</sup> Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.999999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a different measurement method and are available in the "Worst-Case DCD on Arria V GZ I/O Pins" table.

AV-51002 2017.02.10

| Symbol                                                                                               | Conditions                                   | C3, I3L |     |           | C4, I4 |     |           | Unit |

|------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|-----|-----------|--------|-----|-----------|------|

|                                                                                                      |                                              | Min     | Тур | Мах       | Min    | Тур | Max       | Onic |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) True Differential<br>I/O Standards <sup>(179)</sup> | Clock boost factor<br>W = 1 to 40 $^{(180)}$ | 5       | _   | 625       | 5      |     | 525       | MHz  |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) Single Ended I/O<br>Standards                       | Clock boost factor<br>W = 1 to 40 $^{(180)}$ | 5       |     | 625       | 5      | _   | 525       | MHz  |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) Single Ended I/O<br>Standards                       | Clock boost factor<br>W = 1 to 40 $^{(180)}$ | 5       | _   | 420       | 5      |     | 420       | MHz  |

| f <sub>HSCLK_OUT</sub> (output clock<br>frequency)                                                   | _                                            | 5       | _   | 625 (181) | 5      | —   | 525 (181) | MHz  |

### Transmitter High-Speed I/O Specifications

### Table 2-40: Transmitter High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

<sup>(179)</sup> This only applies to DPA and soft-CDR modes.

<sup>&</sup>lt;sup>(180)</sup> Clock Boost Factor (W) is the ratio between the input data rate to the input clock rate.

<sup>&</sup>lt;sup>(181)</sup> This is achieved by using the LVDS clock network.

| Symbol                  | Parameter                                           | Minimum                                                 | Maximum | Unit |

|-------------------------|-----------------------------------------------------|---------------------------------------------------------|---------|------|

| t <sub>CD2CU</sub>      | t <sub>CD2CU</sub> CONF_DONE high to CLKUSR enabled |                                                         | —       | —    |

|                         |                                                     | DCLK period                                             |         |      |

| t <sub>CD2UM</sub><br>C | CONF_DONE high to user mode with CLKUSR option on   | t <sub>CD2CU</sub> +<br>(8576 × CLKUSR period)<br>(209) | _       | _    |

#### **Related Information**

- DCLK-to-DATA[] Ratio (r) for FPP Configuration on page 2-57 ٠

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Arria V GZ Device Datasheet

**Altera Corporation**

<sup>&</sup>lt;sup>(208)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

<sup>&</sup>lt;sup>(209)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

| Term                               | Definition                                                                                                                                                                                                                                                                 |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>C</sub>                     | High-speed receiver and transmitter input and output clock period.                                                                                                                                                                                                         |

| TCCS (channel-to-<br>channel-skew) | The timing difference between the fastest and slowest output edges, including t <sub>CO</sub> variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table). |

| t <sub>DUTY</sub>                  | High-speed I/O block—Duty cycle on the high-speed transmitter output clock.                                                                                                                                                                                                |

| t <sub>FALL</sub>                  | Signal high-to-low transition time (80-20%)                                                                                                                                                                                                                                |

| t <sub>INCCJ</sub>                 | Cycle-to-cycle jitter tolerance on the PLL clock input.                                                                                                                                                                                                                    |

| t <sub>OUTPJ_IO</sub>              | Period jitter on the general purpose I/O driven by a PLL.                                                                                                                                                                                                                  |

| t <sub>OUTPJ_DC</sub>              | Period jitter on the dedicated clock output driven by a PLL.                                                                                                                                                                                                               |

| t <sub>RISE</sub>                  | Signal low-to-high transition time (20-80%)                                                                                                                                                                                                                                |

| Timing Unit Interval<br>(TUI)      | The timing budget allowed for skew, propagation delays, and the data sampling window.<br>(TUI = $1/(\text{receiver input clock frequency multiplication factor}) = t_C/w)$                                                                                                 |

| V <sub>CM(DC)</sub>                | DC common mode input voltage.                                                                                                                                                                                                                                              |

| V <sub>ICM</sub>                   | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                                                                                                                      |

| V <sub>ID</sub>                    | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                                                                                               |

| V <sub>DIF(AC)</sub>               | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                                                                                                                                |

| V <sub>DIF(DC)</sub>               | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                                                                                                                               |

| V <sub>IH</sub>                    | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                                                                                                                      |

| V <sub>IH(AC)</sub>                | High-level AC input voltage                                                                                                                                                                                                                                                |

| V <sub>IH(DC)</sub>                | High-level DC input voltage                                                                                                                                                                                                                                                |

| V <sub>IL</sub>                    | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                                                                                                                        |

| V <sub>IL(AC)</sub>                | Low-level AC input voltage                                                                                                                                                                                                                                                 |

| V <sub>IL(DC)</sub>                | Low-level DC input voltage                                                                                                                                                                                                                                                 |

Altera Corporation