## Intel - 5AGXBB7D4F35C5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 23780                                                      |

| Number of Logic Elements/Cells | 504000                                                     |

| Total RAM Bits                 | 27695104                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxbb7d4f35c5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Figure 1-1: Equation for OCT Variation Without Recalibration

$$R_{OCT} = R_{SCAL} \left( 1 + \left( \frac{dR}{dT} \times \Delta T \right) \pm \left( \frac{dR}{dV} \times \Delta V \right) \right)$$

The definitions for the equation are as follows:

- The R<sub>OCT</sub> value calculated shows the range of OCT resistance with the variation of temperature and V<sub>CCIO</sub>.

- R<sub>SCAL</sub> is the OCT resistance value at power-up.

- $\Delta T$  is the variation of temperature with respect to the temperature at power up.

- $\Delta V$  is the variation of voltage with respect to the V<sub>CCIO</sub> at power up.

- dR/dT is the percentage change of R<sub>SCAL</sub> with temperature.

- dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

## OCT Variation after Power-Up Calibration

### Table 1-10: OCT Variation after Power-Up Calibration for Arria V Devices

This table lists OCT variation with temperature and voltage after power-up calibration. The OCT variation is valid for a  $V_{CCIO}$  range of  $\pm 5\%$  and a temperature range of 0°C to 85°C.

| Symbol | Description                                      | V <sub>CCIO</sub> (V) | Value | Unit |

|--------|--------------------------------------------------|-----------------------|-------|------|

|        |                                                  | 3.0                   | 0.100 |      |

|        |                                                  | 2.5                   | 0.100 |      |

|        | OCT variation with voltage without recalibration | 1.8                   | 0.100 |      |

| dR/dV  |                                                  | 1.5                   | 0.100 | %/mV |

|        |                                                  | 1.35                  | 0.150 |      |

|        |                                                  | 1.25                  | 0.150 |      |

|        |                                                  | 1.2                   | 0.150 |      |

| Symbol/Description                               | Condition                                            | Transceiver Speed Grade 4 |                          | Transceiver Speed Grade 6 |     |                          | Unit |        |

|--------------------------------------------------|------------------------------------------------------|---------------------------|--------------------------|---------------------------|-----|--------------------------|------|--------|

| Symbol/Description                               | Condition                                            | Min                       | Тур                      | Max                       | Min | Тур                      | Max  | Onit   |

| Spread-spectrum<br>modulating clock<br>frequency | PCI Express <sup>®</sup> (PCIe)                      | 30                        |                          | 33                        | 30  | _                        | 33   | kHz    |

| Spread-spectrum<br>downspread                    | PCIe                                                 | —                         | 0 to -0.5%               | _                         |     | 0 to -0.5%               | —    |        |

| On-chip termination resistors                    | _                                                    | _                         | 100                      |                           | _   | 100                      | —    | Ω      |

| V <sub>ICM</sub> (AC coupled)                    |                                                      | —                         | 1.1/1.15 <sup>(26)</sup> |                           | _   | 1.1/1.15 <sup>(26)</sup> | —    | V      |

| V <sub>ICM</sub> (DC coupled)                    | HCSL I/O standard for<br>the PCIe reference<br>clock | 250                       | _                        | 550                       | 250 | _                        | 550  | mV     |

|                                                  | 10 Hz                                                | —                         | _                        | -50                       | _   | —                        | -50  | dBc/Hz |

|                                                  | 100 Hz                                               | _                         | _                        | -80                       | _   | —                        | -80  | dBc/Hz |

| Transmitter REFCLK phase                         | 1 KHz                                                | —                         |                          | -110                      | _   | —                        | -110 | dBc/Hz |

| noise <sup>(27)</sup>                            | 10 KHz                                               | _                         | _                        | -120                      | _   | _                        | -120 | dBc/Hz |

|                                                  | 100 KHz                                              | —                         | _                        | -120                      | _   | —                        | -120 | dBc/Hz |

|                                                  | ≥1 MHz                                               |                           |                          | -130                      | _   | _                        | -130 | dBc/Hz |

| R <sub>REF</sub>                                 | —                                                    | —                         | 2000 ±1%                 |                           | —   | 2000 ±1%                 | _    | Ω      |

<sup>&</sup>lt;sup>(26)</sup> For data rate  $\leq$  3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub> to either 1.1-V or 1.15-V power supply. For data rate > 3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub> to a 1.15-V power supply. For details, refer to the Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines.

<sup>&</sup>lt;sup>(27)</sup> The transmitter REFCLK phase jitter is 30 ps p-p at bit error rate (BER)  $10^{-12}$ .

| Sumbol/Decovintion                                                                       | Condition                     | Transceiver Speed Grade 4                     |                                  |     | Transceiver Speed Grade 6 |                                  |     | Unit |

|------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------|----------------------------------|-----|---------------------------|----------------------------------|-----|------|

| Symbol/Description                                                                       | Condition                     | Min                                           | Тур                              | Max | Min                       | Тур                              | Max | Onit |

| Minimum differential eye<br>opening at the receiver<br>serial input pins <sup>(30)</sup> | _                             | 100                                           | _                                | _   | 100                       | _                                | _   | mV   |

| V <sub>ICM</sub> (AC coupled)                                                            | _                             | _                                             | 0.7/0.75/<br>0.8 <sup>(31)</sup> | _   | _                         | 0.7/0.75/<br>0.8 <sup>(31)</sup> |     | mV   |

| V <sub>ICM</sub> (DC coupled)                                                            | $\leq 3.2 \text{Gbps}^{(32)}$ | 670                                           | 700                              | 730 | 670                       | 700                              | 730 | mV   |

|                                                                                          | 85- $\Omega$ setting          |                                               | 85                               | —   |                           | 85                               | _   | Ω    |

| Differential on-chip                                                                     | 100- $\Omega$ setting         |                                               | 100                              | _   |                           | 100                              |     | Ω    |

| termination resistors                                                                    | 120-Ω setting                 |                                               | 120                              | —   |                           | 120                              |     | Ω    |

|                                                                                          | 150-Ω setting                 |                                               | 150                              | _   |                           | 150                              |     | Ω    |

| t <sub>LTR</sub> <sup>(33)</sup>                                                         |                               | _                                             | _                                | 10  | _                         | _                                | 10  | μs   |

| $t_{LTD}^{(34)}$                                                                         | _                             | 4                                             | _                                | _   | 4                         | _                                | _   | μs   |

| t <sub>LTD_manual</sub> <sup>(35)</sup>                                                  | _                             | 4                                             | _                                | —   | 4                         | _                                | _   | μs   |

| t <sub>LTR_LTD_manual</sub> <sup>(36)</sup>                                              |                               | 15                                            | _                                |     | 15                        |                                  |     | μs   |

| Programmable ppm<br>detector <sup>(37)</sup>                                             | _                             | ±62.5, 100, 125, 200, 250, 300, 500, and 1000 |                                  |     |                           |                                  | ppm |      |

<sup>(30)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the **Receiver Equalization** feature. If you enable the **Receiver Equalization** feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

(31) The AC coupled  $V_{ICM} = 700 \text{ mV}$  for Arria V GX and SX in PCIe mode only. The AC coupled  $V_{ICM} = 750 \text{ mV}$  for Arria V GT and ST in PCIe mode only.

<sup>(32)</sup> For standard protocol compliance, use AC coupling.

$^{(33)}$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

$^{(34)}$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

$^{(35)}$  t<sub>LTD\_manual</sub> is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{\text{LTR\_LTD\_manual}}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

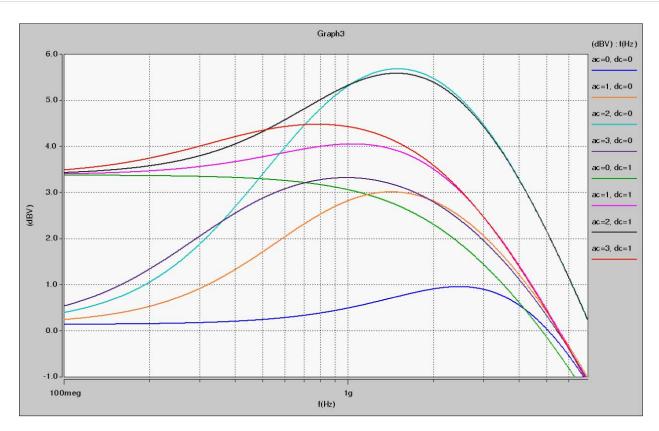

# CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain

## Figure 1-3: CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

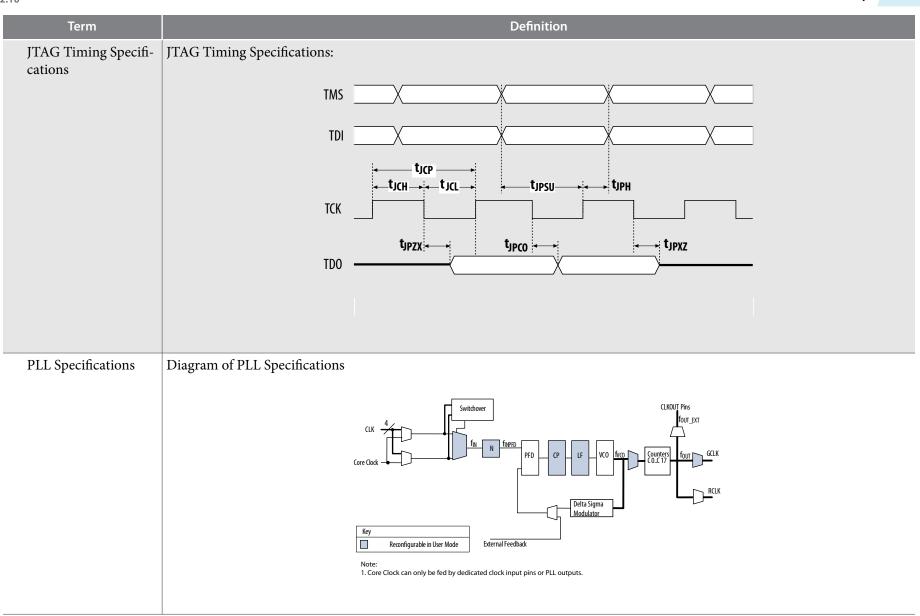

| 1-46 | PLL Specifications |

|------|--------------------|

|------|--------------------|

| Symbol                                          | Parameter                                 | Condition                     | Min | Тур | Max                                       | Unit      |

|-------------------------------------------------|-------------------------------------------|-------------------------------|-----|-----|-------------------------------------------|-----------|

| <b>+</b> (67)                                   | Period jitter for dedicated clock output  | $F_{OUT} \ge 100 \text{ MHz}$ | —   | _   | 175                                       | ps (p-p)  |

| t <sub>outpj_dc</sub> <sup>(67)</sup>           | in integer PLL                            | $F_{OUT} < 100 \text{ MHz}$   | —   | _   | 17.5                                      | mUI (p-p) |

| t(67)                                           | Period jitter for dedicated clock output  | $F_{OUT} \ge 100 \text{ MHz}$ |     |     | 250 <sup>(68)</sup> , 175 <sup>(69)</sup> | ps (p-p)  |

| t <sub>FOUTPJ_DC</sub> <sup>(67)</sup>          | in fractional PLL                         | $F_{OUT} < 100 \text{ MHz}$   |     |     | 25 <sup>(68)</sup> , 17.5 <sup>(69)</sup> | mUI (p-p) |

| t                                               | Cycle-to-cycle jitter for dedicated clock | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 175                                       | ps (p-p)  |

| t <sub>OUTCCJ_DC</sub> <sup>(67)</sup>          | output in integer PLL                     | $F_{OUT} < 100 \text{ MHz}$   | _   |     | 17.5                                      | mUI (p-p) |

| <b>4</b> (67)                                   | Cycle-to-cycle jitter for dedicated clock | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 250 <sup>(68)</sup> , 175 <sup>(69)</sup> | ps (p-p)  |

| t <sub>FOUTCCJ_DC</sub> <sup>(67)</sup>         | output in fractional PLL                  | $F_{OUT} < 100 \text{ MHz}$   | —   |     | 25 <sup>(68)</sup> , 17.5 <sup>(69)</sup> | mUI (p-p) |

| t <sub>OUTPJ_IO</sub> <sup>(67)(70)</sup>       | Period jitter for clock output on a       | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 600                                       | ps (p-p)  |

| OUTPJ_IO                                        | regular I/O in integer PLL                | $F_{OUT} < 100 MHz$           | _   | _   | 60                                        | mUI (p-p) |

| t <sub>FOUTPJ_IO</sub> <sup>(67)(68)(70)</sup>  | Period jitter for clock output on a       | $F_{OUT} \ge 100 \text{ MHz}$ | —   |     | 600                                       | ps (p-p)  |

| FOUTPJ_IO                                       | regular I/O in fractional PLL             | $F_{OUT} < 100 \text{ MHz}$   |     |     | 60                                        | mUI (p-p) |

| <b>t</b> (67)(70)                               | Cycle-to-cycle jitter for clock output on | $F_{OUT} \ge 100 \text{ MHz}$ |     |     | 600                                       | ps (p-p)  |

| t <sub>OUTCCJ_IO</sub> <sup>(67)(70)</sup>      | a regular I/O in integer PLL              | $F_{OUT} < 100 \text{ MHz}$   | —   | _   | 60                                        | mUI (p-p) |

| <b>t</b> (67)(68)(70)                           | Cycle-to-cycle jitter for clock output on | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 600                                       | ps (p-p)  |

| t <sub>FOUTCCJ_IO</sub> <sup>(67)(68)(70)</sup> | a regular I/O in fractional PLL           | $F_{OUT} < 100 \text{ MHz}$   |     |     | 60                                        | mUI (p-p) |

<sup>(67)</sup> Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.99999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a different measurement method and are available in Memory Output Clock Jitter Specification for Arria V Devices table.

<sup>&</sup>lt;sup>(68)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.05–0.95 must be  $\geq$  1000 MHz.

<sup>&</sup>lt;sup>(69)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.20–0.80 must be  $\geq$  1200 MHz.

<sup>&</sup>lt;sup>(70)</sup> External memory interface clock output jitter specifications use a different measurement method, which are available in Memory Output Clock Jitter Specification for Arria V Devices table.

# **DLL Frequency Range Specifications**

## Table 1-43: DLL Frequency Range Specifications for Arria V Devices

| Parameter                     | -I3, -C4  | -I5, -C5  | -C6       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 200 - 667 | 200 - 667 | 200 - 667 | MHz  |

# DQS Logic Block Specifications

## Table 1-44: DQS Phase Shift Error Specifications for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Arria V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -I3, -C4 | –I5, –C5 | -C6 | Unit |

|----------------------------|----------|----------|-----|------|

| 2                          | 40       | 80       | 80  | ps   |

#### 1-80 AS Configuration Timing

| Symbol              | Parameter                                                 | Minimum                                     | Maximum | Unit   |

|---------------------|-----------------------------------------------------------|---------------------------------------------|---------|--------|

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLк period                     | _       |        |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU}$ + ( $T_{init}$ × CLKUSR period) |         | _      |

| T <sub>init</sub>   | Number of clock cycles required for device initialization | 8,576                                       |         | Cycles |

#### **Related Information**

## **FPP Configuration Timing**

Provides the FPP configuration timing waveforms.

# **AS Configuration Timing**

## Table 1-68: AS Timing Parameters for AS ×1 and ×4 Configurations in Arria V Devices

The minimum and maximum numbers apply to both the internal oscillator and CLKUSR when either one is used as the clock source for device configuration.

The  $t_{CF2CD}$ ,  $t_{CF2ST0}$ ,  $t_{CFG}$ ,  $t_{STATUS}$ , and  $t_{CF2ST1}$  timing parameters are identical to the timing parameters for passive serial (PS) mode listed in PS Timing Parameters for Arria V Devices table. You can obtain the  $t_{CF2ST1}$  value if you do not delay configuration by externally holding nSTATUS low.

| Symbol              | Parameter                                                 | Minimum                                     | Maximum | Unit   |

|---------------------|-----------------------------------------------------------|---------------------------------------------|---------|--------|

| t <sub>CO</sub>     | DCLK falling edge to the AS_DATA0/ASDO output             |                                             | 2       | ns     |

| t <sub>SU</sub>     | Data setup time before the falling edge on DCLK           | 1.5                                         | _       | ns     |

| t <sub>DH</sub>     | Data hold time after the falling edge on DCLK             | 0                                           |         | ns     |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode                               | 175                                         | 437     | μs     |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                     | _       | _      |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU}$ + ( $T_{init}$ × Clkusr period) |         | _      |

| T <sub>init</sub>   | Number of clock cycles required for device initialization | 8,576                                       |         | Cycles |

#### 1-82 PS Configuration Timing

| Symbol                              | Parameter                                                 | Minimum                                                     | Maximum | Unit   |

|-------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------|---------|--------|

| $t_{CF2CK}^{(105)}$                 | nCONFIG high to first rising edge on DCLK                 | 1506                                                        | _       | μs     |

| t <sub>ST2CK</sub> <sup>(105)</sup> | nSTATUS high to first rising edge of DCLK                 | 2                                                           |         | μs     |

| t <sub>DSU</sub>                    | DATA[] setup time before rising edge on DCLK              | 5.5                                                         |         | ns     |

| t <sub>DH</sub>                     | DATA[] hold time after rising edge on DCLK                | 0                                                           | _       | ns     |

| t <sub>CH</sub>                     | DCLK high time                                            | $0.45 \times 1/f_{MAX}$                                     |         | S      |

| t <sub>CL</sub>                     | DCLK low time                                             | $0.45 \times 1/f_{MAX}$                                     |         | S      |

| t <sub>CLK</sub>                    | DCLK period                                               | 1/f <sub>MAX</sub>                                          | _       | S      |

| f <sub>MAX</sub>                    | DCLK frequency                                            | -                                                           | 125     | MHz    |

| t <sub>CD2UM</sub>                  | CONF_DONE high to user mode <sup>(106)</sup>              | 175                                                         | 437     | μs     |

| t <sub>CD2CU</sub>                  | CONF_DONE high to CLKUSR enabled                          | $4 \times \text{maximum DCLK period}$                       |         | _      |

| t <sub>CD2UMC</sub>                 | CONF_DONE high to user mode with CLKUSR option on         | t <sub>CD2CU</sub> + (T <sub>init</sub> × Clkusr<br>period) | _       |        |

| T <sub>init</sub>                   | Number of clock cycles required for device initialization | 8,576                                                       | —       | Cycles |

**Related Information**

**PS Configuration Timing**

Provides the PS configuration timing waveform.

$<sup>^{(105)}</sup>$  If <code>nstatus</code> is monitored, follow the  $t_{ST2CK}$  specification. If <code>nstatus</code> is not monitored, follow the  $t_{CF2CK}$  specification.

<sup>&</sup>lt;sup>(106)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

|            |             | Active Serial <sup>(108)</sup> |            |                                      | Fast Passive Parallel <sup>(109)</sup> |            |                                    |  |

|------------|-------------|--------------------------------|------------|--------------------------------------|----------------------------------------|------------|------------------------------------|--|

| Variant    | Member Code | Width                          | DCLK (MHz) | Minimum Configura-<br>tion Time (ms) | Width                                  | DCLK (MHz) | Minimum Configuration Time<br>(ms) |  |

|            | A1          | 4                              | 100        | 178                                  | 16                                     | 125        | 36                                 |  |

|            | A3          | 4                              | 100        | 178                                  | 16                                     | 125        | 36                                 |  |

|            | A5          | 4                              | 100        | 255                                  | 16                                     | 125        | 51                                 |  |

| Arria V GX | A7          | 4                              | 100        | 255                                  | 16                                     | 125        | 51                                 |  |

| Allia v GA | B1          | 4                              | 100        | 344                                  | 16                                     | 125        | 69                                 |  |

|            | B3          | 4                              | 100        | 344                                  | 16                                     | 125        | 69                                 |  |

|            | B5          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

|            | B7          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

|            | C3          | 4                              | 100        | 178                                  | 16                                     | 125        | 36                                 |  |

| Arria V GT | C7          | 4                              | 100        | 255                                  | 16                                     | 125        | 51                                 |  |

| Allia v Gi | D3          | 4                              | 100        | 344                                  | 16                                     | 125        | 69                                 |  |

|            | D7          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

| Arria V SX | В3          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

| Allia V SA | B5          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

| Arria V ST | D3          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

|            | D5          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

**Related Information Configuration Files** on page 1-83

(108) DCLK frequency of 100 MHz using external CLKUSR.

(109) Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

| Symbol/Description                         | Conditions                                                | Transceiver Speed Grade 2 |               |      | Transceiver Speed Grade 3     |      |      | Unit |

|--------------------------------------------|-----------------------------------------------------------|---------------------------|---------------|------|-------------------------------|------|------|------|

| Symbol/Description                         | Conditions                                                | Min                       | Тур           | Max  | Min                           | Тур  | Мах  | Unit |

| Rise time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> | _                         | _             | 400  | _                             | _    | 400  | 20   |

| Fall time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> |                           | _             | 400  |                               |      | 400  | ps   |

| Duty cycle                                 | —                                                         | 45                        | _             | 55   | 45                            |      | 55   | %    |

| Spread-spectrum modulating clock frequency | PCI Express <sup>®</sup> (PCIe)                           | 30                        | _             | 33   | 30                            |      | 33   | kHz  |

| Spread-spectrum downspread                 | PCIe                                                      |                           | 0 to          | _    | _                             | 0 to | —    | %    |

|                                            |                                                           |                           | -0.5          |      |                               | -0.5 |      |      |

| On-chip termination resistors              | —                                                         |                           | 100           | _    |                               | 100  | _    | Ω    |

| Absolute V <sub>MAX</sub>                  | Dedicated reference clock pin                             |                           | _             | 1.6  |                               |      | 1.6  | V    |

|                                            | RX reference clock pin                                    |                           | _             | 1.2  |                               |      | 1.2  |      |

| Absolute V <sub>MIN</sub>                  | —                                                         | -0.4                      | _             | _    | -0.4                          |      |      | V    |

| Peak-to-peak differential input<br>voltage | -                                                         | 200                       | -             | 1600 | 200                           |      | 1600 | mV   |

| V <sub>ICM</sub> (AC coupled)              | Dedicated reference clock pin                             | 1000/900/850 (139)        |               |      | 1000/900/850 (139)            |      |      | mV   |

| · • ·                                      | RX reference clock pin                                    | 1.                        | .0/0.9/0.85 ( | 140) | 1.0/0.9/0.85 <sup>(140)</sup> |      |      | mV   |

| V <sub>ICM</sub> (DC coupled)              | HCSL I/O standard for<br>PCIe reference clock             | 250                       | _             | 550  | 250                           |      | 550  | mV   |

<sup>(138)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

(139) The reference clock common mode voltage is equal to the V<sub>CCR\_GXB</sub> power supply level.

(140) This supply follows VCCR\_GXB

#### 2-32 Standard PCS Data Rate

|                    | ATX PLL                   |                          |                                                                                                       | CMU PLL <sup>(161)</sup>  |                       |                                                | fPLL                      |                       |                                                      |

|--------------------|---------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|------------------------------------------------|---------------------------|-----------------------|------------------------------------------------------|

| Clock Network      | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps)    | Channel<br>Span                                                                                       | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                      |

| xN (PCIe)          | _                         | 8.0                      | 8                                                                                                     | _                         | 5.0                   | 8                                              | _                         | _                     | _                                                    |

| xN (Native PHY IP) | 8.0                       | 8.0<br>8.01 to<br>9.8304 | Up to 13<br>channels<br>above and<br>below PLL<br>Up to 7<br>channels<br>above<br>and<br>below<br>PLL | 7.99                      | 7.99                  | Up to 13<br>channels<br>above and<br>below PLL | 3.125                     | 3.125                 | Up to 13<br>channels<br>above<br>and<br>below<br>PLL |

## Standard PCS Data Rate

## Table 2-30: Standard PCS Approximate Maximum Date Rate (Gbps) for Arria V GZ Devices

The maximum data rate is also constrained by the transceiver speed grade. Refer to the "Commercial and Industrial Speed Grade Offering for Arria V GZ Devices" table for the transceiver speed grade.

| Mode <sup>(164)</sup> | Transceiver | PMA Width                   | 20  | 20  | 16   | 16   | 10  | 10  | 8    | 8    |

|-----------------------|-------------|-----------------------------|-----|-----|------|------|-----|-----|------|------|

| Speed Grade           |             | PCS/Core Width              | 40  | 20  | 32   | 16   | 20  | 10  | 16   | 8    |

| FIFO                  | 2           | C3, I3L<br>core speed grade | 9.9 | 9   | 7.84 | 7.2  | 5.3 | 4.7 | 4.24 | 3.76 |

|                       | 3           | C4, I4<br>core speed grade  | 8.8 | 8.2 | 7.2  | 6.56 | 4.8 | 4.3 | 3.84 | 3.44 |

<sup>(161)</sup> ATX PLL is recommended at 8 Gbps and above data rates for improved jitter performance.

<sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

# **Typical VOD Settings**

| The tolerance is +/-20% for all VOD settings ex | cept for settings 2 and below | r.                         |                         |                            |

|-------------------------------------------------|-------------------------------|----------------------------|-------------------------|----------------------------|

| Symbol                                          | V <sub>OD</sub> Setting       | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |

|                                                 | 0 (166)                       | 0                          | 32                      | 640                        |

|                                                 | 1 <sup>(166)</sup>            | 20                         | 33                      | 660                        |

|                                                 | 2(166)                        | 40                         | 34                      | 680                        |

|                                                 | 3(166)                        | 60                         | 35                      | 700                        |

|                                                 | 4 <sup>(166)</sup>            | 80                         | 36                      | 720                        |

|                                                 | 5 <sup>(166)</sup>            | 100                        | 37                      | 740                        |

|                                                 | 6                             | 120                        | 38                      | 760                        |

| $ m V_{OD}$ differential peak to peak typical   | 7                             | 140                        | 39                      | 780                        |

|                                                 | 8                             | 160                        | 40                      | 800                        |

|                                                 | 9                             | 180                        | 41                      | 820                        |

|                                                 | 10                            | 200                        | 42                      | 840                        |

|                                                 | 11                            | 220                        | 43                      | 860                        |

|                                                 | 12                            | 240                        | 44                      | 880                        |

|                                                 | 13                            | 260                        | 45                      | 900                        |

|                                                 | 14                            | 280                        | 46                      | 920                        |

<sup>(166)</sup> If TX termination resistance = 100  $\Omega$ , this VOD setting is illegal.

| Symbol                                                       | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |

|--------------------------------------------------------------|-------------------------|----------------------------|-------------------------|----------------------------|

|                                                              | 15                      | 300                        | 47                      | 940                        |

|                                                              | 16                      | 320                        | 48                      | 960                        |

|                                                              | 17                      | 340                        | 49                      | 980                        |

|                                                              | 18                      | 360                        | 50                      | 1000                       |

|                                                              | 19                      | 380                        | 51                      | 1020                       |

|                                                              | 20                      | 400                        | 52                      | 1040                       |

|                                                              | 21                      | 420                        | 53                      | 1060                       |

|                                                              | 22                      | 440                        | 54                      | 1080                       |

| $\mathrm{V}_{\mathrm{OD}}$ differential peak to peak typical | 23                      | 460                        | 55                      | 1100                       |

|                                                              | 24                      | 480                        | 56                      | 1120                       |

|                                                              | 25                      | 500                        | 57                      | 1140                       |

|                                                              | 26                      | 520                        | 58                      | 1160                       |

|                                                              | 27                      | 540                        | 59                      | 1180                       |

|                                                              | 28                      | 560                        | 60                      | 1200                       |

|                                                              | 29                      | 580                        | 61                      | 1220                       |

|                                                              | 30                      | 600                        | 62                      | 1240                       |

|                                                              | 31                      | 620                        | 63                      | 1260                       |

AV-51002 2017.02.10

| Symbol                                                                    | Conditions                                                                                      | C3, I3L |     |     |     | - Unit |      |      |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------|-----|-----|-----|--------|------|------|

| Symbol                                                                    | Conditions                                                                                      | Min     | Тур | Мах | Min | Тур    | Max  | Onic |

| t <sub>x Jitter</sub> - True Differential I/O                             | Total Jitter for Data Rate<br>600 Mbps - 1.25 Gbps                                              | _       | _   | 160 | _   |        | 160  | ps   |

| Standards                                                                 | Total Jitter for Data Rate<br>< 600 Mbps                                                        | _       | _   | 0.1 | _   |        | 0.1  | UI   |

| t <sub>x Jitter</sub> - Emulated Differential<br>I/O Standards with Three | Total Jitter for Data Rate<br>600 Mbps - 1.25 Gbps                                              | —       | _   | 300 | _   |        | 325  | ps   |

| External Output Resistor<br>Network                                       | Total Jitter for Data Rate<br>< 600 Mbps                                                        | _       | _   | 0.2 | _   |        | 0.25 | UI   |

| t <sub>DUTY</sub>                                                         | Transmitter output clock duty<br>cycle for both True and Emulated<br>Differential I/O Standards | 45      | 50  | 55  | 45  | 50     | 55   | %    |

|                                                                           | True Differential I/O Standards                                                                 |         | _   | 200 |     |        | 200  | ps   |

| t <sub>RISE</sub> & t <sub>FALL</sub>                                     | Emulated Differential I/O<br>Standards with three external<br>output resistor networks          | _       | _   | 250 | _   | _      | 300  | ps   |

|                                                                           | True Differential I/O Standards                                                                 |         | _   | 150 |     | _      | 150  | ps   |

| TCCS                                                                      | Emulated Differential I/O<br>Standards                                                          | _       | —   | 300 |     |        | 300  | ps   |

# **Receiver High-Speed I/O Specifications**

## Table 2-41: Receiver High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

# **OCT Calibration Block Specifications**

## Table 2-51: OCT Calibration Block Specifications for Arria V GZ Devices

| Symbol                | Description                                                                                                                                                               | Min | Тур  | Мах | Unit   |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by the OCT calibration blocks                                                                                                                              | _   |      | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of OCTUSRCLK clock cycles required for OCT R <sub>S</sub> /R <sub>T</sub> calibration                                                                              | _   | 1000 |     | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for the OCT code to shift out                                                                                                   | _   | 32   |     | Cycles |

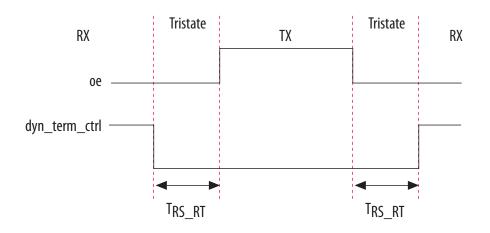

| T <sub>RS_RT</sub>    | Time required between the dyn_term_ctrl and oe signal transitions in a bidirectional I/O buffer to dynamically switch between OCT $R_S$ and $R_T$ (See the figure below.) |     | 2.5  |     | ns     |

# Figure 2-6: Timing Diagram for oe and dyn\_term\_ctrl Signals

#### **Related Information**

Configuration, Design Security, and Remote System Upgrades in Arria V Devices

# Initialization

## Table 2-61: Initialization Clock Source Option and the Maximum Frequency for Arria V GZ Devices

| Initialization Clock Source | Configuration Schemes | Maximum Frequency (MHz) | Minimum Number of Clock Cycles |

|-----------------------------|-----------------------|-------------------------|--------------------------------|

| Internal Oscillator         | AS, PS, FPP           | 12.5                    |                                |

| CLKUSR <sup>(222)</sup>     | PS, FPP               | 125                     | 8576                           |

|                             | AS                    | 100                     | 8370                           |

| DCLK                        | PS, FPP               | 125                     |                                |

# **Configuration Files**

Use the following table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Quartus II software. However, for a specific version of the Quartus II software, any design targeted for the same device has the same uncompressed configuration file size.

Arria V GZ Device Datasheet

**Altera Corporation**

<sup>&</sup>lt;sup>(221)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

<sup>(222)</sup> To enable CLKUSR as the initialization clock source, turn on the Enable user-supplied start-up clock (CLKUSR) option in the Quartus II software from the General panel of the Device and Pin Options dialog box.

# Glossary

## Table 2-68: Glossary

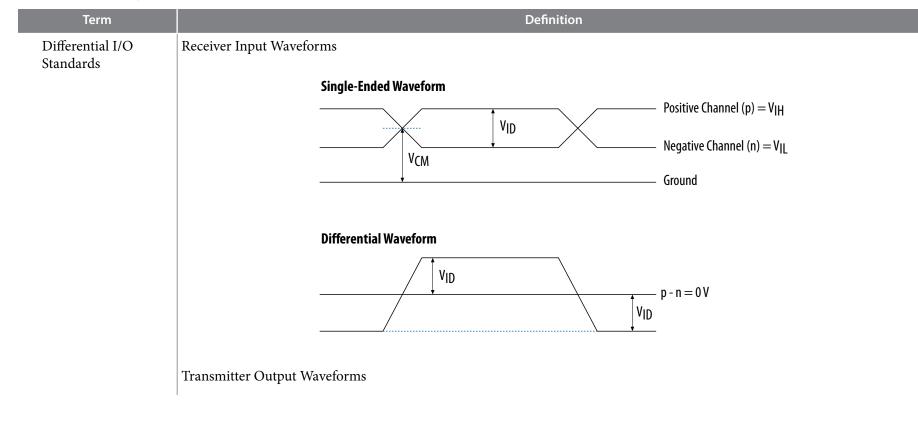

| Term                 | Definition                                                                                                                          |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|                      | Single-Ended Waveform       Positive Channel (p) = V <sub>0H</sub> $V_{0D}$ Negative Channel (n) = V <sub>0L</sub> VCM       Ground |

|                      | Differential Waveform<br>$V_{0D}$<br>$V_{0D}$<br>$V_{0D}$<br>$v_{0D}$<br>$v_{0D}$                                                   |

| f <sub>HSCLK</sub>   | Left and right PLL input clock frequency.                                                                                           |

| f <sub>HSDR</sub>    | High-speed I/O block—Maximum and minimum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI), non-DPA.                              |

| f <sub>HSDRDPA</sub> | High-speed I/O block—Maximum and minimum LVDS data transfer rate (f <sub>HSDRDPA</sub> = 1/TUI), DPA.                               |

| J                    | High-speed I/O block—Deserialization factor (width of parallel data bus).                                                           |

| Term               | Definition                                                                                                                                                       |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OCM</sub>   | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                        |

| V <sub>OD</sub>    | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. |

| V <sub>SWING</sub> | Differential input voltage                                                                                                                                       |

| V <sub>X</sub>     | Input differential cross point voltage                                                                                                                           |

| V <sub>OX</sub>    | Output differential cross point voltage                                                                                                                          |

| W                  | High-speed I/O block—clock boost factor                                                                                                                          |

# **Document Revision History**

| Date          | Version    | Changes                                                                                                                                                                      |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2017 | 2017.02.10 | • Changed the minimum value for t <sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is 1" table.                          |

|               |            | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the<br/>DCLK-to-DATA[] Ratio is &gt;1" table.</li> </ul> |

|               |            | • Changed the minimum value for t <sub>CD2UMC</sub> in the "AS Timing Parameters for AS x1 and AS x4 Configurations in Arria V GZ Devices" table.                            |

|               |            | • Changed the minimum value for t <sub>CD2UMC</sub> in the "PS Timing Parameters for Arria V GZ Devices" table.                                                              |

|               |            | <ul> <li>Changed the minimum number of clock cycles value in the "Initialization Clock Source Option and the<br/>Maximum Frequency for Arria V GZ Devices" table.</li> </ul> |