# E·XFL

#### Intel - 5AGXBB7D6F40C6N Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 23780                                                      |

| Number of Logic Elements/Cells | 504000                                                     |

| Total RAM Bits                 | 27695104                                                   |

| Number of I/O                  | 704                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1517-BBGA                                                  |

| Supplier Device Package        | 1517-FBGA (40x40)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxbb7d6f40c6n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 1-21: Transceiver Clocks Specifications for Arria V GX and SX Devices

| Symbol/Description                                                                | Condition            | Transceiver Speed Grade 4 |     |     | Transc | Unit |     |      |

|-----------------------------------------------------------------------------------|----------------------|---------------------------|-----|-----|--------|------|-----|------|

|                                                                                   | Condition            | Min                       | Тур | Мах | Min    | Тур  | Max | Onic |

| fixedclk clock frequency                                                          | PCIe Receiver Detect | —                         | 125 | —   | —      | 125  | _   | MHz  |

| Transceiver Reconfigura-<br>tion Controller IP (mgmt_<br>clk_clk) clock frequency | —                    | 75                        | _   | 125 | 75     | _    | 125 | MHz  |

# Table 1-22: Receiver Specifications for Arria V GX and SX Devices

| Sumbol/Doccription                                                                                              | Condition | Transc                                   | eiver Speed G | irade 4 | Transc | eiver Speed G | irade 6 | Unit |

|-----------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------|---------------|---------|--------|---------------|---------|------|

| Symbol/Description                                                                                              | Condition | Min                                      | Тур           | Max     | Min    | Тур           | Max     | Onit |

| Supported I/O standards                                                                                         |           | 1.5 V PCML, 2.5 V PCML, LVPECL, and LVDS |               |         |        |               |         |      |

| Data rate <sup>(28)</sup>                                                                                       | _         | 611                                      | _             | 6553.6  | 611    | _             | 3125    | Mbps |

| Absolute $V_{MAX}$ for a receiver pin <sup>(29)</sup>                                                           | _         |                                          |               | 1.2     | _      | _             | 1.2     | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                                    | _         | -0.4                                     | _             | _       | -0.4   | _             | _       | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) before device<br>configuration | —         |                                          |               | 1.6     |        |               | 1.6     | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) after device<br>configuration  | _         |                                          |               | 2.2     |        |               | 2.2     | V    |

<sup>&</sup>lt;sup>(28)</sup> To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>(29)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

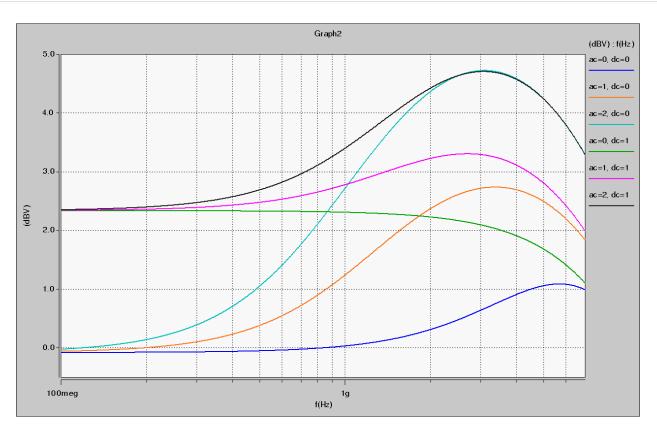

# CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain

Figure 1-2: Continuous Time-Linear Equalizer (CTLE) Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

Arria V GX, GT, SX, and ST Device Datasheet

For example, when  $V_{OD}$  = 800 mV, the corresponding  $V_{OD}$  value setting is 40. The following conditions show that the 1st post tap pre-emphasis setting = 2 is valid:

- $|B| + |C| \le 60 \Rightarrow 40 + 2 = 42$ ٠

- $|B| |C| > 5 \rightarrow 40 2 = 38$

- $(V_{MAX}/V_{MIN} 1)\% < 600\% \Rightarrow (42/38 1)\% = 10.52\%$

To predict the pre-emphasis level for your specific data rate and pattern, run simulations using the Arria V HSSI HSPICE models.

### Table 1-33: Transmitter Pre-Emphasis Levels for Arria V Devices

| Quartus Prime 1st                 |             |             | Quar        | tus Prime V <sub>OD</sub> Se | etting      |             |              |      |

|-----------------------------------|-------------|-------------|-------------|------------------------------|-------------|-------------|--------------|------|

| Post Tap Pre-<br>Emphasis Setting | 10 (200 mV) | 20 (400 mV) | 30 (600 mV) | 35 (700 mV)                  | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) | Unit |

| 0                                 | 0           | 0           | 0           | 0                            | 0           | 0           | 0            | dB   |

| 1                                 | 1.97        | 0.88        | 0.43        | 0.32                         | 0.24        | 0.19        | 0.13         | dB   |

| 2                                 | 3.58        | 1.67        | 0.95        | 0.76                         | 0.61        | 0.5         | 0.41         | dB   |

| 3                                 | 5.35        | 2.48        | 1.49        | 1.2                          | 1           | 0.83        | 0.69         | dB   |

| 4                                 | 7.27        | 3.31        | 2           | 1.63                         | 1.36        | 1.14        | 0.96         | dB   |

| 5                                 | _           | 4.19        | 2.55        | 2.1                          | 1.76        | 1.49        | 1.26         | dB   |

| 6                                 | _           | 5.08        | 3.11        | 2.56                         | 2.17        | 1.83        | 1.56         | dB   |

| 7                                 | _           | 5.99        | 3.71        | 3.06                         | 2.58        | 2.18        | 1.87         | dB   |

| 8                                 | _           | 6.92        | 4.22        | 3.47                         | 2.93        | 2.48        | 2.11         | dB   |

| 9                                 | _           | 7.92        | 4.86        | 4                            | 3.38        | 2.87        | 2.46         | dB   |

| 10                                | _           | 9.04        | 5.46        | 4.51                         | 3.79        | 3.23        | 2.77         | dB   |

| 11                                | _           | 10.2        | 6.09        | 5.01                         | 4.23        | 3.61        | —            | dB   |

| 12                                | _           | 11.56       | 6.74        | 5.51                         | 4.68        | 3.97        | —            | dB   |

| 13                                | _           | 12.9        | 7.44        | 6.1                          | 5.12        | 4.36        | —            | dB   |

| 14                                | _           | 14.44       | 8.12        | 6.64                         | 5.57        | 4.76        | _            | dB   |

| 15                                | _           | _           | 8.87        | 7.21                         | 6.06        | 5.14        | —            | dB   |

Arria V GX, GT, SX, and ST Device Datasheet

| Symbol                                 | Parameter                                                                                                      | Condition                     | Min | Тур | Max                 | Unit     |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|---------------------|----------|

|                                        |                                                                                                                | -3 speed grade                | _   | _   | 670 <sup>(63)</sup> | MHz      |

| f                                      | Output frequency for external clock                                                                            | -4 speed grade                | _   | _   | 670 <sup>(63)</sup> | MHz      |

| f <sub>out_ext</sub>                   | output                                                                                                         | –5 speed grade                | _   | _   | 622 <sup>(63)</sup> | MHz      |

|                                        |                                                                                                                | -6 speed grade                |     |     | 500 <sup>(63)</sup> | MHz      |

| t <sub>OUTDUTY</sub>                   | Duty cycle for external clock output<br>(when set to 50%)                                                      |                               | 45  | 50  | 55                  | %        |

| t <sub>FCOMP</sub>                     | External feedback clock compensation time                                                                      | _                             | _   | _   | 10                  | ns       |

| t <sub>DYCONFIGCLK</sub>               | Dynamic configuration clock for mgmt_<br>clk and scanclk                                                       | _                             | _   | _   | 100                 | MHz      |

| t <sub>LOCK</sub>                      | Time required to lock from end-of-<br>device configuration or deassertion of<br>areset                         | _                             | _   |     | 1                   | ms       |

| t <sub>DLOCK</sub>                     | Time required to lock dynamically<br>(after switchover or reconfiguring any<br>non-post-scale counters/delays) | _                             |     |     | 1                   | ms       |

|                                        |                                                                                                                | Low                           | _   | 0.3 | _                   | MHz      |

| f <sub>CLBW</sub>                      | PLL closed-loop bandwidth                                                                                      | Medium                        | _   | 1.5 | _                   | MHz      |

|                                        |                                                                                                                | High <sup>(64)</sup>          | _   | 4   | _                   | MHz      |

| t <sub>PLL_PSERR</sub>                 | Accuracy of PLL phase shift                                                                                    | —                             | _   | _   | ±50                 | ps       |

| t <sub>ARESET</sub>                    | Minimum pulse width on the areset signal                                                                       | _                             | 10  | _   | _                   | ns       |

| + (65)(66)                             | Input dock and to and ittar                                                                                    | $F_{REF} \ge 100 \text{ MHz}$ | _   | _   | 0.15                | UI (p-p) |

| t <sub>INCCJ</sub> <sup>(65)(66)</sup> | Input clock cycle-to-cycle jitter                                                                              | $F_{REF} < 100 \text{ MHz}$   | _   | _   | ±750                | ps (p-p) |

<sup>&</sup>lt;sup>(64)</sup> High bandwidth PLL settings are not supported in external feedback mode.

<sup>&</sup>lt;sup>(65)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps.

<sup>&</sup>lt;sup>(66)</sup>  $F_{\text{REF}}$  is  $f_{\text{IN}}/N$ , specification applies when N = 1.

#### Table 1-38: Memory Block Performance Specifications for Arria V Devices

| Memory | Mode                                                                                                    | Resourc | es Used |          | Performance |     | Unit |

|--------|---------------------------------------------------------------------------------------------------------|---------|---------|----------|-------------|-----|------|

| Memory | Mode                                                                                                    | ALUTs   | Memory  | -I3, -C4 | –I5, –C5    | -C6 | Onit |

|        | Single port, all supported widths                                                                       | 0       | 1       | 500      | 450         | 400 | MHz  |

|        | Simple dual-port, all supported widths                                                                  | 0       | 1       | 500      | 450         | 400 | MHz  |

| MLAB   | Simple dual-port with read and write at the same address                                                | 0       | 1       | 400      | 350         | 300 | MHz  |

|        | ROM, all supported width                                                                                | —       |         | 500      | 450         | 400 | MHz  |

|        | Single-port, all supported widths                                                                       | 0       | 1       | 400      | 350         | 285 | MHz  |

|        | Simple dual-port, all supported widths                                                                  | 0       | 1       | 400      | 350         | 285 | MHz  |

| Block  | Simple dual-port with the read-during-<br>write option set to <b>Old Data</b> , all supported<br>widths | 0       | 1       | 315      | 275         | 240 | MHz  |

|        | True dual port, all supported widths                                                                    | 0       | 1       | 400      | 350         | 285 | MHz  |

|        | ROM, all supported widths                                                                               | 0       | 1       | 400      | 350         | 285 | MHz  |

# **Internal Temperature Sensing Diode Specifications**

#### Table 1-39: Internal Temperature Sensing Diode Specifications for Arria V Devices

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate | Conversion<br>Time | Resolution | Minimum Resolution with no<br>Missing Codes |

|-------------------|----------|-----------------------------|---------------|--------------------|------------|---------------------------------------------|

| -40 to 100°C      | ±8°C     | No                          | 1 MHz         | < 100 ms           | 8 bits     | 8 bits                                      |

# **Periphery Performance**

This section describes the periphery performance, high-speed I/O, and external memory interface.

Actual achievable frequency depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

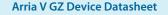

# **High-Speed I/O Specifications**

#### Table 1-40: High-Speed I/O Specifications for Arria V Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block. When J = 1 or 2, bypass the SERDES block.

For LVDS applications, you must use the PLLs in integer PLL mode.

The Arria V devices support the following output standards using true LVDS output buffer types on all I/O banks.

- True RSDS output standard with data rates of up to 360 Mbps

- True mini-LVDS output standard with data rates of up to 400 Mbps

|                                               | Symbol                                                                |                                            | -I3, -C4 |     | -I5, -C5 |      |     | -C6     |      |     | Unit                |      |

|-----------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------|----------|-----|----------|------|-----|---------|------|-----|---------------------|------|

|                                               | Symbol                                                                | Condition                                  | Min      | Тур | Max      | Min  | Тур | Мах     | Min  | Тур | Max                 | Onic |

| f <sub>HSCLK_in</sub> (inp<br>Differential I/ | out clock frequency) True<br>/O Standards                             | Clock boost factor W<br>= 1 to $40^{(72)}$ | 5        | _   | 800      | 5    | _   | 750     | 5    | _   | 625                 | MHz  |

| f <sub>HSCLK_in</sub> (inp<br>Single-Ended    | out clock frequency)<br>I I/O Standards <sup>(73)</sup>               | Clock boost factor W<br>= 1 to $40^{(72)}$ | 5        | _   | 625      | 5    | _   | 625     | 5    |     | 500                 | MHz  |

| f <sub>HSCLK_in</sub> (inp<br>Single-Ended    | out clock frequency)<br>I/O Standards <sup>(74)</sup>                 | Clock boost factor W<br>= 1 to $40^{(72)}$ | 5        |     | 420      | 5    | _   | 420     | 5    | _   | 420                 | MHz  |

| f <sub>HSCLK_OUT</sub> (                      | f <sub>HSCLK_OUT</sub> (output clock frequency)                       |                                            | 5        | _   | 625(75)  | 5    | _   | 625(75) | 5    | _   | 500 <sup>(75)</sup> | MHz  |

| Transmitter                                   | True Differential I/O<br>Standards - f <sub>HSDR</sub> (data<br>rate) | SERDES factor J =3 to $10^{(76)}$          | (77)     |     | 1250     | (77) |     | 1250    | (77) |     | 1050                | Mbps |

<sup>(73)</sup> This applies to DPA and soft-CDR modes only.

<sup>&</sup>lt;sup>(72)</sup> Clock boost factor (W) is the ratio between the input data rate and the input clock rate.

<sup>&</sup>lt;sup>(74)</sup> This applies to non-DPA mode only.

<sup>&</sup>lt;sup>(75)</sup> This is achieved by using the LVDS clock network.

$<sup>^{(76)}</sup>$  The  $F_{max}$  specification is based on the fast clock used for serial data. The interface  $F_{max}$  is also dependent on the parallel clock domain which is design dependent and requires timing analysis.

<sup>&</sup>lt;sup>(77)</sup> The minimum specification depends on the clock source (for example, the PLL and clock pin) and the clock routing resource (global, regional, or local) that you use. The I/O differential buffer and input register do not have a minimum toggle rate.

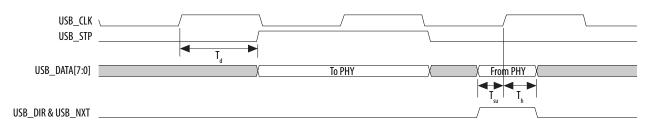

#### Figure 1-12: USB Timing Diagram

# Ethernet Media Access Controller (EMAC) Timing Characteristics

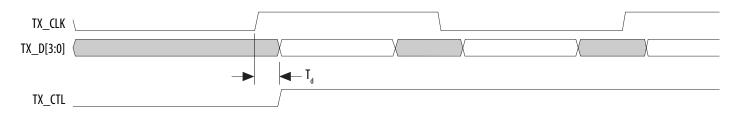

### Table 1-56: Reduced Gigabit Media Independent Interface (RGMII) TX Timing Requirements for Arria V Devices

| Symbol                        | Description                            | Min   | Тур | Max  | Unit |

|-------------------------------|----------------------------------------|-------|-----|------|------|

| T <sub>clk</sub> (1000Base-T) | TX_CLK clock period                    | _     | 8   | _    | ns   |

| T <sub>clk</sub> (100Base-T)  | TX_CLK clock period                    | —     | 40  |      | ns   |

| T <sub>clk</sub> (10Base-T)   | TX_CLK clock period                    | _     | 400 |      | ns   |

| T <sub>dutycycle</sub>        | TX_CLK duty cycle                      | 45    |     | 55   | %    |

| T <sub>d</sub>                | TX_CLK to TXD/TX_CTL output data delay | -0.85 |     | 0.15 | ns   |

#### Figure 1-13: RGMII TX Timing Diagram

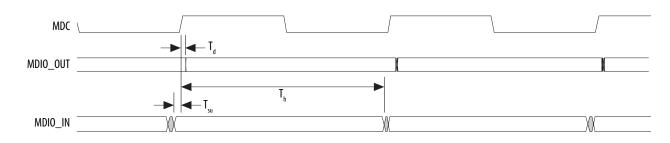

# Figure 1-15: MDIO Timing Diagram

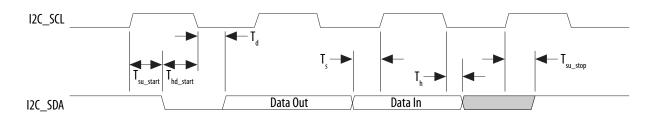

# I<sup>2</sup>C Timing Characteristics

# Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Symbol                | Description                                       | Standar | d Mode | Fast | Mode | Unit |

|-----------------------|---------------------------------------------------|---------|--------|------|------|------|

| Symbol                | Description                                       | Min     | Max    | Min  | Max  | Onic |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10      | —      | 2.5  | _    | μs   |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7     | —      | 0.6  |      | μs   |

| T <sub>clklow</sub>   | SCL low time                                      | 4       | _      | 1.3  |      | μs   |

| T <sub>s</sub>        | Setup time for serial data line (SDA) data to SCL | 0.25    | —      | 0.1  | —    | μs   |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0       | 3.45   | 0    | 0.9  | μs   |

| T <sub>d</sub>        | SCL to SDA output data delay                      | —       | 0.2    | _    | 0.2  | μs   |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7     | _      | 0.6  | _    | μs   |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4       | —      | 0.6  | _    | μs   |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4       | —      | 0.6  | —    | μs   |

#### Figure 1-16: I<sup>2</sup>C Timing Diagram

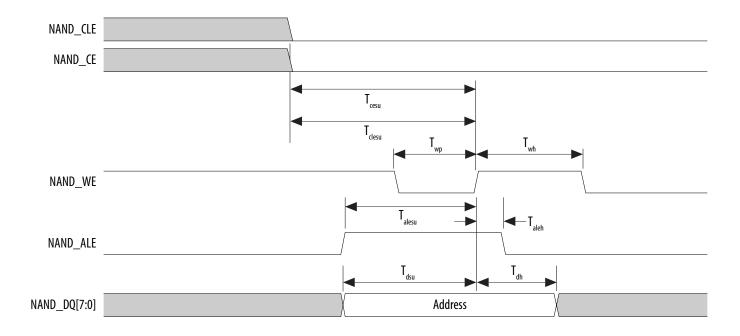

# **NAND Timing Characteristics**

#### Table 1-60: NAND ONFI 1.0 Timing Requirements for Arria V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the c4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                             | Description                                     | Min | Max | Unit |

|------------------------------------|-------------------------------------------------|-----|-----|------|

| T <sub>wp</sub> <sup>(89)</sup>    | Write enable pulse width                        | 10  | _   | ns   |

| T <sub>wh</sub> <sup>(89)</sup>    | Write enable hold time                          | 7   |     | ns   |

| T <sub>rp</sub> <sup>(89)</sup>    | Read enable pulse width                         | 10  |     | ns   |

| T <sub>reh</sub> <sup>(89)</sup>   | Read enable hold time                           | 7   |     | ns   |

| T <sub>clesu</sub> <sup>(89)</sup> | Command latch enable to write enable setup time | 10  |     | ns   |

| T <sub>cleh</sub> <sup>(89)</sup>  | Command latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>cesu</sub> <sup>(89)</sup>  | Chip enable to write enable setup time          | 15  |     | ns   |

| T <sub>ceh</sub> <sup>(89)</sup>   | Chip enable to write enable hold time           | 5   |     | ns   |

| T <sub>alesu</sub> <sup>(89)</sup> | Address latch enable to write enable setup time | 10  |     | ns   |

| T <sub>aleh</sub> <sup>(89)</sup>  | Address latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>dsu</sub> <sup>(89)</sup>   | Data to write enable setup time                 | 10  |     | ns   |

<sup>(89)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

# Figure 1-18: NAND Address Latch Timing Diagram

AV-51002 2017.02.10

The Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

#### Arria V I/O Timing Spreadsheet

Provides the Arria V Excel-based I/O timing spreadsheet.

# Programmable IOE Delay

|    | Available               | Minimum    | Fast Model |       | Slow Model |       |       |       |       | - Unit |

|----|-------------------------|------------|------------|-------|------------|-------|-------|-------|-------|--------|

|    | Offset <sup>(113)</sup> | Industrial | Commercial | -C4   | -C5        | -C6   | -13   | -15   | Onic  |        |

| D1 | 32                      | 0          | 0.508      | 0.517 | 0.870      | 1.063 | 1.063 | 0.872 | 1.057 | ns     |

| D3 | 8                       | 0          | 1.763      | 1.795 | 2.999      | 3.496 | 3.571 | 3.031 | 3.643 | ns     |

| D4 | 32                      | 0          | 0.508      | 0.518 | 0.869      | 1.063 | 1.063 | 1.063 | 1.057 | ns     |

| D5 | 32                      | 0          | 0.508      | 0.517 | 0.870      | 1.063 | 1.063 | 0.872 | 1.057 | ns     |

### Table 1-76: I/O element (IOE) Programmable Delay for Arria V Devices

# Programmable Output Buffer Delay

### Table 1-77: Programmable Output Buffer Delay for Arria V Devices

This table lists the delay chain settings that control the rising and falling edge delays of the output buffer.

You can set the programmable output buffer delay in the Quartus Prime software by setting the **Output Buffer Delay Control** assignment to either positive, negative, or both edges, with the specific values stated here (in ps) for the **Output Buffer Delay** assignment.

<sup>&</sup>lt;sup>(112)</sup> You can set this value in the Quartus Prime software by selecting **D1**, **D3**, **D4**, and **D5** in the **Assignment Name** column of **Assignment Editor**.

<sup>&</sup>lt;sup>(113)</sup> Minimum offset does not include the intrinsic delay.

| 1-88 Glossary       |                                  |             | AV-5100<br>2017.02.1 |

|---------------------|----------------------------------|-------------|----------------------|

| Symbol              | Parameter                        | Typical     | Unit                 |

|                     |                                  | 0 (default) | ps                   |

| D                   | Rising and/or falling edge delay | 50          | ps                   |

| D <sub>OUTBUF</sub> | Kising and/or failing euge delay | 100         | ps                   |

|                     |                                  | 150         | ps                   |

# Glossary

# Table 1-78: Glossary

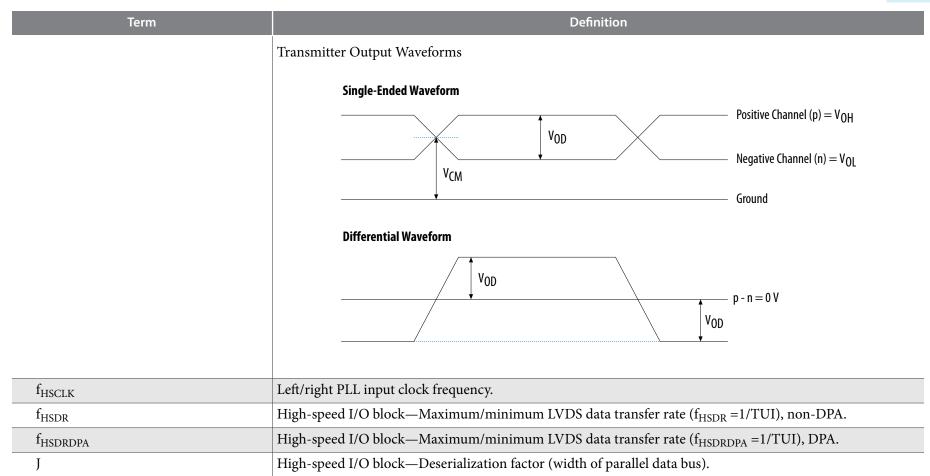

| Term                       | Definition               |                                                                              |

|----------------------------|--------------------------|------------------------------------------------------------------------------|

| Differential I/O standards | Receiver Input Waveforms |                                                                              |

|                            | Single-Ended Waveform    | Positive Channel (p) = $V_{IH}$<br>Negative Channel (n) = $V_{IL}$<br>Ground |

|                            | Differential Waveform    | p - n = 0 V                                                                  |

| Symbol                                                                                    | Description                                                                                                                            | Conditions                                    | Calibration Ac | Unit          |      |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------|---------------|------|

| Symbol                                                                                    | Description                                                                                                                            | Conditions                                    | C3, I3L        | C4, I4        | Onic |

| 25-Ω R <sub>S</sub>                                                                       | Internal series termination with calibration (25- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

| 50-Ω R <sub>S</sub>                                                                       | Internal series termination with calibration (50- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

| 34- $\Omega$ and 40- $\Omega$ R <sub>S</sub>                                              | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                   |                                               |                | ±15           | %    |

| 48-Ω, 60-Ω, 80-Ω, and<br>240-Ω R <sub>S</sub>                                             | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting)                  | $V_{CCIO} = 1.2 V$                            | ±15            | ±15           | %    |

| 50-Ω R <sub>T</sub>                                                                       | Internal parallel termination with calibration (50- $\Omega$ setting)                                                                  | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2 V      | -10 to +40     | -10 to<br>+40 | %    |

| 20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ $R_{\rm T}$ | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25 V         | -10 to +40     | -10 to<br>+40 | %    |

| 60- $\Omega$ and 120- $\Omega$ $R_{\rm T}$                                                | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                | $V_{CCIO} = 1.2$                              | -10 to +40     | -10 to<br>+40 | %    |

| 25- $\Omega R_{S\_left\_shift}$                                                           | Internal left shift series termination with calibration (25- $\Omega$ R <sub>S_left_shift</sub> setting)                               | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

# Table 2-11: OCT Without Calibration Resistance Tolerance Specifications for Arria V GZ Devices

| Symbol | Description                                                            | Conditions                        | Resistance | Unit   |      |

|--------|------------------------------------------------------------------------|-----------------------------------|------------|--------|------|

|        |                                                                        | Conditions                        | C3, I3L    | C4, I4 | Unit |

| - 8    | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0 and 2.5 V | ±40        | ±40    | %    |

| Symbol | Description                                           | V <sub>CCIO</sub> (V) | Typical | Unit |

|--------|-------------------------------------------------------|-----------------------|---------|------|

|        |                                                       | 3.0                   | 0.0297  |      |

|        |                                                       | 2.5                   | 0.0344  |      |

| dR/dV  | OCT variation with voltage without re-calibration     | 1.8                   | 0.0499  | %/mV |

|        |                                                       | 1.5                   | 0.0744  |      |

|        |                                                       | 1.2                   | 0.1241  |      |

|        |                                                       | 3.0                   | 0.189   |      |

|        |                                                       | 2.5                   | 0.208   |      |

| dR/dT  | OCT variation with temperature without re-calibration | 1.8                   | 0.266   | %/°C |

|        |                                                       | 1.5                   | 0.273   |      |

|        |                                                       | 1.2                   | 0.317   |      |

# Pin Capacitance

# Table 2-13: Pin Capacitance for Arria V GZ Devices

| Symbol             | Description                                                      | Maximum | Unit |

|--------------------|------------------------------------------------------------------|---------|------|

| C <sub>IOTB</sub>  | Input capacitance on the top and bottom I/O pins                 | 6       | pF   |

| C <sub>IOLR</sub>  | Input capacitance on the left and right I/O pins                 | 6       | pF   |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output and feedback pins | 6       | pF   |

| Symbol/Description                          | Conditions                | Transceiver Speed Grade 2 |     |       | Transc | Unit |         |      |

|---------------------------------------------|---------------------------|---------------------------|-----|-------|--------|------|---------|------|

| Symbol/Description                          | Conditions                | Min                       | Тур | Max   | Min    | Тур  | Max     | Onit |

|                                             | VCO post-divider<br>L = 2 | 8000                      |     | 12500 | 8000   | _    | 10312.5 | Mbps |

| Supported data rate range                   | L = 4                     | 4000                      |     | 6600  | 4000   |      | 6600    | Mbps |

|                                             | $L = 8^{(155)}$           | 2000                      |     | 3300  | 2000   | _    | 3300    | Mbps |

| t <sub>pll_powerdown</sub> <sup>(156)</sup> | _                         | 1                         |     |       | 1      |      |         | μs   |

| t <sub>pll_lock</sub> <sup>(157)</sup>      |                           |                           |     | 10    | _      |      | 10      | μs   |

#### **Related Information**

- Arria V Device Overview For more information about device ordering codes.

- Transceiver Clocking in Arria V Devices For more information about clocking ATX PLLs.

- **Dynamic Reconfiguration in Arria V Devices** For more information about reconfiguring ATX PLLs.

### **Fractional PLL**

### Table 2-28: Fractional PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

<sup>(155)</sup> This clock can be further divided by central or local clock dividers making it possible to use ATX PLL for data rates < 1 Gbps. For more information about ATX PLLs, refer to the Transceiver Clocking in Arria V Devices chapter and the Dynamic Reconfiguration in Arria V Devices chapter.

$t_{pll_powerdown}$  is the PLL powerdown minimum pulse width.

<sup>(157)</sup>  $t_{pll \ lock}$  is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

| Mode <sup>(164)</sup> | Transceiver | PMA Width                   | 20  | 20  | 16   | 16   | 10  | 10   | 8    | 8    |

|-----------------------|-------------|-----------------------------|-----|-----|------|------|-----|------|------|------|

|                       | Speed Grade | PCS/Core Width              | 40  | 20  | 32   | 16   | 20  | 10   | 16   | 8    |

| Register              | 2           | C3, I3L<br>core speed grade | 9.9 | 9   | 7.92 | 7.2  | 4.9 | 4.,5 | 3.92 | 3.6  |

|                       | 3           | C4, I4<br>core speed grade  | 8.8 | 8.2 | 7.04 | 6.56 | 4.4 | 4.1  | 3.52 | 3.28 |

#### **Related Information**

**Operating Conditions** on page 2-1

### **10G PCS Data Rate**

### Table 2-31: 10G PCS Approximate Maximum Data Rate (Gbps) for Arria V GZ Devices

| Mode <sup>(165)</sup> | Transceiver Speed | PMA Width                   | 64      | 40      | 40    | 40      | 32       | 32    |

|-----------------------|-------------------|-----------------------------|---------|---------|-------|---------|----------|-------|

| Mode                  | Grade             | PCS Width                   | 64      | 66/67   | 50    | 40      | 64/66/67 | 32    |

| FIFO                  | 2                 | C3, I3L core speed<br>grade | 12.5    | 12.5    | 10.69 | 12.5    | 10.88    | 10.88 |

|                       | 3                 | C4, I4 core speed<br>grade  | 10.3125 | 10.3125 | 10.69 | 10.3125 | 9.92     | 9.92  |

| Register              | 2                 | C3, I3L core speed<br>grade | 12.5    | 12.5    | 10.69 | 12.5    | 10.88    | 10.88 |

|                       | 3                 | C4, I4 core speed<br>grade  | 10.3125 | 10.3125 | 10.69 | 10.3125 | 9.92     | 9.92  |

<sup>&</sup>lt;sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

<sup>&</sup>lt;sup>(165)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

t<sub>ARESET</sub>

| Symbol                                | Parameter                                                                                                       | Min | Тур | Max | Unit |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OUT</sub> <sup>(169)</sup>     | Output frequency for an internal global or regional clock (C3, I3L speed grade)                                 | —   | —   | 650 | MHz  |

| IOUT                                  | Output frequency for an internal global or regional clock (C4, I4 speed grade)                                  | —   |     | 580 | MHz  |

| f <sub>OUT_EXT</sub> <sup>(169)</sup> | Output frequency for an external clock output (C3, I3L speed grade)                                             | _   | _   | 667 | MHz  |

| IOUT_EXT                              | Output frequency for an external clock output (C4, I4 speed grade)                                              | _   | _   | 533 | MHz  |

| toutduty                              | Duty cycle for a dedicated external clock output (when set to 50%)                                              | 45  | 50  | 55  | %    |

| t <sub>FCOMP</sub>                    | External feedback clock compensation time                                                                       | _   |     | 10  | ns   |

| f <sub>dyconfigclk</sub>              | Dynamic configuration clock for mgmt_clk and scanclk                                                            | _   | _   | 100 | MHz  |

| t <sub>LOCK</sub>                     | Time required to lock from the end-of-device configuration or deassertion of areset                             | _   | _   | 1   | ms   |

| t <sub>DLOCK</sub>                    | Time required to lock dynamically (after switchover<br>or reconfiguring any non-post-scale counters/<br>delays) | _   | _   | 1   | ms   |

|                                       | PLL closed-loop low bandwidth                                                                                   | _   | 0.3 |     | MHz  |

| $f_{CLBW}$                            | PLL closed-loop medium bandwidth                                                                                | _   | 1.5 |     | MHz  |

|                                       | PLL closed-loop high bandwidth (170)                                                                            | _   | 4   |     | MHz  |

| t <sub>PLL_PSERR</sub>                | Accuracy of PLL phase shift                                                                                     | —   | —   | ±50 | ps   |

10

\_\_\_\_

\_

Minimum pulse width on the areset signal

ns

$<sup>^{(169)}</sup>$  This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $f_{OUT}$  of the PLL.

<sup>&</sup>lt;sup>(170)</sup> High bandwidth PLL settings are not supported in external feedback mode.

| Symbol                  | Parameter                                         | Minimum                                                 | Maximum | Unit |

|-------------------------|---------------------------------------------------|---------------------------------------------------------|---------|------|

| t <sub>CD2CU</sub>      | CONF_DONE high to CLKUSR enabled                  | $4 \times maximum$                                      | —       | —    |

|                         |                                                   | DCLK period                                             |         |      |

| t <sub>CD2UM</sub><br>C | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> +<br>(8576 × CLKUSR period)<br>(209) | _       | _    |

#### **Related Information**

- DCLK-to-DATA[] Ratio (r) for FPP Configuration on page 2-57 ٠

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Arria V GZ Device Datasheet

<sup>&</sup>lt;sup>(208)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

<sup>&</sup>lt;sup>(209)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

| Symbol              | Parameter                                         | Minimum                                        | Maximum | Unit |

|---------------------|---------------------------------------------------|------------------------------------------------|---------|------|

| t <sub>CO</sub>     | DCLK falling edge to AS_DATA0/ASDO output         |                                                | 4       | ns   |

| t <sub>SU</sub>     | Data setup time before falling edge on DCLK       | 1.5                                            | —       | ns   |

| t <sub>H</sub>      | Data hold time after falling edge on DCLK         | 0                                              | —       | ns   |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode (216)                 | 175                                            | 437     | μs   |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period          | _       | _    |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> + (8576 × Clkusr<br>period) | _       | _    |

#### Table 2-59: DCLK Frequency Specification in the AS Configuration Scheme

This applies to the DCLK frequency specification when using the internal oscillator as the configuration clock source.

The AS multi-device configuration scheme does not support  ${\tt DCLK}$  frequency of 100 MHz.

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

| 10.6    | 15.7    | 25.0    | MHz  |

| 21.3    | 31.4    | 50.0    | MHz  |

| 42.6    | 62.9    | 100.0   | MHz  |

#### **Related Information**

- Passive Serial Configuration Timing on page 2-67

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

<sup>&</sup>lt;sup>(216)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on this pin, refer to the "Initialization" section of the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.