Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 8962                                                       |

| Number of Logic Elements/Cells | 190000                                                     |

| Total RAM Bits                 | 13284352                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxfa5h4f35c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Operating Conditions                                                                                                                                                                                                               | 2-1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Operating Conditions  Switching Characteristics  Transceiver Performance Specifications  Core Performance Specifications  Periphery Performance  Configuration Specification  POR Specifications  TAC Configuration Specifications | 2-21 |

| Transceiver Performance Specifications                                                                                                                                                                                             | 2-21 |

| Core Performance Specifications                                                                                                                                                                                                    | 2-37 |

| Periphery Performance                                                                                                                                                                                                              | 2-44 |

| Configuration Specification                                                                                                                                                                                                        | 2-56 |

| POR Specifications                                                                                                                                                                                                                 | 2-56 |

| JTAG Configuration Specifications                                                                                                                                                                                                  | 2-57 |

| Fast Passive Parallel (FPP) Configuration Timing                                                                                                                                                                                   | 2-57 |

| Active Serial Configuration Timing                                                                                                                                                                                                 | 2-65 |

| Active Serial Configuration Timing Passive Serial Configuration Timing                                                                                                                                                             | 2-67 |

| Initialization                                                                                                                                                                                                                     | 2-69 |

| Initialization                                                                                                                                                                                                                     | 2-69 |

| Remote System Upgrades Circuitry Timing Specification                                                                                                                                                                              | 2-70 |

| User Watchdog Internal Oscillator Frequency Specification                                                                                                                                                                          | 2-71 |

| User Watchdog Internal Oscillator Frequency Specification                                                                                                                                                                          | 2-71 |

| Programmable IOE Delay                                                                                                                                                                                                             | 2-72 |

| Programmable Output Buffer Delay                                                                                                                                                                                                   | 272. |

| Glossary                                                                                                                                                                                                                           | 2-73 |

| Document Revision History                                                                                                                                                                                                          | 2-78 |

|                                                                                                                                                                                                                                    |      |

### **I/O Standard Specifications**

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Arria V devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

### Single-Ended I/O Standards

Table 1-14: Single-Ended I/O Standards for Arria V Devices

| I/O Standard    | V <sub>CCIO</sub> (V) |     | V <sub>IL</sub> (V) |      | V <sub>IH</sub> (V)    |                        | V <sub>OL</sub> (V)  | V <sub>OH</sub> (V)    | I <sub>OL</sub> <sup>(13)</sup> | I <sub>OH</sub> <sup>(13)</sup> (mA) |                                  |

|-----------------|-----------------------|-----|---------------------|------|------------------------|------------------------|----------------------|------------------------|---------------------------------|--------------------------------------|----------------------------------|

| 1/O Standard    | Min                   | Тур | Max                 | Min  | Max                    | Min                    | Max                  | Max                    | Min                             | (mA)                                 | I <sub>OH</sub> <sup>(12</sup> ) |

| 3.3-V<br>LVTTL  | 3.135                 | 3.3 | 3.465               | -0.3 | 0.8                    | 1.7                    | 3.6                  | 0.45                   | 2.4                             | 4                                    | -4                               |

| 3.3-V<br>LVCMOS | 3.135                 | 3.3 | 3.465               | -0.3 | 0.8                    | 1.7                    | 3.6                  | 0.2                    | V <sub>CCIO</sub> - 0.2         | 2                                    | -2                               |

| 3.0-V<br>LVTTL  | 2.85                  | 3   | 3.15                | -0.3 | 0.8                    | 1.7                    | 3.6                  | 0.4                    | 2.4                             | 2                                    | -2                               |

| 3.0-V<br>LVCMOS | 2.85                  | 3   | 3.15                | -0.3 | 0.8                    | 1.7                    | 3.6                  | 0.2                    | V <sub>CCIO</sub> - 0.2         | 0.1                                  | -0.1                             |

| 3.0-V PCI       | 2.85                  | 3   | 3.15                | _    | $0.3 \times V_{CCIO}$  | $0.5 \times V_{CCIO}$  | $V_{\rm CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$           | 1.5                                  | -0.5                             |

| 3.0-V<br>PCI-X  | 2.85                  | 3   | 3.15                | _    | $0.35 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$  | $V_{\rm CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$           | 1.5                                  | -0.5                             |

| 2.5 V           | 2.375                 | 2.5 | 2.625               | -0.3 | 0.7                    | 1.7                    | 3.6                  | 0.4                    | 2                               | 1                                    | -1                               |

| 1.8 V           | 1.71                  | 1.8 | 1.89                | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | 0.45                   | V <sub>CCIO</sub> - 0.45        | 2                                    | -2                               |

| 1.5 V           | 1.425                 | 1.5 | 1.575               | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$          | 2                                    | -2                               |

| 1.2 V           | 1.14                  | 1.2 | 1.26                | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$          | 2                                    | -2                               |

To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification (4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

| Symbol/Description                                                                                  | Condition                 | Т     | Unit                     |         |       |

|-----------------------------------------------------------------------------------------------------|---------------------------|-------|--------------------------|---------|-------|

| Symbol/Description                                                                                  | Condition                 | Min   | Тур                      | Max     | Offic |

| Data rate (10-Gbps transceiver) <sup>(44)</sup>                                                     | _                         | 0.611 | _                        | 10.3125 | Gbps  |

| Absolute V <sub>MAX</sub> for a receiver pin <sup>(45)</sup>                                        | _                         | _     | _                        | 1.2     | V     |

| Absolute V <sub>MIN</sub> for a receiver pin                                                        | _                         | -0.4  | _                        | _       | V     |

| Maximum peak-to-peak differential input voltage $V_{\rm ID}$ (diff p-p) before device configuration | _                         | _     | _                        | 1.6     | V     |

| Maximum peak-to-peak differential input voltage $V_{\rm ID}$ (diff p-p) after device configuration  | _                         | _     | _                        | 2.2     | V     |

| Minimum differential eye opening at the receiver serial input pins (46)                             | _                         | 100   | _                        | _       | mV    |

| V <sub>ICM</sub> (AC coupled)                                                                       | _                         | _     | 750 <sup>(47)</sup> /800 | _       | mV    |

| V <sub>ICM</sub> (DC coupled)                                                                       | ≤ 3.2Gbps <sup>(48)</sup> | 670   | 700                      | 730     | mV    |

|                                                                                                     | 85-Ω setting              |       | 85                       |         | Ω     |

| Differential on-chip termination                                                                    | 100-Ω setting             |       | 100                      |         | Ω     |

| resistors                                                                                           | 120-Ω setting             |       | 120                      |         | Ω     |

|                                                                                                     | 150- $\Omega$ setting     |       | 150                      |         | Ω     |

| t <sub>LTR</sub> <sup>(49)</sup>                                                                    | _                         | _     | _                        | 10      | μs    |

| $t_{\mathrm{LTD}}^{(50)}$                                                                           | _                         | 4     | _                        | _       | μs    |

<sup>(45)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

<sup>(46)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the **Receiver Equalization** feature. If you enable the **Receiver Equalization** feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

$<sup>^{(47)}\,</sup>$  The AC coupled  $V_{ICM}$  is 750 mV for PCIe mode only.

<sup>(48)</sup> For standard protocol compliance, use AC coupling.

$t_{LTR}$  is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

<sup>(50)</sup> t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

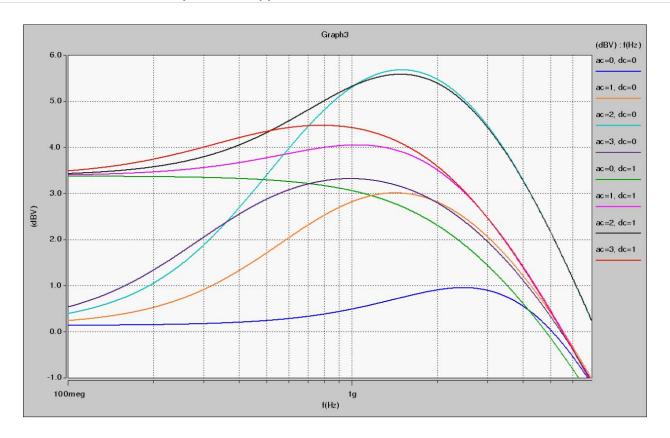

## CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain

Figure 1-3: CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

| Quartus Prime 1st                 |             | Quartus Prime V <sub>OD</sub> Setting |             |             |             |             |              |      |

|-----------------------------------|-------------|---------------------------------------|-------------|-------------|-------------|-------------|--------------|------|

| Post Tap Pre-<br>Emphasis Setting | 10 (200 mV) | 20 (400 mV)                           | 30 (600 mV) | 35 (700 mV) | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) | Unit |

| 16                                | _           | _                                     | 9.56        | 7.73        | 6.49        | _           | _            | dB   |

| 17                                | _           | _                                     | 10.43       | 8.39        | 7.02        | _           | _            | dB   |

| 18                                | _           | _                                     | 11.23       | 9.03        | 7.52        | _           | _            | dB   |

| 19                                | _           | _                                     | 12.18       | 9.7         | 8.02        | _           | _            | dB   |

| 20                                | _           | _                                     | 13.17       | 10.34       | 8.59        | _           | _            | dB   |

| 21                                | _           | _                                     | 14.2        | 11.1        | _           | _           | _            | dB   |

| 22                                | _           | _                                     | 15.38       | 11.87       | _           | _           | _            | dB   |

| 23                                | _           | _                                     | _           | 12.67       | _           | _           | _            | dB   |

| 24                                | _           | _                                     | _           | 13.48       | _           | _           | _            | dB   |

| 25                                | _           | _                                     | _           | 14.37       | _           | _           | _            | dB   |

| 26                                | _           | _                                     | _           | _           | _           | _           | _            | dB   |

| 27                                | _           | _                                     | _           | _           | _           | _           | _            | dB   |

| 28                                | _           | _                                     | _           | _           | _           | _           | _            | dB   |

| 29                                | _           | _                                     | _           | _           | _           | _           | _            | dB   |

| 30                                | _           | _                                     | _           | _           | _           | _           | _            | dB   |

| 31                                | _           | _                                     | _           | _           | _           | _           | _            | dB   |

#### **Related Information**

**SPICE Models for Altera Devices**

Provides the Arria V HSSI HSPICE models.

## **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Arria V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Altera Sales Representative.

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

| Symbol                           | Parameter                                                           | Condition      | Min          | Тур          | Max                 | Unit |

|----------------------------------|---------------------------------------------------------------------|----------------|--------------|--------------|---------------------|------|

|                                  |                                                                     | −3 speed grade | 5            | _            | 800(61)             | MHz  |

| ¢                                | Input alogh from on av                                              | -4 speed grade | 5            | _            | 800 <sup>(61)</sup> | MHz  |

| $f_{IN}$                         | Input clock frequency                                               | −5 speed grade | 5            | _            | 750 <sup>(61)</sup> | MHz  |

|                                  |                                                                     | -6 speed grade | 5            | _            | 625(61)             | MHz  |

| $f_{INPFD}$                      | Integer input clock frequency to the phase frequency detector (PFD) | _              | 5            | _            | 325                 | MHz  |

| $f_{FINPFD}$                     | Fractional input clock frequency to the PFD                         | _              | 50           | _            | 160                 | MHz  |

|                                  |                                                                     | −3 speed grade | 600          | _            | 1600                | MHz  |

| f <sub>VCO</sub> <sup>(62)</sup> | PLL voltage-controlled oscillator                                   | −4 speed grade | 600          | _            | 1600                | MHz  |

| IACO                             | (VCO) operating range                                               | −5 speed grade | 600          | _            | 1600                | MHz  |

|                                  |                                                                     | -6 speed grade | 600          | _            | 1300                | MHz  |

| $t_{EINDUTY}$                    | Input clock or external feedback clock input duty cycle             | _              | 40           | _            | 60                  | %    |

|                                  |                                                                     | -3 speed grade | _            | _            | 500(63)             | MHz  |

| ¢                                | Output frequency for internal global or                             | −4 speed grade | <del>_</del> | <del>_</del> | 500(63)             | MHz  |

| $f_{OUT}$                        | regional clock                                                      | −5 speed grade | _            | _            | 500(63)             | MHz  |

|                                  |                                                                     | −6 speed grade | _            | _            | 400(63)             | MHz  |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(61)</sup> This specification is limited in the Quartus Prime software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

The VCO frequency reported by the Quartus Prime software takes into consideration the VCO post-scale counter  $\kappa$  value. Therefore, if the counter  $\kappa$  has a value of 2, the frequency reported can be lower than the  $f_{VCO}$  specification.

This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $F_{OUT}$  of the PLL.

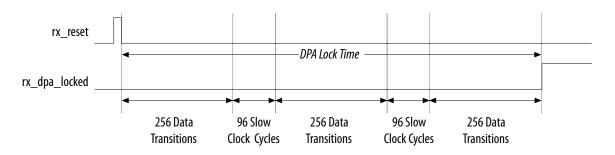

### **DPA Lock Time Specifications**

Figure 1-4: Dynamic Phase Alignment (DPA) Lock Time Specifications with DPA PLL Calibration Enabled

Table 1-41: DPA Lock Time Specifications for Arria V Devices

The specifications are applicable to both commercial and industrial grades. The DPA lock time is for one channel. One data transition is defined as a 0-to-1 or 1-to-0 transition.

| Standard           | Training Pattern    | Number of Data<br>Transitions in One<br>Repetition of the Training<br>Pattern | Number of Repetitions per<br>256 Data Transitions <sup>(84)</sup> | Maximum Data Transition |

|--------------------|---------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|

| SPI-4              | 0000000001111111111 | 2                                                                             | 128                                                               | 640                     |

| Parallel Rapid I/O | 00001111            | 2                                                                             | 128                                                               | 640                     |

| r araner Kapid 1/O | 10010000            | 4                                                                             | 64                                                                | 640                     |

| Miscellaneous      | 10101010            | 8                                                                             | 32                                                                | 640                     |

| iviliscentaneous   | 01010101            | 8                                                                             | 32                                                                | 640                     |

<sup>(84)</sup> This is the number of repetitions for the stated training pattern to achieve the 256 data transitions.

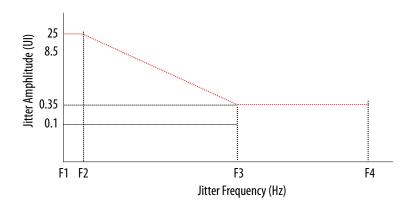

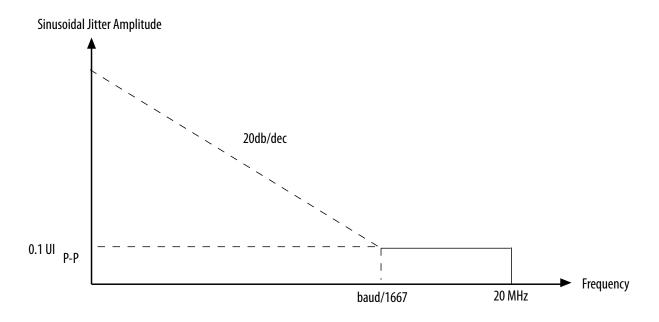

## LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specifications

Figure 1-5: LVDS Soft-Clock Data Recovery (CDR)/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate Equal to 1.25 Gbps

Table 1-42: LVDS Soft-CDR/DPA Sinusoidal Jitter Mask Values for a Data Rate Equal to 1.25 Gbps

| Jitter Freq | uency (Hz) | Sinusoidal Jitter (UI) |

|-------------|------------|------------------------|

| F1          | 10,000     | 25.000                 |

| F2          | 17,565     | 25.000                 |

| F3          | 1,493,000  | 0.350                  |

| F4          | 50,000,000 | 0.350                  |

### Initialization

Table 1-71: Initialization Clock Source Option and the Maximum Frequency for Arria V Devices

| Initialization Clock Source | Configuration Scheme | Maximum Frequency (MHz) | Minimum Number of Clock Cycles |

|-----------------------------|----------------------|-------------------------|--------------------------------|

| Internal Oscillator         | AS, PS, and FPP      | 12.5                    |                                |

| CLKUSR <sup>(107)</sup>     | PS and FPP           | 125                     | T                              |

|                             | AS                   | 100                     | $\mathrm{T_{init}}$            |

| DCLK                        | PS and FPP           | 125                     |                                |

## **Configuration Files**

### Table 1-72: Uncompressed .rbf Sizes for Arria V Devices

Use this table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Quartus Prime software. However, for a specific version of the Quartus Prime software, any design targeted for the same device has the same uncompressed configuration file size.

The IOCSR raw binary file (.rbf) size is specifically for the Configuration via Protocol (CvP) feature.

<sup>(107)</sup> To enable CLKUSR as the initialization clock source, turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus Prime software from the **General** panel of the **Device and Pin Options** dialog box.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2012     | 2.0     | <ul> <li>Updated for the Quartus II software v12.0 release:</li> <li>Restructured document.</li> <li>Updated "Supply Current and Power Consumption" section.</li> <li>Updated Table 20, Table 21, Table 24, Table 25, Table 26, Table 35, Table 39, Table 43, and Table 52.</li> <li>Added Table 22, Table 23, and Table 33.</li> <li>Added Figure 1–1 and Figure 1–2.</li> <li>Added "Initialization" and "Configuration Files" sections.</li> </ul> |

| February 2012 | 1.3     | <ul> <li>Updated Table 2–1.</li> <li>Updated Transceiver-FPGA Fabric Interface rows in Table 2–20.</li> <li>Updated V<sub>CCP</sub> description.</li> </ul>                                                                                                                                                                                                                                                                                           |

| December 2011 | 1.2     | Updated Table 2–1 and Table 2–3.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| November 2011 | 1.1     | <ul> <li>Updated Table 2–1, Table 2–19, Table 2–26, and Table 2–36.</li> <li>Added Table 2–5.</li> <li>Added Figure 2–4.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| August 2011   | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Symbol            | Description                    | Condition    | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-------------------|--------------------------------|--------------|--------------------------|---------|--------------------------|------|

| $V_{I}$           | DC input voltage               | _            | -0.5                     | _       | 3.6                      | V    |

| $V_{O}$           | Output voltage                 | _            | 0                        | _       | V <sub>CCIO</sub>        | V    |

| Т_                | Operating junction temperature | Commercial   | 0                        | _       | 85                       | °C   |

| 1 J               |                                | Industrial   | -40                      | _       | 100                      | °C   |

| t                 | Power supply ramp time         | Standard POR | 200 μs                   | _       | 100 ms                   | _    |

| t <sub>RAMP</sub> |                                | Fast POR     | 200 μs                   | _       | 4 ms                     | _    |

### **Recommended Transceiver Power Supply Operating Conditions**

Table 2-6: Recommended Transceiver Power Supply Operating Conditions for Arria V GZ Devices

| Symbol                              | Description                                        | Minimum <sup>(118)</sup> | Typical | Maximum <sup>(118)</sup> | Unit |

|-------------------------------------|----------------------------------------------------|--------------------------|---------|--------------------------|------|

| $V_{CCA\_GXBL}$                     | Transceiver channel PLL power supply (left side)   | 2.85                     | 3.0     | 3.15                     | V    |

| (119), (120)                        | Transceiver channer FLL power supply (left side)   | 2.375                    | 2.5     | 2.625                    |      |

| V <sub>CCA</sub> _GXBR (119), (120) | Transceiver channel PLL power supply (right side)  | 2.85                     | 3.0     | 3.15                     | V    |

| GXBR (119), (120)                   | Transcerver chainler FLL power supply (right side) | 2.375                    | 2.5     | 2.625                    |      |

| V <sub>CCHIP_L</sub>                | Transceiver hard IP power supply (left side)       | 0.82                     | 0.85    | 0.88                     | V    |

| V <sub>CCHSSI_L</sub>               | Transceiver PCS power supply (left side)           | 0.82                     | 0.85    | 0.88                     | V    |

| V <sub>CCHSSI_R</sub>               | Transceiver PCS power supply (right side)          | 0.82                     | 0.85    | 0.88                     | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

Altera Corporation

Arria V GZ Device Datasheet

<sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

This supply must be connected to 3.0 V if the CMU PLL, receiver CDR, or both, are configured at a base data rate > 6.5 Gbps. Up to 6.5 Gbps, you can connect this supply to either 3.0 V or 2.5 V.

<sup>(120)</sup> When using ATX PLLs, the supply must be 3.0 V.

## **I/O Standard Specifications**

The  $V_{OL}$  and  $V_{OH}$  values are valid at the corresponding  $I_{OH}$  and  $I_{OL}$ , respectively.

Table 2-16: Single-Ended I/O Standards for Arria V GZ Devices

| I/O Standard  |       | V <sub>CCIO</sub> (V) |       | V <sub>II</sub> | _(V)                       | V <sub>IH</sub>            | (V)                     | V <sub>OL</sub> (V)                                        | V <sub>OH</sub> (V)           | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) |

|---------------|-------|-----------------------|-------|-----------------|----------------------------|----------------------------|-------------------------|------------------------------------------------------------|-------------------------------|----------------------|----------------------|

| i/O Staildaid | Min   | Тур                   | Max   | Min             | Max                        | Min                        | Max                     | Max                                                        | Min                           | IOL (IIIA)           | IOH (IIIA)           |

| LVTTL         | 2.85  | 3                     | 3.15  | -0.3            | 0.8                        | 1.7                        | 3.6                     | 0.4                                                        | 2.4                           | 2                    | -2                   |

| LVCMOS        | 2.85  | 3                     | 3.15  | -0.3            | 0.8                        | 1.7                        | 3.6                     | 0.2                                                        | V <sub>CCIO</sub> - 0.2       | 0.1                  | -0.1                 |

| 2.5 V         | 2.375 | 2.5                   | 2.625 | -0.3            | 0.7                        | 1.7                        | 3.6                     | 0.4                                                        | 2                             | 1                    | -1                   |

| 1.8 V         | 1.71  | 1.8                   | 1.89  | -0.3            | $0.35 \times V_{\rm CCIO}$ | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | 0.45                                                       | V <sub>CCIO</sub> - 0.45      | 2                    | -2                   |

| 1.5 V         | 1.425 | 1.5                   | 1.575 | -0.3            | $0.35 \times V_{\rm CCIO}$ | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | $0.25 \times V_{\rm CCIO}$                                 | $0.75 \times V_{\text{CCIO}}$ | 2                    | -2                   |

| 1.2 V         | 1.14  | 1.2                   | 1.26  | -0.3            | $0.35 \times V_{\rm CCIO}$ | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | $\begin{array}{c} 0.25 \times \\ V_{\rm CCIO} \end{array}$ | $0.75 \times V_{\text{CCIO}}$ | 2                    | -2                   |

Table 2-17: Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Arria V GZ Devices

| I/O Standard           | V <sub>CCIO</sub> (V) |     |       |                        | V <sub>REF</sub> (V)                                      |                            | V <sub>TT</sub> (V)                                    |                |                         |  |

|------------------------|-----------------------|-----|-------|------------------------|-----------------------------------------------------------|----------------------------|--------------------------------------------------------|----------------|-------------------------|--|

| i/O Standard           | Min                   | Тур | Max   | Min                    | Тур                                                       | Max                        | Min                                                    | Тур            | Max                     |  |

| SSTL-2<br>Class I, II  | 2.375                 | 2.5 | 2.625 | $0.49 \times V_{CCIO}$ | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} \end{array}$ | $0.51 \times V_{\rm CCIO}$ | V <sub>REF</sub> - 0.04                                | $V_{REF}$      | V <sub>REF</sub> + 0.04 |  |

| SSTL-18<br>Class I, II | 1.71                  | 1.8 | 1.89  | 0.833                  | 0.9                                                       | 0.969                      | V <sub>REF</sub> - 0.04                                | $V_{REF}$      | V <sub>REF</sub> + 0.04 |  |

| SSTL-15<br>Class I, II | 1.425                 | 1.5 | 1.575 | $0.49 \times V_{CCIO}$ | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} \end{array}$ | $0.51 \times V_{\rm CCIO}$ | $\begin{array}{c} 0.49 \times \\ V_{CCIO} \end{array}$ | 0.5 ×<br>VCCIO | $0.51 \times V_{CCIO}$  |  |

| I/O Standard           |      | V <sub>CCIO</sub> (\ | <b>/</b> ) | V <sub>DIF</sub> | <sub>(DC)</sub> (V)     |                                      | $V_{X(AC)}(V)$        |                                     | V <sub>CN</sub>           | <sub>M(DC)</sub> (V               | )                            | V    | <sub>DIF(AC)</sub> (V)      |

|------------------------|------|----------------------|------------|------------------|-------------------------|--------------------------------------|-----------------------|-------------------------------------|---------------------------|-----------------------------------|------------------------------|------|-----------------------------|

| 1/O Standard           | Min  | Тур                  | Max        | Min              | Max                     | Min                                  | Тур                   | Max                                 | Min                       | Тур                               | Max                          | Min  | Max                         |

| HSTL-12 Class<br>I, II | 1.14 | 1.2                  | 1.26       | 0.16             | V <sub>CCIO</sub> + 0.3 | _                                    | $0.5 \times V_{CCIO}$ | _                                   | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub><br>IO | $0.6 \times V_{\text{CCIO}}$ | 0.3  | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14 | 1.2                  | 1.3        | 0.26             | 0.26                    | 0.5 ×<br>V <sub>CCIO</sub> –<br>0.12 | $0.5 \times V_{CCIO}$ | $0.5 \times V_{\rm CCIO} \\ + 0.12$ | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub>       | 0.6 ×<br>V <sub>CCIO</sub>   | 0.44 | 0.44                        |

Table 2-21: Differential I/O Standard Specifications for Arria V GZ Devices

| I/O Standard   | V <sub>CCIO</sub> (V) <sup>(128)</sup>                                                                                                                                                                                                                     |     | V <sub>ID</sub> (mV) <sup>(129)</sup> |     |                   | V <sub>ICM(DC)</sub> (V) |      | V <sub>OD</sub> (V) <sup>(130)</sup> |      |       | V <sub>OCM</sub> (V) <sup>(130)</sup> |     |       |      |       |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------|-----|-------------------|--------------------------|------|--------------------------------------|------|-------|---------------------------------------|-----|-------|------|-------|

| i/O Standard   | Min                                                                                                                                                                                                                                                        | Тур | Max                                   | Min | Condition         | Max                      | Min  | Condition                            | Max  | Min   | Тур                                   | Max | Min   | Тур  | Max   |

| PCML           | PCML Transmitter, receiver, and input reference clock pins of the high-speed transceivers use the PCML I/O standard. For transmitter, receiver, and reference clock I/O pin specifications, refer to the "Transceiver Performance Specifications" section. |     |                                       |     |                   |                          |      |                                      |      |       |                                       |     |       |      |       |

| 2.5 V<br>LVDS  | 2.375                                                                                                                                                                                                                                                      | 2.5 | 2.625                                 | 100 | V <sub>CM</sub> = | _                        | 0.05 | D <sub>MAX</sub> ≤<br>700 Mbps       | 1.8  | 0.247 | _                                     | 0.6 | 1.125 | 1.25 | 1.375 |

| (131)          | 2.373                                                                                                                                                                                                                                                      | 2.3 | 2.023                                 | 100 | 1.25 V            | _                        | 1.05 | D <sub>MAX</sub> > 700 Mbps          | 1.55 | 0.247 | _                                     | 0.6 | 1.125 | 1.25 | 1.375 |

| BLVDS<br>(132) | 2.375                                                                                                                                                                                                                                                      | 2.5 | 2.625                                 | 100 | _                 | _                        | _    | _                                    | _    | _     | _                                     | _   | _     | _    | _     |

$<sup>^{\</sup>left(128\right)}\,$  Differential inputs are powered by VCCPD which requires 2.5 V.

<sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>(130)</sup> RL range:  $90 \le RL \le 110 \Omega$ .

<sup>(131)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.6 V for data rates above 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

<sup>(132)</sup> There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

## **Switching Characteristics**

## **Transceiver Performance Specifications**

### **Reference Clock**

### Table 2-22: Reference Clock Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                               | Conditions                    | Transceiver Speed Grade 2                                                   |     |     | Transce | Unit |     |       |  |  |  |  |

|------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------|-----|-----|---------|------|-----|-------|--|--|--|--|

| Symbol/Description                                               | Conditions                    | Min                                                                         | Тур | Max | Min     | Тур  | Max | Offic |  |  |  |  |

| Reference Clock                                                  |                               |                                                                             |     |     |         |      |     |       |  |  |  |  |

| Supported I/O Standards                                          | Dedicated reference clock pin | 10                                                                          |     |     |         |      |     |       |  |  |  |  |

|                                                                  | RX reference clock pin        | RX reference clock pin 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |     |     |         |      |     |       |  |  |  |  |

| Input Reference Clock<br>Frequency<br>(CMU PLL) (137)            | _                             | 40                                                                          | _   | 710 | 40      | _    | 710 | MHz   |  |  |  |  |

| Input Reference Clock<br>Frequency<br>(ATX PLL) <sup>(137)</sup> | _                             | 100                                                                         | _   | 710 | 100     | _    | 710 | MHz   |  |  |  |  |

$<sup>^{(137)}</sup>$  The input reference clock frequency options depend on the data rate and the device speed grade.

| Symbol                                        | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |

|-----------------------------------------------|-------------------------|----------------------------|-------------------------|----------------------------|

|                                               | 15                      | 300                        | 47                      | 940                        |

|                                               | 16                      | 320                        | 48                      | 960                        |

|                                               | 17                      | 340                        | 49                      | 980                        |

|                                               | 18                      | 360                        | 50                      | 1000                       |

|                                               | 19                      | 380                        | 51                      | 1020                       |

|                                               | 20                      | 400                        | 52                      | 1040                       |

|                                               | 21                      | 420                        | 53                      | 1060                       |

|                                               | 22                      | 440                        | 54                      | 1080                       |

| $ m V_{OD}$ differential peak to peak typical | 23                      | 460                        | 55                      | 1100                       |

|                                               | 24                      | 480                        | 56                      | 1120                       |

|                                               | 25                      | 500                        | 57                      | 1140                       |

|                                               | 26                      | 520                        | 58                      | 1160                       |

|                                               | 27                      | 540                        | 59                      | 1180                       |

|                                               | 28                      | 560                        | 60                      | 1200                       |

|                                               | 29                      | 580                        | 61                      | 1220                       |

|                                               | 30                      | 600                        | 62                      | 1240                       |

|                                               | 31                      | 620                        | 63                      | 1260                       |

## **Core Performance Specifications**

## **Clock Tree Specifications**

Table 2-33: Clock Tree Performance for Arria V GZ Devices

| Symbol                    | Perfor  | Unit   |       |

|---------------------------|---------|--------|-------|

| Symbol                    | C3, I3L | C4, I4 | Offic |

| Global and Regional Clock | 650     | 580    | MHz   |

| Periphery Clock           | 500     | 500    | MHz   |

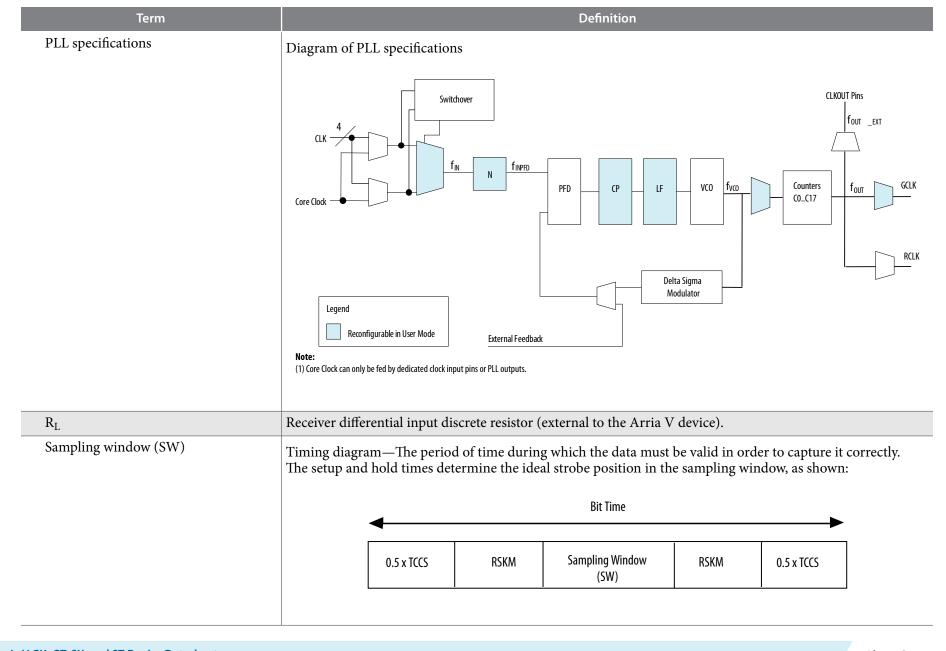

### **PLL Specifications**

Table 2-34: PLL Specifications for Arria V GZ Devices

| Symbol                           | Parameter                                               | Min | Тур | Max  | Unit |

|----------------------------------|---------------------------------------------------------|-----|-----|------|------|

| f <sub>IN</sub> <sup>(167)</sup> | Input clock frequency (C3, I3L speed grade)             | 5   | _   | 800  | MHz  |

| IIN                              | Input clock frequency (C4, I4 speed grade)              | 5   | _   | 650  | MHz  |

| f <sub>INPFD</sub>               | Input frequency to the PFD                              | 5   | _   | 325  | MHz  |

| $f_{ m FINPFD}$                  | Fractional Input clock frequency to the PFD             | 50  | _   | 160  | MHz  |

| f <sub>VCO</sub> (168)           | PLL VCO operating range (C3, I3L speed grade)           | 600 | _   | 1600 | MHz  |

| IVCO ( )                         | PLL VCO operating range (C4, I4 speed grade)            | 600 | _   | 1300 | MHz  |

| t <sub>EINDUTY</sub>             | Input clock or external feedback clock input duty cycle | 40  | _   | 60   | %    |

<sup>(167)</sup> This specification is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

<sup>(168)</sup> The VCO frequency reported by the Quartus II software in the **PLL Usage Summary** section of the compilation report takes into consideration the VCO post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the f<sub>VCO</sub> specification.

Figure 2-5: LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate < 1.25 Gbps

### Non DPA Mode High-Speed I/O Specifications

### Table 2-46: High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol          | Conditions |     | C3, I3L |     |     | Unit |     |      |

|-----------------|------------|-----|---------|-----|-----|------|-----|------|

| <b>Зутро</b> і  | Conditions | Min | Тур     | Max | Min | Тур  | Max | Onit |

| Sampling Window | _          | _   | _       | 300 | _   | _    | 300 | ps   |

**Altera Corporation** Arria V GZ Device Datasheet

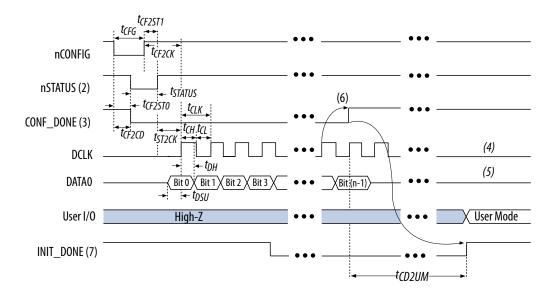

## **Passive Serial Configuration Timing**

### Figure 2-10: PS Configuration Timing Waveform

Timing waveform for a passive serial (PS) configuration when using a MAX II device, MAX V device, or microprocessor as an external host.

#### Notes:

- 1. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 2. After power-up, the Arria V GZ device holds nSTATUS low for the time of the POR delay.

- 3. After power-up, before and during configuration, CONF\_DONE is low.

- 4. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 5. DATA0 is available as a user I/O pin after configuration. The state of this pin depends on the dual-purpose pin settings in the Device and Pins Option.

- 6. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high after the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 7. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.

| Term               | Definition                                                                                                                                                       |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{OCM}$          | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                        |

| V <sub>OD</sub>    | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. |

| V <sub>SWING</sub> | Differential input voltage                                                                                                                                       |

| $V_{X}$            | Input differential cross point voltage                                                                                                                           |

| V <sub>OX</sub>    | Output differential cross point voltage                                                                                                                          |

| W                  | High-speed I/O block—clock boost factor                                                                                                                          |

# **Document Revision History**

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2017 | 2017.02.10 | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is 1" table.</li> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is &gt;1" table.</li> </ul>                                                                                                                     |

|               |            | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "AS Timing Parameters for AS x1 and AS x4 Configurations in Arria V GZ Devices" table.</li> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "PS Timing Parameters for Arria V GZ Devices" table.</li> <li>Changed the minimum number of clock cycles value in the "Initialization Clock Source Option and the Maximum Frequency for Arria V GZ Devices" table.</li> </ul> |

Altera Corporation Arria V GZ Device Datasheet