### Intel - 5AGXFA5H4F35I5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 8962                                                       |

| Number of Logic Elements/Cells | 190000                                                     |

| Total RAM Bits                 | 13284352                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                |                                                            |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxfa5h4f35i5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

AV-51002 2017.02.10

1-5

| Symbol                                 | Description                                 | Condition          | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|----------------------------------------|---------------------------------------------|--------------------|------------------------|---------|------------------------|------|

| V                                      |                                             | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| V <sub>CC</sub>                        | Core voltage power supply                   | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

| V                                      | Periphery circuitry, PCIe hard IP block,    | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| V <sub>CCP</sub>                       | and transceiver PCS power supply            | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

|                                        |                                             | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| V                                      |                                             | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

| V <sub>CCPGM</sub>                     | Configuration pins power supply             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

|                                        |                                             | 1.8 V              | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CC_AUX</sub>                    | Auxiliary supply                            | —                  | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCBAT</sub> <sup>(2)</sup>      | Battery back-up power supply                | _                  | 1.2                    | _       | 3.0                    | V    |

|                                        | (For design security volatile key register) |                    |                        |         |                        |      |

|                                        |                                             |                    | 3.135                  | 3.3     | 3.465                  | V    |

| V <sub>CCPD</sub> <sup>(3)</sup> I/O p | I/O pre-driver power supply                 | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

|                                        |                                             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

<sup>(1)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

(2) If you do not use the design security feature in Arria V devices, connect V<sub>CCBAT</sub> to a 1.5-V, 2.5-V, or 3.0-V power supply. Arria V power-on reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

<sup>&</sup>lt;sup>(3)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25, or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.  $V_{CCPD}$  must be 3.3 V when  $V_{CCIO}$  is 3.3 V.

### **Transceiver Power Supply Operating Conditions**

| Table 1-4: Transceiver Power Supply Operating Conditions for Arria V Device | es |

|-----------------------------------------------------------------------------|----|

|-----------------------------------------------------------------------------|----|

| Symbol                | Description                                           | Minimum <sup>(5)</sup> | Typical                 | Maximum <sup>(5)</sup> | Unit |

|-----------------------|-------------------------------------------------------|------------------------|-------------------------|------------------------|------|

| V <sub>CCA_GXBL</sub> | Transceiver high voltage power (left side)            | 2.375                  | 2.500                   | 2.625                  | V    |

| V <sub>CCA_GXBR</sub> | Transceiver high voltage power (right side)           | 2.373                  | 2.300                   | 2.025                  | v    |

| V <sub>CCR_GXBL</sub> | GX and SX speed grades—receiver power (left side)     | 1.08/1.12              | 1.1/1.15 <sup>(6)</sup> | 1.14/1.18              | V    |

| V <sub>CCR_GXBR</sub> | GX and SX speed grades—receiver power (right side)    | 1.00/1.12              | 1.1/1.13                | 1.14/1.10              | v    |

| V <sub>CCR_GXBL</sub> | GT and ST speed grades—receiver power (left side)     | 1.17                   | 1.20                    | 1.23                   | V    |

| V <sub>CCR_GXBR</sub> | GT and ST speed grades—receiver power (right side)    | 1.17                   | 1.20                    | 1.23                   | v    |

| V <sub>CCT_GXBL</sub> | GX and SX speed grades—transmitter power (left side)  | 1.08/1.12              | 1.1/1.15 <sup>(6)</sup> | 1.14/1.18              | V    |

| V <sub>CCT_GXBR</sub> | GX and SX speed grades—transmitter power (right side) | 1.00/1.12              | 1.1/1.13                | 1.14/1.10              | v    |

| V <sub>CCT_GXBL</sub> | GT and ST speed grades—transmitter power (left side)  | 1.17                   | 1.20                    | 1.23                   | V    |

| V <sub>CCT_GXBR</sub> | GT and ST speed grades—transmitter power (right side) | 1.17                   | 1.20                    | 1.23                   | v    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power (left side)           | 1.425                  | 1.500                   | 1.575                  | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power (right side)          | 1.423                  | 1.300                   | 1.373                  | v    |

<sup>(5)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(6)</sup> For data rate <=3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub>, V<sub>CCT\_GXBL/R</sub>, or V<sub>CCL\_GXBL/R</sub> to either 1.1-V or 1.15-V power supply. For data rate >3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub>, V<sub>CCT\_GXBL/R</sub>, or V<sub>CCL\_GXBL/R</sub> to a 1.15-V power supply. For details, refer to the Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines.

AV-51002 2017.02.10

| Symbol                               | Description                                                  | Condition             | Minimum <sup>(7)</sup> | Typical | Maximum <sup>(7)</sup> | Unit |

|--------------------------------------|--------------------------------------------------------------|-----------------------|------------------------|---------|------------------------|------|

|                                      | HPS I/O                                                      | 3.3 V                 | 3.135                  | 3.3     | 3.465                  | V    |

| V <sub>CCPD_HPS</sub> <sup>(8)</sup> | pre-driver<br>power                                          | 3.0 V                 | 2.85                   | 3.0     | 3.15                   | V    |

|                                      | supply                                                       | 2.5 V                 | 2.375                  | 2.5     | 2.625                  | V    |

|                                      |                                                              | 3.3 V                 | 3.135                  | 3.3     | 3.465                  | V    |

|                                      |                                                              | 3.0 V                 | 2.85                   | 3.0     | 3.15                   | V    |

|                                      | HPS I/O                                                      | 2.5 V                 | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCIO_HPS</sub>                | buffers<br>power                                             | 1.8 V                 | 1.71                   | 1.8     | 1.89                   | V    |

|                                      | supply                                                       | 1.5 V                 | 1.425                  | 1.5     | 1.575                  | V    |

|                                      |                                                              | 1.35 V <sup>(9)</sup> | 1.283                  | 1.35    | 1.418                  | V    |

|                                      |                                                              | 1.2 V                 | 1.14                   | 1.2     | 1.26                   | V    |

|                                      | HPS reset                                                    | 3.3 V                 | 3.135                  | 3.3     | 3.465                  | V    |

| X7                                   | and clock                                                    | 3.0 V                 | 2.85                   | 3.0     | 3.15                   | V    |

| V <sub>CCRSTCLK_HPS</sub>            | input pins<br>power                                          | 2.5 V                 | 2.375                  | 2.5     | 2.625                  | V    |

|                                      | supply                                                       | 1.8 V                 | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CCPLL_HPS</sub>               | HPS PLL<br>analog<br>voltage<br>regulator<br>power<br>supply | _                     | 2.375                  | 2.5     | 2.625                  | V    |

<sup>&</sup>lt;sup>(7)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(8)</sup> V<sub>CCPD\_HPS</sub> must be 2.5 V when V<sub>CCIO\_HPS</sub> is 2.5, 1.8, 1.5, or 1.2 V. V<sub>CCPD\_HPS</sub> must be 3.0 V when V<sub>CCIO\_HPS</sub> is 3.0 V. V<sub>CCPD\_HPS</sub> must be 3.3 V when V<sub>CCIO\_HPS</sub> is 3.3 V.

$<sup>^{(9)}\,</sup>$  V<sub>CCIO\_HPS</sub> 1.35 V is supported for HPS row I/O bank only.

| Symbol | Description                         | Condition | Minimum <sup>(7)</sup> | Typical | Maximum <sup>(7)</sup> | Unit |

|--------|-------------------------------------|-----------|------------------------|---------|------------------------|------|

|        | HPS<br>auxiliary<br>power<br>supply | _         | 2.375                  | 2.5     | 2.625                  | V    |

#### **Related Information**

**Recommended Operating Conditions** on page 1-4 Provides the steady-state voltage values for the FPGA portion of the device.

### DC Characteristics

#### Supply Current and Power Consumption

Altera offers two ways to estimate power for your design-the Excel-based Early Power Estimator (EPE) and the Quartus® Prime PowerPlay Power Analyzer feature.

Use the Excel-based EPE before you start your design to estimate the supply current for your design. The EPE provides a magnitude estimate of the device power because these currents vary greatly with the resources you use.

The Quartus Prime PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-androute. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide Provides more information about power estimation tools.

- PowerPlay Power Analysis chapter, Quartus Prime Handbook Provides more information about power estimation tools.

**Altera Corporation**

<sup>&</sup>lt;sup>(7)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

### Table 1-21: Transceiver Clocks Specifications for Arria V GX and SX Devices

| Symbol/Description                                                                | Condition            | Transceiver Speed Grade 4 |     | Transceiver Speed Grade 6 |     |     | Unit |      |

|-----------------------------------------------------------------------------------|----------------------|---------------------------|-----|---------------------------|-----|-----|------|------|

| Symbol/Description                                                                | Condition            | Min                       | Тур | Мах                       | Min | Тур | Max  | Onic |

| fixedclk clock frequency                                                          | PCIe Receiver Detect | —                         | 125 | —                         | —   | 125 | _    | MHz  |

| Transceiver Reconfigura-<br>tion Controller IP (mgmt_<br>clk_clk) clock frequency | _                    | 75                        | _   | 125                       | 75  | _   | 125  | MHz  |

# Table 1-22: Receiver Specifications for Arria V GX and SX Devices

| Sumbol/Doccription                                                                                              | Condition | Transc | Transceiver Speed Grade 4 |             |            | eiver Speed G | Unit |      |

|-----------------------------------------------------------------------------------------------------------------|-----------|--------|---------------------------|-------------|------------|---------------|------|------|

| Symbol/Description                                                                                              | Condition | Min    | Тур                       | Max         | Min        | Тур           | Max  | Onit |

| Supported I/O standards                                                                                         |           | ]      | 1.5 V PCML,               | 2.5 V PCML, | LVPECL, an | d LVDS        |      |      |

| Data rate <sup>(28)</sup>                                                                                       | _         | 611    | _                         | 6553.6      | 611        | _             | 3125 | Mbps |

| Absolute $V_{MAX}$ for a receiver pin <sup>(29)</sup>                                                           | _         |        | _                         | 1.2         | _          | _             | 1.2  | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                                    | _         | -0.4   | _                         | _           | -0.4       | _             | _    | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) before device<br>configuration | —         |        |                           | 1.6         |            |               | 1.6  | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) after device<br>configuration  | _         |        |                           | 2.2         |            |               | 2.2  | V    |

<sup>&</sup>lt;sup>(28)</sup> To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>(29)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

| Sumbol/Decovintion                                                                       | Condition                     | Transc | eiver Speed G                                 | irade 4 | Transc | eiver Speed G                    | Grade 6 | Unit |  |

|------------------------------------------------------------------------------------------|-------------------------------|--------|-----------------------------------------------|---------|--------|----------------------------------|---------|------|--|

| Symbol/Description                                                                       | Condition                     | Min    | Тур                                           | Max     | Min    | Тур                              | Max     | Onit |  |

| Minimum differential eye<br>opening at the receiver<br>serial input pins <sup>(30)</sup> | _                             | 100    | _                                             | _       | 100    | _                                | _       | mV   |  |

| V <sub>ICM</sub> (AC coupled)                                                            | _                             | _      | 0.7/0.75/<br>0.8 <sup>(31)</sup>              | _       | _      | 0.7/0.75/<br>0.8 <sup>(31)</sup> |         | mV   |  |

| V <sub>ICM</sub> (DC coupled)                                                            | $\leq 3.2 \text{Gbps}^{(32)}$ | 670    | 700                                           | 730     | 670    | 700                              | 730     | mV   |  |

|                                                                                          | 85- $\Omega$ setting          |        | 85                                            | —       | _      | 85                               | _       | Ω    |  |

| Differential on-chip                                                                     | 100- $\Omega$ setting         |        | 100                                           | _       |        | 100                              |         | Ω    |  |

| termination resistors                                                                    | 120-Ω setting                 |        | 120                                           | —       |        | 120                              |         | Ω    |  |

|                                                                                          | 150-Ω setting                 |        | 150                                           | _       |        | 150                              |         | Ω    |  |

| t <sub>LTR</sub> <sup>(33)</sup>                                                         |                               | _      | _                                             | 10      | _      | _                                | 10      | μs   |  |

| $t_{LTD}^{(34)}$                                                                         | _                             | 4      | _                                             | _       | 4      | _                                | _       | μs   |  |

| t <sub>LTD_manual</sub> <sup>(35)</sup>                                                  | _                             | 4      | _                                             | —       | 4      | _                                | _       | μs   |  |

| t <sub>LTR_LTD_manual</sub> <sup>(36)</sup>                                              |                               | 15     | _                                             |         | 15     |                                  |         | μs   |  |

| Programmable ppm<br>detector <sup>(37)</sup>                                             | _                             |        | ±62.5, 100, 125, 200, 250, 300, 500, and 1000 |         |        |                                  |         |      |  |

<sup>(30)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the **Receiver Equalization** feature. If you enable the **Receiver Equalization** feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

(31) The AC coupled  $V_{ICM} = 700 \text{ mV}$  for Arria V GX and SX in PCIe mode only. The AC coupled  $V_{ICM} = 750 \text{ mV}$  for Arria V GT and ST in PCIe mode only.

<sup>(32)</sup> For standard protocol compliance, use AC coupling.

$^{(33)}$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

$^{(34)}$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

$^{(35)}$  t<sub>LTD\_manual</sub> is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{\text{LTR\_LTD\_manual}}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

| Symbol/Description                                                          | Condition                                                   | Tran | sceiver Speed Gra | Unit |     |

|-----------------------------------------------------------------------------|-------------------------------------------------------------|------|-------------------|------|-----|

| Symbol/Description                                                          | Condition                                                   | Min  | Тур               | Max  | Ont |

|                                                                             | 85-Ω setting                                                | —    | 85                | —    | Ω   |

| Differential on-chip termination                                            | 100- $\Omega$ setting                                       |      | 100               |      | Ω   |

| resistors                                                                   | 120-Ω setting                                               | —    | 120               | —    | Ω   |

|                                                                             | 150-Ω setting                                               |      | 150               |      | Ω   |

| Intra-differential pair skew                                                | TX $V_{CM}$ = 0.65 V (AC coupled)<br>and slew rate of 15 ps |      |                   | 15   | ps  |

| Intra-transceiver block transmitter channel-to-channel skew                 | ×6 PMA bonded mode                                          |      |                   | 180  | ps  |

| Inter-transceiver block transmitter channel-to-channel skew <sup>(55)</sup> | × <i>N</i> PMA bonded mode                                  |      |                   | 500  | ps  |

# Table 1-30: CMU PLL Specifications for Arria V GT and ST Devices

| Symbol/Description        | Transceiver S | peed Grade 3 | Unit |

|---------------------------|---------------|--------------|------|

| Symbol/Description        | Min           | Max          | Onit |

| Supported data range      | 0.611         | 10.3125      | Gbps |

| fPLL supported data range | 611           | 3125         | Mbps |

<sup>(55)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

### Table 1-31: Transceiver-FPGA Fabric Interface Specifications for Arria V GT and ST Devices

| Symbol/Description                  | Transceiver S | peed Grade 3                                | Unit |

|-------------------------------------|---------------|---------------------------------------------|------|

| Symbol/Description                  | Min           | Мах                                         | Unit |

| Interface speed (PMA direct mode)   | 50            | 153.6 <sup>(56)</sup> , 161 <sup>(57)</sup> | MHz  |

| Interface speed (single-width mode) | 25            | 187.5                                       | MHz  |

| Interface speed (double-width mode) | 25            | 163.84                                      | MHz  |

**Related Information**

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 1-35

- CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain on page 1-36

<sup>&</sup>lt;sup>(56)</sup> The maximum frequency when core transceiver local routing is selected.

<sup>&</sup>lt;sup>(57)</sup> The maximum frequency when core transceiver network routing (GCLK, RCLK, or PCLK) is selected.

#### 1-62 SPI Timing Characteristics

| Symbol                 | Description                                       | Min | Мах | Unit |

|------------------------|---------------------------------------------------|-----|-----|------|

| T <sub>h</sub>         | SPI MISO hold time                                | 1   | _   | ns   |

| T <sub>dutycycle</sub> | SPI_CLK duty cycle                                | 45  | 55  | %    |

| T <sub>dssfrst</sub>   | Output delay SPI_SS valid before first clock edge | 8   |     | ns   |

| T <sub>dsslst</sub>    | Output delay SPI_SS valid after last clock edge   | 8   |     | ns   |

| T <sub>dio</sub>       | Master-out slave-in (MOSI) output delay           | -1  | 1   | ns   |

**Altera Corporation**

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(86)</sup> This value is based on rx\_sample\_dly = 1 and spi\_m\_clk = 120 MHz. spi\_m\_clk is the internal clock that is used by SPI Master to derive it's SCLK\_OUT. These timings are based on rx\_sample\_dly of 1. This delay can be adjusted as needed to accommodate slower response times from the slave. Note that a delay of 0 is not allowed. The setup time can be used as a reference starting point. It is very crucial to do a calibration to get the correct rx\_sample\_dly value because each SPI slave device may have different output delay and each application board may have different path delay. For more information about rx\_sample\_delay, refer to the SPI Controller chapter in the Hard Processor System Technical Reference Manual.

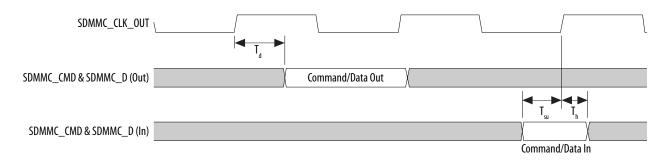

### Figure 1-11: SD/MMC Timing Diagram

#### **Related Information**

**Booting and Configuration Chapter, Arria V Hard Processor System Technical Reference Manual** Provides more information about CSEL pin settings in the SD/MMC Controller CSEL Pin Settings table.

#### **USB Timing Characteristics**

PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.

### Table 1-55: USB Timing Requirements for Arria V Devices

| Symbol           | Description                                   | Min | Тур   | Мах | Unit |

|------------------|-----------------------------------------------|-----|-------|-----|------|

| T <sub>clk</sub> | USB CLK clock period                          | _   | 16.67 | _   | ns   |

| T <sub>d</sub>   | CLK to USB_STP/USB_DATA[7:0] output delay     | 4.4 | —     | 11  | ns   |

| T <sub>su</sub>  | Setup time for USB_DIR/USB_NXT/USB_DATA[7:0]  |     | _     |     | ns   |

| T <sub>h</sub>   | h Hold time for USB_DIR/USB_NXT/USB_DATA[7:0] |     | —     |     | ns   |

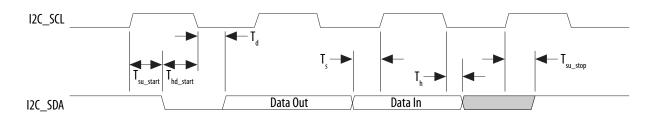

### Figure 1-16: I<sup>2</sup>C Timing Diagram

## **NAND Timing Characteristics**

#### Table 1-60: NAND ONFI 1.0 Timing Requirements for Arria V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the c4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                             | Description                                     | Min | Max | Unit |

|------------------------------------|-------------------------------------------------|-----|-----|------|

| T <sub>wp</sub> <sup>(89)</sup>    | Write enable pulse width                        | 10  | _   | ns   |

| T <sub>wh</sub> <sup>(89)</sup>    | Write enable hold time                          | 7   |     | ns   |

| T <sub>rp</sub> <sup>(89)</sup>    | Read enable pulse width                         | 10  |     | ns   |

| T <sub>reh</sub> <sup>(89)</sup>   | Read enable hold time                           |     |     | ns   |

| T <sub>clesu</sub> <sup>(89)</sup> | Command latch enable to write enable setup time |     |     | ns   |

| T <sub>cleh</sub> <sup>(89)</sup>  | Command latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>cesu</sub> <sup>(89)</sup>  | Chip enable to write enable setup time          | 15  |     | ns   |

| T <sub>ceh</sub> <sup>(89)</sup>   | Chip enable to write enable hold time           | 5   |     | ns   |

| T <sub>alesu</sub> <sup>(89)</sup> | Address latch enable to write enable setup time | 10  |     | ns   |

| T <sub>aleh</sub> <sup>(89)</sup>  | Address latch enable to write enable hold time  |     |     | ns   |

| T <sub>dsu</sub> <sup>(89)</sup>   | Data to write enable setup time                 | 10  |     | ns   |

<sup>(89)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

# **FPP Configuration Timing**

### DCLK-to-DATA[] Ratio (r) for FPP Configuration

Fast passive parallel (FPP) configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the DATA[] rate in byte per second (Bps) or word per second (Wps). For example, in FPP  $\times 16$  where the *r* is 2, the DCLK frequency must be 2 times the DATA[] rate in Wps.

### Table 1-65: DCLK-to-DATA[] Ratio for Arria V Devices

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

|                      | Off        | Off         | 1                        |

| FPP (8-bit wide)     | On         | Off         | 1                        |

| rrr (o-on wide)      | Off        | On          | 2                        |

|                      | On         | On          | 2                        |

|                      | Off        | Off         | 1                        |

| FPP (16-bit wide)    | On         | Off         | 2                        |

| rrr (10-on wide)     | Off        | On          | 4                        |

|                      | On         | On          | 4                        |

# FPP Configuration Timing when DCLK-to-DATA[] = 1

When you enable decompression or the design security feature, the DCLK-to-DATA[] ratio varies for FPP ×8 and FPP ×16. For the respective DCLKto-DATA[] ratio, refer to the DCLK-to-DATA[] Ratio for Arria V Devices table.

#### Table 1-66: FPP Timing Parameters When DCLK-to-DATA[] Ratio is 1 for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum | Unit |

|---------------------|------------------------------|---------|---------|------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | _       | 600     | ns   |

| t <sub>CF2ST0</sub> | nconfig low to nstatus low   | _       | 600     | ns   |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       | _       | μs   |

#### Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

#### 1-80 AS Configuration Timing

| Symbol              | Parameter                                                 | Minimum                                     | Maximum | Unit   |

|---------------------|-----------------------------------------------------------|---------------------------------------------|---------|--------|

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLк period                     | _       |        |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU}$ + ( $T_{init}$ × CLKUSR period) |         | _      |

| T <sub>init</sub>   | Number of clock cycles required for device initialization | 8,576                                       |         | Cycles |

#### **Related Information**

### **FPP Configuration Timing**

Provides the FPP configuration timing waveforms.

# **AS Configuration Timing**

### Table 1-68: AS Timing Parameters for AS ×1 and ×4 Configurations in Arria V Devices

The minimum and maximum numbers apply to both the internal oscillator and CLKUSR when either one is used as the clock source for device configuration.

The  $t_{CF2CD}$ ,  $t_{CF2ST0}$ ,  $t_{CFG}$ ,  $t_{STATUS}$ , and  $t_{CF2ST1}$  timing parameters are identical to the timing parameters for passive serial (PS) mode listed in PS Timing Parameters for Arria V Devices table. You can obtain the  $t_{CF2ST1}$  value if you do not delay configuration by externally holding nSTATUS low.

| Symbol              | Parameter                                                                                                                                                                                                   | Minimum                               | Maximum | Unit   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------|--------|

| t <sub>CO</sub>     | DCLK falling edge to the AS_DATA0/ASDO output                                                                                                                                                               | _                                     | 2       | ns     |

| t <sub>SU</sub>     | Data setup time before the falling edge on DCLK                                                                                                                                                             | 1.5                                   |         | ns     |

| t <sub>DH</sub>     | Data hold time after the falling edge on DCLK                                                                                                                                                               | 0                                     |         | ns     |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode                                                                                                                                                                                 | 175                                   | 437     | μs     |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                                                                                                                                                                            | $4 \times \text{maximum DCLK period}$ |         | _      |

| t <sub>CD2UMC</sub> | $\begin{array}{c} \text{CONF}_{\text{DONE}} \text{ high to user mode with CLKUSR option on} \\ \text{t}_{\text{CD2CU}} + (\text{T}_{\text{init}} \times \text{CLKUSR option}) \\ \text{period} \end{array}$ |                                       | _       | _      |

| T <sub>init</sub>   | Number of clock cycles required for device initialization                                                                                                                                                   | 8,576                                 | —       | Cycles |

| Symbol                                                                                    | Description                                                                                                                            | Conditions                                    | Calibration Ac | Unit          |      |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------|---------------|------|

| Symbol                                                                                    | Description                                                                                                                            | Conditions                                    | C3, I3L        | C4, I4        | Onic |

| 25-Ω R <sub>S</sub>                                                                       | Internal series termination with calibration (25- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

| 50-Ω R <sub>S</sub>                                                                       | Internal series termination with calibration (50- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

| 34- $\Omega$ and 40- $\Omega$ R <sub>S</sub>                                              | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                   | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2 V    | ±15            | ±15           | %    |

| 48-Ω, 60-Ω, 80-Ω, and<br>240-Ω R <sub>S</sub>                                             | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting)                  | $V_{CCIO} = 1.2 V$                            | ±15            | ±15           | %    |

| 50-Ω R <sub>T</sub>                                                                       | Internal parallel termination with calibration (50- $\Omega$ setting)                                                                  | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2 V      | -10 to +40     | -10 to<br>+40 | %    |

| 20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ $R_{\rm T}$ | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25 V         | -10 to +40     | -10 to<br>+40 | %    |

| 60- $\Omega$ and 120- $\Omega$ $R_{\rm T}$                                                | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                | $V_{CCIO} = 1.2$                              | -10 to +40     | -10 to<br>+40 | %    |

| 25- $\Omega R_{S\_left\_shift}$                                                           | Internal left shift series termination with calibration (25- $\Omega$ R <sub>S_left_shift</sub> setting)                               | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15            | ±15           | %    |

# Table 2-11: OCT Without Calibration Resistance Tolerance Specifications for Arria V GZ Devices

| Symbol Description | Description                                                            | Conditions                        | Resistance | Unit   |      |

|--------------------|------------------------------------------------------------------------|-----------------------------------|------------|--------|------|

|                    | Description                                                            | Conditions                        | C3, I3L    | C4, I4 | Onit |

| - 8                | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0 and 2.5 V | ±40        | ±40    | %    |

| Symbol               | Description                                                            | Conditions                 | Resistance | Unit   |   |

|----------------------|------------------------------------------------------------------------|----------------------------|------------|--------|---|

| Symbol               | Description                                                            | Conditions                 | C3, I3L    | C4, I4 |   |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | % |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | % |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | % |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | % |

| 100-Ω R <sub>D</sub> | Internal differential termination (100- $\Omega$ setting)              | $V_{CCIO} = 2.5 V$         | ±25        | ±25    | % |

### Figure 2-1: OCT Variation Without Re-Calibration for Arria V GZ Devices

$$\mathbf{R}_{\text{OCT}} = \mathbf{R}_{\text{SCAL}} \left( 1 + \left( \frac{dR}{dT} \times \bigtriangleup T \right) \pm \left( \frac{dR}{dV} \times \bigtriangleup V \right) \right)$$

Notes:

1. The  $R_{oct}$  value shows the range of OCT resistance with the variation of temperature and  $V_{ccio}$ . 2.  $R_{scAL}$  is the OCT resistance value at power-up. 3.  $\Delta T$  is the variation of temperature with respect to the temperature at power-up. 4.  $\Delta V$  is the variation of voltage with respect to the  $V_{ccio}$  at power-up. 5. dR/dT is the percentage change of  $R_{scAL}$  with temperature. 6. dR/dV is the percentage change of  $R_{scAL}$  with voltage

6. dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

### Table 2-12: OCT Variation after Power-Up Calibration for Arria V GZ Devices

Valid for a V<sub>CCIO</sub> range of  $\pm$ 5% and a temperature range of 0° to 85°C.

AV-51002 2017.02.10

| Symbol/Description                                                                              | Conditions                                  | Transceiver Speed Grade 2 |              |     | Transceiver Speed Grade 3 |              |     | Unit |

|-------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------|--------------|-----|---------------------------|--------------|-----|------|

| Symbol/Description                                                                              | Conditions                                  | Min                       | Тур          | Мах | Min                       | Тур          | Мах |      |

| Maximum peak-to-peak differential input voltage $V_{ID}$ (diff p-p) before device configuration | _                                           | _                         | _            | 1.6 | _                         | _            | 1.6 | V    |

| Maximum peak-to-peak differential input voltage V <sub>ID</sub> (diff p-p) after                | $V_{CCR\_GXB} = 1.0 V$ $(V_{ICM} = 0.75 V)$ | _                         | _            | 1.8 | _                         |              | 1.8 | V    |

| device configuration <sup>(146)</sup>                                                           | $V_{CCR\_GXB} = 0.85 V$ $(V_{ICM} = 0.6 V)$ |                           | _            | 2.4 | _                         | _            | 2.4 | V    |

| Minimum differential eye opening at receiver serial input pins <sup>(147)(148)</sup>            | _                                           | 85                        | _            | _   | 85                        | _            |     | mV   |

|                                                                                                 | 85– $\Omega$ setting                        |                           | 85 ± 30%     | _   | _                         | 85<br>± 30%  | _   | Ω    |

| Differential on-chip termination                                                                | 100– $\Omega$ setting                       |                           | 100<br>± 30% |     | _                         | 100<br>± 30% |     | Ω    |

| resistors                                                                                       | 120– $\Omega$ setting                       | —                         | 120<br>± 30% |     | —                         | 120<br>± 30% |     | Ω    |

|                                                                                                 | 150– $\Omega$ setting                       | _                         | 150<br>± 30% |     | _                         | 150<br>± 30% |     | Ω    |

<sup>&</sup>lt;sup>(146)</sup> The maximum peak to peak differential input voltage  $V_{ID}$  after device configuration is equal to 4 × (absolute  $V_{MAX}$  for receiver pin -  $V_{ICM}$ ).

<sup>&</sup>lt;sup>(147)</sup> The differential eye opening specification at the receiver input pins assumes that **Receiver Equalization** is disabled. If you enable **Receiver Equalization**, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

<sup>&</sup>lt;sup>(148)</sup> Minimum eye opening of 85 mV is only for the unstressed input eye condition.

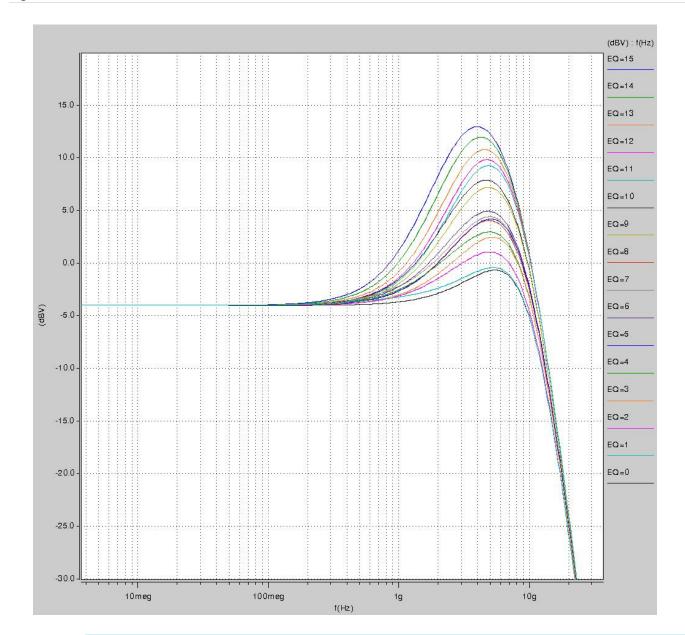

### Figure 2-2: AC Gain Curves for Arria V GZ Channels (full bandwidth)

Altera Corporation

| Memory        | Mode                                                                                             | Resources Used |        | Performance |     |     |     | Unit |

|---------------|--------------------------------------------------------------------------------------------------|----------------|--------|-------------|-----|-----|-----|------|

|               | Mode                                                                                             | ALUTs          | Memory | C3          | C4  | I3L | 14  |      |

|               | Single-port, all supported widths                                                                | 0              | 1      | 650         | 550 | 500 | 450 | MHz  |

|               | Simple dual-port, all supported widths                                                           | 0              | 1      | 650         | 550 | 500 | 450 | MHz  |

|               | Simple dual-port with the read-during-write option set to <b>Old Data</b> , all supported widths | 0              | 1      | 455         | 400 | 455 | 400 | MHz  |

| M20K<br>Block | Simple dual-port with ECC enabled, $512 \times 32$                                               | 0              | 1      | 400         | 350 | 400 | 350 | MHz  |

|               | Simple dual-port with ECC and optional pipeline registers enabled, 512 × 32                      | 0              | 1      | 500         | 450 | 500 | 450 | MHz  |

|               | True dual port, all supported widths                                                             | 0              | 1      | 650         | 550 | 500 | 450 | MHz  |

|               | ROM, all supported widths                                                                        | 0              | 1      | 650         | 550 | 500 | 450 | MHz  |

# **Temperature Sensing Diode Specifications**

### Table 2-37: Internal Temperature Sensing Diode Specification

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate  | Conversion Time | Resolution | Minimum Resolution<br>with no Missing<br>Codes |

|-------------------|----------|-----------------------------|----------------|-----------------|------------|------------------------------------------------|

| -40°C to 100°C    | ±8°C     | No                          | 1 MHz, 500 kHz | < 100 ms        | 8 bits     | 8 bits                                         |

## Table 2-38: External Temperature Sensing Diode Specifications for Arria V GZ Devices

| Description                              | Min | Тур | Max | Unit |

|------------------------------------------|-----|-----|-----|------|

| I <sub>bias</sub> , diode source current | 8   | —   | 200 | μΑ   |

| V <sub>bias,</sub> voltage across diode  | 0.3 | _   | 0.9 | V    |

| Series resistance                        |     |     | < 1 | Ω    |

#### Table 2-55: DCLK-to-DATA[] Ratio for Arria V GZ Devices

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the data rate in bytes per second (Bps), or words per second (Wps). For example, in FPP ×16 when the DCLK-to-DATA[] ratio is 2, the DCLK frequency must be 2 times the data rate in Wps. Arria V GZ devices use the additional clock cycles to decrypt and decompress the configuration data.

| Configuration Scheme | Decompression | Design Security | DCLK-to-DATA[] Ratio |

|----------------------|---------------|-----------------|----------------------|

| FPP ×8               | Disabled      | Disabled        | 1                    |

|                      | Disabled      | Enabled         | 1                    |

|                      | Enabled       | Disabled        | 2                    |

|                      | Enabled       | Enabled         | 2                    |

|                      | Disabled      | Disabled        | 1                    |

| FPP ×16              | Disabled      | Enabled         | 2                    |

| 111 ×10              | Enabled       | Disabled        | 4                    |

|                      | Enabled       | Enabled         | 4                    |

|                      | Disabled      | Disabled        | 1                    |

| FPP ×32              | Disabled      | Enabled         | 4                    |

| 111 / 52             | Enabled       | Disabled        | 8                    |

|                      | Enabled       | Enabled         | 8                    |

# FPP Configuration Timing when DCLK to DATA[] > 1

### Figure 2-8: FPP Configuration Timing Waveform When the DCLK-to-DATA[] Ratio is >1,

t<sub>CF2ST1</sub> tcfg ;↔ nCONFIG ŤĊF2CK nSTATUS (3) 🕳 tstatus tCF2ST0 CONF\_DONE (4) TCL tCH tsT2CK ŤĊF2CD (8) DCLK (6) (7) 1 2 ••• r 2 ••• r 1  $\mathbf{D}$ (5) tCLK DATA[31..0] (8) Word 0 Word User Mode Word 3 • • • Word (n-1) tDH tDH tpsy High-Z User I/O User Mode INIT DONE (9) tCD2UM

Timing when using a MAX II device, MAX V device, or microprocessor as an external host.

#### Notes:

- 1. To find out the DCLK-to-DATA[] ratio for your system, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 2. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 3. After power-up, the Arria V GZ device holds nSTATUS low for the time as specified by the POR delay.

- 4. After power-up, before and during configuration, CONF\_DONE is low.

- 5. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 6. "r" denotes the DCLK-to-DATA[] ratio. For the DCLK-to-DATA[] ratio based on the decompression and the design security feature enable settings, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 7. If needed, pause DCLK by holding it low. When DCLK restarts, the external host must provide data on the DATA[31.0] pins prior to sending the first DCLK rising edge.

- 8. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high after the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 9. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.