### Intel - 5AGXFA7H4F35C4N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 11460                                                      |

| Number of Logic Elements/Cells | 242000                                                     |

| Total RAM Bits                 | 15470592                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxfa7h4f35c4n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Figure 1-1: Equation for OCT Variation Without Recalibration

$$R_{OCT} = R_{SCAL} \left( 1 + \left( \frac{dR}{dT} \times \Delta T \right) \pm \left( \frac{dR}{dV} \times \Delta V \right) \right)$$

The definitions for the equation are as follows:

- The R<sub>OCT</sub> value calculated shows the range of OCT resistance with the variation of temperature and V<sub>CCIO</sub>.

- R<sub>SCAL</sub> is the OCT resistance value at power-up.

- $\Delta T$  is the variation of temperature with respect to the temperature at power up.

- $\Delta V$  is the variation of voltage with respect to the V<sub>CCIO</sub> at power up.

- dR/dT is the percentage change of R<sub>SCAL</sub> with temperature.

- dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

### OCT Variation after Power-Up Calibration

### Table 1-10: OCT Variation after Power-Up Calibration for Arria V Devices

This table lists OCT variation with temperature and voltage after power-up calibration. The OCT variation is valid for a  $V_{CCIO}$  range of  $\pm 5\%$  and a temperature range of 0°C to 85°C.

| Symbol | Description                                      | V <sub>CCIO</sub> (V) | Value | Unit |

|--------|--------------------------------------------------|-----------------------|-------|------|

|        |                                                  | 3.0                   | 0.100 |      |

|        |                                                  | 2.5                   | 0.100 |      |

|        | OCT variation with voltage without recalibration | 1.8                   | 0.100 |      |

| dR/dV  |                                                  | 1.5                   | 0.100 | %/mV |

|        |                                                  | 1.35                  | 0.150 |      |

|        |                                                  | 1.25                  | 0.150 |      |

|        |                                                  | 1.2                   | 0.150 |      |

| Symbol                    | Description                                  | Maximum | Unit |

|---------------------------|----------------------------------------------|---------|------|

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver (RX) pin | 50      | mA   |

### Internal Weak Pull-Up Resistor

All I/O pins, except configuration, test, and JTAG pins, have an option to enable weak pull-up.

### Table 1-13: Internal Weak Pull-Up Resistor Values for Arria V Devices

| Symbol          | Description                           | Condition (V) <sup>(11)</sup> | Value <sup>(12)</sup> | Unit |

|-----------------|---------------------------------------|-------------------------------|-----------------------|------|

|                 |                                       | $V_{CCIO} = 3.3 \pm 5\%$      | 25                    | kΩ   |

|                 |                                       | $V_{CCIO} = 3.0 \pm 5\%$      | 25                    | kΩ   |

|                 |                                       | $V_{CCIO} = 2.5 \pm 5\%$      | 25                    | kΩ   |

| R <sub>PU</sub> |                                       | $V_{CCIO} = 1.8 \pm 5\%$      | 25                    | kΩ   |

| Кру             | programmable pull-up resistor option. | $V_{CCIO} = 1.5 \pm 5\%$      | 25                    | kΩ   |

|                 |                                       | $V_{CCIO} = 1.35 \pm 5\%$     | 25                    | kΩ   |

|                 |                                       | $V_{CCIO} = 1.25 \pm 5\%$     | 25                    | kΩ   |

|                 |                                       | $V_{CCIO} = 1.2 \pm 5\%$      | 25                    | kΩ   |

### **Related Information**

### Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

<sup>(10)</sup> The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

$<sup>^{(11)}</sup>$  Pin pull-up resistance values may be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

<sup>&</sup>lt;sup>(12)</sup> Valid with  $\pm 10\%$  tolerances to cover changes over PVT.

### Table 1-38: Memory Block Performance Specifications for Arria V Devices

| Momony        | Memory Mode -                                                                                           |       | Resources Used |          | Performance | Unit |      |

|---------------|---------------------------------------------------------------------------------------------------------|-------|----------------|----------|-------------|------|------|

| Memory        | Mode                                                                                                    | ALUTs | Memory         | -I3, -C4 | –I5, –C5    | -C6  | Onit |

|               | Single port, all supported widths                                                                       | 0     | 1              | 500      | 450         | 400  | MHz  |

|               | Simple dual-port, all supported widths                                                                  | 0     | 1              | 500      | 450         | 400  | MHz  |

| MLAB          | Simple dual-port with read and write at the same address                                                | 0     | 1              | 400      | 350         | 300  | MHz  |

|               | ROM, all supported width                                                                                |       |                | 500      | 450         | 400  | MHz  |

|               | Single-port, all supported widths                                                                       | 0     | 1              | 400      | 350         | 285  | MHz  |

|               | Simple dual-port, all supported widths                                                                  | 0     | 1              | 400      | 350         | 285  | MHz  |

| M10K<br>Block | Simple dual-port with the read-during-<br>write option set to <b>Old Data</b> , all supported<br>widths | 0     | 1              | 315      | 275         | 240  | MHz  |

|               | True dual port, all supported widths                                                                    | 0     | 1              | 400      | 350         | 285  | MHz  |

|               | ROM, all supported widths                                                                               | 0     | 1              | 400      | 350         | 285  | MHz  |

## **Internal Temperature Sensing Diode Specifications**

### Table 1-39: Internal Temperature Sensing Diode Specifications for Arria V Devices

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate | Conversion<br>Time | Resolution | Minimum Resolution with no<br>Missing Codes |

|-------------------|----------|-----------------------------|---------------|--------------------|------------|---------------------------------------------|

| -40 to 100°C      | ±8°C     | No                          | 1 MHz         | < 100 ms           | 8 bits     | 8 bits                                      |

## **Periphery Performance**

This section describes the periphery performance, high-speed I/O, and external memory interface.

Actual achievable frequency depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

| Symbol                                                                                                           | Condition                                                                                    |     | -I3, -C4 |      | –I5, –C5 |     | -C6  |     |     | Unit |      |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|----------|------|----------|-----|------|-----|-----|------|------|

| Symbol                                                                                                           | Condition                                                                                    | Min | Тур      | Max  | Min      | Тур | Мах  | Min | Тур | Max  | Unit |

| t <sub>x Jitter</sub> -Emulated<br>Differential I/O<br>Standards with Three                                      | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps                                        | _   | -        | 260  |          | _   | 300  | _   | _   | 350  | ps   |

| External Output Resistor<br>Network                                                                              | Total Jitter for Data<br>Rate < 600 Mbps                                                     | —   | _        | 0.16 |          | _   | 0.18 | _   |     | 0.21 | UI   |

| t <sub>x Jitter</sub> -Emulated<br>Differential I/O<br>Standards with One<br>External Output<br>Resistor Network | _                                                                                            |     |          | 0.15 |          |     | 0.15 |     |     | 0.15 | UI   |

| t <sub>DUTY</sub>                                                                                                | TX output clock duty<br>cycle for both True<br>and Emulated<br>Differential I/O<br>Standards | 45  | 50       | 55   | 45       | 50  | 55   | 45  | 50  | 55   | %    |

|                                                                                                                  | True Differential I/O<br>Standards <sup>(82)</sup>                                           | _   | _        | 160  |          |     | 180  | _   |     | 200  | ps   |

| t <sub>RISE</sub> and t <sub>FALL</sub>                                                                          | Emulated Differential<br>I/O Standards with<br>Three External Output<br>Resistor Network     | _   |          | 250  |          |     | 250  |     |     | 300  | ps   |

|                                                                                                                  | Emulated Differential<br>I/O Standards with<br>One External Output<br>Resistor Network       |     |          | 500  |          | _   | 500  |     |     | 500  | ps   |

$<sup>^{(82)}\,</sup>$  This applies to default pre-emphasis and  $V_{OD}$  settings only.

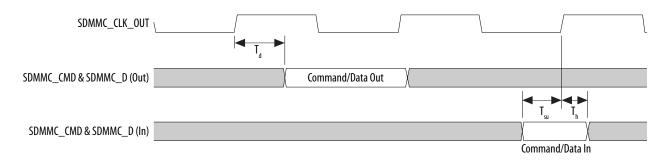

After the Boot ROM code exits and control is passed to the preloader, software can adjust the value of drvsel and smplsel via the system manager. drvsel can be set from 1 to 7 and smplsel can be set from 0 to 7. While the preloader is executing, the values for SDMMC\_CLK and SDMMC\_CLK\_OUT increase to a maximum of 200 MHz and 50 MHz respectively.

The SD/MMC interface calibration support will be available in a future release of the preloader through the SoC EDS software update.

| Symbol                                              | Description                                         | Min                                                         | Мах                                                                                                  | Unit |

|-----------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|

|                                                     | SDMMC_CLK clock period (Identification mode)        | 20                                                          | _                                                                                                    | ns   |

| T <sub>sdmmc_clk</sub> (internal reference clock)   | SDMMC_CLK clock period<br>(Default speed mode)      | 5                                                           | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK clock period<br>(High speed mode)         | 5                                                           | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK_OUT clock<br>period (Identification mode) | 2500                                                        | _                                                                                                    | ns   |

| T <sub>sdmmc_clk_out</sub> (interface output clock) | SDMMC_CLK_OUT clock period (Default speed mode)     | 40                                                          | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK_OUT clock<br>period (High speed mode)     | 20                                                          | _                                                                                                    | ns   |

| T <sub>dutycycle</sub>                              | SDMMC_CLK_OUT duty cycle                            | 45                                                          | 55                                                                                                   | %    |

| T <sub>d</sub>                                      | SDMMC_CMD/SDMMC_D<br>output delay                   | $\frac{(T_{sdmmc\_clk} \times drvsel)/2}{-1.23}$            | $\begin{array}{c} (\mathrm{T}_{sdmmc\_clk} \times \texttt{drvsel})/2 \\ + 1.69^{\ (87)} \end{array}$ | ns   |

| T <sub>su</sub>                                     | Input setup time                                    | $1.05 - (T_{sdmmc_clk} \times smplsel)/2^{(88)}$            |                                                                                                      | ns   |

| T <sub>h</sub>                                      | Input hold time                                     | $\frac{(T_{sdmmc\_clk} \times \texttt{smplsel})}{2^{(88)}}$ | —                                                                                                    | ns   |

<sup>&</sup>lt;sup>(87)</sup> drvsel is the drive clock phase shift select value.

<sup>&</sup>lt;sup>(88)</sup> smplsel is the sample clock phase shift select value.

### Figure 1-11: SD/MMC Timing Diagram

### **Related Information**

**Booting and Configuration Chapter, Arria V Hard Processor System Technical Reference Manual** Provides more information about CSEL pin settings in the SD/MMC Controller CSEL Pin Settings table.

### **USB Timing Characteristics**

PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.

### Table 1-55: USB Timing Requirements for Arria V Devices

| Symbol           | Description                                                | Min | Тур   | Мах | Unit |

|------------------|------------------------------------------------------------|-----|-------|-----|------|

| T <sub>clk</sub> | USB CLK clock period                                       | _   | 16.67 | _   | ns   |

| T <sub>d</sub>   | CLK to USB_STP/USB_DATA[7:0] output delay                  | 4.4 | —     | 11  | ns   |

| T <sub>su</sub>  | Setup time for USB_DIR/USB_NXT/USB_DATA[7:0]               |     | _     |     | ns   |

| T <sub>h</sub>   | T <sub>h</sub> Hold time for USB_DIR/USB_NXT/USB_DATA[7:0] |     | —     |     | ns   |

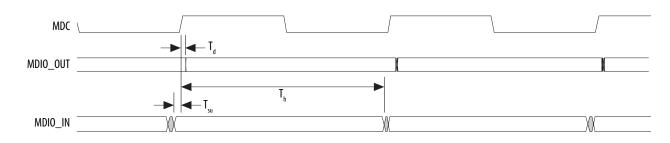

## Figure 1-15: MDIO Timing Diagram

## I<sup>2</sup>C Timing Characteristics

## Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Symbol                | Symbol Description –                              |      | Standard Mode |     | Mode | Unit |  |

|-----------------------|---------------------------------------------------|------|---------------|-----|------|------|--|

| Symbol                | Description                                       | Min  | Max           | Min | Max  | Onit |  |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10   | —             | 2.5 | _    | μs   |  |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7  | —             | 0.6 |      | μs   |  |

| T <sub>clklow</sub>   | SCL low time                                      | 4    | _             | 1.3 |      | μs   |  |

| T <sub>s</sub>        | Setup time for serial data line (SDA) data to SCL | 0.25 | —             | 0.1 | —    | μs   |  |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0    | 3.45          | 0   | 0.9  | μs   |  |

| T <sub>d</sub>        | SCL to SDA output data delay                      | —    | 0.2           | _   | 0.2  | μs   |  |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7  | _             | 0.6 | _    | μs   |  |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4    | —             | 0.6 | _    | μs   |  |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4    | —             | 0.6 | —    | μs   |  |

| Variant    | Member Code | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) |

|------------|-------------|--------------------------------|------------------------|

|            | A1          | 71,015,712                     | 439,960                |

|            | A3          | 71,015,712                     | 439,960                |

|            | A5          | 101,740,800                    | 446,360                |

| Arria V GX | A7          | 101,740,800                    | 446,360                |

| Allia V GA | B1          | 137,785,088                    | 457,368                |

|            | B3          | 137,785,088                    | 457,368                |

|            | B5          | 185,915,808                    | 463,128                |

|            | B7          | 185,915,808                    | 463,128                |

|            | C3          | 71,015,712                     | 439,960                |

| Arria V GT | C7          | 101,740,800                    | 446,360                |

| Allia v GI | D3          | 137,785,088                    | 457,368                |

|            | D7          | 185,915,808                    | 463,128                |

| Arria V SX | B3          | 185,903,680                    | 450,968                |

| Allia v SA | B5          | 185,903,680                    | 450,968                |

| Arria V ST | D3          | 185,903,680                    | 450,968                |

| 7111a V 51 | D5          | 185,903,680                    | 450,968                |

## **Minimum Configuration Time Estimation**

### Table 1-73: Minimum Configuration Time Estimation for Arria V Devices

The estimated values are based on the configuration .rbf sizes in Uncompressed .rbf Sizes for Arria V Devices table.

| 1-88 Glossary       |                                  |             | AV-5100<br>2017.02.1 |

|---------------------|----------------------------------|-------------|----------------------|

| Symbol              | Parameter                        | Typical     | Unit                 |

|                     |                                  | 0 (default) | ps                   |

| D                   | Rising and/or falling edge delay | 50          | ps                   |

| D <sub>OUTBUF</sub> |                                  | 100         | ps                   |

|                     |                                  | 150         | ps                   |

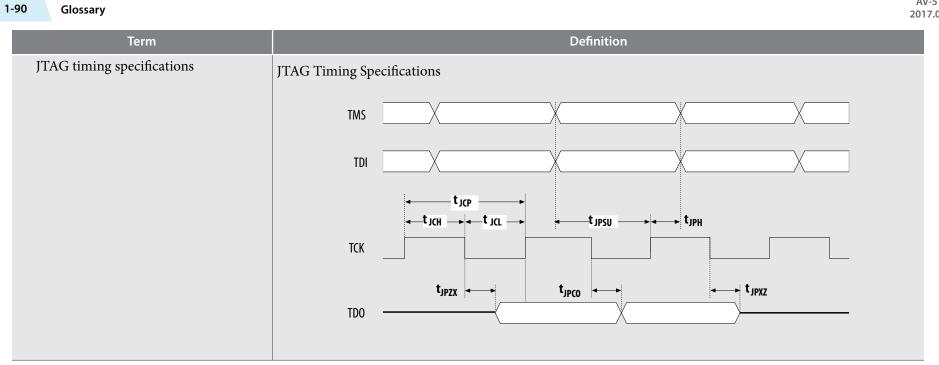

# Glossary

## Table 1-78: Glossary

| Term                       | Definition                                                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Differential I/O standards | Receiver Input Waveforms                                                                                                    |

|                            | Single-Ended Waveform $V_{ID}$ Positive Channel (p) = $V_{IH}$ $V_{CM}$ Negative Channel (n) = $V_{IL}$ Ground       Ground |

|                            | Differential Waveform<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$v_{ID}$                                                       |

### 1-98 Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.8     | <ul> <li>Added a note in Table 3, Table 4, and Table 5: The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.</li> <li>Updated V<sub>CC_HPS</sub> specification in Table 5.</li> <li>Added a note in Table 19: Differential inputs are powered by V<sub>CCPD</sub> which requires 2.5 V.</li> <li>Updated "Minimum differential eye opening at the receiver serial input pins" specification in Table 20 and Table 21.</li> <li>Updated description in "HPS PLL Specifications" section.</li> <li>Updated VCO range maximum specification in Table 39.</li> <li>Updated T<sub>h</sub> and T<sub>h</sub> specifications in Table 45.</li> <li>Added T<sub>h</sub> specification in Table 47 and Figure 13.</li> <li>Updated a note in Figure 20, Figure 21, and Figure 23 as follows: Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.</li> <li>Removed "Remote update only in AS mode" specification in Table 58.</li> <li>Added DCLK device initialization clock source specification in Table 60.</li> <li>Added description in "Configuration Files" section: The IOCSR .rbf size is specifically for the Configuration via Protocol (CvP) feature.</li> <li>Removed f<sub>MAX_RU_CLK</sub> specification in Table 63.</li> </ul> |

| February 2014 | 3.7     | <ul> <li>Updated V<sub>CCRSTCLK_HPS</sub> maximum specification in Table 1.</li> <li>Added V<sub>CC_AUX_SHARED</sub> specification in Table 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| December 2013 | 3.6     | <ul> <li>Added "HPS PLL Specifications".</li> <li>Added Table 24, Table 39, and Table 40.</li> <li>Updated Table 1, Table 3, Table 5, Table 19, Table 20, Table 21, Table 38, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, Table 50, Table 51, Table 55, Table 56, and Table 59.</li> <li>Updated Figure 7, Figure 13, Figure 15, Figure 16, and Figure 19.</li> <li>Removed table: GPIO Pulse Width for Arria V Devices.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Date        | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2013 | 3.5     | <ul><li>Removed "Pending silicon characterization" note in Table 29.</li><li>Updated Table 25.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| August 2013 | 3.4     | <ul> <li>Removed Preliminary tags for Table 1, Table 2, Table 3, Table 4, Table 5, Table 6, Table 7, Table 9, Table 12, Table 13, Table 14, Table 15, Table 16, Table 17, Table 18, Table 19, Table 20, Table 21, Table 22, Table 23, Table 24, Table 25, Table 26, Table 27, Table 28, Table 29, Table 30, Table 31, Table 35, Table 36, Table 51, Table 53, Table 54, Table 55, Table 56, Table 57, Table 60, Table 62, and Table 64.</li> <li>Updated Table 1, Table 3, Table 11, Table 19, Table 20, Table 21, Table 22, Table 25, and Table 29.</li> </ul> |

| June 2013   | 3.3     | Updated Table 20, Table 21, Table 25, and Table 38.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| May 2013    | 3.2     | <ul> <li>Added Table 37.</li> <li>Updated Figure 8, Figure 9, Figure 20, Figure 22, and Figure 23.</li> <li>Updated Table 1, Table 5, Table 10, Table 13, Table 19, Table 20, Table 21, Table 23, Table 29, Table 39, Table 40, Table 46, Table 56, Table 57, Table 60, and Table 64.</li> <li>Updated industrial junction temperature range for -I3 speed grade in "PLL Specifications" section.</li> </ul>                                                                                                                                                    |

| March 2013  | 3.1     | <ul> <li>Added HPS reset information in the "HPS Specifications" section.</li> <li>Added Table 60.</li> <li>Updated Table 1, Table 3, Table 17, Table 20, Table 29, and Table 59.</li> <li>Updated Figure 21.</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

### 2-2 Absolute Maximum Ratings

Lower number refers to faster speed grade.

L = Low power devices.

| Transceiver Speed Grade | Core Speed Grade |     |     |     |  |  |  |

|-------------------------|------------------|-----|-----|-----|--|--|--|

| Transceiver speeu Graue | C3               | C4  | I3L | 14  |  |  |  |

| 2                       | Yes              | _   | Yes | -   |  |  |  |

| 3                       |                  | Yes |     | Yes |  |  |  |

### **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Arria V GZ devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied for these conditions.

**Caution:** Conditions other than those listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

### Table 2-2: Absolute Maximum Ratings for Arria V GZ Devices

| Symbol                | Description                                                            | Minimum | Maximum | Unit |

|-----------------------|------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>       | Power supply for core voltage and periphery circuitry                  | -0.5    | 1.35    | V    |

| V <sub>CCPT</sub>     | Power supply for programmable power technology                         | -0.5    | 1.8     | V    |

| V <sub>CCPGM</sub>    | Power supply for configuration pins                                    | -0.5    | 3.9     | V    |

| V <sub>CC_AUX</sub>   | Auxiliary supply for the programmable power technology                 | -0.5    | 3.4     | V    |

| V <sub>CCBAT</sub>    | Battery back-up power supply for design security volatile key register | -0.5    | 3.9     | V    |

| V <sub>CCPD</sub>     | I/O pre-driver power supply                                            | -0.5    | 3.9     | V    |

| V <sub>CCIO</sub>     | I/O power supply                                                       | -0.5    | 3.9     | V    |

| V <sub>CCD_FPLL</sub> | PLL digital power supply                                               | -0.5    | 1.8     | V    |

| V <sub>CCA_FPLL</sub> | PLL analog power supply                                                | -0.5    | 3.4     | V    |

| Symbol               | Description                                                            | Conditions                 | Resistance | Unit   |   |

|----------------------|------------------------------------------------------------------------|----------------------------|------------|--------|---|

| Symbol               | Description                                                            | Conditions                 | C3, I3L    | C4, I4 |   |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | % |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | % |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | % |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | % |

| 100-Ω R <sub>D</sub> | Internal differential termination (100- $\Omega$ setting)              | $V_{CCIO} = 2.5 V$         | ±25        | ±25    | % |

### Figure 2-1: OCT Variation Without Re-Calibration for Arria V GZ Devices

$$\mathbf{R}_{\text{OCT}} = \mathbf{R}_{\text{SCAL}} \left( 1 + \left( \frac{dR}{dT} \times \bigtriangleup T \right) \pm \left( \frac{dR}{dV} \times \bigtriangleup V \right) \right)$$

Notes:

1. The  $R_{oct}$  value shows the range of OCT resistance with the variation of temperature and  $V_{ccio}$ . 2.  $R_{scAL}$  is the OCT resistance value at power-up. 3.  $\Delta T$  is the variation of temperature with respect to the temperature at power-up. 4.  $\Delta V$  is the variation of voltage with respect to the  $V_{ccio}$  at power-up. 5. dR/dT is the percentage change of  $R_{scAL}$  with temperature. 6. dR/dV is the percentage change of  $R_{scAL}$  with voltage

6. dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

## Table 2-12: OCT Variation after Power-Up Calibration for Arria V GZ Devices

Valid for a V<sub>CCIO</sub> range of  $\pm$ 5% and a temperature range of 0° to 85°C.

## I/O Standard Specifications

The  $V_{OL}$  and  $V_{OH}$  values are valid at the corresponding  $I_{OH}$  and  $I_{OL}$ , respectively.

### Table 2-16: Single-Ended I/O Standards for Arria V GZ Devices

| I/O Standard |       | V <sub>CCIO</sub> (V) |       | VII  | _ (V)                     | V <sub>IH</sub>             | (V)                        | V <sub>OL</sub> (V)         | V <sub>OH</sub> (V)      | l <sub>OL</sub> (mA) | l <sub>OH</sub> (mA) |

|--------------|-------|-----------------------|-------|------|---------------------------|-----------------------------|----------------------------|-----------------------------|--------------------------|----------------------|----------------------|

|              | Min   | Тур                   | Max   | Min  | Max                       | Min                         | Max                        | Max                         | Min                      | 10L (IIIA)           | 10H (1117)           |

| LVTTL        | 2.85  | 3                     | 3.15  | -0.3 | 0.8                       | 1.7                         | 3.6                        | 0.4                         | 2.4                      | 2                    | -2                   |

| LVCMOS       | 2.85  | 3                     | 3.15  | -0.3 | 0.8                       | 1.7                         | 3.6                        | 0.2                         | V <sub>CCIO</sub> – 0.2  | 0.1                  | -0.1                 |

| 2.5 V        | 2.375 | 2.5                   | 2.625 | -0.3 | 0.7                       | 1.7                         | 3.6                        | 0.4                         | 2                        | 1                    | -1                   |

| 1.8 V        | 1.71  | 1.8                   | 1.89  | -0.3 | $0.35 \times V_{ m CCIO}$ | 0.65 ×<br>V <sub>CCIO</sub> | V <sub>CCIO</sub><br>+ 0.3 | 0.45                        | V <sub>CCIO</sub> - 0.45 | 2                    | -2                   |

| 1.5 V        | 1.425 | 1.5                   | 1.575 | -0.3 | $0.35 \times V_{ m CCIO}$ | 0.65 ×<br>V <sub>CCIO</sub> | V <sub>CCIO</sub><br>+ 0.3 | $0.25 	imes V_{ m CCIO}$    | $0.75 \times V_{CCIO}$   | 2                    | -2                   |

| 1.2 V        | 1.14  | 1.2                   | 1.26  | -0.3 | $0.35 \times V_{ m CCIO}$ | 0.65 ×<br>V <sub>CCIO</sub> | V <sub>CCIO</sub><br>+ 0.3 | 0.25 ×<br>V <sub>CCIO</sub> | $0.75 \times V_{CCIO}$   | 2                    | -2                   |

## Table 2-17: Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Arria V GZ Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       |                        | V <sub>REF</sub> (V)    |                           |                            | V <sub>TT</sub> (V) |                         |  |

|------------------------|-------|-----------------------|-------|------------------------|-------------------------|---------------------------|----------------------------|---------------------|-------------------------|--|

| I/O Standard           | Min   | Тур                   | Max   | Min                    | Тур                     | Max                       | Min                        | Тур                 | Max                     |  |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                   | 2.625 | $0.49 \times V_{CCIO}$ | $0.5 	imes V_{ m CCIO}$ | $0.51 \times V_{ m CCIO}$ | V <sub>REF</sub> - 0.04    | V <sub>REF</sub>    | V <sub>REF</sub> + 0.04 |  |

| SSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.833                  | 0.9                     | 0.969                     | V <sub>REF</sub> - 0.04    | V <sub>REF</sub>    | V <sub>REF</sub> + 0.04 |  |

| SSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | $0.49 \times V_{CCIO}$ | $0.5 	imes V_{ m CCIO}$ | $0.51 \times V_{ m CCIO}$ | $0.49 \times V_{\rm CCIO}$ | 0.5 ×<br>VCCIO      | $0.51 \times V_{CCIO}$  |  |

| Memory        | Mode                                                                                             | Resou | rces Used |     | Unit |     |     |     |

|---------------|--------------------------------------------------------------------------------------------------|-------|-----------|-----|------|-----|-----|-----|

| метногу       | imoue                                                                                            | ALUTs | Memory    | C3  | C4   | I3L | 14  |     |

|               | Single-port, all supported widths                                                                | 0     | 1         | 650 | 550  | 500 | 450 | MHz |

|               | Simple dual-port, all supported widths                                                           | 0     | 1         | 650 | 550  | 500 | 450 | MHz |

|               | Simple dual-port with the read-during-write option set to <b>Old Data</b> , all supported widths | 0     | 1         | 455 | 400  | 455 | 400 | MHz |

| M20K<br>Block | Simple dual-port with ECC enabled, $512 \times 32$                                               | 0     | 1         | 400 | 350  | 400 | 350 | MHz |

| DIOCK         | Simple dual-port with ECC and optional pipeline registers enabled, 512 × 32                      | 0     | 1         | 500 | 450  | 500 | 450 | MHz |

|               | True dual port, all supported widths                                                             | 0     | 1         | 650 | 550  | 500 | 450 | MHz |

|               | ROM, all supported widths                                                                        | 0     | 1         | 650 | 550  | 500 | 450 | MHz |

## **Temperature Sensing Diode Specifications**

## Table 2-37: Internal Temperature Sensing Diode Specification

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate  | Conversion Time | Resolution | Minimum Resolution<br>with no Missing<br>Codes |

|-------------------|----------|-----------------------------|----------------|-----------------|------------|------------------------------------------------|

| -40°C to 100°C    | ±8°C     | No                          | 1 MHz, 500 kHz | < 100 ms        | 8 bits     | 8 bits                                         |

## Table 2-38: External Temperature Sensing Diode Specifications for Arria V GZ Devices

| Description                              | Min | Тур | Max | Unit |

|------------------------------------------|-----|-----|-----|------|

| I <sub>bias</sub> , diode source current | 8   | —   | 200 | μΑ   |

| V <sub>bias,</sub> voltage across diode  | 0.3 | _   | 0.9 | V    |

| Series resistance                        | _   |     | < 1 | Ω    |

## **OCT Calibration Block Specifications**

## Table 2-51: OCT Calibration Block Specifications for Arria V GZ Devices

| Symbol                | Description                                                                                                                                                               | Min | Тур  | Мах | Unit   |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by the OCT calibration blocks                                                                                                                              | _   |      | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of OCTUSRCLK clock cycles required for OCT R <sub>S</sub> /R <sub>T</sub> calibration                                                                              | _   | 1000 |     | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for the OCT code to shift out                                                                                                   | _   | 32   |     | Cycles |

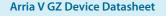

| T <sub>RS_RT</sub>    | Time required between the dyn_term_ctrl and oe signal transitions in a bidirectional I/O buffer to dynamically switch between OCT $R_S$ and $R_T$ (See the figure below.) |     | 2.5  |     | ns     |

## Figure 2-6: Timing Diagram for oe and dyn\_term\_ctrl Signals

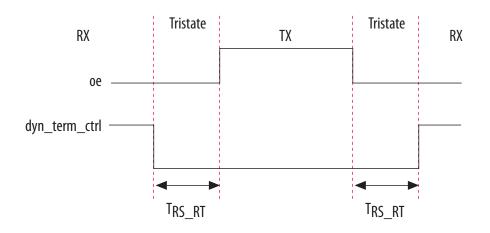

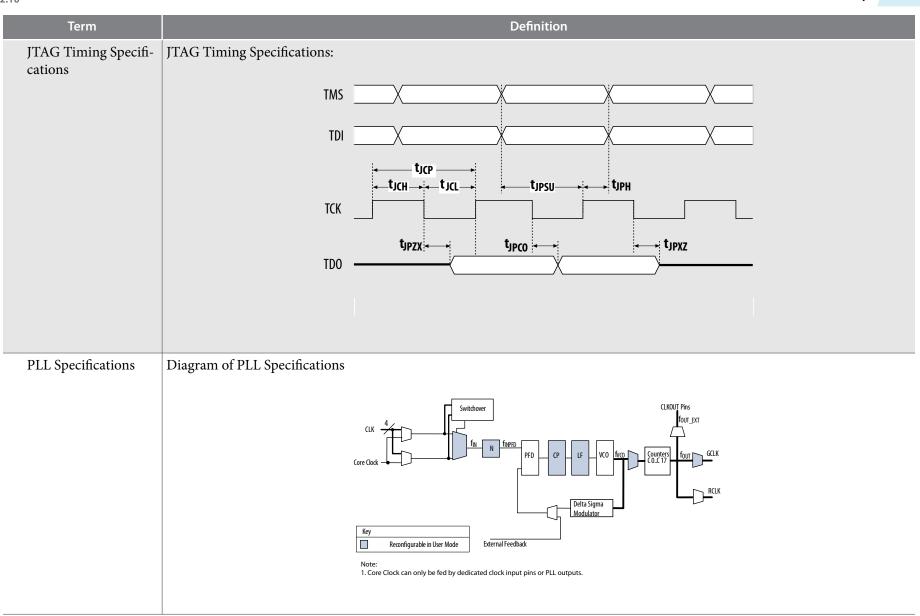

| Term                               | Definition                                                                                                                                                                                                                                                                 |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| t <sub>C</sub>                     | High-speed receiver and transmitter input and output clock period.                                                                                                                                                                                                         |  |  |

| TCCS (channel-to-<br>channel-skew) | The timing difference between the fastest and slowest output edges, including t <sub>CO</sub> variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table). |  |  |

| t <sub>DUTY</sub>                  | High-speed I/O block—Duty cycle on the high-speed transmitter output clock.                                                                                                                                                                                                |  |  |

| t <sub>FALL</sub>                  | Signal high-to-low transition time (80-20%)                                                                                                                                                                                                                                |  |  |

| t <sub>INCCJ</sub>                 | Cycle-to-cycle jitter tolerance on the PLL clock input.                                                                                                                                                                                                                    |  |  |

| t <sub>OUTPJ_IO</sub>              | Period jitter on the general purpose I/O driven by a PLL.                                                                                                                                                                                                                  |  |  |

| t <sub>OUTPJ_DC</sub>              | Period jitter on the dedicated clock output driven by a PLL.                                                                                                                                                                                                               |  |  |

| t <sub>RISE</sub>                  | Signal low-to-high transition time (20-80%)                                                                                                                                                                                                                                |  |  |

| Timing Unit Interval<br>(TUI)      | The timing budget allowed for skew, propagation delays, and the data sampling window.<br>(TUI = $1/(\text{receiver input clock frequency multiplication factor}) = t_C/w)$                                                                                                 |  |  |

| V <sub>CM(DC)</sub>                | DC common mode input voltage.                                                                                                                                                                                                                                              |  |  |

| V <sub>ICM</sub>                   | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                                                                                                                      |  |  |

| V <sub>ID</sub>                    | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                                                                                               |  |  |

| V <sub>DIF(AC)</sub>               | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                                                                                                                                |  |  |

| V <sub>DIF(DC)</sub>               | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                                                                                                                               |  |  |

| V <sub>IH</sub>                    | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                                                                                                                      |  |  |

| V <sub>IH(AC)</sub>                | High-level AC input voltage                                                                                                                                                                                                                                                |  |  |

| V <sub>IH(DC)</sub>                | High-level DC input voltage                                                                                                                                                                                                                                                |  |  |

| V <sub>IL</sub>                    | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                                                                                                                        |  |  |

| V <sub>IL(AC)</sub>                | Low-level AC input voltage                                                                                                                                                                                                                                                 |  |  |

| V <sub>IL(DC)</sub>                | Low-level DC input voltage                                                                                                                                                                                                                                                 |  |  |

Altera Corporation

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.8     | <ul> <li>Updated Table 21.</li> <li>Updated Table 22 V<sub>OCM</sub> (DC Coupled) condition.</li> <li>Updated the DCLK note to Figure 6, Figure 7, and Figure 9.</li> <li>Added note to Table 5 and Table 6.</li> <li>Added the DCLK specification to Table 50.</li> <li>Added note to Table 51.</li> <li>Updated the list of parameters in Table 53.</li> </ul> |

| February 2014 | 3.7     | Updated Table 28.                                                                                                                                                                                                                                                                                                                                                |

| December 2013 | 3.6     | <ul> <li>Updated Table 2, Table 13, Table 18, Table 19, Table 22, Table 30, Table 33, Table 37, Table 38, Table 45, Table 46, Table 47, Table 56, Table 49.</li> <li>Updated "PLL Specifications".</li> </ul>                                                                                                                                                    |

| August 2013   | 3.5     | Updated Table 28.                                                                                                                                                                                                                                                                                                                                                |

| August 2013   | 3.4     | <ul> <li>Removed Preliminary tags for Table 2, Table 4, Table 5, Table 14, Table 27, Table 28, Table 29, Table 31, Table 32, Table 43, Table 45, Table 46, Table 47, Table 48, Table 49, Table 50, and Table 54.</li> <li>Updated Table 2 and Table 28.</li> </ul>                                                                                               |

| June 2013     | 3.3     | Updated Table 23, Table 28, Table 51, and Table 55.                                                                                                                                                                                                                                                                                                              |

| May 2013      | 3.2     | <ul> <li>Added Table 23.</li> <li>Updated Table 5, Table 22, Table 26, and Table 57.</li> <li>Updated Figure 6, Figure 7, Figure 8, and Figure 9.</li> </ul>                                                                                                                                                                                                     |

| March 2013    | 3.1     | <ul> <li>Updated Table 2, Table 6, Table 7, Table 8, Table 19, Table 22, Table 26, Table 29, Table 52.</li> <li>Updated "Maximum Allowed Overshoot and Undershoot Voltage".</li> </ul>                                                                                                                                                                           |

| December 2012 | 3.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                 |