Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 11460                                                      |

| Number of Logic Elements/Cells | 242000                                                     |

| Total RAM Bits                 | 15470592                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.12V ~ 1.18V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxfa7h4f35i3g |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### I/O Pin Leakage Current

Table 1-6: I/O Pin Leakage Current for Arria V Devices

| Symbol           | Description        | Condition                             | Min | Тур | Max | Unit |

|------------------|--------------------|---------------------------------------|-----|-----|-----|------|

| $I_{\mathrm{I}}$ | Input pin          | $V_{I} = 0 V \text{ to } V_{CCIOMAX}$ | -30 | _   | 30  | μΑ   |

| $I_{OZ}$         | Tri-stated I/O pin | $V_O = 0 V \text{ to } V_{CCIOMAX}$   | -30 | _   | 30  | μΑ   |

### **Bus Hold Specifications**

### Table 1-7: Bus Hold Parameters for Arria V Devices

The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

|                                             |                   |                                               |     |      |     |      |     | V <sub>CCI</sub> | <sub>O</sub> (V) |      |     |      |     |      |      |

|---------------------------------------------|-------------------|-----------------------------------------------|-----|------|-----|------|-----|------------------|------------------|------|-----|------|-----|------|------|

| Parameter                                   | Symbol            | Condition                                     | 1   | .2   | 1   | .5   | 1   | .8               | 2                | .5   | 3   | .0   | 3.  | .3   | Unit |

|                                             |                   |                                               | Min | Max  | Min | Max  | Min | Max              | Min              | Max  | Min | Max  | Min | Max  |      |

| Bus-hold,<br>low,<br>sustaining<br>current  | I <sub>SUSL</sub> | $V_{IN} > V_{IL}$ (max)                       | 8   | _    | 12  |      | 30  | _                | 50               | _    | 70  | _    | 70  | _    | μA   |

| Bus-hold,<br>high,<br>sustaining<br>current | I <sub>SUSH</sub> | $V_{IN} < V_{IH}$ (min)                       | -8  | _    | -12 | _    | -30 | _                | -50              | _    | -70 | _    | -70 | _    | μA   |

| Bus-hold,<br>low,<br>overdrive<br>current   | I <sub>ODL</sub>  | 0 V < V <sub>IN</sub><br>< V <sub>CCIO</sub>  | _   | 125  | _   | 175  | _   | 200              | _                | 300  | _   | 500  | _   | 500  | μA   |

| Bus-hold,<br>high,<br>overdrive<br>current  | I <sub>ODH</sub>  | 0 V <v<sub>IN<br/><v<sub>CCIO</v<sub></v<sub> | _   | -125 | _   | -175 | _   | -200             | _                | -300 | _   | -500 | _   | -500 | μA   |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

| Symbol | Description                                          | V <sub>CCIO</sub> (V) | Value | Unit |

|--------|------------------------------------------------------|-----------------------|-------|------|

|        |                                                      | 3.0                   | 0.189 |      |

|        |                                                      | 2.5                   | 0.208 |      |

|        | OCT variation with temperature without recalibration | 1.8                   | 0.266 |      |

| dR/dT  |                                                      | 1.5                   | 0.273 | %/°C |

|        |                                                      | 1.35                  | 0.200 |      |

|        |                                                      | 1.25                  | 0.200 |      |

|        |                                                      | 1.2                   | 0.317 |      |

### Pin Capacitance

Table 1-11: Pin Capacitance for Arria V Devices

| Symbol              | Description                                                  | Maximum | Unit |

|---------------------|--------------------------------------------------------------|---------|------|

| $C_{IOTB}$          | Input capacitance on top/bottom I/O pins                     | 6       | pF   |

| $C_{IOLR}$          | Input capacitance on left/right I/O pins                     | 6       | pF   |

| $C_{OUTFB}$         | Input capacitance on dual-purpose clock output/feedback pins | 6       | pF   |

| C <sub>IOVREF</sub> | Input capacitance on V <sub>REF</sub> pins                   | 48      | pF   |

# **Hot Socketing**

Table 1-12: Hot Socketing Specifications for Arria V Devices

| Symbol                    | Description                                     | Maximum           | Unit |

|---------------------------|-------------------------------------------------|-------------------|------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                          | 300               | μΑ   |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                          | 8 <sup>(10)</sup> | mA   |

| I <sub>XCVR-TX (DC)</sub> | DC current per transceiver transmitter (TX) pin | 100               | mA   |

### Arria V GX, GT, SX, and ST Device Datasheet

### Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications

Table 1-16: Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications for Arria V Devices

| I/O Standard        | V <sub>II</sub> | <sub>-(DC)</sub> (V)     | V <sub>IH(Do</sub>       | <sub>C)</sub> (V)       | V <sub>IL(AC)</sub> (V)  | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)     | V <sub>OH</sub> (V)      | I <sub>OL</sub> <sup>(14)</sup> | I <sub>OH</sub> <sup>(14)</sup> (mA) |

|---------------------|-----------------|--------------------------|--------------------------|-------------------------|--------------------------|--------------------------|-------------------------|--------------------------|---------------------------------|--------------------------------------|

| i/O Standard        | Min             | Max                      | Min                      | Max                     | Max                      | Min                      | Max                     | Min                      | (mA)                            | IOH. (IIIA)                          |

| SSTL-2<br>Class I   | -0.3            | V <sub>REF</sub> - 0.15  | $V_{REF} + 0.15$         | $V_{\rm CCIO} + 0.3$    | V <sub>REF</sub> - 0.31  | $V_{REF} + 0.31$         | V <sub>TT</sub> - 0.608 | $V_{TT} + 0.608$         | 8.1                             | -8.1                                 |

| SSTL-2<br>Class II  | -0.3            | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | $V_{\rm CCIO} + 0.3$    | V <sub>REF</sub> - 0.31  | $V_{REF} + 0.31$         | V <sub>TT</sub> - 0.81  | $V_{TT} + 0.81$          | 16.2                            | -16.2                                |

| SSTL-18<br>Class I  | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | V <sub>TT</sub> - 0.603 | V <sub>TT</sub> + 0.603  | 6.7                             | -6.7                                 |

| SSTL-18<br>Class II | -0.3            | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | $V_{\rm CCIO} + 0.3$    | V <sub>REF</sub> - 0.25  | $V_{REF} + 0.25$         | 0.28                    | V <sub>CCIO</sub> - 0.28 | 13.4                            | -13.4                                |

| SSTL-15<br>Class I  | _               | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> - 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$    | 8                               | -8                                   |

| SSTL-15<br>Class II | _               | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> - 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$    | 16                              | -16                                  |

| SSTL-135            | _               | V <sub>REF</sub> - 0.09  | $V_{REF} + 0.09$         | _                       | V <sub>REF</sub> - 0.16  | $V_{REF} + 0.16$         | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$    | _                               | _                                    |

| SSTL-125            | _               | V <sub>REF</sub> - 0.85  | $V_{REF} + 0.85$         | _                       | V <sub>REF</sub> - 0.15  | $V_{REF} + 0.15$         | $0.2 \times V_{CCIO}$   | $0.8 \times V_{CCIO}$    | _                               | _                                    |

| HSTL-18<br>Class I  | _               | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                     | V <sub>CCIO</sub> - 0.4  | 8                               | -8                                   |

| HSTL-18<br>Class II | _               | V <sub>REF</sub> - 0.1   | $V_{REF} + 0.1$          | _                       | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                     | V <sub>CCIO</sub> - 0.4  | 16                              | -16                                  |

| HSTL-15<br>Class I  | _               | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> – 0.2   | $V_{REF} + 0.2$          | 0.4                     | V <sub>CCIO</sub> - 0.4  | 8                               | -8                                   |

To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

| Symbol/Description                          | Condition                                                     | Т           | ransceiver Speed Gr                                                            | - Unit |       |  |

|---------------------------------------------|---------------------------------------------------------------|-------------|--------------------------------------------------------------------------------|--------|-------|--|

| Symbol/Description                          | Condition                                                     | Min         | Тур                                                                            | Max    | Offic |  |

| $t_{\mathrm{LTD\_manual}}^{(51)}$           | _                                                             | 4           | _                                                                              | _      | μs    |  |

| t <sub>LTR_LTD_manual</sub> <sup>(52)</sup> | _                                                             | 15 —        |                                                                                | _      | μs    |  |

| Programmable ppm detector <sup>(53)</sup>   | _                                                             | ±62.5, 100  | ppm                                                                            |        |       |  |

| Run length                                  | _                                                             | _           | _                                                                              | 200    | UI    |  |

| Programmable equalization AC and DC gain    | AC gain setting = 0 to $3^{(54)}$<br>DC gain setting = 0 to 1 | and DC Gain | oss Supported AC Gain<br>and CTLE Response at<br>d DC Gain for Arria V<br>ums. |        |       |  |

Table 1-29: Transmitter Specifications for Arria V GT and ST Devices

| Symbol/Description              | Condition                  | Tran       | sceiver Speed Gra | Unit    |       |  |

|---------------------------------|----------------------------|------------|-------------------|---------|-------|--|

| Symbol/Description              | Condition                  | Min        | Тур               | Max     | Offic |  |

| Supported I/O standards         |                            | 1.5 V PCML |                   |         |       |  |

| Data rate (6-Gbps transceiver)  | _                          | 611        | _                 | 6553.6  | Mbps  |  |

| Data rate (10-Gbps transceiver) | _                          | 0.611      | _                 | 10.3125 | Gbps  |  |

| V <sub>OCM</sub> (AC coupled)   | _                          | _          | 650               | _       | mV    |  |

| V <sub>OCM</sub> (DC coupled)   | ≤ 3.2 Gbps <sup>(48)</sup> | 670        | 700               | 730     | mV    |  |

Arria V GX, GT, SX, and ST Device Datasheet

$t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{LTR\_LTD\_manual}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

<sup>(53)</sup> The rate match FIFO supports only up to  $\pm 300$  ppm.

<sup>(54)</sup> The Quartus Prime software allows AC gain setting = 3 for design with data rate between 611 Mbps and 1.25 Gbps only.

| Symbol            | Description          | Min                                                  | Тур | Max | Unit |

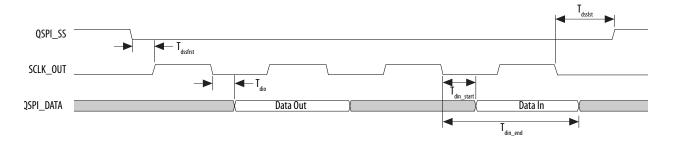

|-------------------|----------------------|------------------------------------------------------|-----|-----|------|

| $T_{ m din\_end}$ | Input data valid end | $(2 + R_{delay}) \times T_{qspi\_clk} - 1.21^{(85)}$ | _   | _   | ns   |

### Figure 1-8: Quad SPI Flash Timing Diagram

This timing diagram illustrates clock polarity mode 0 and clock phase mode 0.

#### **Related Information**

Quad SPI Flash Controller Chapter, Arria V Hard Processor System Technical Reference Manual

Provides more information about Rdelay.

### **SPI Timing Characteristics**

Table 1-52: SPI Master Timing Requirements for Arria V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol    | Description                               | Min       | Max | Unit |

|-----------|-------------------------------------------|-----------|-----|------|

| $T_{clk}$ | CLK clock period                          | 16.67     | _   | ns   |

| $T_{su}$  | SPI Master-in slave-out (MISO) setup time | 8.35 (86) | _   | ns   |

<sup>&</sup>lt;sup>(85)</sup> R<sub>delay</sub> is set by programming the register qspiregs.rddatacap. For the SoC EDS software version 13.1 and later, Altera provides automatic Quad SPI calibration in the preloader. For more information about R<sub>delay</sub>, refer to the Quad SPI Flash Controller chapter in the Arria V Hard Processor System Technical Reference Manual.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

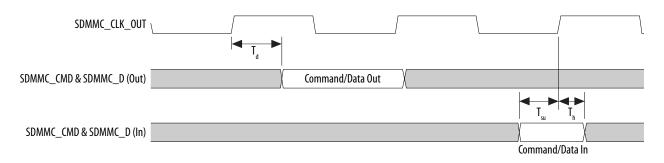

Figure 1-11: SD/MMC Timing Diagram

Booting and Configuration Chapter, Arria V Hard Processor System Technical Reference Manual

Provides more information about CSEL pin settings in the SD/MMC Controller CSEL Pin Settings table.

### **USB Timing Characteristics**

PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.

Table 1-55: USB Timing Requirements for Arria V Devices

| Symbol    | Description                                  | Min | Тур   | Max | Unit |

|-----------|----------------------------------------------|-----|-------|-----|------|

| $T_{clk}$ | USB CLK clock period                         | _   | 16.67 | _   | ns   |

| $T_d$     | CLK to USB_STP/USB_DATA[7:0] output delay    | 4.4 | _     | 11  | ns   |

| $T_{su}$  | Setup time for USB_DIR/USB_NXT/USB_DATA[7:0] | 2   | _     | _   | ns   |

| $T_h$     | Hold time for USB_DIR/USB_NXT/USB_DATA[7:0]  | 1   | _     | _   | ns   |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

| POR Delay | Minimum | Maximum | Unit |

|-----------|---------|---------|------|

| Standard  | 100     | 300     | ms   |

**MSEL Pin Settings**

Provides more information about POR delay based on MSEL pin settings for each configuration scheme.

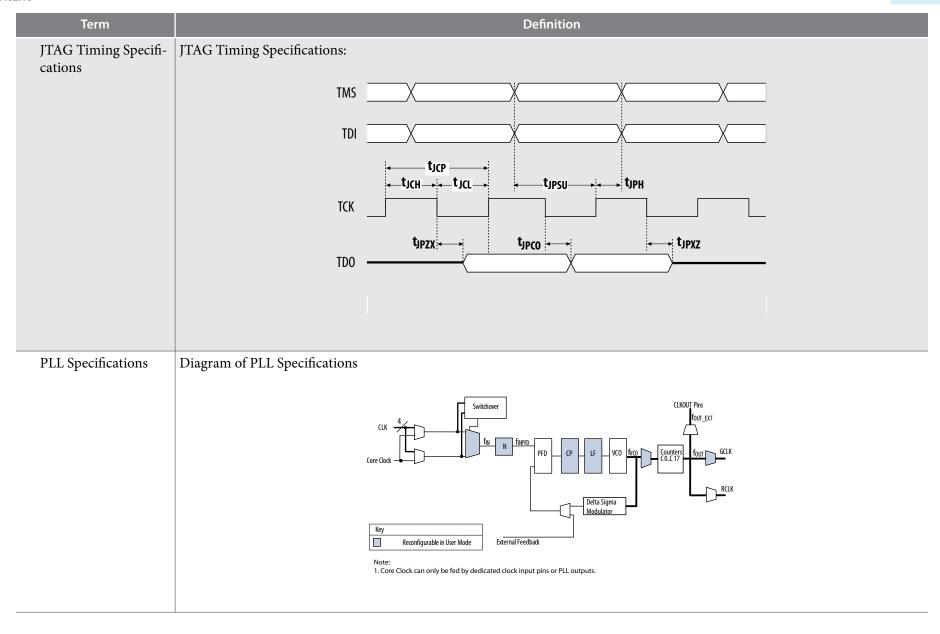

# **FPGA JTAG Configuration Timing**

Table 1-64: FPGA JTAG Timing Parameters and Values for Arria V Devices

| Symbol                  | Description                              | Min                     | Max                | Unit |

|-------------------------|------------------------------------------|-------------------------|--------------------|------|

| $t_{JCP}$               | TCK clock period                         | 30, 167 <sup>(92)</sup> | _                  | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14                      | _                  | ns   |

| $t_{JCL}$               | TCK clock low time                       | 14                      | _                  | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2                       | _                  | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3                       | _                  | ns   |

| $t_{JPH}$               | JTAG port hold time                      | 5                       | _                  | ns   |

| $t_{ m JPCO}$           | JTAG port clock to output                | _                       | 12 <sup>(93)</sup> | ns   |

| $t_{JPZX}$              | JTAG port high impedance to valid output | _                       | 14 <sup>(93)</sup> | ns   |

| $t_{JPXZ}$              | JTAG port valid output to high impedance | _                       | 14 <sup>(93)</sup> | ns   |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

$<sup>^{(92)}</sup>$  The minimum TCK clock period is 167 ns if  $V_{CCBAT}$  is within the range 1.2 V – 1.5 V when you perform the volatile key programming.

<sup>(93)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

### Initialization

Table 1-71: Initialization Clock Source Option and the Maximum Frequency for Arria V Devices

| Initialization Clock Source | Configuration Scheme | Maximum Frequency (MHz) | Minimum Number of Clock Cycles |  |  |

|-----------------------------|----------------------|-------------------------|--------------------------------|--|--|

| Internal Oscillator         | AS, PS, and FPP      | 12.5                    |                                |  |  |

| CLKUSR <sup>(107)</sup>     | PS and FPP           | 125                     | т                              |  |  |

| CLKUSR                      | AS                   | 100                     | $\mathrm{T_{init}}$            |  |  |

| DCLK                        | PS and FPP           | 125                     |                                |  |  |

# **Configuration Files**

### Table 1-72: Uncompressed .rbf Sizes for Arria V Devices

Use this table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Quartus Prime software. However, for a specific version of the Quartus Prime software, any design targeted for the same device has the same uncompressed configuration file size.

The IOCSR raw binary file (.rbf) size is specifically for the Configuration via Protocol (CvP) feature.

<sup>(107)</sup> To enable CLKUSR as the initialization clock source, turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus Prime software from the **General** panel of the **Device and Pin Options** dialog box.

|            |             |       | Active Seria | <b>[</b> (108)                       | Fast Passive Parallel <sup>(109)</sup> |            |                                    |  |

|------------|-------------|-------|--------------|--------------------------------------|----------------------------------------|------------|------------------------------------|--|

| Variant    | Member Code | Width | DCLK (MHz)   | Minimum Configura-<br>tion Time (ms) | Width                                  | DCLK (MHz) | Minimum Configuration Time<br>(ms) |  |

|            | A1          | 4     | 100          | 178                                  | 16                                     | 125        | 36                                 |  |

|            | A3          | 4     | 100          | 178                                  | 16                                     | 125        | 36                                 |  |

|            | A5          | 4     | 100          | 255                                  | 16                                     | 125        | 51                                 |  |

| Arria V GX | A7          | 4     | 100          | 255                                  | 16                                     | 125        | 51                                 |  |

| Allia V GA | B1          | 4     | 100          | 344                                  | 16                                     | 125        | 69                                 |  |

|            | В3          | 4     | 100          | 344                                  | 16                                     | 125        | 69                                 |  |

|            | B5          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |

|            | B7          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |

|            | C3          | 4     | 100          | 178                                  | 16                                     | 125        | 36                                 |  |

| Arria V GT | C7          | 4     | 100          | 255                                  | 16                                     | 125        | 51                                 |  |

| Allia v G1 | D3          | 4     | 100          | 344                                  | 16                                     | 125        | 69                                 |  |

|            | D7          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |

| Arria V SX | В3          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |

| Ailia V SA | B5          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |

| Arria V ST | D3          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |

| Ailia v 51 | D5          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |

**Configuration Files** on page 1-83

<sup>(108)</sup> DCLK frequency of 100 MHz using external CLKUSR.

(109) Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2015 | 2015.12.16 | Updated Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Arria V Devices table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |            | <ul> <li>Updated F<sub>clk</sub>, T<sub>dutycycle</sub>, and T<sub>dssfrst</sub> specifications.</li> <li>Added T<sub>qspi_clk</sub>, T<sub>din_start</sub>, and T<sub>din_end</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> <li>Updated the minimum specification for T<sub>clk</sub> to 16.67 ns and removed the maximum specification in SPI Master Timing Requirements for Arria V Devices table.</li> <li>Updated Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Arria V Devices table.</li> <li>Updated T<sub>clk</sub> to T<sub>sdmmc_clk_out</sub> symbol.</li> <li>Updated T<sub>sdmmc_clk_out</sub> and T<sub>d</sub> specifications.</li> <li>Added T<sub>sdmmc_clk</sub>, T<sub>su</sub>, and T<sub>h</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> <li>Updated the following diagrams:</li> <li>Quad SPI Flash Timing Diagram</li> <li>SD/MMC Timing Diagram</li> <li>Updated configuration .rbf sizes for Arria V devices.</li> <li>Changed instances of Quartus II to Quartus Prime.</li> </ul> |

| Date        | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2013 | 3.5     | <ul><li>Removed "Pending silicon characterization" note in Table 29.</li><li>Updated Table 25.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| August 2013 | 3.4     | <ul> <li>Removed Preliminary tags for Table 1, Table 2, Table 3, Table 4, Table 5, Table 6, Table 7, Table 9, Table 12, Table 13, Table 14, Table 15, Table 16, Table 17, Table 18, Table 19, Table 20, Table 21, Table 22, Table 23, Table 24, Table 25, Table 26, Table 27, Table 28, Table 29, Table 30, Table 31, Table 35, Table 36, Table 51, Table 53, Table 54, Table 55, Table 56, Table 57, Table 60, Table 62, and Table 64.</li> <li>Updated Table 1, Table 3, Table 11, Table 19, Table 20, Table 21, Table 22, Table 25, and Table 29.</li> </ul> |

| June 2013   | 3.3     | Updated Table 20, Table 21, Table 25, and Table 38.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| May 2013    | 3.2     | <ul> <li>Added Table 37.</li> <li>Updated Figure 8, Figure 9, Figure 20, Figure 22, and Figure 23.</li> <li>Updated Table 1, Table 5, Table 10, Table 13, Table 19, Table 20, Table 21, Table 23, Table 29, Table 39, Table 40, Table 46, Table 56, Table 57, Table 60, and Table 64.</li> <li>Updated industrial junction temperature range for -I3 speed grade in "PLL Specifications" section.</li> </ul>                                                                                                                                                    |

| March 2013  | 3.1     | <ul> <li>Added HPS reset information in the "HPS Specifications" section.</li> <li>Added Table 60.</li> <li>Updated Table 1, Table 3, Table 17, Table 20, Table 29, and Table 59.</li> <li>Updated Figure 21.</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

Arria V GX, GT, SX, and ST Device Datasheet

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2012 | 3.0     | <ul> <li>Updated Table 2, Table 4, Table 9, Table 14, Table 16, Table 17, Table 20, Table 21, Table 25, Table 29, Table 36, Table 56, Table 57, and Table 60.</li> <li>Removed table: Transceiver Block Jitter Specifications for Arria V Devices.</li> <li>Added HPS information: <ul> <li>Added "HPS Specifications" section.</li> <li>Added Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, and Table 50.</li> <li>Added Figure 7, Figure 8, Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, Figure 14, Figure 15, Figure 16, Figure 17, Figure 18, and Figure 19.</li> <li>Updated Table 3 and Table 5.</li> </ul> </li> </ul> |

| October 2012  | 2.4     | <ul> <li>Updated Arria V GX V<sub>CCR_GXBL/R</sub>, V<sub>CCT_GXBL/R</sub>, and V<sub>CCL_GXBL/R</sub> minimum and maximum values, and data rate in Table 4.</li> <li>Added receiver V<sub>ICM</sub> (AC coupled) and V<sub>ICM</sub> (DC coupled) values, and transmitter V<sub>OCM</sub> (AC coupled) and V<sub>OCM</sub> (DC coupled) values in Table 20 and Table 21.</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| August 2012   | 2.3     | Updated the SERDES factor condition in Table 30.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| July 2012     | 2.2     | <ul> <li>Updated the maximum voltage for V<sub>I</sub> (DC input voltage) in Table 1.</li> <li>Updated Table 20 to include the Arria V GX -I3 speed grade.</li> <li>Updated the minimum value of the fixedclk clock frequency in Table 20 and Table 21.</li> <li>Updated the SERDES factor condition in Table 30.</li> <li>Updated Table 50 to include the IOE programmable delay settings for the Arria V GX -I3 speed grade.</li> </ul>                                                                                                                                                                                                                                                                        |

| June 2012     | 2.1     | Updated $V_{CCR\_GXBL/R}$ , $V_{CCT\_GXBL/R}$ , and $V_{CCL\_GXBL/R}$ values in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2012     | 2.0     | <ul> <li>Updated for the Quartus II software v12.0 release:</li> <li>Restructured document.</li> <li>Updated "Supply Current and Power Consumption" section.</li> <li>Updated Table 20, Table 21, Table 24, Table 25, Table 26, Table 35, Table 39, Table 43, and Table 52.</li> <li>Added Table 22, Table 23, and Table 33.</li> <li>Added Figure 1–1 and Figure 1–2.</li> <li>Added "Initialization" and "Configuration Files" sections.</li> </ul> |

| February 2012 | 1.3     | <ul> <li>Updated Table 2–1.</li> <li>Updated Transceiver-FPGA Fabric Interface rows in Table 2–20.</li> <li>Updated V<sub>CCP</sub> description.</li> </ul>                                                                                                                                                                                                                                                                                           |

| December 2011 | 1.2     | Updated Table 2–1 and Table 2–3.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| November 2011 | 1.1     | <ul> <li>Updated Table 2–1, Table 2–19, Table 2–26, and Table 2–36.</li> <li>Added Table 2–5.</li> <li>Added Figure 2–4.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| August 2011   | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

AV-51002 2017.02.10

| Symbol/Description                             | Conditions              | Trans | ceiver Spee   | d Grade 2 | Transc | Unit          |     |       |

|------------------------------------------------|-------------------------|-------|---------------|-----------|--------|---------------|-----|-------|

| 3yiiiboi/Description                           | Conditions              | Min   | Тур           | Max       | Min    | Тур           | Max | Offic |

| fixedclk clock frequency                       | PCIe<br>Receiver Detect | _     | 100 or<br>125 | _         | _      | 100 or<br>125 | _   | MHz   |

| Reconfiguration clock (mgmt_clk_clk) frequency | _                       | 100   | _             | 125       | 100    | _             | 125 | MHz   |

#### **Related Information**

Arria V Device Overview

For more information about device ordering codes.

#### Receiver

### Table 2-24: Receiver Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                               | Conditions                  | Trans                                               | ceiver Spee | d Grade 2 | Transc | - Unit |         |       |

|--------------------------------------------------|-----------------------------|-----------------------------------------------------|-------------|-----------|--------|--------|---------|-------|

| 3yiiiboi/Description                             | Conditions                  | Min                                                 | Тур         | Max       | Min    | Тур    | Max     | Offic |

| Supported I/O Standards                          | 1.4-V PCML, 1.5-V PCML, 2.5 | .4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |             |           |        |        |         |       |

| Data rate (Standard PCS) (143), (144)            | _                           | 600                                                 | _           | 9900      | 600    | _      | 8800    | Mbps  |

| Data rate (10G PCS) (143), (144)                 | _                           | 600                                                 | _           | 12500     | 600    | _      | 10312.5 | Mbps  |

| Absolute $V_{MAX}$ for a receiver pin $^{(145)}$ | _                           | _                                                   | _           | 1.2       | _      | _      | 1.2     | V     |

| Absolute V <sub>MIN</sub> for a receiver pin     | _                           | -0.4                                                | _           | _         | -0.4   | _      | _       | V     |

<sup>(143)</sup> The line data rate may be limited by PCS-FPGA interface speed grade.

Altera Corporation Arria V GZ Device Datasheet

$<sup>^{(144)}</sup>$  To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>(145)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

|                    | ATX PLL                   |                       |                                                                                                       |                           | CMU PLL (161)         |                                                |                           | fPLL                  |                                                      |  |  |

|--------------------|---------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|------------------------------------------------|---------------------------|-----------------------|------------------------------------------------------|--|--|

|                    | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                                                                       | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                      |  |  |

| xN (PCIe)          | _                         | 8.0                   | 8                                                                                                     | _                         | 5.0                   | 8                                              | _                         | _                     | _                                                    |  |  |

| xN (Native PHY IP) | 8.0                       | 8.01 to<br>9.8304     | Up to 13<br>channels<br>above and<br>below PLL<br>Up to 7<br>channels<br>above<br>and<br>below<br>PLL | 7.99                      | 7.99                  | Up to 13<br>channels<br>above and<br>below PLL | 3.125                     | 3.125                 | Up to 13<br>channels<br>above<br>and<br>below<br>PLL |  |  |

#### **Standard PCS Data Rate**

# Table 2-30: Standard PCS Approximate Maximum Date Rate (Gbps) for Arria V GZ Devices

The maximum data rate is also constrained by the transceiver speed grade. Refer to the "Commercial and Industrial Speed Grade Offering for Arria V GZ Devices" table for the transceiver speed grade.

| Mode (10-7) | Transceiver | PMA Width                  | 20  | 20  | 16   | 16   | 10  | 10  | 8    | 8    |

|-------------|-------------|----------------------------|-----|-----|------|------|-----|-----|------|------|

|             | Speed Grade | PCS/Core Width             | 40  | 20  | 32   | 16   | 20  | 10  | 16   | 8    |

| FIFO        | 2           | C3, I3L core speed grade   | 9.9 | 9   | 7.84 | 7.2  | 5.3 | 4.7 | 4.24 | 3.76 |

| THO         | 3           | C4, I4<br>core speed grade | 8.8 | 8.2 | 7.2  | 6.56 | 4.8 | 4.3 | 3.84 | 3.44 |

<sup>(161)</sup> ATX PLL is recommended at 8 Gbps and above data rates for improved jitter performance.

Altera Corporation

Arria V GZ Device Datasheet

<sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

| Symbol                                                                                               | Conditions                              | C3, I3L |     | C4, I4    |     |     | - Unit    |       |

|------------------------------------------------------------------------------------------------------|-----------------------------------------|---------|-----|-----------|-----|-----|-----------|-------|

| Symbol                                                                                               | Conditions                              | Min     | Тур | Max       | Min | Тур | Max       | Offic |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) True Differential<br>I/O Standards <sup>(179)</sup> | Clock boost factor<br>W = 1 to 40 (180) | 5       | _   | 625       | 5   | _   | 525       | MHz   |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) Single Ended I/O<br>Standards                       | Clock boost factor<br>W = 1 to 40 (180) | 5       | _   | 625       | 5   | _   | 525       | MHz   |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) Single Ended I/O<br>Standards                       | Clock boost factor<br>W = 1 to 40 (180) | 5       | _   | 420       | 5   | _   | 420       | MHz   |

| f <sub>HSCLK_OUT</sub> (output clock frequency)                                                      | _                                       | 5       | _   | 625 (181) | 5   | _   | 525 (181) | MHz   |

### **Transmitter High-Speed I/O Specifications**

### Table 2-40: Transmitter High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

Arria V GZ Device Datasheet

Altera Corporation

$<sup>^{\</sup>left(179\right)}\,$  This only applies to DPA and soft-CDR modes.

<sup>(180)</sup> Clock Boost Factor (W) is the ratio between the input data rate to the input clock rate.

<sup>(181)</sup> This is achieved by using the LVDS clock network.

| Standard           | Training Pattern | Number of Data Transitions<br>in One Repetition of the<br>Training Pattern | Number of Repetitions per<br>256 Data Transitions <sup>(201)</sup> | Maximum              |

|--------------------|------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------|

| Parallel Rapid I/O | 00001111         | 2                                                                          | 128                                                                | 640 data transitions |

| raranei Kapiu 1/O  | 10010000         | 4                                                                          | 64                                                                 | 640 data transitions |

| Miscellaneous      | 10101010         | 8                                                                          | 32                                                                 | 640 data transitions |

|                    | 01010101         | 8                                                                          | 32                                                                 | 640 data transitions |

### Soft CDR Mode High-Speed I/O Specifications

### Table 2-44: High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol                 | Conditions - | C3, I3L |     |     | C4, I4 |     |     | Unit  |

|------------------------|--------------|---------|-----|-----|--------|-----|-----|-------|

|                        | Conditions   | Min     | Тур | Max | Min    | Тур | Max | Onit  |

| Soft-CDR ppm tolerance | _            | _       | _   | 300 | _      | _   | 300 | ± ppm |

Altera Corporation Arria V GZ Device Datasheet

$<sup>^{(201)}</sup>$  This is the number of repetitions for the stated training pattern to achieve the 256 data transitions.

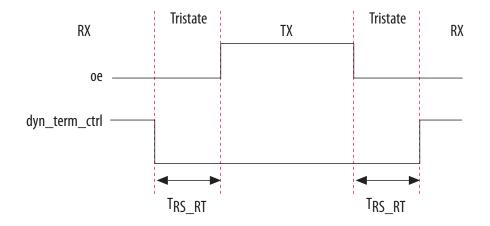

# **OCT Calibration Block Specifications**

Table 2-51: OCT Calibration Block Specifications for Arria V GZ Devices

| Symbol                | Description                                                                                                                                                                             | Min | Тур  | Max | Unit   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by the OCT calibration blocks                                                                                                                                            |     | _    | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of OCTUSRCLK clock cycles required for OCT R <sub>S</sub> /R <sub>T</sub> calibration                                                                                            | _   | 1000 | _   | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for the OCT code to shift out                                                                                                                 | _   | 32   | _   | Cycles |

| T <sub>RS_RT</sub>    | Time required between the $\tt dyn\_term\_ctrl$ and $\tt oe$ signal transitions in a bidirectional I/O buffer to dynamically switch between OCT $R_S$ and $R_T$ (See the figure below.) | _   | 2.5  | _   | ns     |

Figure 2-6: Timing Diagram for oe and dyn\_term\_ctrl Signals

Arria V GZ Device Datasheet

Altera Corporation

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

For more information about the reconfiguration input for the ALTREMOTE\_UPDATE IP core, refer to the "User Watchdog Timer" section.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

For more information about the reset\_timer input for the ALTREMOTE\_UPDATE IP core, refer to the "Remote System Upgrade State Machine" section.

# **User Watchdog Internal Oscillator Frequency Specification**

Table 2-65: User Watchdog Internal Oscillator Frequency Specifications

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O Timing and the Quartus II Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Quartus II Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

Arria V Devices Documentation page

For the Excel-based I/O Timing spreadsheet

Arria V GZ Device Datasheet Altera Corporation

<sup>(226)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "Remote System Upgrade State Machine" section in the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

<sup>(227)</sup> This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "User Watchdog Timer" section in the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

Arria V GZ Device Datasheet

Altera Corporation