Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 17110                                                      |

| Number of Logic Elements/Cells | 362000                                                     |

| Total RAM Bits                 | 19822592                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.12V ~ 1.18V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxfb3h4f35i3g |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol  | Description      | Condition (V) | Overshoot Duration as % of High Time | Unit |

|---------|------------------|---------------|--------------------------------------|------|

|         |                  | 3.8           | 100                                  | %    |

|         |                  | 3.85          | 68                                   | %    |

|         |                  | 3.9           | 45                                   | %    |

|         |                  | 3.95          | 28                                   | %    |

|         |                  | 4             | 15                                   | %    |

|         |                  | 4.05          | 13                                   | %    |

|         |                  | 4.1           | 11                                   | %    |

|         |                  | 4.15          | 9                                    | %    |

| Vi (AC) | AC input voltage | 4.2           | 8                                    | %    |

|         |                  | 4.25          | 7                                    | %    |

|         |                  | 4.3           | 5.4                                  | %    |

|         |                  | 4.35          | 3.2                                  | %    |

|         |                  | 4.4           | 1.9                                  | %    |

|         |                  | 4.45          | 1.1                                  | %    |

|         |                  | 4.5           | 0.6                                  | %    |

|         |                  | 4.55          | 0.4                                  | %    |

|         |                  | 4.6           | 0.2                                  | %    |

## **Recommended Operating Conditions**

This section lists the functional operation limits for the AC and DC parameters for Arria V devices.

## **Recommended Operating Conditions**

## Table 1-3: Recommended Operating Conditions for Arria V Devices

This table lists the steady-state voltage values expected from Arria V devices. Power supply ramps must all be strictly monotonic, without plateaus.

| I/O Standard  | V <sub>CCIO</sub> (V) |      | V <sub>SWI</sub> | <sub>ING(DC)</sub> (V) |      | V <sub>X(AC)</sub> (V)      |                      | V <sub>SI</sub>                | <sub>WING(AC)</sub> (V)                       |                           |

|---------------|-----------------------|------|------------------|------------------------|------|-----------------------------|----------------------|--------------------------------|-----------------------------------------------|---------------------------|

| i/O Stalldard | Min                   | Тур  | Max              | Min                    | Max  | Min                         | Тур                  | Max                            | Min                                           | Max                       |

| SSTL-125      | 1.19                  | 1.25 | 1.31             | 0.18                   | (15) | V <sub>CCIO</sub> /2 - 0.15 | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15 | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |

#### Differential HSTL and HSUL I/O Standards

Table 1-18: Differential HSTL and HSUL I/O Standards for Arria V Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>DI</sub> | <sub>F(DC)</sub> (V)    |                                                                     | V <sub>X(AC)</sub> (V)    |                                                                        |                                                           | V <sub>CM(DC)</sub> (V)   |                            | V    | <sub>DIF(AC)</sub> (V)   |

|------------------------|-------|-----------------------|-------|-----------------|-------------------------|---------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------|----------------------------|------|--------------------------|

| i/O Stailualu          | Min   | Тур                   | Max   | Min             | Max                     | Min                                                                 | Тур                       | Max                                                                    | Min                                                       | Тур                       | Max                        | Min  | Max                      |

| HSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.2             | _                       | 0.78                                                                | _                         | 1.12                                                                   | 0.78                                                      | _                         | 1.12                       | 0.4  | _                        |

| HSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.2             | _                       | 0.68                                                                | _                         | 0.9                                                                    | 0.68                                                      | _                         | 0.9                        | 0.4  |                          |

| HSTL-12<br>Class I, II | 1.14  | 1.2                   | 1.26  | 0.16            | V <sub>CCIO</sub> + 0.3 | _                                                                   | $0.5 \times V_{\rm CCIO}$ | _                                                                      | $\begin{array}{c} 0.4 \times \\ V_{\rm CCIO} \end{array}$ | $0.5 \times V_{\rm CCIO}$ | $0.6 \times V_{\rm CCIO}$  | 0.3  | V <sub>CCIO</sub> + 0.48 |

| HSUL-12                | 1.14  | 1.2                   | 1.3   | 0.26            | 0.26                    | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} - \\ 0.12 \end{array}$ | $0.5 \times V_{\rm CCIO}$ | $\begin{array}{c} 0.5 \times \\ V_{\text{CCIO}} \\ + 0.12 \end{array}$ | $\begin{array}{c} 0.4 \times \\ V_{\rm CCIO} \end{array}$ | $0.5 \times V_{\rm CCIO}$ | 0.6 ×<br>V <sub>CCIO</sub> | 0.44 | 0.44                     |

## **Differential I/O Standard Specifications**

## Table 1-19: Differential I/O Standard Specifications for Arria V Devices

Differential inputs are powered by  $\rm V_{\rm CCPD}$  which requires 2.5 V.

| Protocol                             | Sub-protocol      | Data Rate (Mbps) |

|--------------------------------------|-------------------|------------------|

|                                      | CPRI E6LV         | 614.4            |

|                                      | CPRI E6HV         | 614.4            |

|                                      | CPRI E6LVII       | 614.4            |

|                                      | CPRI E12LV        | 1,228.8          |

|                                      | CPRI E12HV        | 1,228.8          |

|                                      | CPRI E12LVII      | 1,228.8          |

| Common Public Radio Interface (CPRI) | CPRI E24LV        | 2,457.6          |

|                                      | CPRI E24LVII      | 2,457.6          |

|                                      | CPRI E30LV        | 3,072            |

|                                      | CPRI E30LVII      | 3,072            |

|                                      | CPRI E48LVII      | 4,915.2          |

|                                      | CPRI E60LVII      | 6,144            |

|                                      | CPRI E96LVIII(60) | 9,830.4          |

| Gbps Ethernet (GbE)                  | GbE 1250          | 1,250            |

|                                      | OBSAI 768         | 768              |

| OBSAI                                | OBSAI 1536        | 1,536            |

| OBSAI                                | OBSAI 3072        | 3,072            |

|                                      | OBSAI 6144        | 6,144            |

|                                      | SDI 270 SD        | 270              |

| Serial digital interface (SDI)       | SDI 1485 HD       | 1,485            |

|                                      | SDI 2970 3G       | 2,970            |

<sup>(60)</sup> You can achieve compliance with TX channel restriction of one HSSI channel per six-channel transceiver bank.

### **DSP Block Performance Specifications**

Table 1-37: DSP Block Performance Specifications for Arria V Devices

|                               | Mode                                                     |     |     | Performance  |      |  |  |

|-------------------------------|----------------------------------------------------------|-----|-----|--------------|------|--|--|

|                               |                                                          |     |     | - <b>C</b> 6 | Unit |  |  |

|                               | Independent 9 × 9 multiplication                         | 370 | 310 | 220          | MHz  |  |  |

|                               | Independent 18 × 19 multiplication                       | 370 | 310 | 220          | MHz  |  |  |

|                               | Independent 18 × 25 multiplication                       | 370 | 310 | 220          | MHz  |  |  |

| C                             | Independent 20 × 24 multiplication                       | 370 | 310 | 220          | MHz  |  |  |

| Block                         | Independent 27 × 27 multiplication                       | 310 | 250 | 200          | MHz  |  |  |

|                               | Two 18 × 19 multiplier adder mode                        | 370 | 310 | 220          | MHz  |  |  |

|                               | $18 \times 18$ multiplier added summed with 36-bit input | 370 | 310 | 220          | MHz  |  |  |

| Modes using Two<br>DSP Blocks | Complex 18 × 19 multiplication                           | 370 | 310 | 220          | MHz  |  |  |

## **Memory Block Performance Specifications**

To achieve the maximum memory block performance, use a memory block clock that comes through global clock routing from an on-chip PLL and set to 50% output duty cycle. Use the Quartus Prime software to report timing for the memory block clocking schemes.

When you use the error detection cyclical redundancy check (CRC) feature, there is no degradation in  $f_{MAX}$ .

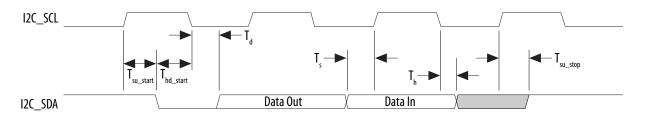

### Figure 1-16: I<sup>2</sup>C Timing Diagram

### **NAND Timing Characteristics**

#### Table 1-60: NAND ONFI 1.0 Timing Requirements for Arria V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the C4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                            | Description                                     | Min | Max         | Unit |

|-----------------------------------|-------------------------------------------------|-----|-------------|------|

| $T_{wp}^{(89)}$                   | Write enable pulse width                        | 10  | _           | ns   |

| T <sub>wh</sub> <sup>(89)</sup>   | Write enable hold time                          | 7   | _           | ns   |

| T <sub>rp</sub> <sup>(89)</sup>   | Read enable pulse width                         | 10  | <del></del> | ns   |

| $T_{reh}^{(89)}$                  | Read enable hold time                           | 7   | _           | ns   |

| $T_{clesu}^{(89)}$                | Command latch enable to write enable setup time | 10  | _           | ns   |

| T <sub>cleh</sub> <sup>(89)</sup> | Command latch enable to write enable hold time  | 5   | _           | ns   |

| T <sub>cesu</sub> <sup>(89)</sup> | Chip enable to write enable setup time          | 15  | _           | ns   |

| $T_{ceh}^{(89)}$                  | Chip enable to write enable hold time           |     | _           | ns   |

| T <sub>alesu</sub> (89)           | Address latch enable to write enable setup time | 10  | _           | ns   |

| T <sub>aleh</sub> <sup>(89)</sup> | Address latch enable to write enable hold time  | 5   | _           | ns   |

| $T_{dsu}^{(89)}$                  | Data to write enable setup time                 | 10  | _           | ns   |

<sup>(89)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

Arria V GX, GT, SX, and ST Device Datasheet

## **FPP Configuration Timing**

#### DCLK-to-DATA[] Ratio (r) for FPP Configuration

Fast passive parallel (FPP) configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the DATA[] rate in byte per second (Bps) or word per second (Wps). For example, in FPP ×16 where the r is 2, the DCLK frequency must be 2 times the DATA[] rate in Wps.

Table 1-65: DCLK-to-DATA[] Ratio for Arria V Devices

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

|                      | Off        | Off         | 1                        |

| FPP (8-bit wide)     | On         | Off         | 1                        |

| TTT (0-bit wide)     | Off        | On          | 2                        |

|                      | On         | On          | 2                        |

|                      | Off        | Off         | 1                        |

| FPP (16-bit wide)    | On         | Off         | 2                        |

| TTT (10-bit wide)    | Off        | On          | 4                        |

|                      | On         | On          | 4                        |

### FPP Configuration Timing when DCLK-to-DATA[] = 1

When you enable decompression or the design security feature, the DCLK-to-DATA[] ratio varies for FPP  $\times 8$  and FPP  $\times 16$ . For the respective DCLK-to-DATA[] ratio, refer to the DCLK-to-DATA[] Ratio for Arria V Devices table.

Table 1-66: FPP Timing Parameters When DCLK-to-DATA[] Ratio is 1 for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum | Unit |

|---------------------|------------------------------|---------|---------|------|

| $t_{CF2CD}$         | nconfig low to conf_done low | _       | 600     | ns   |

| t <sub>CF2ST0</sub> | nconfig low to nstatus low   | _       | 600     | ns   |

| $t_{\mathrm{CFG}}$  | nconfig low pulse width      | 2       | _       | μs   |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

| Term                 | Definition                                                                                                  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

|                      | Transmitter Output Waveforms                                                                                |  |  |  |

|                      | Single-Ended Waveform  Positive Channel (p) = V <sub>OH</sub> Negative Channel (n) = V <sub>OL</sub> Ground |  |  |  |

|                      | Differential Waveform                                                                                       |  |  |  |

| $f_{HSCLK}$          | Left/right PLL input clock frequency.                                                                       |  |  |  |

| $f_{HSDR}$           | High-speed I/O block—Maximum/minimum LVDS data transfer rate (f <sub>HSDR</sub> =1/TUI), non-DPA.           |  |  |  |

| f <sub>HSDRDPA</sub> | High-speed I/O block—Maximum/minimum LVDS data transfer rate (f <sub>HSDRDPA</sub> =1/TUI), DPA.            |  |  |  |

| J                    | High-speed I/O block—Deserialization factor (width of parallel data bus).                                   |  |  |  |

| Term     | Definition                              |

|----------|-----------------------------------------|

| $V_{OX}$ | Output differential cross point voltage |

| W        | High-speed I/O block—Clock boost factor |

# **Document Revision History**

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2016 | 2016.12.09 | <ul> <li>Updated V<sub>ICM</sub> (AC coupled) specifications in Receiver Specifications for Arria V GX and SX Devices table.</li> <li>Added maximum specification for T<sub>d</sub> in Management Data Input/Output (MDIO) Timing Requirements for Arria V Devices table.</li> <li>Updated T<sub>init</sub> specifications in the following tables:         <ul> <li>FPP Timing Parameters When DCLK-to-DATA[] Ratio is 1 for Arria V Devices</li> <li>FPP Timing Parameters When DCLK-to-DATA[] Ratio is &gt;1 for Arria V Devices</li> <li>AS Timing Parameters for AS ×1 and ×4 Configurations in Arria V Devices</li> <li>PS Timing Parameters for Arria V Devices</li> </ul> </li> </ul> |

| June 2016     | 2016.06.10 | <ul> <li>Changed pin capacitance to maximum values.</li> <li>Updated SPI Master Timing Requirements for Arria V Devices table.</li> <li>Added T<sub>su</sub> and T<sub>h</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> <li>Updated SPI Master Timing Diagram.</li> <li>Updated T<sub>clk</sub> spec from maximum to minimum in I<sup>2</sup>C Timing Requirements for Arria V Devices table.</li> </ul>                                                                                                                                                                                                                                                      |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2012 | 3.0     | <ul> <li>Updated Table 2, Table 4, Table 9, Table 14, Table 16, Table 17, Table 20, Table 21, Table 25, Table 29, Table 36, Table 56, Table 57, and Table 60.</li> <li>Removed table: Transceiver Block Jitter Specifications for Arria V Devices.</li> <li>Added HPS information: <ul> <li>Added "HPS Specifications" section.</li> <li>Added Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, and Table 50.</li> <li>Added Figure 7, Figure 8, Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, Figure 14, Figure 15, Figure 16, Figure 17, Figure 18, and Figure 19.</li> <li>Updated Table 3 and Table 5.</li> </ul> </li> </ul> |

| October 2012  | 2.4     | <ul> <li>Updated Arria V GX V<sub>CCR_GXBL/R</sub>, V<sub>CCT_GXBL/R</sub>, and V<sub>CCL_GXBL/R</sub> minimum and maximum values, and data rate in Table 4.</li> <li>Added receiver V<sub>ICM</sub> (AC coupled) and V<sub>ICM</sub> (DC coupled) values, and transmitter V<sub>OCM</sub> (AC coupled) and V<sub>OCM</sub> (DC coupled) values in Table 20 and Table 21.</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| August 2012   | 2.3     | Updated the SERDES factor condition in Table 30.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| July 2012     | 2.2     | <ul> <li>Updated the maximum voltage for V<sub>I</sub> (DC input voltage) in Table 1.</li> <li>Updated Table 20 to include the Arria V GX -I3 speed grade.</li> <li>Updated the minimum value of the fixedclk clock frequency in Table 20 and Table 21.</li> <li>Updated the SERDES factor condition in Table 30.</li> <li>Updated Table 50 to include the IOE programmable delay settings for the Arria V GX -I3 speed grade.</li> </ul>                                                                                                                                                                                                                                                                        |

| June 2012     | 2.1     | Updated $V_{CCR\_GXBL/R}$ , $V_{CCT\_GXBL/R}$ , and $V_{CCL\_GXBL/R}$ values in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>DIF</sub> | <sub>(DC)</sub> (V) |                         | $V_{X(AC)}(V)$                       |                       | V <sub>CN</sub>                     | <sub>M(DC)</sub> (V       | )                                 | V                            | <sub>DIF(AC)</sub> (V) |                             |

|------------------------|-----------------------|-----|------------------|---------------------|-------------------------|--------------------------------------|-----------------------|-------------------------------------|---------------------------|-----------------------------------|------------------------------|------------------------|-----------------------------|

| i/O Standard           | Min                   | Тур | Max              | Min                 | Max                     | Min                                  | Тур                   | Max                                 | Min                       | Тур                               | Max                          | Min                    | Max                         |

| HSTL-12 Class<br>I, II | 1.14                  | 1.2 | 1.26             | 0.16                | V <sub>CCIO</sub> + 0.3 | _                                    | $0.5 \times V_{CCIO}$ | _                                   | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub><br>IO | $0.6 \times V_{\text{CCIO}}$ | 0.3                    | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14                  | 1.2 | 1.3              | 0.26                | 0.26                    | 0.5 ×<br>V <sub>CCIO</sub> –<br>0.12 | $0.5 \times V_{CCIO}$ | $0.5 \times V_{\rm CCIO} \\ + 0.12$ | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub>       | 0.6 ×<br>V <sub>CCIO</sub>   | 0.44                   | 0.44                        |

Table 2-21: Differential I/O Standard Specifications for Arria V GZ Devices

| I/O Standard   | V <sub>CCIO</sub> (V) <sup>(128)</sup>                                                                                                                                                                                                                     |        |       | V <sub>ID</sub> (mV) <sup>(129)</sup> |                             |      | V <sub>ICM(DC)</sub> (V) |                                | Vo  | <sub>D</sub> (V) <sup>(13</sup> | 0)   | V     | <sub>OCM</sub> (V) <sup>(13</sup> | 30)  |       |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|---------------------------------------|-----------------------------|------|--------------------------|--------------------------------|-----|---------------------------------|------|-------|-----------------------------------|------|-------|

| i/O Standard   | Min                                                                                                                                                                                                                                                        | Тур    | Max   | Min                                   | Condition                   | Max  | Min                      | Condition                      | Max | Min                             | Тур  | Max   | Min                               | Тур  | Max   |

| PCML           | PCML Transmitter, receiver, and input reference clock pins of the high-speed transceivers use the PCML I/O standard. For transmitter, receiver, and reference clock I/O pin specifications, refer to the "Transceiver Performance Specifications" section. |        |       |                                       |                             |      |                          |                                |     |                                 |      |       |                                   |      |       |

| 2.5 V<br>LVDS  | 2.375                                                                                                                                                                                                                                                      | 2.5    | 2.625 | 100                                   | V <sub>CM</sub> =           |      | 0.05                     | $D_{MAX} \le 700 \text{ Mbps}$ | 1.8 | 0.247                           | _    | 0.6   | 1.125                             | 1.25 | 1.375 |

| (131)          | LVD3   2.3/3   2.3   2.023   100                                                                                                                                                                                                                           | 1.25 V | _     | 1.05                                  | D <sub>MAX</sub> > 700 Mbps | 1.55 | 0.247                    | _                              | 0.6 | 1.125                           | 1.25 | 1.375 |                                   |      |       |

| BLVDS<br>(132) | 2.375                                                                                                                                                                                                                                                      | 2.5    | 2.625 | 100                                   | _                           | _    | _                        | _                              | _   | _                               | _    | _     | _                                 | _    | _     |

$<sup>^{\</sup>left(128\right)}\,$  Differential inputs are powered by VCCPD which requires 2.5 V.

<sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>(130)</sup> RL range:  $90 \le RL \le 110 \Omega$ .

<sup>(131)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.6 V for data rates above 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

<sup>(132)</sup> There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

| Symbol/Description                                                                                               | Conditions                                                                | Transceiver Speed Grade 2 |              |     | Transo | eiver Spe    | ed Grade 3 | Unit  |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------|--------------|-----|--------|--------------|------------|-------|

| 3yiiiboi/Description                                                                                             | Conditions                                                                | Min                       | Тур          | Max | Min    | Тур          | Max        | Oille |

| $\label{eq:maximum peak-to-peak differential} \\ input voltage V_{ID} (diff p-p) before \\ device configuration$ | _                                                                         | _                         | _            | 1.6 | _      | _            | 1.6        | V     |

| Maximum peak-to-peak differential                                                                                | $V_{\text{CCR\_GXB}} = 1.0 \text{ V}$ $(V_{\text{ICM}} = 0.75 \text{ V})$ | _                         | _            | 1.8 | _      | _            | 1.8        | V     |

| input voltage $V_{ID}$ (diff p-p) after device configuration $^{(146)}$                                          | $V_{\text{CCR\_GXB}} = 0.85 \text{ V}$ $(V_{\text{ICM}} = 0.6 \text{ V})$ | _                         | _            | 2.4 | _      | _            | 2.4        | V     |

| Minimum differential eye opening at receiver serial input pins (147)(148)                                        | _                                                                         | 85                        | _            | _   | 85     | _            | _          | mV    |

|                                                                                                                  | 85– $\Omega$ setting                                                      |                           | 85 ± 30%     | _   | _      | 85<br>± 30%  | _          | Ω     |

| Differential on-chip termination                                                                                 | 100–Ω setting                                                             | _                         | 100<br>± 30% | _   | _      | 100<br>± 30% | _          | Ω     |

| resistors                                                                                                        | 120–Ω setting                                                             | _                         | 120<br>± 30% | _   | _      | 120<br>± 30% | _          | Ω     |

|                                                                                                                  | 150– $\Omega$ setting                                                     | _                         | 150<br>± 30% | _   | _      | 150<br>± 30% | _          | Ω     |

$<sup>^{(146)} \ \</sup> The\ maximum\ peak\ to\ peak\ differential\ input\ voltage\ V_{ID}\ after\ device\ configuration\ is\ equal\ to\ 4\times (absolute\ V_{MAX}\ for\ receiver\ pin\ -\ V_{ICM}).$

<sup>(147)</sup> The differential eye opening specification at the receiver input pins assumes that **Receiver Equalization** is disabled. If you enable **Receiver Equalization**, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

<sup>(148)</sup> Minimum eye opening of 85 mV is only for the unstressed input eye condition.

| Symbol/Description                                          | Conditions                                 | Trans | ceiver Spee  | d Grade 2 | Transo | eiver Spee   | ed Grade 3 | Unit |

|-------------------------------------------------------------|--------------------------------------------|-------|--------------|-----------|--------|--------------|------------|------|

| symbol/Description                                          | Conditions                                 | Min   | Тур          | Max       | Min    | Тур          | Max        | Onit |

|                                                             | 85- $\Omega$ setting                       | _     | 85 ± 20%     | _         | _      | 85<br>± 20%  | _          | Ω    |

| Differential on-chip termination                            | 100- $\Omega$ setting                      | _     | 100<br>± 20% | _         | _      | 100<br>± 20% | _          | Ω    |

| resistors                                                   | 120-Ω setting                              | _     | 120<br>± 20% | _         | _      | 120<br>± 20% | _          | Ω    |

|                                                             | 150- $\Omega$ setting                      | _     | 150<br>± 20% | _         | _      | 150<br>± 20% | _          | Ω    |

| V <sub>OCM</sub> (AC coupled)                               | 0.65-V setting                             | _     | 650          | _         | _      | 650          | _          | mV   |

| V <sub>OCM</sub> (DC coupled)                               | _                                          | _     | 650          | _         | _      | 650          | _          | mV   |

| Intra-differential pair skew                                | $Tx V_{CM} = 0.5 V$ and slew rate of 15 ps | _     | _            | 15        | _      | _            | 15         | ps   |

| Intra-transceiver block transmitter channel-to-channel skew | x6 PMA bonded mode                         | _     | _            | 120       | _      | _            | 120        | ps   |

| Inter-transceiver block transmitter channel-to-channel skew | xN PMA bonded mode                         | _     | _            | 500       | _      | _            | 500        | ps   |

#### **Related Information**

Arria V Device Overview

For more information about device ordering codes.

Altera Corporation Arria V GZ Device Datasheet

| Symbol                                                                                               | Conditions                              |     | C3, I3L |           |     | Unit |           |       |

|------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|---------|-----------|-----|------|-----------|-------|

| Зупівої                                                                                              | Containions                             | Min | Тур     | Max       | Min | Тур  | Max       | Offic |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) True Differential<br>I/O Standards <sup>(179)</sup> | Clock boost factor<br>W = 1 to 40 (180) | 5   | _       | 625       | 5   | _    | 525       | MHz   |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) Single Ended I/O<br>Standards                       | Clock boost factor<br>W = 1 to 40 (180) | 5   | _       | 625       | 5   | _    | 525       | MHz   |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) Single Ended I/O<br>Standards                       | Clock boost factor<br>W = 1 to 40 (180) | 5   | _       | 420       | 5   | _    | 420       | MHz   |

| f <sub>HSCLK_OUT</sub> (output clock frequency)                                                      | _                                       | 5   | _       | 625 (181) | 5   | _    | 525 (181) | MHz   |

## **Transmitter High-Speed I/O Specifications**

## Table 2-40: Transmitter High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

$<sup>^{\</sup>left(179\right)}\,$  This only applies to DPA and soft-CDR modes.

<sup>(180)</sup> Clock Boost Factor (W) is the ratio between the input data rate to the input clock rate.

<sup>(181)</sup> This is achieved by using the LVDS clock network.

| Symbol                                                                    | Conditions                                                                                |     | C3, I3L |     |     | C4, I4 |      | Unit  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|---------|-----|-----|--------|------|-------|

| Syllibol                                                                  | Conditions                                                                                | Min | Тур     | Max | Min | Тур    | Max  | Offic |

| t <sub>x Jitter</sub> - True Differential I/O                             | Total Jitter for Data Rate<br>600 Mbps - 1.25 Gbps                                        | _   | _       | 160 | _   | _      | 160  | ps    |

| Standards                                                                 | Total Jitter for Data Rate<br>< 600 Mbps                                                  | _   | _       | 0.1 | _   |        | 0.1  | UI    |

| t <sub>x Jitter</sub> - Emulated Differential<br>I/O Standards with Three | Total Jitter for Data Rate<br>600 Mbps - 1.25 Gbps                                        | _   | _       | 300 | _   | _      | 325  | ps    |

| External Output Resistor<br>Network                                       | Total Jitter for Data Rate<br>< 600 Mbps                                                  | _   | _       | 0.2 | _   |        | 0.25 | UI    |

| $t_{ m DUTY}$                                                             | Transmitter output clock duty cycle for both True and Emulated Differential I/O Standards | 45  | 50      | 55  | 45  | 50     | 55   | %     |

|                                                                           | True Differential I/O Standards                                                           | _   | _       | 200 | _   | _      | 200  | ps    |

| $t_{RISE} \& t_{FALL}$                                                    | Emulated Differential I/O<br>Standards with three external<br>output resistor networks    | _   | _       | 250 | _   | _      | 300  | ps    |

|                                                                           | True Differential I/O Standards                                                           | _   | _       | 150 | _   | _      | 150  | ps    |

| TCCS                                                                      | Emulated Differential I/O<br>Standards                                                    | _   | _       | 300 | _   | _      | 300  | ps    |

## **Receiver High-Speed I/O Specifications**

## Table 2-41: Receiver High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

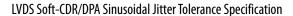

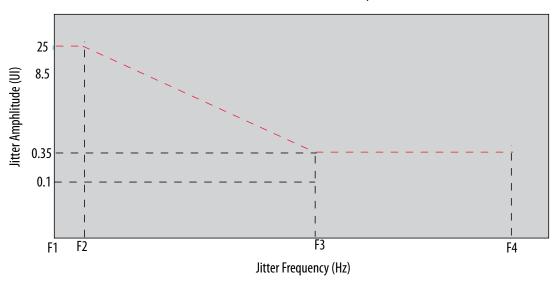

Figure 2-4: LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate ≥ 1.25 Gbps

Table 2-45: LVDS Soft-CDR/DPA Sinusoidal Jitter Mask Values for a Data Rate ≥ 1.25 Gbps

| Jitter Free | quency (Hz) | Sinusoidal Jitter (UI) |  |  |

|-------------|-------------|------------------------|--|--|

| F1          | F1 10,000   |                        |  |  |

| F2          | F2 17,565   |                        |  |  |

| F3          | 1,493,000   | 0.350                  |  |  |

| F4          | 50,000,000  | 0.350                  |  |  |

## **DLL Range Specifications**

#### Table 2-47: DLL Range Specifications for Arria V GZ Devices

Arria V GZ devices support memory interface frequencies lower than 300 MHz, although the reference clock that feeds the DLL must be at least 300 MHz. To support interfaces below 300 MHz, multiply the reference clock feeding the DLL to ensure the frequency is within the supported range of the DLL.

| Parameter                     | C3, I3L   | C4, I4    | Unit |

|-------------------------------|-----------|-----------|------|

| DLL operating frequency range | 300 – 890 | 300 – 890 | MHz  |

### **DQS Logic Block Specifications**

#### Table 2-48: DQS Phase Offset Delay Per Setting for Arria V GZ Devices

The typical value equals the average of the minimum and maximum values.

The delay settings are linear with a cumulative delay variation of 40 ps for all speed grades. For example, when using a -3 speed grade and applying a 10-phase offset setting to a 90° phase shift at 400 MHz, the expected average cumulative delay is  $[625 \text{ ps} + (10 \times 11 \text{ ps}) \pm 20 \text{ ps}] = 735 \text{ ps} \pm 20 \text{ ps}$ .

| Speed Grade | Min | Max | Unit |

|-------------|-----|-----|------|

| C3, I3L     | 8   | 15  | ps   |

| C4, I4      | 8   | 16  | ps   |

## Table 2-49: DQS Phase Shift Error Specification for DLL-Delayed Clock (t<sub>DQS\_PSERR</sub>) for Arria V GZ Devices

This error specification is the absolute maximum and minimum error. For example, skew on three DQS delay buffers in a -3 speed grade is  $\pm 84$  ps or  $\pm 42$  ps.

| Number of DQS Delay Buffers | C3, I3L | C4, I4 | Unit |

|-----------------------------|---------|--------|------|

| 1                           | 30      | 32     | ps   |

| 2                           | 60      | 64     | ps   |

| 3                           | 90      | 96     | ps   |

## **OCT Calibration Block Specifications**

Table 2-51: OCT Calibration Block Specifications for Arria V GZ Devices

| Symbol                | Description                                                                                                                                                                             | Min | Тур  | Max | Unit   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by the OCT calibration blocks                                                                                                                                            | _   | _    | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of OCTUSRCLK clock cycles required for OCT R <sub>S</sub> /R <sub>T</sub> calibration                                                                                            | _   | 1000 | _   | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for the OCT code to shift out                                                                                                                 | _   | 32   | _   | Cycles |

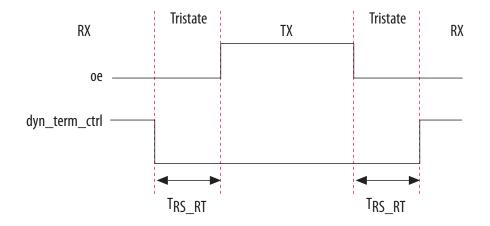

| T <sub>RS_RT</sub>    | Time required between the $\tt dyn\_term\_ctrl$ and $\tt oe$ signal transitions in a bidirectional I/O buffer to dynamically switch between OCT $R_S$ and $R_T$ (See the figure below.) | _   | 2.5  | _   | ns     |

Figure 2-6: Timing Diagram for oe and dyn\_term\_ctrl Signals

| Symbol             | Parameter                                         | Minimum                                     | Maximum | Unit |

|--------------------|---------------------------------------------------|---------------------------------------------|---------|------|

| $t_{\rm CD2CU}$    | CONF_DONE high to CLKUSR enabled                  | 4 × maximum                                 | _       | _    |

|                    |                                                   | DCLK period                                 |         |      |

| t <sub>CD2UM</sub> | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> + (8576 × CLKUSR period) | _       | _    |

#### **Related Information**

- DCLK-to-DATA[] Ratio (r) for FPP Configuration on page 2-57

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

<sup>(208)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the *Configuration*, *Design Security, and Remote System Upgrades in Arria V Devices* chapter.

| Symbol              | Parameter                                         | Minimum                                     | Maximum | Unit |

|---------------------|---------------------------------------------------|---------------------------------------------|---------|------|

| $t_{CO}$            | DCLK falling edge to AS_DATA0/ASDO output         | _                                           | 4       | ns   |

| t <sub>SU</sub>     | Data setup time before falling edge on DCLK       | 1.5                                         | _       | ns   |

| $t_{\rm H}$         | Data hold time after falling edge on DCLK         | 0                                           | _       | ns   |

| $t_{CD2UM}$         | CONF_DONE high to user mode (216)                 | 175                                         | 437     | μs   |

| $t_{\rm CD2CU}$     | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK period                     | _       | _    |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> + (8576 × CLKUSR period) | _       | _    |

#### Table 2-59: DCLK Frequency Specification in the AS Configuration Scheme

This applies to the DCLK frequency specification when using the internal oscillator as the configuration clock source.

The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

| 10.6    | 15.7    | 25.0    | MHz  |

| 21.3    | 31.4    | 50.0    | MHz  |

| 42.6    | 62.9    | 100.0   | MHz  |

#### **Related Information**

- Passive Serial Configuration Timing on page 2-67

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Altera Corporation

Arria V GZ Device Datasheet

<sup>(216)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on this pin, refer to the "Initialization" section of the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.