Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 19811                                                      |

| Number of Logic Elements/Cells | 420000                                                     |

| Total RAM Bits                 | 23625728                                                   |

| Number of I/O                  | 704                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1517-BBGA                                                  |

| Supplier Device Package        | 1517-FBGA (40x40)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxfb5k4f40c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Caution:** Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

Table 1-1: Absolute Maximum Ratings for Arria V Devices

| Symbol                    | Description                                                                                          | Minimum | Maximum | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------|---------|---------|------|

| $V_{CC}$                  | Core voltage power supply                                                                            | -0.50   | 1.43    | V    |

| V <sub>CCP</sub>          | Periphery circuitry, PCIe® hardIP block, and transceiver physical coding sublayer (PCS) power supply | -0.50   | 1.43    | V    |

| V <sub>CCPGM</sub>        | Configuration pins power supply                                                                      | -0.50   | 3.90    | V    |

| V <sub>CC_AUX</sub>       | Auxiliary supply                                                                                     | -0.50   | 3.25    | V    |

| V <sub>CCBAT</sub>        | Battery back-up power supply for design security volatile key register                               | -0.50   | 3.90    | V    |

| V <sub>CCPD</sub>         | I/O pre-driver power supply                                                                          | -0.50   | 3.90    | V    |

| V <sub>CCIO</sub>         | I/O power supply                                                                                     | -0.50   | 3.90    | V    |

| V <sub>CCD_FPLL</sub>     | Phase-locked loop (PLL) digital power supply                                                         | -0.50   | 1.80    | V    |

| V <sub>CCA_FPLL</sub>     | PLL analog power supply                                                                              | -0.50   | 3.25    | V    |

| V <sub>CCA_GXB</sub>      | Transceiver high voltage power                                                                       | -0.50   | 3.25    | V    |

| V <sub>CCH_GXB</sub>      | Transmitter output buffer power                                                                      | -0.50   | 1.80    | V    |

| V <sub>CCR_GXB</sub>      | Receiver power                                                                                       | -0.50   | 1.50    | V    |

| V <sub>CCT_GXB</sub>      | Transmitter power                                                                                    | -0.50   | 1.50    | V    |

| V <sub>CCL_GXB</sub>      | Transceiver clock network power                                                                      | -0.50   | 1.50    | V    |

| $\overline{V_{I}}$        | DC input voltage                                                                                     | -0.50   | 3.80    | V    |

| V <sub>CC_HPS</sub>       | HPS core voltage and periphery circuitry power supply                                                | -0.50   | 1.43    | V    |

| V <sub>CCPD_HPS</sub>     | HPS I/O pre-driver power supply                                                                      | -0.50   | 3.90    | V    |

| V <sub>CCIO_HPS</sub>     | HPS I/O power supply                                                                                 | -0.50   | 3.90    | V    |

| V <sub>CCRSTCLK_HPS</sub> | HPS reset and clock input pins power supply                                                          | -0.50   | 3.90    | V    |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

Transceiver Specifications for Arria V GT and ST Devices on page 1-29

Provides the specifications for transmitter, receiver, and reference clock I/O pin.

# **Switching Characteristics**

This section provides performance characteristics of Arria V core and periphery blocks.

## **Transceiver Performance Specifications**

Transceiver Specifications for Arria V GX and SX Devices

Table 1-20: Reference Clock Specifications for Arria V GX and SX Devices

| Symbol/Description                      | Condition                                                | Trans        | ceiver Speed Gr | ade 4                         | Transco        | eiver Speed G            | irade 6                       | Unit  |

|-----------------------------------------|----------------------------------------------------------|--------------|-----------------|-------------------------------|----------------|--------------------------|-------------------------------|-------|

| Symbol/Description                      | Condition                                                | Min          | Тур             | Max                           | Min            | Тур                      | Max                           | Offic |

| Supported I/O standards                 | 1.2 V PCM                                                | L, 1.4 V PCN | L,1.5 V PCML    | , 2.5 V PCMI                  | L, Differentia | LVPECL <sup>(23)</sup> , | HCSL, and                     | LVDS  |

| Input frequency from REFCLK input pins  | _                                                        | 27           | _               | 710                           | 27             | _                        | 710                           | MHz   |

| Rise time                               | Measure at ±60 mV of differential signal <sup>(24)</sup> | _            | _               | 400                           | _              | _                        | 400                           | ps    |

| Fall time                               | Measure at ±60 mV of differential signal <sup>(24)</sup> | _            | _               | 400                           | _              | _                        | 400                           | ps    |

| Duty cycle                              | _                                                        | 45           | _               | 55                            | 45             | _                        | 55                            | %     |

| Peak-to-peak differential input voltage | _                                                        | 200          | _               | 300 <sup>(25)</sup> /<br>2000 | 200            | _                        | 300 <sup>(25)</sup> /<br>2000 | mV    |

Send Feedback

<sup>(23)</sup> Differential LVPECL signal levels must comply to the minimum and maximum peak-to-peak differential input voltage specified in this table.

<sup>(24)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

<sup>(25)</sup> The maximum peak-to peak differential input voltage of 300 mV is allowed for DC coupled link.

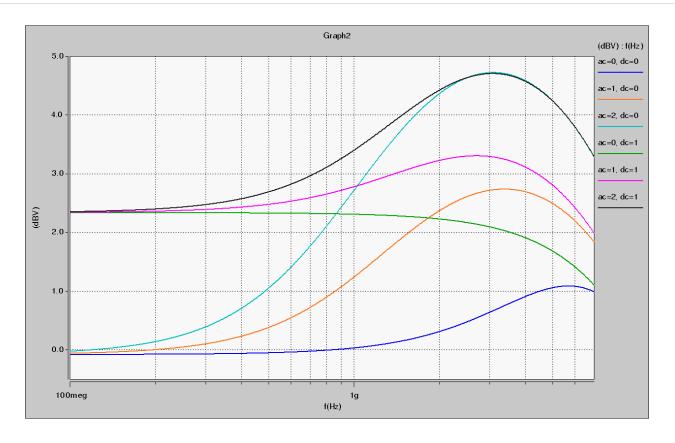

## CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain

Figure 1-2: Continuous Time-Linear Equalizer (CTLE) Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

| Protocol                             | Sub-protocol      | Data Rate (Mbps) |

|--------------------------------------|-------------------|------------------|

|                                      | CPRI E6LV         | 614.4            |

|                                      | CPRI E6HV         | 614.4            |

|                                      | CPRI E6LVII       | 614.4            |

|                                      | CPRI E12LV        | 1,228.8          |

|                                      | CPRI E12HV        | 1,228.8          |

|                                      | CPRI E12LVII      | 1,228.8          |

| Common Public Radio Interface (CPRI) | CPRI E24LV        | 2,457.6          |

|                                      | CPRI E24LVII      | 2,457.6          |

|                                      | CPRI E30LV        | 3,072            |

|                                      | CPRI E30LVII      | 3,072            |

|                                      | CPRI E48LVII      | 4,915.2          |

|                                      | CPRI E60LVII      | 6,144            |

|                                      | CPRI E96LVIII(60) | 9,830.4          |

| Gbps Ethernet (GbE)                  | GbE 1250          | 1,250            |

|                                      | OBSAI 768         | 768              |

| OBSAI                                | OBSAI 1536        | 1,536            |

| OBSAI                                | OBSAI 3072        | 3,072            |

|                                      | OBSAI 6144        | 6,144            |

|                                      | SDI 270 SD        | 270              |

| Serial digital interface (SDI)       | SDI 1485 HD       | 1,485            |

|                                      | SDI 2970 3G       | 2,970            |

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

<sup>(60)</sup> You can achieve compliance with TX channel restriction of one HSSI channel per six-channel transceiver bank.

| Symbol                                                                                                                                       | Condition                                                |      | −l3, −C4 |      |      | −l5, −C5 |      |      | -C6 |      | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|----------|------|------|----------|------|------|-----|------|------|

| Зупірої                                                                                                                                      | Condition                                                | Min  | Тур      | Max  | Min  | Тур      | Max  | Min  | Тур | Max  | Onit |

|                                                                                                                                              | SERDES factor $J \ge 8^{(76)(78)}$ , LVDS TX with RX DPA | (77) | _        | 1600 | (77) | _        | 1500 | (77) | _   | 1250 | Mbps |

|                                                                                                                                              | SERDES factor J = 1<br>to 2, Uses DDR<br>Registers       | (77) | _        | (79) | (77) | _        | (79) | (77) | _   | (79) | Mbps |

| Emulated Differential I/<br>O Standards with Three<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup> | SERDES factor J = 4<br>to 10 <sup>(81)</sup>             | (77) | _        | 945  | (77) | _        | 945  | (77) | _   | 945  | Mbps |

| Emulated Differential I/<br>O Standards with One<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup>   | SERDES factor J = 4<br>to 10 <sup>(81)</sup>             | (77) | _        | 200  | (77) | _        | 200  | (77) | _   | 200  | Mbps |

| t <sub>x Jitter</sub> -True Differential<br>I/O Standards                                                                                    | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps    | _    | _        | 160  | _    | _        | 160  | _    | _   | 160  | ps   |

| 1/O Standards                                                                                                                                | Total Jitter for Data<br>Rate < 600 Mbps                 | _    | _        | 0.1  | _    | _        | 0.1  | _    | _   | 0.1  | UI   |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

$<sup>^{(78)}\,</sup>$  The  $V_{CC}$  and  $V_{CCP}$  must be on a separate power layer and a maximum load of 5 pF for chip-to-chip interface.

<sup>(79)</sup> The maximum ideal data rate is the SERDES factor (J) x the PLL maximum output frequency (f<sub>OUT</sub>), provided you can close the design timing and the signal integrity simulation is clean.

You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine the leftover timing margin.

<sup>(81)</sup> When using True LVDS RX channels for emulated LVDS TX channel, only serialization factors 1 and 2 are supported.

|                  | Symbol                                                    | Condition                                            |      | −I3, −C4 |       |      | −l5, −C5 |       |      | -C6 |       | Unit  |

|------------------|-----------------------------------------------------------|------------------------------------------------------|------|----------|-------|------|----------|-------|------|-----|-------|-------|

|                  | Зупівої                                                   | Condition                                            | Min  | Тур      | Max   | Min  | Тур      | Max   | Min  | Тур | Max   | Offic |

|                  | TCCS                                                      | True Differential I/O<br>Standards                   | _    | _        | 150   | _    | _        | 150   | _    | _   | 150   | ps    |

|                  | 1003                                                      | Emulated Differential I/O Standards                  |      | _        | 300   | _    | _        | 300   | _    | _   | 300   | ps    |

|                  | True Differential I/O<br>Standards - f <sub>HSDRDPA</sub> | SERDES factor J =3 to 10 <sup>(76)</sup>             | 150  | _        | 1250  | 150  | _        | 1250  | 150  | _   | 1050  | Mbps  |

|                  | (data rate)                                               | SERDES factor $J \ge 8$ with DPA <sup>(76)(78)</sup> | 150  | _        | 1600  | 150  | _        | 1500  | 150  | _   | 1250  | Mbps  |

| Receiver         |                                                           | SERDES factor J = 3<br>to 10                         | (77) | _        | (83)  | (77) | _        | (83)  | (77) | _   | (83)  | Mbps  |

|                  | f <sub>HSDR</sub> (data rate)                             | SERDES factor J = 1<br>to 2, uses DDR<br>registers   | (77) | _        | (79)  | (77) | _        | (79)  | (77) | _   | (79)  | Mbps  |

| DPA Mode         | DPA run length                                            | _                                                    | _    | _        | 10000 | _    | _        | 10000 | _    | _   | 10000 | UI    |

| Soft-CDR<br>Mode | Soft-CDR ppm tolerance                                    | _                                                    | _    | _        | 300   | _    | _        | 300   | _    | _   | 300   | ±ppm  |

| Non-DPA<br>Mode  | Sampling Window                                           | _                                                    | _    | _        | 300   | _    | _        | 300   | _    | _   | 300   | ps    |

You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

## **Memory Output Clock Jitter Specifications**

## Table 1-45: Memory Output Clock Jitter Specifications for Arria V Devices

The memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2/DDR3 SDRAM standard. The memory output clock jitter is applicable when an input jitter of 30 ps (p-p) is applied with bit error rate (BER)  $10^{-12}$ , equivalent to 14 sigma. Altera recommends using the UniPHY intellectual property (IP) with PHYCLK connections for better jitter performance.

| Parameter                    | Clock Network | Symbol                | -l3, | -C4 | − <b>I</b> 5, | -C5 | -(  | <b>C6</b> | Unit |

|------------------------------|---------------|-----------------------|------|-----|---------------|-----|-----|-----------|------|

| raiailletei                  | Clock Network | Зуппоот               | Min  | Max | Min           | Max | Min | Max       | Onit |

| Clock period jitter          | PHYCLK        | t <sub>JIT(per)</sub> | -41  | 41  | -50           | 50  | -55 | 55        | ps   |

| Cycle-to-cycle period jitter | PHYCLK        | t <sub>JIT(cc)</sub>  | 6    | 3   | 9             | 0   | 9   | 4         | ps   |

## **OCT Calibration Block Specifications**

Table 1-46: OCT Calibration Block Specifications for Arria V Devices

| Symbol                | Description                                                                                                                                                 | Min | Тур  | Max | Unit   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by OCT calibration blocks                                                                                                                    | _   | _    | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of octusrclk clock cycles required for $R_{S}$ OCT/ $\!R_{T}$ OCT calibration                                                                        | _   | 1000 | _   | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for OCT code to shift out                                                                                         | _   | 32   | _   | Cycles |

| $T_{RS\_RT}$          | Time required between the $dyn\_term\_ctrl$ and $oe$ signal transitions in a bidirectional I/O buffer to dynamically switch between $R_S$ OCT and $R_T$ OCT | _   | 2.5  | _   | ns     |

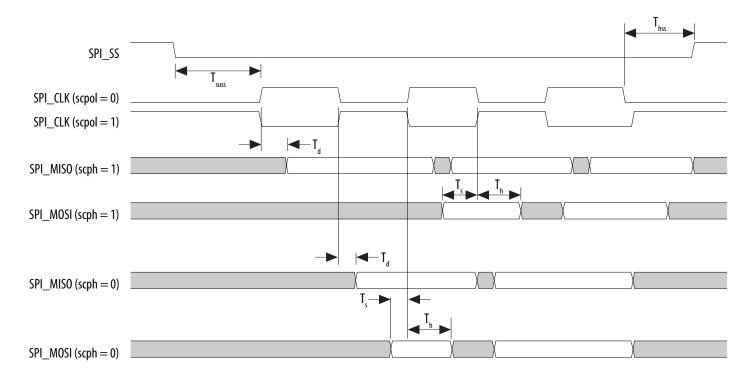

Figure 1-10: SPI Slave Timing Diagram

#### **Related Information**

SPI Controller, Arria V Hard Processor System Technical Reference Manual

Provides more information about rx\_sample\_delay.

## **SD/MMC Timing Characteristics**

## Table 1-54: Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Arria V Devices

After power up or cold reset, the Boot ROM uses <code>drvsel = 3</code> and <code>smplsel = 0</code> to execute the code. At the same time, the SD/MMC controller enters the Identification Phase followed by the Data Phase. During this time, the value of interface output clock <code>SDMMC\_CLK\_OUT</code> changes from a maximum of 400 kHz (Identification Phase) up to a maximum of 12.5 MHz (Data Phase), depending on the internal reference clock <code>SDMMC\_CLK</code> and the <code>CSEL</code> setting. The value of <code>SDMMC\_CLK</code> is based on the external oscillator frequency and has a maximum value of 50 MHz.

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

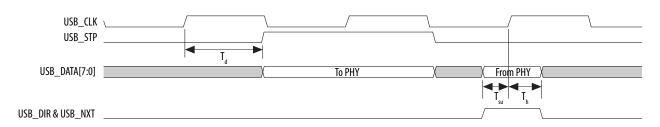

Figure 1-12: USB Timing Diagram

## **Ethernet Media Access Controller (EMAC) Timing Characteristics**

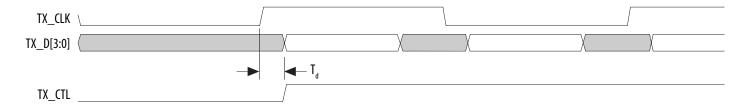

Table 1-56: Reduced Gigabit Media Independent Interface (RGMII) TX Timing Requirements for Arria V Devices

| Symbol                        | Description                            | Min   | Тур | Max  | Unit |

|-------------------------------|----------------------------------------|-------|-----|------|------|

| T <sub>clk</sub> (1000Base-T) | TX_CLK clock period                    | _     | 8   | _    | ns   |

| T <sub>clk</sub> (100Base-T)  | TX_CLK clock period                    | _     | 40  | _    | ns   |

| T <sub>clk</sub> (10Base-T)   | TX_CLK clock period                    | _     | 400 | _    | ns   |

| T <sub>dutycycle</sub>        | TX_CLK duty cycle                      | 45    | _   | 55   | %    |

| $T_d$                         | TX_CLK to TXD/TX_CTL output data delay | -0.85 | _   | 0.15 | ns   |

Figure 1-13: RGMII TX Timing Diagram

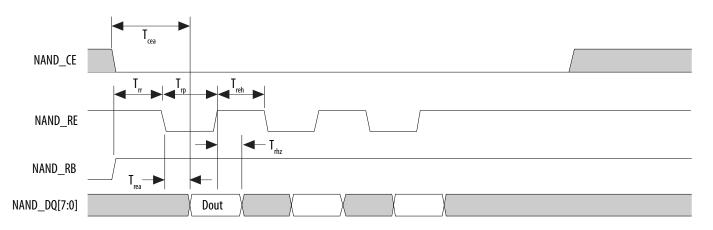

Figure 1-20: NAND Data Read Timing Diagram

## **ARM Trace Timing Characteristics**

Table 1-61: ARM Trace Timing Requirements for Arria V Devices

Most debugging tools have a mechanism to adjust the capture point of trace data.

| Description                     | Min  | Max | Unit |

|---------------------------------|------|-----|------|

| CLK clock period                | 12.5 | _   | ns   |

| CLK maximum duty cycle          | 45   | 55  | %    |

| CLK to D0 –D7 output data delay | -1   | 1   | ns   |

### **UART Interface**

The maximum UART baud rate is 6.25 megasymbols per second.

### **GPIO** Interface

The minimum detectable general-purpose I/O (GPIO) pulse width is 2  $\mu s$ . The pulse width is based on a debounce clock frequency of 1 MHz.

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

| Symbol       | Parameter                        | Typical     | Unit |

|--------------|----------------------------------|-------------|------|

|              |                                  | 0 (default) | ps   |

| D            | Rising and/or falling edge delay | 50          | ps   |

| $D_{OUTBUF}$ | Kishig and/or faming edge delay  | 100         | ps   |

|              |                                  | 150         | ps   |

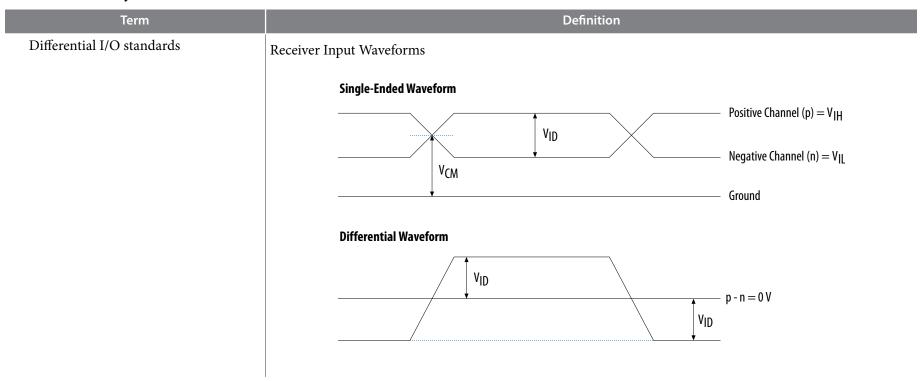

# Glossary

Table 1-78: Glossary

Arria V GX, GT, SX, and ST Device Datasheet **Altera Corporation**

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.8     | <ul> <li>Added a note in Table 3, Table 4, and Table 5: The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.</li> <li>Updated V<sub>CC_HPS</sub> specification in Table 5.</li> <li>Added a note in Table 19: Differential inputs are powered by V<sub>CCPD</sub> which requires 2.5 V.</li> <li>Updated "Minimum differential eye opening at the receiver serial input pins" specification in Table 20 and Table 21.</li> <li>Updated description in "HPS PLL Specifications" section.</li> <li>Updated VCO range maximum specification in Table 39.</li> <li>Updated T<sub>d</sub> and T<sub>h</sub> specifications in Table 45.</li> <li>Added T<sub>h</sub> specification in Table 47 and Figure 13.</li> <li>Updated a note in Figure 20, Figure 21, and Figure 23 as follows: Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.</li> <li>Removed "Remote update only in AS mode" specification in Table 58.</li> <li>Added DCLK device initialization clock source specification in Table 60.</li> <li>Added description in "Configuration Files" section: The IOCSR .rbf size is specifically for the Configuration via Protocol (CvP) feature.</li> <li>Removed f<sub>MAX_RU_CLK</sub> specification in Table 63.</li> </ul> |

| February 2014 | 3.7     | $ \begin{array}{ll} \bullet & \mbox{Updated $V_{CCRSTCLK\_HPS}$ maximum specification in Table 1.} \\ \bullet & \mbox{Added $V_{CC\_AUX\_SHARED}$ specification in Table 1.} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| December 2013 | 3.6     | <ul> <li>Added "HPS PLL Specifications".</li> <li>Added Table 24, Table 39, and Table 40.</li> <li>Updated Table 1, Table 3, Table 5, Table 19, Table 20, Table 21, Table 38, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, Table 50, Table 51, Table 55, Table 56, and Table 59.</li> <li>Updated Figure 7, Figure 13, Figure 15, Figure 16, and Figure 19.</li> <li>Removed table: GPIO Pulse Width for Arria V Devices.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

### **Transceiver Power Supply Requirements**

Table 2-7: Transceiver Power Supply Voltage Requirements for Arria V GZ Devices

| Conditions                                                                                                                                | VCCR_GXB and VCCT_GXB (122) | VCCA_GXB | VCCH_GXB | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------|----------|------|

| If BOTH of the following conditions are true:                                                                                             | 1.05                        |          |          |      |

| <ul><li>Data rate &gt; 10.3 Gbps.</li><li>DFE is used.</li></ul>                                                                          |                             |          |          |      |

| If ANY of the following conditions are true (123):                                                                                        | 1.0                         | 3.0      |          |      |

| <ul> <li>ATX PLL is used.</li> <li>Data rate &gt; 6.5Gbps.</li> <li>DFE (data rate ≤ 10.3 Gbps), AEQ, or EyeQ feature is used.</li> </ul> |                             |          | 1.5      | V    |

| If ALL of the following conditions are true:                                                                                              | 0.85                        | 2.5      |          |      |

| ATX PLL is not used.                                                                                                                      |                             |          |          |      |

| <ul> <li>Data rate ≤ 6.5Gbps.</li> <li>DFE, AEQ, and EyeQ are not used.</li> </ul>                                                        |                             |          |          |      |

| • Dre, Aeq, and eyeq are not used.                                                                                                        |                             |          |          |      |

#### **DC Characteristics**

## **Supply Current**

Standby current is the current drawn from the respective power rails used for power budgeting.

Use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design because these currents vary greatly with the resources you use.

Altera Corporation Arria V GZ Device Datasheet

<sup>(122)</sup> If the VCCR\_GXB and VCCT\_GXB supplies are set to 1.0 V or 1.05 V, they cannot be shared with the VCC core supply. If the VCCR\_GXB and VCCT\_GXB are set to 0.85 V, they can be shared with the VCC core supply.

<sup>(123)</sup> Choose this power supply voltage requirement option if you plan to upgrade your design later with any of the listed conditions.

| I/O Standard           |      | V <sub>CCIO</sub> (\ | <b>/</b> ) | V <sub>DIF</sub> | <sub>(DC)</sub> (V)     |                                      | $V_{X(AC)}(V)$        |                                     | V <sub>CN</sub>           | <sub>И(DC)</sub> (V               | )                            | V    | <sub>DIF(AC)</sub> (V)      |

|------------------------|------|----------------------|------------|------------------|-------------------------|--------------------------------------|-----------------------|-------------------------------------|---------------------------|-----------------------------------|------------------------------|------|-----------------------------|

| 1/O Standard           | Min  | Тур                  | Max        | Min              | Max                     | Min                                  | Тур                   | Max                                 | Min                       | Тур                               | Max                          | Min  | Max                         |

| HSTL-12 Class<br>I, II | 1.14 | 1.2                  | 1.26       | 0.16             | V <sub>CCIO</sub> + 0.3 | _                                    | $0.5 \times V_{CCIO}$ | _                                   | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub><br>IO | $0.6 \times V_{\text{CCIO}}$ | 0.3  | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14 | 1.2                  | 1.3        | 0.26             | 0.26                    | 0.5 ×<br>V <sub>CCIO</sub> –<br>0.12 | $0.5 \times V_{CCIO}$ | $0.5 \times V_{\rm CCIO} \\ + 0.12$ | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub>       | 0.6 ×<br>V <sub>CCIO</sub>   | 0.44 | 0.44                        |

Table 2-21: Differential I/O Standard Specifications for Arria V GZ Devices

| I/O Standard   | V <sub>CCIO</sub> (V) <sup>(128)</sup>                                                                                                                                                                                                                |     | V <sub>ID</sub> (mV) <sup>(129)</sup> |     | V <sub>ICM(DC)</sub> (V) |     | V <sub>OD</sub> (V) <sup>(130)</sup> |                                |      | V <sub>OCM</sub> (V) (130) |     |     |       |      |       |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------|-----|--------------------------|-----|--------------------------------------|--------------------------------|------|----------------------------|-----|-----|-------|------|-------|

| i/O Standard   | Min                                                                                                                                                                                                                                                   | Тур | Max                                   | Min | Condition                | Max | Min                                  | Condition                      | Max  | Min                        | Тур | Max | Min   | Тур  | Max   |

| PCML           | Transmitter, receiver, and input reference clock pins of the high-speed transceivers use the PCML I/O standard. For transmitter, receiver, and reference clock I/O pin specifications, refer to the "Transceiver Performance Specifications" section. |     |                                       |     |                          |     |                                      |                                |      |                            |     |     |       |      |       |

| 2.5 V<br>LVDS  | 2.375 2.5                                                                                                                                                                                                                                             | 2.5 | 2.625                                 | 100 | V <sub>CM</sub> =        | _   | 0.05                                 | D <sub>MAX</sub> ≤<br>700 Mbps | 1.8  | 0.247                      | _   | 0.6 | 1.125 | 1.25 | 1.375 |

| (131)          | 2.373                                                                                                                                                                                                                                                 | 2.3 | 2.023                                 | 100 | 1.25 V                   | _   | 1.05                                 | D <sub>MAX</sub> > 700 Mbps    | 1.55 | 0.247                      | _   | 0.6 | 1.125 | 1.25 | 1.375 |

| BLVDS<br>(132) | 2.375                                                                                                                                                                                                                                                 | 2.5 | 2.625                                 | 100 | _                        | _   | _                                    | _                              | _    | _                          | _   | _   | _     | _    | _     |

$<sup>^{\</sup>left(128\right)}\,$  Differential inputs are powered by VCCPD which requires 2.5 V.

Arria V GZ Device Datasheet

Altera Corporation

<sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>(130)</sup> RL range:  $90 \le RL \le 110 \Omega$ .

<sup>(131)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.6 V for data rates above 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

<sup>(132)</sup> There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

|                    | ATX PLL                   |                       |                                                                                                       |                           | CMU PLL (161)         |                                                |                           | fPLL                  |                                                      |  |  |

|--------------------|---------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|------------------------------------------------|---------------------------|-----------------------|------------------------------------------------------|--|--|

| Clock Network      | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                                                                       | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                      |  |  |

| xN (PCIe)          | _                         | 8.0                   | 8                                                                                                     | _                         | 5.0                   | 8                                              | _                         | _                     | _                                                    |  |  |

| xN (Native PHY IP) | 8.0                       | 8.01 to<br>9.8304     | Up to 13<br>channels<br>above and<br>below PLL<br>Up to 7<br>channels<br>above<br>and<br>below<br>PLL | 7.99                      | 7.99                  | Up to 13<br>channels<br>above and<br>below PLL | 3.125                     | 3.125                 | Up to 13<br>channels<br>above<br>and<br>below<br>PLL |  |  |

#### **Standard PCS Data Rate**

## Table 2-30: Standard PCS Approximate Maximum Date Rate (Gbps) for Arria V GZ Devices

The maximum data rate is also constrained by the transceiver speed grade. Refer to the "Commercial and Industrial Speed Grade Offering for Arria V GZ Devices" table for the transceiver speed grade.

| Mode (164)  | Modo (164) Transceiver   | PMA Width                  | 20  | 20   | 16  | 16   | 10  | 10   | 8    | 8    |

|-------------|--------------------------|----------------------------|-----|------|-----|------|-----|------|------|------|

| Speed Grade | PCS/Core Width           | 40                         | 20  | 32   | 16  | 20   | 10  | 16   | 8    |      |

| FIFO 2      | C3, I3L core speed grade | 9.9                        | 9   | 7.84 | 7.2 | 5.3  | 4.7 | 4.24 | 3.76 |      |

| THO         | 3                        | C4, I4<br>core speed grade | 8.8 | 8.2  | 7.2 | 6.56 | 4.8 | 4.3  | 3.84 | 3.44 |

<sup>(161)</sup> ATX PLL is recommended at 8 Gbps and above data rates for improved jitter performance.

Altera Corporation

Arria V GZ Device Datasheet

<sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

| Symbol                                        | Parameter                                                                                                     | Min | Тур | Max  | Unit      |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----|------|-----------|

| t <sub>OUTPJ_IO</sub> , (173), (175)          | Period Jitter for a clock output on a regular I/O in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )            | _   | _   | 600  | ps (p-p)  |

| COUTPJ_IO ,                                   | Period Jitter for a clock output on a regular I/O in integer PLL ( $f_{OUT}$ < 100 MHz)                       | _   | _   | 60   | mUI (p-p) |

| t(173) (175) (176)                            | Period Jitter for a clock output on a regular I/O in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )         | _   | _   | 600  | ps (p-p)  |

| t <sub>FOUTPJ_IO</sub> (1733), (1755), (1766) | Period Jitter for a clock output on a regular I/O in fractional PLL ( $f_{OUT}$ < 100 MHz)                    | _   | _   | 60   | mUI (p-p) |

| t <sub>OUTCCJ_IO</sub> (173), (175)           | Cycle-to-cycle Jitter for a clock output on a regular I/O in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )    | _   | _   | 600  | ps (p-p)  |

| OUTCCJ_IO * * * *                             | Cycle-to-cycle Jitter for a clock output on a regular I/O in integer PLL ( $f_{OUT}$ < 100 MHz)               | _   | _   | 60   | mUI (p-p) |

| t <sub>FOUTCCJ_IO</sub> (173), (175), (176)   | Cycle-to-cycle Jitter for a clock output on a regular I/O in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ ) | _   | _   | 600  | ps (p-p)  |

| FOUTCCJ_IO * *, * *, * *, * *                 | Cycle-to-cycle Jitter for a clock output on a regular I/O in fractional PLL ( $f_{OUT}$ < 100 MHz)            | _   | _   | 60   | mUI (p-p) |

| (173) (177)                                   | Period Jitter for a dedicated clock output in cascaded PLLs ( $f_{OUT} \ge 100 \text{ MHz}$ )                 | _   | _   | 175  | ps (p-p)  |

| t <sub>CASC_OUTPJ_DC</sub> (173), (177)       | Period Jitter for a dedicated clock output in cascaded PLLS (f <sub>OUT</sub> < 100 MHz)                      | _   | _   | 17.5 | mUI (p-p) |

| dK <sub>BIT</sub>                             | Bit number of Delta Sigma Modulator (DSM)                                                                     | 8   | 24  | 32   | Bits      |

<sup>(175)</sup> The external memory interface clock output jitter specifications use a different measurement method, which is available in the "Memory Output Clock Jitter Specification for Arria V GZ Devices" table.

a. Upstream PLL:  $0.59 \text{Mhz} \leq \text{Upstream PLL BW} < 1 \text{ MHz}$

b. Downstream PLL: Downstream PLL BW > 2 MHz

Altera Corporation

Arria V GZ Device Datasheet

This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.05–0.95 must be  $\geq$  1000 MHz.

<sup>(177)</sup> The cascaded PLL specification is only applicable with the following condition:

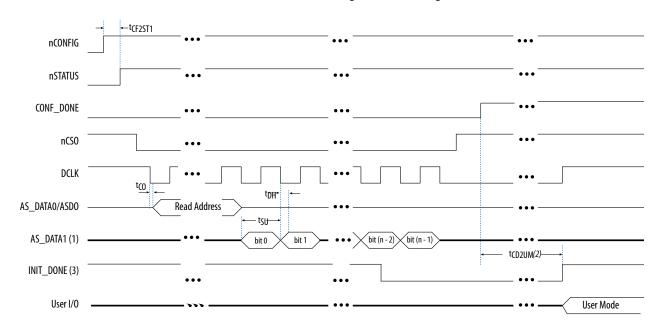

# **Active Serial Configuration Timing**

## Figure 2-9: AS Configuration Timing

Timing waveform for the active serial (AS) x1 mode and AS x4 mode configuration timing.

#### Notes:

- 1. If you are using AS ×4 mode, this signal represents the AS\_DATA[3..0] and EPCQ sends in 4-bits of data for each DCLKcycle.

- 2. The initialization clock can be from internal oscillator or CLKUSR pin

- 3. After the option bit to enable the INIT\_DONE pin isconfigured into the device, the INIT\_DONE ges low.

## Table 2-58: AS Timing Parameters for AS x1 and AS x4 Configurations in Arria V GZ Devices

The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

$t_{CF2CD}$ ,  $t_{CF2ST0}$ ,  $t_{CFG}$ ,  $t_{STATUS}$ , and  $t_{CF2ST1}$  timing parameters are identical to the timing parameters for PS mode listed in the "PS Timing Parameters for Arria V GZ Devices" table.

Arria V GZ Device Datasheet

Altera Corporation

## Table 2-60: PS Timing Parameters for Arria V GZ Devices

| Symbol                   | Parameter                                         | Minimum                                                           | Maximum     | Unit |

|--------------------------|---------------------------------------------------|-------------------------------------------------------------------|-------------|------|

| t <sub>CF2CD</sub>       | nconfig low to conf_done low                      | _                                                                 | 600         | ns   |

| t <sub>CF2ST0</sub>      | nconfig low to nstatus low                        | _                                                                 | 600         | ns   |

| t <sub>CFG</sub>         | nconfig low pulse width                           | 2                                                                 | _           | μs   |

| t <sub>STATUS</sub>      | nstatus low pulse width                           | 268                                                               | 1,506 (217) | μs   |

| t <sub>CF2ST1</sub>      | nconfig high to nstatus high                      | _                                                                 | 1,506 (218) | μs   |

| t <sub>CF2CK</sub> (219) | nconfig high to first rising edge on DCLK         | 1,506                                                             | _           | μs   |

| t <sub>ST2CK</sub> (219) | nstatus high to first rising edge of DCLK         | 2                                                                 | _           | μs   |

| $t_{ m DSU}$             | DATA[] setup time before rising edge on DCLK      | 5.5                                                               | _           | ns   |

| t <sub>DH</sub>          | DATA[] hold time after rising edge on DCLK        | 0                                                                 | _           | ns   |

| t <sub>CH</sub>          | DCLK high time                                    | $0.45 \times 1/f_{MAX}$                                           | _           | S    |

| $t_{\rm CL}$             | DCLK low time                                     | $0.45 \times 1/f_{MAX}$                                           | _           | S    |

| $t_{CLK}$                | DCLK period                                       | 1/f <sub>MAX</sub>                                                | _           | S    |

| $f_{MAX}$                | DCLK frequency                                    | _                                                                 | 125         | MHz  |

| t <sub>CD2UM</sub>       | CONF_DONE high to user mode (220)                 | 175                                                               | 437         | μs   |

| t <sub>CD2CU</sub>       | CONF_DONE high to CLKUSR enabled                  | 4 × maximum DCLK period                                           | _           | _    |

| t <sub>CD2UMC</sub>      | CONF_DONE high to user mode with CLKUSR option on | $t_{\text{CD2CU}} + (8576 \times \text{CLKUSR})$<br>period) (221) | _           | _    |

$<sup>^{(217)}</sup>$  This value is applicable if you do not delay configuration by extending the nconfig or nstatus low pulse width.

Altera Corporation

Arria V GZ Device Datasheet

<sup>(218)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>(219)</sup> If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

<sup>(220)</sup> The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

#### Related Information

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

For more information about the reconfiguration input for the ALTREMOTE\_UPDATE IP core, refer to the "User Watchdog Timer" section.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

For more information about the reset\_timer input for the ALTREMOTE\_UPDATE IP core, refer to the "Remote System Upgrade State Machine" section.

## **User Watchdog Internal Oscillator Frequency Specification**

Table 2-65: User Watchdog Internal Oscillator Frequency Specifications

| Minimum | Typical | Maximum | Unit |  |  |

|---------|---------|---------|------|--|--|

| 5.3     | 7.9     | 12.5    | MHz  |  |  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O Timing and the Quartus II Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Quartus II Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

Arria V Devices Documentation page

For the Excel-based I/O Timing spreadsheet

Arria V GZ Device Datasheet Altera Corporation

<sup>(226)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "Remote System Upgrade State Machine" section in the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

<sup>(227)</sup> This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "User Watchdog Timer" section in the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2016     | 2016.06.20 | <ul> <li>Changed column heading from "Value" to "Maximum" in the "Pin Capacitance for Arria V GZ Devices" table.</li> <li>Changed the minimum supported data rate range values from "1000" to "2000" in the "ATX PLL Specifications for Arria V GZ Devices" table.</li> <li>Added the supported data rates for the following output standards using true LVDS output buffer types in the "High-Speed Clock Specifications for Arria V GZ Devices" table:</li> <li>True RSDS output standard: data rates of up to 230 Mbps</li> <li>True mini-LVDS output standard: data rates of up to 340 Mbps</li> </ul> |

| December 2015 | 2015.12.16 | <ul> <li>Removed the CDR ppm tolerance specification from the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Removed transmitter rise and fall time specifications from the "Transmitter Specifications for Arria V GZ Devices" table.</li> <li>Changed the .rbf sizes in the "Uncompressed .rbf Sizes for Arria V GZ Devices" table.</li> <li>Added a footnote to the "Transmitter High-Speed I/O Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                              |

| June 2015     | 2015.06.16 | <ul> <li>Changed the conditions for the reference clock rise and fall time and added a note to the condition in the "Reference Clock Specifications for Arria V GZ Devices" table.</li> <li>Added a note to the "Minimum differential eye opening at receiver serial input pins" specification in the "Receiver Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                                   |

| January 2015  | 2015.01.30 | <ul> <li>Added 240-Ω to the "OCT Calibration Accuracy Specifications for Arria V GZ Devices" table.</li> <li>Changed the CDR PPM tolerance spec in the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Added additional max data rate for fPLL in the "Fractional PLL Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                                                            |

Arria V GZ Device Datasheet

Altera Corporation