# E·XFL

## Intel - 5AGXMA1D4F27I5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 3537                                                       |

| Number of Logic Elements/Cells | 75000                                                      |

| Total RAM Bits                 | 8666112                                                    |

| Number of I/O                  | 336                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 672-BBGA, FCBGA                                            |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxma1d4f27i5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1-4 Recommended Operating Conditions

| Symbol  | Description              | Condition (V) | Overshoot Duration as % of High Time | Unit |   |

|---------|--------------------------|---------------|--------------------------------------|------|---|

|         |                          | 3.8           | 100                                  | %    |   |

|         |                          | 3.85          | 68                                   | %    |   |

|         |                          | 3.9           | 45                                   | %    |   |

|         |                          | 3.95          | 28                                   | %    |   |

|         |                          | 4             | 15                                   | %    |   |

|         |                          | 4.05          | 13                                   | %    |   |

|         |                          | 4.1           | 11                                   | %    |   |

|         | Vi (AC) AC input voltage |               | 4.15                                 | 9    | % |

| Vi (AC) |                          | 4.2           | 8                                    | %    |   |

|         |                          | 4.25          | 7                                    | %    |   |

|         |                          | 4.3           | 5.4                                  | %    |   |

|         |                          | 4.35          | 3.2                                  | %    |   |

|         |                          | 4.4           | 1.9                                  | %    |   |

|         |                          | 4.45          | 1.1                                  | %    |   |

|         |                          | 4.5           | 0.6                                  | %    |   |

|         |                          | 4.55          | 0.4                                  | %    |   |

|         |                          | 4.6           | 0.2                                  | %    |   |

# **Recommended Operating Conditions**

This section lists the functional operation limits for the AC and DC parameters for Arria V devices.

#### **Recommended Operating Conditions**

## Table 1-3: Recommended Operating Conditions for Arria V Devices

This table lists the steady-state voltage values expected from Arria V devices. Power supply ramps must all be strictly monotonic, without plateaus.

# Typical TX V<sub>OD</sub> Setting for Arria V Transceiver Channels with termination of 100 $\Omega$

| Table 1-32: Typical TX Vor | Setting for Arria V Transceive | r Channels with termination of 100 $\Omega$ |

|----------------------------|--------------------------------|---------------------------------------------|

|                            |                                |                                             |

| Symbol                                               | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|------------------------------------------------------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|                                                      | 6 <sup>(59)</sup>                       | 120                        | 34                                      | 680                        |

|                                                      | 7 <sup>(59)</sup>                       | 140                        | 35                                      | 700                        |

|                                                      | 8(59)                                   | 160                        | 36                                      | 720                        |

|                                                      | 9                                       | 180                        | 37                                      | 740                        |

|                                                      | 10                                      | 200                        | 38                                      | 760                        |

|                                                      | 11                                      | 220                        | 39                                      | 780                        |

|                                                      | 12                                      | 240                        | 40                                      | 800                        |

|                                                      | 13                                      | 260                        | 41                                      | 820                        |

|                                                      | 14                                      | 280                        | 42                                      | 840                        |

| V <sub>OD</sub> differential peak-to-peak<br>typical | 15                                      | 300                        | 43                                      | 860                        |

| -) <b>F</b>                                          | 16                                      | 320                        | 44                                      | 880                        |

|                                                      | 17                                      | 340                        | 45                                      | 900                        |

|                                                      | 18                                      | 360                        | 46                                      | 920                        |

|                                                      | 19                                      | 380                        | 47                                      | 940                        |

|                                                      | 20                                      | 400                        | 48                                      | 960                        |

|                                                      | 21                                      | 420                        | 49                                      | 980                        |

|                                                      | 22                                      | 440                        | 50                                      | 1000                       |

|                                                      | 23                                      | 460                        | 51                                      | 1020                       |

|                                                      | 24                                      | 480                        | 52                                      | 1040                       |

<sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

<sup>(59)</sup> Only valid for data rates  $\leq$  5 Gbps.

| Symbol | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|--------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|        | 25                                      | 500                        | 53                                      | 1060                       |

|        | 26                                      | 520                        | 54                                      | 1080                       |

|        | 27                                      | 540                        | 55                                      | 1100                       |

|        | 28                                      | 560                        | 56                                      | 1120                       |

|        | 29                                      | 580                        | 57                                      | 1140                       |

|        | 30                                      | 600                        | 58                                      | 1160                       |

|        | 31                                      | 620                        | 59                                      | 1180                       |

|        | 32                                      | 640                        | 60                                      | 1200                       |

|        | 33                                      | 660                        |                                         |                            |

## **Transmitter Pre-Emphasis Levels**

The following table lists the simulation data on the transmitter pre-emphasis levels in dB for the first post tap under the following conditions:

- Low-frequency data pattern—five 1s and five 0s

- Data rate—2.5 Gbps

The levels listed are a representation of possible pre-emphasis levels under the specified conditions only and the pre-emphasis levels may change with data pattern and data rate.

Arria V devices only support 1st post tap pre-emphasis with the following conditions:

- The 1st post tap pre-emphasis settings must satisfy  $|B| + |C| \le 60$  where  $|B| = V_{OD}$  setting with termination value,  $R_{TERM} = 100 \Omega$  and |C| = 1st post tap pre-emphasis setting.

- |B| |C| > 5 for data rates < 5 Gbps and |B| |C| > 8.25 for data rates > 5 Gbps.

- $(V_{MAX}/V_{MIN} 1)\% < 600\%$ , where  $V_{MAX} = |B| + |C|$  and  $V_{MIN} = |B| |C|$ .

Exception for PCIe Gen2 design:  $V_{OD}$  setting = 43 and pre-emphasis setting = 19 are allowed for PCIe Gen2 design with transmit de-emphasis – 6dB setting (pipe\_txdeemp = 1'b0) using Altera PCIe Hard IP and PIPE IP cores.

<sup>&</sup>lt;sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

| Protocol                                        | Sub-protocol | Data Rate (Mbps) |

|-------------------------------------------------|--------------|------------------|

|                                                 | SONET 155    | 155.52           |

| SONET                                           | SONET 622    | 622.08           |

|                                                 | SONET 2488   | 2,488.32         |

|                                                 | GPON 155     | 155.52           |

| Gigabit-capable passive optical network (GPON)  | GPON 622     | 622.08           |

| Orgabil-Capable passive optical network (Or ON) | GPON 1244    | 1,244.16         |

|                                                 | GPON 2488    | 2,488.32         |

| QSGMII                                          | QSGMII 5000  | 5,000            |

# **Core Performance Specifications**

# **Clock Tree Specifications**

# Table 1-35: Clock Tree Specifications for Arria V Devices

| Parameter                       |          | Unit     |     |      |

|---------------------------------|----------|----------|-----|------|

|                                 | -I3, -C4 | –I5, –C5 | -C6 | Onic |

| Global clock and Regional clock | 625      | 625      | 525 | MHz  |

| Peripheral clock                | 450      | 400      | 350 | MHz  |

# **PLL Specifications**

## Table 1-36: PLL Specifications for Arria V Devices

This table lists the Arria V PLL block specifications. Arria V PLL block does not include HPS PLL.

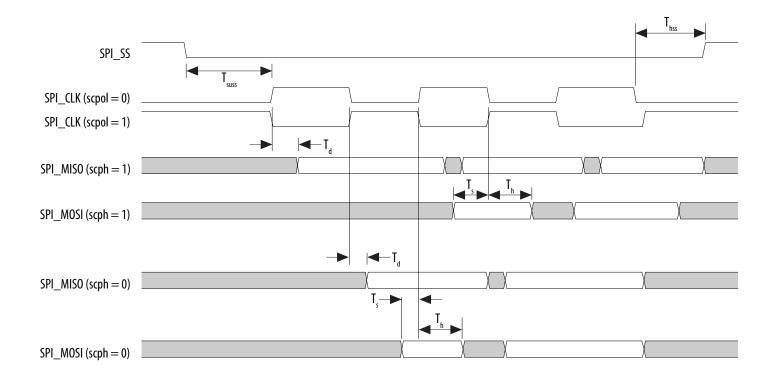

#### Figure 1-10: SPI Slave Timing Diagram

#### **Related Information**

#### SPI Controller, Arria V Hard Processor System Technical Reference Manual

Provides more information about rx\_sample\_delay.

## **SD/MMC Timing Characteristics**

#### Table 1-54: Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Arria V Devices

After power up or cold reset, the Boot ROM uses drvsel = 3 and smplsel = 0 to execute the code. At the same time, the SD/MMC controller enters the Identification Phase followed by the Data Phase. During this time, the value of interface output clock SDMMC\_CLK\_OUT changes from a maximum of 400 kHz (Identification Phase) up to a maximum of 12.5 MHz (Data Phase), depending on the internal reference clock SDMMC\_CLK and the CSEL setting. The value of SDMMC\_CLK is based on the external oscillator frequency and has a maximum value of 50 MHz.

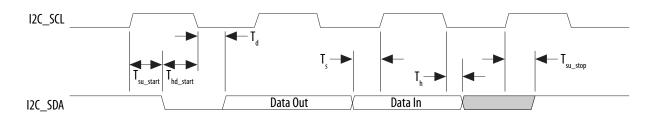

#### Figure 1-16: I<sup>2</sup>C Timing Diagram

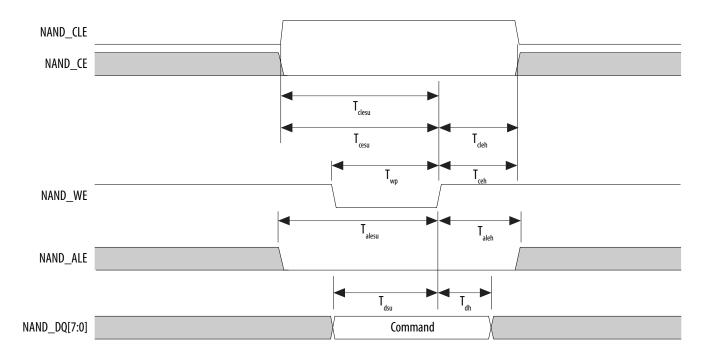

# **NAND Timing Characteristics**

#### Table 1-60: NAND ONFI 1.0 Timing Requirements for Arria V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the c4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                             | Description                                     | Min | Max | Unit |

|------------------------------------|-------------------------------------------------|-----|-----|------|

| T <sub>wp</sub> <sup>(89)</sup>    | Write enable pulse width                        | 10  | _   | ns   |

| T <sub>wh</sub> <sup>(89)</sup>    | Write enable hold time                          | 7   |     | ns   |

| T <sub>rp</sub> <sup>(89)</sup>    | Read enable pulse width                         | 10  |     | ns   |

| T <sub>reh</sub> <sup>(89)</sup>   | Read enable hold time                           | 7   |     | ns   |

| T <sub>clesu</sub> <sup>(89)</sup> | Command latch enable to write enable setup time | 10  |     | ns   |

| T <sub>cleh</sub> <sup>(89)</sup>  | Command latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>cesu</sub> <sup>(89)</sup>  | Chip enable to write enable setup time          | 15  |     | ns   |

| T <sub>ceh</sub> <sup>(89)</sup>   | Chip enable to write enable hold time           | 5   |     | ns   |

| T <sub>alesu</sub> <sup>(89)</sup> | Address latch enable to write enable setup time | 10  |     | ns   |

| T <sub>aleh</sub> <sup>(89)</sup>  | Address latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>dsu</sub> <sup>(89)</sup>   | Data to write enable setup time                 | 10  |     | ns   |

<sup>(89)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

| Symbol                          | Description                        | Min | Мах | Unit |

|---------------------------------|------------------------------------|-----|-----|------|

| T <sub>dh</sub> <sup>(89)</sup> | Data to write enable hold time     | 5   | —   | ns   |

| T <sub>cea</sub>                | Chip enable to data access time    |     | 25  | ns   |

| T <sub>rea</sub>                | Read enable to data access time    |     | 16  | ns   |

| T <sub>rhz</sub>                | Read enable to data high impedance |     | 100 | ns   |

| T <sub>rr</sub>                 | Ready to read enable low           | 20  |     | ns   |

# Figure 1-17: NAND Command Latch Timing Diagram

# Initialization

#### Table 1-71: Initialization Clock Source Option and the Maximum Frequency for Arria V Devices

| Initialization Clock Source | Configuration Scheme | Maximum Frequency (MHz) | Minimum Number of Clock Cycles |

|-----------------------------|----------------------|-------------------------|--------------------------------|

| Internal Oscillator         | AS, PS, and FPP      | 12.5                    |                                |

| CLKUSR <sup>(107)</sup>     | PS and FPP           | 125                     | Т                              |

| CLAUSR                      | AS                   | 100                     | 1 init                         |

| DCLK                        | PS and FPP           | 125                     |                                |

# **Configuration Files**

#### Table 1-72: Uncompressed .rbf Sizes for Arria V Devices

Use this table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Quartus Prime software. However, for a specific version of the Quartus Prime software, any design targeted for the same device has the same uncompressed configuration file size.

The IOCSR raw binary file (.rbf) size is specifically for the Configuration via Protocol (CvP) feature.

Arria V GX, GT, SX, and ST Device Datasheet

<sup>&</sup>lt;sup>(107)</sup> To enable CLKUSR as the initialization clock source, turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Quartus Prime software from the **General** panel of the **Device and Pin Options** dialog box.

| Symbol           | Description                    | Minimum | Maximum | Unit |

|------------------|--------------------------------|---------|---------|------|

| V <sub>I</sub>   | DC input voltage               | -0.5    | 3.8     | V    |

| T <sub>J</sub>   | Operating junction temperature | -55     | 125     | °C   |

| T <sub>STG</sub> | Storage temperature (No bias)  | -65     | 150     | °C   |

| I <sub>OUT</sub> | DC output current per pin      | -25     | 40      | mA   |

## Table 2-3: Transceiver Power Supply Absolute Conditions for Arria V GZ Devices

| Symbol                | Description                                         | Minimum | Maximum | Unit |

|-----------------------|-----------------------------------------------------|---------|---------|------|

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (left side)    | -0.5    | 3.75    | V    |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (right side)   | -0.5    | 3.75    | V    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left side)        | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS power supply (left side)            | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS power supply (right side)           | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBL</sub> | Receiver analog power supply (left side)            | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBR</sub> | Receiver analog power supply (right side)           | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left side)         | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBR</sub> | Transmitter analog power supply (right side)        | -0.5    | 1.35    | V    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power supply (left side)  | -0.5    | 1.8     | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power supply (right side) | -0.5    | 1.8     | V    |

# Maximum Allowed Overshoot and Undershoot Voltage

During transitions, input signals may overshoot to the voltage shown in the following table. They may also undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

**Bus Hold Specifications**

#### Table 2-9: Bus Hold Parameters for Arria V GZ Devices

|                               |                   |                                                                                     | V <sub>CCIO</sub> |      |       |      |       |      |       |      |       |      |      |

|-------------------------------|-------------------|-------------------------------------------------------------------------------------|-------------------|------|-------|------|-------|------|-------|------|-------|------|------|

| Parameter                     | Symbol            | Conditions                                                                          | 1.2               | 2 V  | 1.5   | 5 V  | 1.8   | 8 V  | 2.5   | 5 V  | 3.(   | ) V  | Unit |

|                               |                   |                                                                                     | Min               | Max  | Min   | Max  | Min   | Max  | Min   | Max  | Min   | Max  |      |

| Low<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum)                                      | 22.5              |      | 25.0  | _    | 30.0  | _    | 50.0  |      | 70.0  |      | μΑ   |

| High<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum)                                      | -22.5             |      | -25.0 |      | -30.0 | _    | -50.0 |      | -70.0 | _    | μΑ   |

| Low<br>overdrive<br>current   | I <sub>ODL</sub>  | $\begin{array}{c} 0\mathrm{V} < \mathrm{V_{IN}} < \\ \mathrm{V_{CCIO}} \end{array}$ |                   | 120  | _     | 160  |       | 200  |       | 300  | _     | 500  | μΑ   |

| High<br>overdrive<br>current  | I <sub>ODH</sub>  | $0V < V_{IN} < V_{CCIO}$                                                            |                   | -120 |       | -160 |       | -200 |       | -300 | _     | -500 | μΑ   |

| Bus-hold<br>trip point        | V <sub>TRIP</sub> | _                                                                                   | 0.45              | 0.95 | 0.50  | 1.00 | 0.68  | 1.07 | 0.70  | 1.70 | 0.80  | 2.00 | V    |

#### **On-Chip Termination (OCT) Specifications**

If you enable OCT calibration, calibration is automatically performed at power-up for I/Os connected to the calibration block.

#### Table 2-10: OCT Calibration Accuracy Specifications for Arria V GZ Devices

OCT calibration accuracy is valid at the time of calibration only.

| Symbol | Description                                           | V <sub>CCIO</sub> (V) | Typical | Unit |  |

|--------|-------------------------------------------------------|-----------------------|---------|------|--|

|        |                                                       | 3.0                   | 0.0297  |      |  |

|        |                                                       | 2.5                   | 0.0344  |      |  |

| dR/dV  | OCT variation with voltage without re-calibration     | 1.8                   | 0.0499  | %/mV |  |

|        |                                                       | 1.5                   | 0.0744  |      |  |

|        |                                                       | 1.2                   | 0.1241  |      |  |

|        |                                                       | 3.0                   | 0.189   |      |  |

|        |                                                       | 2.5                   | 0.208   | -    |  |

| dR/dT  | OCT variation with temperature without re-calibration | 1.8                   | 0.266   | %/°C |  |

|        |                                                       | 1.5                   | 0.273   |      |  |

|        |                                                       | 1.2                   | 0.317   |      |  |

# Pin Capacitance

# Table 2-13: Pin Capacitance for Arria V GZ Devices

| Symbol             | Description                                                      | Maximum | Unit |

|--------------------|------------------------------------------------------------------|---------|------|

| C <sub>IOTB</sub>  | Input capacitance on the top and bottom I/O pins                 | 6       | pF   |

| C <sub>IOLR</sub>  | Input capacitance on the left and right I/O pins                 | 6       | pF   |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output and feedback pins | 6       | pF   |

| Symbol/Description                         | Conditions                                                | Transceiver Speed Grade 2 |                    |      | Transceiver Speed Grade 3     |      |      | Unit |

|--------------------------------------------|-----------------------------------------------------------|---------------------------|--------------------|------|-------------------------------|------|------|------|

| Symbol/Description                         | Conditions                                                | Min                       | Тур                | Max  | Min                           | Тур  | Мах  | Unit |

| Rise time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> | _                         | _                  | 400  | _                             | _    | 400  | 20   |

| Fall time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> |                           | _                  | 400  |                               |      | 400  | ps   |

| Duty cycle                                 | —                                                         | 45                        | _                  | 55   | 45                            |      | 55   | %    |

| Spread-spectrum modulating clock frequency | PCI Express <sup>®</sup> (PCIe)                           | 30                        | _                  | 33   | 30                            |      | 33   | kHz  |

| Spread-spectrum downspread                 | PCIe                                                      |                           | 0 to               | _    | _                             | 0 to | —    | %    |

|                                            |                                                           |                           | -0.5               |      |                               | -0.5 |      |      |

| On-chip termination resistors              | —                                                         |                           | 100                | _    |                               | 100  |      | Ω    |

| Absolute V <sub>MAX</sub>                  | Dedicated reference clock pin                             |                           | _                  | 1.6  |                               |      | 1.6  | V    |

|                                            | RX reference clock pin                                    |                           | _                  | 1.2  |                               |      | 1.2  |      |

| Absolute V <sub>MIN</sub>                  | —                                                         | -0.4                      | _                  | _    | -0.4                          |      |      | V    |

| Peak-to-peak differential input<br>voltage | -                                                         | 200                       | -                  | 1600 | 200                           |      | 1600 | mV   |

| V <sub>ICM</sub> (AC coupled)              | Dedicated reference clock pin                             | 10                        | 1000/900/850 (139) |      | 1000/900/850 (139)            |      |      | mV   |

| · • ·                                      | RX reference clock pin                                    | 1.                        | .0/0.9/0.85        | 140) | 1.0/0.9/0.85 <sup>(140)</sup> |      |      | mV   |

| V <sub>ICM</sub> (DC coupled)              | HCSL I/O standard for<br>PCIe reference clock             | 250                       | _                  | 550  | 250                           |      | 550  | mV   |

<sup>(138)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

(139) The reference clock common mode voltage is equal to the V<sub>CCR\_GXB</sub> power supply level.

(140) This supply follows VCCR\_GXB

| Symbol/Description                                 | Conditions              | Transceiver Speed Grade 2 |               |     | Transceiver Speed Grade 3 |               |     | - Unit |

|----------------------------------------------------|-------------------------|---------------------------|---------------|-----|---------------------------|---------------|-----|--------|

| Symbol/Description                                 | Conditions              | Min                       | Тур           | Max | Min                       | Тур           | Max | Onit   |

| fixedclk clock frequency                           | PCIe<br>Receiver Detect | -                         | 100 or<br>125 | _   | _                         | 100 or<br>125 | _   | MHz    |

| Reconfiguration clock (mgmt_clk_<br>clk) frequency | —                       | 100                       | _             | 125 | 100                       | _             | 125 | MHz    |

#### **Related Information**

#### Arria V Device Overview

For more information about device ordering codes.

#### Receiver

#### Table 2-24: Receiver Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                           | Transceiver Speed Grad                               |      | d Grade 2 | Grade 2 Transceiver Speed Grade |      | ed Grade 3 | — Unit  |      |

|--------------------------------------------------------------|------------------------------------------------------|------|-----------|---------------------------------|------|------------|---------|------|

| Symbol/Description                                           | Conditions                                           | Min  | Тур       | Мах                             | Min  | Тур        | Мах     |      |

| Supported I/O Standards                                      | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |      |           |                                 |      |            |         |      |

| Data rate (Standard PCS) <sup>(143)</sup> , <sup>(144)</sup> | —                                                    | 600  | _         | 9900                            | 600  | _          | 8800    | Mbps |

| Data rate (10G PCS) (143), (144)                             | _                                                    | 600  |           | 12500                           | 600  | _          | 10312.5 | Mbps |

| Absolute $V_{MAX}$ for a receiver pin $^{(145)}$             | —                                                    | _    |           | 1.2                             | _    | _          | 1.2     | V    |

| Absolute $\mathrm{V}_{\mathrm{MIN}}$ for a receiver pin      | _                                                    | -0.4 |           |                                 | -0.4 | _          |         | V    |

<sup>&</sup>lt;sup>(143)</sup> The line data rate may be limited by PCS-FPGA interface speed grade.

<sup>(144)</sup> To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>&</sup>lt;sup>(145)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

# **Core Performance Specifications**

# **Clock Tree Specifications**

## Table 2-33: Clock Tree Performance for Arria V GZ Devices

| Symbol                    | Perfor  | Unit   |      |

|---------------------------|---------|--------|------|

| Synbol                    | C3, I3L | C4, I4 | Onit |

| Global and Regional Clock | 650     | 580    | MHz  |

| Periphery Clock           | 500     | 500    | MHz  |

# **PLL Specifications**

# Table 2-34: PLL Specifications for Arria V GZ Devices

| Symbol                            | Parameter                                               | Min | Тур | Max  | Unit |

|-----------------------------------|---------------------------------------------------------|-----|-----|------|------|

| f <sub>IN</sub> <sup>(167)</sup>  | Input clock frequency (C3, I3L speed grade)             | 5   | _   | 800  | MHz  |

| IIN                               | Input clock frequency (C4, I4 speed grade)              | 5   | _   | 650  | MHz  |

| f <sub>INPFD</sub>                | Input frequency to the PFD                              | 5   |     | 325  | MHz  |

| f <sub>FINPFD</sub>               | Fractional Input clock frequency to the PFD             | 50  | _   | 160  | MHz  |

| f <sub>VCO</sub> <sup>(168)</sup> | PLL VCO operating range (C3, I3L speed grade)           | 600 |     | 1600 | MHz  |

| IVCO                              | PLL VCO operating range (C4, I4 speed grade)            | 600 | _   | 1300 | MHz  |

| t <sub>EINDUTY</sub>              | Input clock or external feedback clock input duty cycle | 40  |     | 60   | %    |

<sup>(167)</sup> This specification is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

<sup>(168)</sup> The VCO frequency reported by the Quartus II software in the **PLL Usage Summary** section of the compilation report takes into consideration the VCO post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the f<sub>VCO</sub> specification.

Arria V GZ Device Datasheet

| Symbol                                                                         | Parameter                                                                                                     | Min | Тур | Max  | Unit      |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----|------|-----------|

| t <sub>OUTPJ_IO</sub> <sup>, (173)</sup> , <sup>(175)</sup>                    | Period Jitter for a clock output on a regular I/O in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )            | _   | _   | 600  | ps (p-p)  |

|                                                                                | Period Jitter for a clock output on a regular I/O in integer PLL ( $f_{OUT} < 100 \text{ MHz}$ )              |     |     | 60   | mUI (p-p) |

| t <sub>FOUTPJ_IO</sub> <sup>(173)</sup> , <sup>(175)</sup> , <sup>(176)</sup>  | Period Jitter for a clock output on a regular I/O in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )         |     | _   | 600  | ps (p-p)  |

|                                                                                | Period Jitter for a clock output on a regular I/O in fractional PLL (f <sub>OUT</sub> < 100 MHz)              |     | _   | 60   | mUI (p-p) |

| (173) (175)                                                                    | Cycle-to-cycle Jitter for a clock output on a regular I/O in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )    |     |     | 600  | ps (p-p)  |

| t <sub>OUTCCJ_IO</sub> <sup>(173)</sup> , <sup>(175)</sup>                     | Cycle-to-cycle Jitter for a clock output on a regular<br>I/O in integer PLL (f <sub>OUT</sub> < 100 MHz)      |     |     | 60   | mUI (p-p) |

| t <sub>FOUTCCJ_IO</sub> <sup>(173)</sup> , <sup>(175)</sup> , <sup>(176)</sup> | Cycle-to-cycle Jitter for a clock output on a regular I/O in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ ) | _   | _   | 600  | ps (p-p)  |

| <sup>L</sup> FOUTCCJ_IO                                                        | Cycle-to-cycle Jitter for a clock output on a regular<br>I/O in fractional PLL (f <sub>OUT</sub> < 100 MHz)   |     |     | 60   | mUI (p-p) |

| <b>t</b>                                                                       | Period Jitter for a dedicated clock output in cascaded PLLs ( $f_{OUT} \ge 100 \text{ MHz}$ )                 | _   | _   | 175  | ps (p-p)  |

| t <sub>CASC_OUTPJ_DC</sub> <sup>(173)</sup> , <sup>(177)</sup>                 | Period Jitter for a dedicated clock output in cascaded PLLS (f <sub>OUT</sub> < 100 MHz)                      |     | _   | 17.5 | mUI (p-p) |

| dK <sub>BIT</sub>                                                              | Bit number of Delta Sigma Modulator (DSM)                                                                     | 8   | 24  | 32   | Bits      |

<sup>(175)</sup> The external memory interface clock output jitter specifications use a different measurement method, which is available in the "Memory Output Clock Jitter Specification for Arria V GZ Devices" table.

<sup>(176)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.05–0.95 must be  $\geq$  1000 MHz.

<sup>(177)</sup> The cascaded PLL specification is only applicable with the following condition:

a. Upstream PLL: 0.59Mhz ≤ Upstream PLL BW < 1 MHz

b. Downstream PLL: Downstream PLL BW > 2 MHz

#### **DLL Range Specifications**

#### Table 2-47: DLL Range Specifications for Arria V GZ Devices

Arria V GZ devices support memory interface frequencies lower than 300 MHz, although the reference clock that feeds the DLL must be at least 300 MHz. To support interfaces below 300 MHz, multiply the reference clock feeding the DLL to ensure the frequency is within the supported range of the DLL.

| Parameter                     | C3, I3L   | C4, I4    | Unit |

|-------------------------------|-----------|-----------|------|

| DLL operating frequency range | 300 - 890 | 300 - 890 | MHz  |

#### **DQS Logic Block Specifications**

#### Table 2-48: DQS Phase Offset Delay Per Setting for Arria V GZ Devices

The typical value equals the average of the minimum and maximum values.

The delay settings are linear with a cumulative delay variation of 40 ps for all speed grades. For example, when using a -3 speed grade and applying a 10-phase offset setting to a 90° phase shift at 400 MHz, the expected average cumulative delay is  $[625 \text{ ps} + (10 \times 11 \text{ ps}) \pm 20 \text{ ps}] = 735 \text{ ps} \pm 20 \text{ ps}$ .

| Speed Grade | Min | Мах | Unit |

|-------------|-----|-----|------|

| C3, I3L     | 8   | 15  | ps   |

| C4, I4      | 8   | 16  | ps   |

## Table 2-49: DQS Phase Shift Error Specification for DLL-Delayed Clock (t<sub>DQS\_PSERR</sub>) for Arria V GZ Devices

This error specification is the absolute maximum and minimum error. For example, skew on three DQS delay buffers in a -3 speed grade is  $\pm 84$  ps or  $\pm 42$  ps.

| Number of DQS Delay Buffers | C3, I3L | C4, I4 | Unit |

|-----------------------------|---------|--------|------|

| 1                           | 30      | 32     | ps   |

| 2                           | 60      | 64     | ps   |

| 3                           | 90      | 96     | ps   |

Note: When you enable the decompression or design security feature, the DCLK-to-DATA[] ratio varies for FPP ×8, FPP ×16, and FPP ×32. For the respective DCLK-to-DATA[] ratio, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

#### Table 2-56: FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is 1

Use these timing parameters when the decompression and design security features are disabled.

| Symbol                      | Parameter                                    | Minimum                | Maximum     | Unit |

|-----------------------------|----------------------------------------------|------------------------|-------------|------|

| t <sub>CF2CD</sub>          | nCONFIG low to CONF_DONE low                 | _                      | 600         | ns   |

| t <sub>CF2ST0</sub>         | nconfig low to nstatus low                   | _                      | 600         | ns   |

| t <sub>CFG</sub>            | nCONFIG low pulse width                      | 2                      | _           | μs   |

| t <sub>STATUS</sub>         | nSTATUS low pulse width                      | 268                    | 1,506 (205) | μs   |

| t <sub>CF2ST1</sub>         | nCONFIG high to nSTATUS high                 | _                      | 1,506 (206) | μs   |

| t <sub>CF2CK</sub><br>(207) | nCONFIG high to first rising edge on DCLK    | 1,506                  | _           | μs   |

| t <sub>ST2CK</sub> (20      | hstatus high to first rising edge of DCLK    | 2                      | _           | μs   |

| t <sub>DSU</sub>            | DATA[] setup time before rising edge on DCLK | 5.5                    | —           | ns   |

| t <sub>DH</sub>             | DATA[] hold time after rising edge on DCLK   | 0                      | _           | ns   |

| t <sub>CH</sub>             | DCLK high time                               | $0.45 	imes 1/f_{MAX}$ | —           | s    |

| t <sub>CL</sub>             | DCLK low time                                | $0.45 	imes 1/f_{MAX}$ | _           | s    |

| t <sub>CLK</sub>            | DCLK period                                  | 1/f <sub>MAX</sub>     | —           | S    |

| f                           | DCLK frequency (FPP ×8/×16)                  | _                      | 125         | MHz  |

| f <sub>MAX</sub>            | DCLK frequency (FPP ×32)                     | —                      | 100         | MHz  |

| t <sub>CD2UM</sub>          | CONF_DONE high to user mode (208)            | 175                    | 437         | μs   |

<sup>&</sup>lt;sup>(205)</sup> This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>&</sup>lt;sup>(206)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>&</sup>lt;sup>(207)</sup> If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

#### 2-64 FPP Configuration Timing when DCLK to DATA[] > 1

| Symbol              | Parameter                                         | Minimum                                    | Maximum | Unit |

|---------------------|---------------------------------------------------|--------------------------------------------|---------|------|

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period      | _       | —    |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | $t_{CD2CU}$ + (8576 × CLKUSR period) (215) | _       | —    |

#### **Related Information**

- DCLK-to-DATA[] Ratio (r) for FPP Configuration on page 2-57

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

<sup>&</sup>lt;sup>(215)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

#### Table 2-60: PS Timing Parameters for Arria V GZ Devices

| Symbol                      | Parameter                                         | Minimum                                               | Maximum     | Unit |  |

|-----------------------------|---------------------------------------------------|-------------------------------------------------------|-------------|------|--|

| t <sub>CF2CD</sub>          | nCONFIG low to CONF_DONE low                      | —                                                     | 600         | ns   |  |

| t <sub>CF2ST0</sub>         | nCONFIG low to nSTATUS low                        | _                                                     | 600         | ns   |  |

| t <sub>CFG</sub>            | nCONFIG low pulse width                           | 2                                                     |             | μs   |  |

| t <sub>STATUS</sub>         | nSTATUS low pulse width                           | 268                                                   | 1,506 (217) | μs   |  |

| t <sub>CF2ST1</sub>         | nCONFIG high to nSTATUS high                      | _                                                     | 1,506 (218) | μs   |  |

| t <sub>CF2CK</sub><br>(219) | nCONFIG high to first rising edge on DCLK         | 1,506                                                 | _           | μs   |  |

| t <sub>ST2CK</sub> (219)    | nSTATUS high to first rising edge of DCLK         | 2                                                     |             | μs   |  |

| t <sub>DSU</sub>            | DATA[] setup time before rising edge on DCLK      | 5.5                                                   |             | ns   |  |

| t <sub>DH</sub>             | DATA[] hold time after rising edge on DCLK        | 0                                                     | _           | ns   |  |

| t <sub>CH</sub>             | DCLK high time                                    | $0.45 	imes 1/f_{MAX}$                                |             | s    |  |

| t <sub>CL</sub>             | DCLK low time                                     | $0.45 	imes 1/f_{MAX}$                                | —           | S    |  |

| t <sub>CLK</sub>            | DCLK period                                       | 1/f <sub>MAX</sub>                                    |             | s    |  |

| f <sub>MAX</sub>            | DCLK frequency                                    | _                                                     | 125         | MHz  |  |

| t <sub>CD2UM</sub>          | CONF_DONE high to user mode <sup>(220)</sup>      | 175                                                   | 437         | μs   |  |

| t <sub>CD2CU</sub>          | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period                 |             |      |  |

| t <sub>CD2UMC</sub>         | CONF_DONE high to user mode with CLKUSR option on | $t_{CD2CU}$ + (8576 × CLKUSR period) <sup>(221)</sup> | _           |      |  |

<sup>&</sup>lt;sup>(217)</sup> This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>&</sup>lt;sup>(218)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>&</sup>lt;sup>(219)</sup> If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

<sup>&</sup>lt;sup>(220)</sup> The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2016     | 2016.06.20 | <ul> <li>Changed column heading from "Value" to "Maximum" in the "Pin Capacitance for Arria V GZ Devices" table.</li> <li>Changed the minimum supported data rate range values from "1000" to "2000" in the "ATX PLL Specifications for Arria V GZ Devices" table.</li> <li>Added the supported data rates for the following output standards using true LVDS output buffer types in the "High-Speed Clock Specifications for Arria V GZ Devices" table:</li> <li>True RSDS output standard: data rates of up to 230 Mbps</li> <li>True mini-LVDS output standard: data rates of up to 340 Mbps</li> </ul> |

| December 2015 | 2015.12.16 | <ul> <li>Removed the CDR ppm tolerance specification from the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Removed transmitter rise and fall time specifications from the "Transmitter Specifications for Arria V GZ Devices" table.</li> <li>Changed the .rbf sizes in the "Uncompressed .rbf Sizes for Arria V GZ Devices" table.</li> <li>Added a footnote to the "Transmitter High-Speed I/O Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                              |

| June 2015     | 2015.06.16 | <ul> <li>Changed the conditions for the reference clock rise and fall time and added a note to the condition in the<br/>"Reference Clock Specifications for Arria V GZ Devices" table.</li> <li>Added a note to the "Minimum differential eye opening at receiver serial input pins" specification in the<br/>"Receiver Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                           |

| January 2015  | 2015.01.30 | <ul> <li>Added 240-Ω to the "OCT Calibration Accuracy Specifications for Arria V GZ Devices" table.</li> <li>Changed the CDR PPM tolerance spec in the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Added additional max data rate for fPLL in the "Fractional PLL Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                                                            |