# E·XFL

## Intel - 5AGXMA3D4F27I5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detuns                         |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 7362                                                       |

| Number of Logic Elements/Cells | 156000                                                     |

| Total RAM Bits                 | 11746304                                                   |

| Number of I/O                  | 336                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 672-BBGA, FCBGA                                            |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxma3d4f27i5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| I/O Standard        | V <sub>IL</sub> | <sub>.(DC)</sub> (V)    | V <sub>IH(D</sub>       | <sub>C)</sub> (V)        | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)    | V <sub>OH</sub> (V)     | I <sub>OL</sub> <sup>(14)</sup> | I <sub>OH</sub> <sup>(14)</sup> (mA) |

|---------------------|-----------------|-------------------------|-------------------------|--------------------------|-------------------------|-------------------------|------------------------|-------------------------|---------------------------------|--------------------------------------|

|                     | Min             | Max Min                 |                         | Max                      | Max                     | Min                     | Max                    | Min                     | (mA)                            | OH (יעייי)                           |

| HSTL-15<br>Class II | —               | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$         | —                        | V <sub>REF</sub> – 0.2  | $V_{REF} + 0.2$         | 0.4                    | V <sub>CCIO</sub> – 0.4 | 16                              | -16                                  |

| HSTL-12<br>Class I  | -0.15           | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$  | 8                               | -8                                   |

| HSTL-12<br>Class II | -0.15           | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$  | 16                              | -16                                  |

| HSUL-12             | —               | V <sub>REF</sub> - 0.13 | V <sub>REF</sub> + 0.13 | _                        | V <sub>REF</sub> – 0.22 | $V_{REF} + 0.22$        | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$   |                                 | _                                    |

## **Differential SSTL I/O Standards**

Table 1-17: Differential SSTL I/O Standards for Arria V Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>SW</sub> | <sub>ING(DC)</sub> (V) |                                 | $V_{X(AC)}(V)$       |                                 | V <sub>SWING(AC)</sub> (V)                    |                           |  |

|------------------------|-------|-----------------------|-------|-----------------|------------------------|---------------------------------|----------------------|---------------------------------|-----------------------------------------------|---------------------------|--|

|                        | Min   | Тур                   | Max   | Min             | Мах                    | Min                             | Тур                  | Мах                             | Min                                           | Max                       |  |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                   | 2.625 | 0.3             | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 – 0.2      | _                    | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$          |  |

| SSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.25            | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 –<br>0.175 | _                    | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | $V_{CCIO} + 0.6$          |  |

| SSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.2             | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | —                    | V <sub>CCIO</sub> /2<br>+ 0.15  | $2(V_{IH(AC)} - V_{REF})$                     | $2(V_{IL(AC)} - V_{REF})$ |  |

| SSTL-135               | 1.283 | 1.35                  | 1.45  | 0.18            | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |  |

<sup>&</sup>lt;sup>(14)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

$<sup>^{(15)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

|                  | Symbol                                                    | Condition                                               |      | -I3, -C4 |       |      | –I5, –C5 |       |      | Unit |       |      |  |

|------------------|-----------------------------------------------------------|---------------------------------------------------------|------|----------|-------|------|----------|-------|------|------|-------|------|--|

|                  | Symbol                                                    | Condition                                               | Min  | Тур      | Max   | Min  | Тур      | Мах   | Min  | Тур  | Max   | Onic |  |

|                  | TCCS                                                      | True Differential I/O<br>Standards                      | _    | _        | 150   | _    | _        | 150   | _    | _    | 150   | ps   |  |

|                  | 1003                                                      | Emulated Differential<br>I/O Standards                  | _    | _        | 300   | _    | _        | 300   |      | _    | 300   | ps   |  |

|                  | True Differential I/O<br>Standards - f <sub>HSDRDPA</sub> | SERDES factor J =3 to $10^{(76)}$                       | 150  |          | 1250  | 150  | _        | 1250  | 150  |      | 1050  | Mbps |  |

|                  | (data rate)                                               | SERDES factor $J \ge 8$<br>with DPA <sup>(76)(78)</sup> | 150  | _        | 1600  | 150  | _        | 1500  | 150  | _    | 1250  | Mbps |  |

| Receiver         |                                                           | SERDES factor J = 3<br>to 10                            | (77) | _        | (83)  | (77) | _        | (83)  | (77) | _    | (83)  | Mbps |  |

|                  | f <sub>HSDR</sub> (data rate)                             | SERDES factor J = 1<br>to 2, uses DDR<br>registers      | (77) |          | (79)  | (77) |          | (79)  | (77) |      | (79)  | Mbps |  |

| DPA Mode         | DPA run length                                            | _                                                       | _    | _        | 10000 | _    | _        | 10000 | _    | _    | 10000 | UI   |  |

| Soft-CDR<br>Mode | Soft-CDR ppm tolerance                                    | _                                                       | _    | _        | 300   | _    | _        | 300   | _    | _    | 300   | ±ppm |  |

| Non-DPA<br>Mode  | Sampling Window                                           | _                                                       |      | _        | 300   | _    | _        | 300   |      | _    | 300   | ps   |  |

Arria V GX, GT, SX, and ST Device Datasheet

<sup>&</sup>lt;sup>(83)</sup> You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

After the Boot ROM code exits and control is passed to the preloader, software can adjust the value of drvsel and smplsel via the system manager. drvsel can be set from 1 to 7 and smplsel can be set from 0 to 7. While the preloader is executing, the values for SDMMC\_CLK and SDMMC\_CLK\_OUT increase to a maximum of 200 MHz and 50 MHz respectively.

The SD/MMC interface calibration support will be available in a future release of the preloader through the SoC EDS software update.

| Symbol                                              | Description                                         | Min                                                         | Мах                                                                                                  | Unit |

|-----------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|

|                                                     | SDMMC_CLK clock period (Identification mode)        | 20                                                          | _                                                                                                    | ns   |

| T <sub>sdmmc_clk</sub> (internal reference clock)   | SDMMC_CLK clock period<br>(Default speed mode)      | 5                                                           | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK clock period<br>(High speed mode)         | 5                                                           | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK_OUT clock<br>period (Identification mode) | 2500                                                        | _                                                                                                    | ns   |

| T <sub>sdmmc_clk_out</sub> (interface output clock) | SDMMC_CLK_OUT clock period (Default speed mode)     | 40                                                          | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK_OUT clock<br>period (High speed mode)     | 20                                                          | _                                                                                                    | ns   |

| T <sub>dutycycle</sub>                              | SDMMC_CLK_OUT duty cycle                            | 45                                                          | 55                                                                                                   | %    |

| T <sub>d</sub>                                      | SDMMC_CMD/SDMMC_D<br>output delay                   | $\frac{(T_{sdmmc\_clk} \times drvsel)/2}{-1.23^{(87)}}$     | $\begin{array}{c} (\mathrm{T}_{sdmmc\_clk} \times \texttt{drvsel})/2 \\ + 1.69^{\ (87)} \end{array}$ | ns   |

| T <sub>su</sub>                                     | Input setup time                                    | $1.05 - (T_{sdmmc_clk} \times smplsel)/2^{(88)}$            |                                                                                                      | ns   |

| T <sub>h</sub>                                      | Input hold time                                     | $\frac{(T_{sdmmc\_clk} \times \texttt{smplsel})}{2^{(88)}}$ | —                                                                                                    | ns   |

<sup>&</sup>lt;sup>(87)</sup> drvsel is the drive clock phase shift select value.

<sup>&</sup>lt;sup>(88)</sup> smplsel is the sample clock phase shift select value.

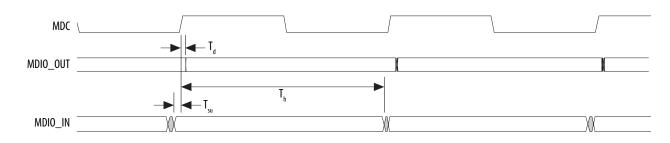

# Figure 1-15: MDIO Timing Diagram

# I<sup>2</sup>C Timing Characteristics

# Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Symbol                | Description                                       | Standar | d Mode | Fast | Mode | Unit |

|-----------------------|---------------------------------------------------|---------|--------|------|------|------|

| Symbol                | Description                                       | Min     | Max    | Min  | Max  | Onit |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10      | —      | 2.5  | _    | μs   |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7     | —      | 0.6  |      | μs   |

| T <sub>clklow</sub>   | SCL low time                                      | 4       | _      | 1.3  |      | μs   |

| T <sub>s</sub>        | Setup time for serial data line (SDA) data to SCL | 0.25    | —      | 0.1  | —    | μs   |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0       | 3.45   | 0    | 0.9  | μs   |

| T <sub>d</sub>        | SCL to SDA output data delay                      | —       | 0.2    | _    | 0.2  | μs   |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7     | _      | 0.6  | _    | μs   |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4       | —      | 0.6  | _    | μs   |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4       | —      | 0.6  | —    | μs   |

| Variant    | Member Code | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) |

|------------|-------------|--------------------------------|------------------------|

|            | A1          | 71,015,712                     | 439,960                |

|            | A3          | 71,015,712                     | 439,960                |

|            | A5          | 101,740,800                    | 446,360                |

| Arria V GX | A7          | 101,740,800                    | 446,360                |

| Allia V GA | B1          | 137,785,088                    | 457,368                |

|            | B3          | 137,785,088                    | 457,368                |

|            | B5          | 185,915,808                    | 463,128                |

|            | B7          | 185,915,808                    | 463,128                |

|            | C3          | 71,015,712                     | 439,960                |

| Arria V GT | C7          | 101,740,800                    | 446,360                |

| Allia v GI | D3          | 137,785,088                    | 457,368                |

|            | D7          | 185,915,808                    | 463,128                |

| Arria V SX | B3          | 185,903,680                    | 450,968                |

| Allia v SA | B5          | 185,903,680                    | 450,968                |

| Arria V ST | D3          | 185,903,680                    | 450,968                |

|            | D5          | 185,903,680                    | 450,968                |

# **Minimum Configuration Time Estimation**

#### Table 1-73: Minimum Configuration Time Estimation for Arria V Devices

The estimated values are based on the configuration .rbf sizes in Uncompressed .rbf Sizes for Arria V Devices table.

- PowerPlay Early Power Estimator User Guide For more information about the EPE tool.

- **PowerPlay Power Analysis** ٠ For more information about PowerPlay power analysis.

#### **Power Consumption**

Altera offers two ways to estimate power consumption for a design-the Excel-based Early Power Estimator and the Quartus II PowerPlay Power Analyzer feature.

Note: You typically use the interactive Excel-based Early Power Estimator before designing the FPGA to get a magnitude estimate of the device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-and-route. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide For more information about the EPE tool.

- PowerPlay Power Analysis For more information about PowerPlay power analysis.

#### I/O Pin Leakage Current

#### Table 2-8: I/O Pin Leakage Current for Arria V GZ Devices

If  $V_O = V_{CCIO}$  to  $V_{CCIOMax}$ , 100 µA of leakage current per I/O is expected.

| Symbol          | Description           | Conditions                     | Min | Тур | Max | Unit |

|-----------------|-----------------------|--------------------------------|-----|-----|-----|------|

| II              | Input pin             | $V_{I} = 0 V$ to $V_{CCIOMAX}$ | -30 |     | 30  | μΑ   |

| I <sub>OZ</sub> | Tri-stated I/O<br>pin | $V_{O} = 0 V$ to $V_{CCIOMAX}$ | -30 | —   | 30  | μΑ   |

#### Table 2-19: Differential SSTL I/O Standards for Arria V GZ Devices

| I/O Standard            | V <sub>CCIO</sub> (V) |      |       | V <sub>SWIN</sub> | V <sub>SWING(DC)</sub> (V) |                                 | V <sub>X(AC)</sub> (V) |                                 |                                               | V <sub>SWING(AC)</sub> (V) |

|-------------------------|-----------------------|------|-------|-------------------|----------------------------|---------------------------------|------------------------|---------------------------------|-----------------------------------------------|----------------------------|

|                         | Min                   | Тур  | Max   | Min               | Max                        | Min                             | Тур                    | Max                             | Min                                           | Мах                        |

| SSTL-2 Class I,<br>II   | 2.375                 | 2.5  | 2.625 | 0.3               | V <sub>CCIO</sub><br>+ 0.6 | V <sub>CCIO</sub> /2<br>- 0.2   | _                      | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$           |

| SSTL-18 Class I,<br>II  | 1.71                  | 1.8  | 1.89  | 0.25              | V <sub>CCIO</sub><br>+ 0.6 | V <sub>CCIO</sub> /2<br>- 0.175 |                        | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | V <sub>CCIO</sub> + 0.6    |

| SSTL-15 Class I,<br>II  | 1.425                 | 1.5  | 1.575 | 0.2               | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  |                        | V <sub>CCIO</sub> /2<br>+ 0.15  | 0.35                                          | _                          |

| SSTL-135<br>Class I, II | 1.283                 | 1.35 | 1.45  | 0.2               | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  | V <sub>CCIO</sub> /2   | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub><br>- V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$  |

| SSTL-125<br>Class I, II | 1.19                  | 1.25 | 1.31  | 0.18              | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  | V <sub>CCIO</sub> /2   | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub><br>- V <sub>REF</sub> ) | _                          |

| SSTL-12<br>Class I, II  | 1.14                  | 1.2  | 1.26  | 0.18              | —                          | V <sub>REF</sub><br>-0.15       | V <sub>CCIO</sub> /2   | V <sub>REF</sub><br>+ 0.15      | -0.30                                         | 0.30                       |

# Table 2-20: Differential HSTL and HSUL I/O Standards for Arria V GZ Devices

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>DIF(DC)</sub> (V) |     |     | V <sub>X(AC)</sub> (V) |     |      | V <sub>CM(DC)</sub> (V) |     |      | V <sub>DIF(AC)</sub> (V) |     |

|------------------------|-----------------------|-----|--------------------------|-----|-----|------------------------|-----|------|-------------------------|-----|------|--------------------------|-----|

|                        | Min                   | Тур | Max                      | Min | Max | Min                    | Тур | Max  | Min                     | Тур | Max  | Min                      | Max |

| HSTL-18 Class<br>I, II | 1.71                  | 1.8 | 1.89                     | 0.2 |     | 0.78                   |     | 1.12 | 0.78                    | _   | 1.12 | 0.4                      | _   |

| HSTL-15 Class<br>I, II | 1.425                 | 1.5 | 1.575                    | 0.2 |     | 0.68                   |     | 0.9  | 0.68                    | _   | 0.9  | 0.4                      | _   |

$<sup>^{(127)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

# **Switching Characteristics**

# **Transceiver Performance Specifications**

# **Reference Clock**

#### Table 2-22: Reference Clock Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                                                                                 | Conditions             | Transc                                                                      | eiver Speed | Grade 2 | Transce | Unit |     |      |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------|-------------|---------|---------|------|-----|------|--|--|--|--|

| Symbol/Description                                                                                                 | Conditions             | Min                                                                         | Тур         | Max     | Min     | Тур  | Max | Onit |  |  |  |  |

| Reference Clock                                                                                                    |                        |                                                                             |             |         |         |      |     |      |  |  |  |  |

| Supported I/O StandardsDedicated reference clock1.2-V PCML, 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, Differential LVPEC |                        |                                                                             |             |         |         |      |     |      |  |  |  |  |

|                                                                                                                    | RX reference clock pin | RX reference clock pin 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |             |         |         |      |     |      |  |  |  |  |

| Input Reference Clock<br>Frequency<br>(CMU PLL) <sup>(137)</sup>                                                   | _                      | 40                                                                          | _           | 710     | 40      | _    | 710 | MHz  |  |  |  |  |

| Input Reference Clock<br>Frequency<br>(ATX PLL) <sup>(137)</sup>                                                   | _                      | 100                                                                         | _           | 710     | 100     | _    | 710 | MHz  |  |  |  |  |

<sup>(137)</sup> The input reference clock frequency options depend on the data rate and the device speed grade.

| Symbol/Description                                 | Conditions              | Trans | ceiver Spee   | d Grade 2 | Transc | Unit          |     |      |

|----------------------------------------------------|-------------------------|-------|---------------|-----------|--------|---------------|-----|------|

| Symbol/Description                                 | Conditions              | Min   | Тур           | Max       | Min    | Тур           | Max | Onit |

| fixedclk clock frequency                           | PCIe<br>Receiver Detect | -     | 100 or<br>125 | _         | _      | 100 or<br>125 | _   | MHz  |

| Reconfiguration clock (mgmt_clk_<br>clk) frequency | —                       | 100   | _             | 125       | 100    | _             | 125 | MHz  |

#### Arria V Device Overview

For more information about device ordering codes.

#### Receiver

#### Table 2-24: Receiver Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                           | Conditions                  | Trans   | ceiver Spee | d Grade 2 | Transc | Unit |         |      |

|--------------------------------------------------------------|-----------------------------|---------|-------------|-----------|--------|------|---------|------|

| Symbol/Description                                           | Conditions                  | Min     | Тур         | Мах       | Min    | Тур  | Мах     |      |

| Supported I/O Standards                                      | 1.4-V PCML, 1.5-V PCML, 2.5 | -V PCML | LVPECL, a   | and LVDS  |        |      |         |      |

| Data rate (Standard PCS) <sup>(143)</sup> , <sup>(144)</sup> | —                           | 600     | _           | 9900      | 600    | _    | 8800    | Mbps |

| Data rate (10G PCS) (143), (144)                             | _                           | 600     |             | 12500     | 600    | _    | 10312.5 | Mbps |

| Absolute $V_{MAX}$ for a receiver pin $^{(145)}$             | —                           | _       |             | 1.2       | _      | _    | 1.2     | V    |

| Absolute $\mathrm{V}_{\mathrm{MIN}}$ for a receiver pin      | _                           | -0.4    |             |           | -0.4   | _    |         | V    |

<sup>&</sup>lt;sup>(143)</sup> The line data rate may be limited by PCS-FPGA interface speed grade.

<sup>(144)</sup> To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>&</sup>lt;sup>(145)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

| Symbol/Description                           | Conditions                                              | Trans | ceiver Spee | d Grade 2 | Transc | eiver Spee | ed Grade 3 | Unit |  |

|----------------------------------------------|---------------------------------------------------------|-------|-------------|-----------|--------|------------|------------|------|--|

| Symbol/Description                           | Conditions                                              | Min   | Тур         | Мах       | Min    | Тур        | Мах        |      |  |

|                                              | $V_{CCR\_GXB} = 0.85 V$<br>full bandwidth               | _     | 600         | _         | _      | 600        | _          | mV   |  |

| V <sub>ICM</sub> (AC and DC coupled)         | $V_{CCR_{GXB}} = 0.85 V$<br>half bandwidth              | _     | 600         |           | _      | 600        | _          | mV   |  |

| V <sub>ICM</sub> (AC and DC coupled)         | $V_{CCR_{GXB}} = 1.0 V$<br>full bandwidth               |       | 700         | _         |        | 700        | _          | mV   |  |

|                                              | $V_{CCR_{GXB}} = 1.0 V$<br>half bandwidth               |       | 700         | _         |        | 700        | _          | mV   |  |

| t <sub>LTR</sub> <sup>(149)</sup>            | —                                                       | _     | _           | 10        | _      | _          | 10         | μs   |  |

| t <sub>LTD</sub> <sup>(150)</sup>            | _                                                       | 4     |             |           | 4      | _          |            | μs   |  |

| t <sub>LTD_manual</sub> <sup>(151)</sup>     | —                                                       | 4     | _           |           | 4      | _          |            | μs   |  |

| t <sub>LTR_LTD_manual</sub> <sup>(152)</sup> | _                                                       | 15    |             |           | 15     | _          |            | μs   |  |

| Programmable equalization (AC Gain)          | Full bandwidth (6.25 GHz)<br>Half bandwidth (3.125 GHz) |       |             | 16        |        | _          | 16         | dB   |  |

2-26

Receiver

$<sup>^{(149)}</sup>$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

$<sup>^{(150)}</sup>$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

<sup>(151)</sup>  $t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{\text{LTR\_LTD\_manual}}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

| 2-28 | Transmitter |

|------|-------------|

|------|-------------|

| Symbol/Description                                                             | Conditions                                        | Trans | ceiver Spee  | d Grade 2 | Transc | eiver Spee   | ed Grade 3 | Unit |

|--------------------------------------------------------------------------------|---------------------------------------------------|-------|--------------|-----------|--------|--------------|------------|------|

| Symbol/Description                                                             | Conditions                                        | Min   | Тур          | Мах       | Min    | Тур          | Max        | Onic |

|                                                                                | 85- $\Omega$ setting                              | _     | 85 ± 20%     | _         |        | 85<br>± 20%  | _          | Ω    |

| Differential on-chip termination resistors                                     | 100-Ω setting                                     | —     | 100<br>± 20% | _         |        | 100<br>± 20% |            | Ω    |

|                                                                                | 120-Ω setting                                     | _     | 120<br>± 20% |           |        | 120<br>± 20% |            | Ω    |

|                                                                                | 150-Ω setting                                     | _     | 150<br>± 20% | _         |        | 150<br>± 20% |            | Ω    |

| V <sub>OCM</sub> (AC coupled)                                                  | 0.65-V setting                                    | _     | 650          |           |        | 650          |            | mV   |

| V <sub>OCM</sub> (DC coupled)                                                  | —                                                 |       | 650          |           |        | 650          |            | mV   |

| Intra-differential pair skew                                                   | Tx V <sub>CM</sub> = 0.5 V and slew rate of 15 ps | _     | _            | 15        | _      | _            | 15         | ps   |

| Intra-transceiver block transmitter x6 PMA bonded mode channel-to-channel skew |                                                   | —     |              | 120       |        | _            | 120        | ps   |

| Inter-transceiver block transmitter channel-to-channel skew                    | xN PMA bonded mode                                | —     | —            | 500       | _      | _            | 500        | ps   |

#### Arria V Device Overview

For more information about device ordering codes.

| Mada (164)  | Mode (164) Transceiver | PMA Width                   | 20  | 20  | 16   | 16   | 10  | 10   | 8    | 8    |

|-------------|------------------------|-----------------------------|-----|-----|------|------|-----|------|------|------|

| Speed Grade | PCS/Core Width         | 40                          | 20  | 32  | 16   | 20   | 10  | 16   | 8    |      |

| Pagistar    | 2                      | C3, I3L<br>core speed grade | 9.9 | 9   | 7.92 | 7.2  | 4.9 | 4.,5 | 3.92 | 3.6  |

| Register    | 3                      | C4, I4<br>core speed grade  | 8.8 | 8.2 | 7.04 | 6.56 | 4.4 | 4.1  | 3.52 | 3.28 |

**Operating Conditions** on page 2-1

## **10G PCS Data Rate**

## Table 2-31: 10G PCS Approximate Maximum Data Rate (Gbps) for Arria V GZ Devices

| Mode <sup>(165)</sup> | Transceiver Speed | PMA Width                   | 64      | 40      | 40    | 40      | 32       | 32    |

|-----------------------|-------------------|-----------------------------|---------|---------|-------|---------|----------|-------|

| Mode                  | Grade             | PCS Width                   | 64      | 66/67   | 50    | 40      | 64/66/67 | 32    |

| EIEO                  | 2                 | C3, I3L core speed<br>grade | 12.5    | 12.5    | 10.69 | 12.5    | 10.88    | 10.88 |

| FIFO                  | 3                 | C4, I4 core speed<br>grade  | 10.3125 | 10.3125 | 10.69 | 10.3125 | 9.92     | 9.92  |

| Pagistar              | 2                 | C3, I3L core speed<br>grade | 12.5    | 12.5    | 10.69 | 12.5    | 10.88    | 10.88 |

| Register              | 3                 | C4, I4 core speed<br>grade  | 10.3125 | 10.3125 | 10.69 | 10.3125 | 9.92     | 9.92  |

<sup>&</sup>lt;sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

<sup>&</sup>lt;sup>(165)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

| Memory        | Mode                                                                                             | Resou | rces Used |     | Perfor | mance |     | Unit |  |

|---------------|--------------------------------------------------------------------------------------------------|-------|-----------|-----|--------|-------|-----|------|--|

| Memory        | imoue                                                                                            | ALUTs | Memory    | C3  | C4     | I3L   | 14  | Onit |  |

|               | Single-port, all supported widths                                                                | 0     | 1         | 650 | 550    | 500   | 450 | MHz  |  |

|               | Simple dual-port, all supported widths                                                           | 0     | 1         | 650 | 550    | 500   | 450 | MHz  |  |

|               | Simple dual-port with the read-during-write option set to <b>Old Data</b> , all supported widths | 0     | 1         | 455 | 400    | 455   | 400 | MHz  |  |

| M20K<br>Block | Simple dual-port with ECC enabled, $512 \times 32$                                               | 0     | 1         | 400 | 350    | 400   | 350 | MHz  |  |

|               | Simple dual-port with ECC and optional pipeline registers enabled, 512 × 32                      | 0     | 1         | 500 | 450    | 500   | 450 | MHz  |  |

|               | True dual port, all supported widths                                                             | 0     | 1         | 650 | 550    | 500   | 450 | MHz  |  |

|               | ROM, all supported widths                                                                        | 0     | 1         | 650 | 550    | 500   | 450 | MHz  |  |

# **Temperature Sensing Diode Specifications**

## Table 2-37: Internal Temperature Sensing Diode Specification

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate  | Conversion Time | Resolution | Minimum Resolution<br>with no Missing<br>Codes |

|-------------------|----------|-----------------------------|----------------|-----------------|------------|------------------------------------------------|

| -40°C to 100°C    | ±8°C     | No                          | 1 MHz, 500 kHz | < 100 ms        | 8 bits     | 8 bits                                         |

# Table 2-38: External Temperature Sensing Diode Specifications for Arria V GZ Devices

| Description                              | Min | Тур | Max | Unit |

|------------------------------------------|-----|-----|-----|------|

| I <sub>bias</sub> , diode source current | 8   | —   | 200 | μΑ   |

| V <sub>bias,</sub> voltage across diode  | 0.3 | _   | 0.9 | V    |

| Series resistance                        |     |     | < 1 | Ω    |

AV-51002 2017.02.10

| Symbol                                                                    | Conditions                                                                                      |     | C3, I3I |     |     | C4, I4 |      | – Unit |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|---------|-----|-----|--------|------|--------|

| Symbol                                                                    | Conditions                                                                                      | Min | Тур     | Мах | Min | Тур    | Мах  | Onic   |

| t <sub>x litter</sub> - True Differential I/O                             | Total Jitter for Data Rate<br>600 Mbps - 1.25 Gbps                                              | _   | _       | 160 | _   |        | 160  | ps     |

| Standards                                                                 | Total Jitter for Data Rate<br>< 600 Mbps                                                        | _   | _       | 0.1 | _   |        | 0.1  | UI     |

| t <sub>x Jitter</sub> - Emulated Differential<br>I/O Standards with Three | Total Jitter for Data Rate<br>600 Mbps - 1.25 Gbps                                              | —   | _       | 300 | _   |        | 325  | ps     |

| External Output Resistor<br>Network                                       | Total Jitter for Data Rate<br>< 600 Mbps                                                        | _   | _       | 0.2 | _   |        | 0.25 | UI     |

| t <sub>DUTY</sub>                                                         | Transmitter output clock duty<br>cycle for both True and Emulated<br>Differential I/O Standards | 45  | 50      | 55  | 45  | 50     | 55   | %      |

|                                                                           | True Differential I/O Standards                                                                 |     | _       | 200 |     |        | 200  | ps     |

| t <sub>RISE</sub> & t <sub>FALL</sub>                                     | Emulated Differential I/O<br>Standards with three external<br>output resistor networks          | _   | _       | 250 | _   | _      | 300  | ps     |

|                                                                           | True Differential I/O Standards                                                                 |     | _       | 150 |     | _      | 150  | ps     |

| TCCS                                                                      | Emulated Differential I/O<br>Standards                                                          | _   | —       | 300 |     |        | 300  | ps     |

# **Receiver High-Speed I/O Specifications**

#### Table 2-41: Receiver High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol                                                                   | Conditions                                                                |       | C3, I3L |       |       | C4, I4 |       | Unit |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------|-------|---------|-------|-------|--------|-------|------|

| Symbol                                                                   | Conditions                                                                | Min   | Тур     | Мах   | Min   | Тур    | Max   | Onic |

| True Differential I/O<br>Standards - f <sub>HSDRDPA</sub><br>(data rate) | SERDES factor $J = 3$ to 10<br>(192), (193), (194), (195), (196), (197)   | 150   | _       | 1250  | 150   |        | 1050  | Mbps |

|                                                                          | SERDES factor $J \ge 4$<br>LVDS RX with DPA<br>(193), (195), (196), (197) | 150   |         | 1600  | 150   |        | 1250  | Mbps |

|                                                                          | SERDES factor J = 2,<br>uses DDR Registers                                | (198) | _       | (199) | (198) | _      | (199) | Mbps |

|                                                                          | SERDES factor J = 1,<br>uses SDR Register                                 | (198) |         | (199) | (198) |        | (199) | Mbps |

|                                                                          | SERDES factor $J = 3$ to 10                                               | (198) | —       | (200) | (198) | _      | (200) | Mbps |

| f <sub>HSDR</sub> (data rate)                                            | SERDES factor J = 2,<br>uses DDR Registers                                | (198) | —       | (199) | (198) |        | (199) | Mbps |

|                                                                          | SERDES factor J = 1,<br>uses SDR Register                                 | (198) | _       | (199) | (198) | _      | (199) | Mbps |

$^{(192)}$  The  $F_{MAX}$  specification is based on the fast clock used for serial data. The interface  $F_{MAX}$  is also dependent on the parallel clock domain which is design dependent and requires timing analysis.

<sup>(193)</sup> Arria V GZ RX LVDS will need DPA. For Arria V GZ TX LVDS, the receiver side component must have DPA.

<sup>(194)</sup> Arria V GZ LVDS serialization and de-serialization factor needs to be x4 and above.

<sup>(195)</sup> Requires package skew compensation with PCB trace length.

<sup>(196)</sup> Do not mix single-ended I/O buffer within LVDS I/O bank.

<sup>(197)</sup> Chip-to-chip communication only with a maximum load of 5 pF.

<sup>(198)</sup> The minimum specification depends on the clock source (for example, the PLL and clock pin) and the clock routing resource (global, regional, or local) that you use. The I/O differential buffer and input register do not have a minimum toggle rate.

<sup>(199)</sup> The maximum ideal data rate is the SERDES factor (J) x the PLL maximum output frequency (fOUT) provided you can close the design timing and the signal integrity simulation is clean.

<sup>(200)</sup> You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

## Non DPA Mode High-Speed I/O Specifications

#### Table 2-46: High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol          | Conditions | C3, I3L |     |     | C4, I4 |     |     | Unit |

|-----------------|------------|---------|-----|-----|--------|-----|-----|------|

|                 |            | Min     | Тур | Max | Min    | Тур | Мах | Onic |

| Sampling Window | _          |         |     | 300 |        |     | 300 | ps   |

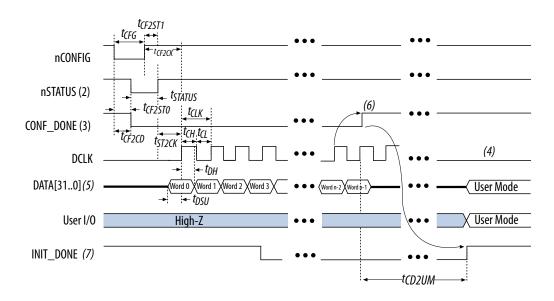

## FPP Configuration Timing when DCLK to DATA[] = 1

#### Figure 2-7: FPP Configuration Timing Waveform When the DCLK-to-DATA[] Ratio is 1

Timing waveform for FPP configuration when using a MAX<sup>®</sup> II or MAX V device as an external host.

Notes:

- 1. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic-high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 2. After power-up, the Arria V GZ device holds nSTATUS low for the time of the POR delay.

- 3. After power-up, before and during configuration, CONF\_DONE is low.

- 4. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 5. For FPP ×16, use DATA[15..0]. For FPP ×8, use DATA[7..0]. DATA[31..0] are available as a user I/O pin after configuration. The state of this pin depends on the dual-purpose pin settings.

- 6. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high when the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 7. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.

Arria V GZ Device Datasheet

# FPP Configuration Timing when DCLK to DATA[] > 1

#### Figure 2-8: FPP Configuration Timing Waveform When the DCLK-to-DATA[] Ratio is >1,

t<sub>CF2ST1</sub> tcfg ;↔ nCONFIG ŤĊF2CK nSTATUS (3) 🕳 tstatus tCF2ST0 CONF\_DONE (4) TCL tCH tsT2CK ŤĊF2CD (8) DCLK (6) (7) 1 2 ••• r 2 ••• r 1  $\mathbf{D}$ (5) tCLK DATA[31..0] (8) Word 0 Word User Mode Word 3 • • • Word (n-1) tDH tDH tpsy High-Z User I/O User Mode INIT DONE (9) tCD2UM

Timing when using a MAX II device, MAX V device, or microprocessor as an external host.

#### Notes:

- 1. To find out the DCLK-to-DATA[] ratio for your system, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 2. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 3. After power-up, the Arria V GZ device holds nSTATUS low for the time as specified by the POR delay.

- 4. After power-up, before and during configuration, CONF\_DONE is low.

- 5. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 6. "r" denotes the DCLK-to-DATA[] ratio. For the DCLK-to-DATA[] ratio based on the decompression and the design security feature enable settings, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 7. If needed, pause DCLK by holding it low. When DCLK restarts, the external host must provide data on the DATA[31.0] pins prior to sending the first DCLK rising edge.

- 8. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high after the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 9. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices For more information about the reconfiguration input for the ALTREMOTE\_UPDATE IP core, refer to the "User Watchdog Timer" section.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices For more information about the reset\_timer input for the ALTREMOTE\_UPDATE IP core, refer to the "Remote System Upgrade State Machine" section.

# User Watchdog Internal Oscillator Frequency Specification

#### Table 2-65: User Watchdog Internal Oscillator Frequency Specifications

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O Timing and the Quartus II Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Quartus II Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete placeand-route.

#### **Related Information**

# **Arria V Devices Documentation page**

For the Excel-based I/O Timing spreadsheet

#### Arria V GZ Device Datasheet

Altera Corporation

<sup>&</sup>lt;sup>(226)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "Remote System Upgrade State Machine" section in the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

<sup>&</sup>lt;sup>(227)</sup> This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "User Watchdog Timer" section in the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

| Term                 | Definition                                                                                                                          |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                      | Single-Ended Waveform       Positive Channel (p) = V <sub>0H</sub> $V_{0D}$ Negative Channel (n) = V <sub>0L</sub> VCM       Ground |  |  |  |  |  |

|                      | Differential Waveform<br>$V_{0D}$<br>$V_{0D}$<br>$V_{0D}$<br>$v_{0D}$<br>$v_{0D}$                                                   |  |  |  |  |  |

| f <sub>HSCLK</sub>   | Left and right PLL input clock frequency.                                                                                           |  |  |  |  |  |

| f <sub>HSDR</sub>    | High-speed I/O block—Maximum and minimum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI), non-DPA.                              |  |  |  |  |  |

| f <sub>HSDRDPA</sub> | High-speed I/O block—Maximum and minimum LVDS data transfer rate (f <sub>HSDRDPA</sub> = 1/TUI), DPA.                               |  |  |  |  |  |

| J                    | High-speed I/O block—Deserialization factor (width of parallel data bus).                                                           |  |  |  |  |  |