Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 7362                                                       |

| Number of Logic Elements/Cells | 156000                                                     |

| Total RAM Bits                 | 11746304                                                   |

| Number of I/O                  | 416                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 896-BBGA, FCBGA                                            |

| Supplier Device Package        | 896-FBGA (31x31)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxma3d4f31c4g |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol                            | Description                                 | Condition          | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|-----------------------------------|---------------------------------------------|--------------------|------------------------|---------|------------------------|------|

| V                                 | Cara valtaga nawar supply                   | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| $V_{CC}$                          | Core voltage power supply                   | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

| V                                 | Periphery circuitry, PCIe hard IP block,    | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| $V_{CCP}$                         | and transceiver PCS power supply            | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

|                                   |                                             | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| V                                 | Configuration pins power supply             | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

| $V_{CCPGM}$                       | Configuration pins power suppry             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

|                                   |                                             | 1.8 V              | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CC_AUX</sub>               | Auxiliary supply                            | _                  | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCBAT</sub> <sup>(2)</sup> | Battery back-up power supply                | _                  | 1.2                    | _       | 3.0                    | V    |

|                                   | (For design security volatile key register) |                    |                        |         |                        |      |

|                                   |                                             | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| $V_{CCPD}^{(3)}$                  | I/O pre-driver power supply                 | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

|                                   |                                             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

<sup>(1)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(2)</sup> If you do not use the design security feature in Arria V devices, connect V<sub>CCBAT</sub> to a 1.5-V, 2.5-V, or 3.0-V power supply. Arria V power-on reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

$<sup>^{(3)}</sup>$  V<sub>CCPD</sub> must be 2.5 V when V<sub>CCIO</sub> is 2.5, 1.8, 1.5, 1.35, 1.25, or 1.2 V. V<sub>CCPD</sub> must be 3.0 V when V<sub>CCIO</sub> is 3.0 V. V<sub>CCPD</sub> must be 3.3 V when V<sub>CCIO</sub> is 3.3 V.

| Symbol/Description                               | Condition                                            | Trans | sceiver Speed Gr | ade 4 | Transc | Unit         |      |        |

|--------------------------------------------------|------------------------------------------------------|-------|------------------|-------|--------|--------------|------|--------|

| Symbol/Description                               | Condition                                            | Min   | Тур              | Max   | Min    | Тур          | Max  | Unit   |

| Spread-spectrum<br>modulating clock<br>frequency | PCI Express® (PCIe)                                  | 30    | _                | 33    | 30     | _            | 33   | kHz    |

| Spread-spectrum<br>downspread                    | PCIe                                                 | _     | 0 to -0.5%       | _     | _      | 0 to -0.5%   | _    | _      |

| On-chip termination resistors                    | _                                                    | _     | 100              | _     | _      | 100          | _    | Ω      |

| V <sub>ICM</sub> (AC coupled)                    | _                                                    | _     | 1.1/1.15(26)     | _     | _      | 1.1/1.15(26) | _    | V      |

| V <sub>ICM</sub> (DC coupled)                    | HCSL I/O standard for<br>the PCIe reference<br>clock | 250   | _                | 550   | 250    | _            | 550  | mV     |

|                                                  | 10 Hz                                                | _     | _                | -50   | _      | _            | -50  | dBc/Hz |

|                                                  | 100 Hz                                               | _     | _                | -80   | _      | _            | -80  | dBc/Hz |

| Transmitter REFCLK phase                         | 1 KHz                                                | _     | _                | -110  | _      | _            | -110 | dBc/Hz |

| noise <sup>(27)</sup>                            | 10 KHz                                               | _     | _                | -120  | _      | _            | -120 | dBc/Hz |

|                                                  | 100 KHz                                              | _     | _                | -120  | _      | _            | -120 | dBc/Hz |

|                                                  | ≥1 MHz                                               | _     | _                | -130  | _      | _            | -130 | dBc/Hz |

| $R_{REF}$                                        | _                                                    | _     | 2000 ±1%         | _     | _      | 2000 ±1%     | _    | Ω      |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

For data rate  $\leq$  3.2 Gbps, connect  $V_{CCR\_GXBL/R}$  to either 1.1-V or 1.15-V power supply. For data rate > 3.2 Gbps, connect  $V_{CCR\_GXBL/R}$  to a 1.15-V power supply. For details, refer to the Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines.

The transmitter REFCLK phase jitter is 30 ps p-p at bit error rate (BER) 10<sup>-12</sup>.

| Symbol/Description                 | Condition | Tran | sceiver Speed Gra | Unit |        |

|------------------------------------|-----------|------|-------------------|------|--------|

| Symbol/Description                 | Condition | Min  | Тур               | Max  | Offic  |

|                                    | 10 Hz     | _    | _                 | -50  | dBc/Hz |

|                                    | 100 Hz    | _    | _                 | -80  | dBc/Hz |

| Transmitter REFCLK phase noise(43) | 1 KHz     | _    | _                 | -110 | dBc/Hz |

| Transmitter REPCER phase noise     | 10 KHz    | _    | _                 | -120 | dBc/Hz |

|                                    | 100 KHz   | _    | _                 | -120 | dBc/Hz |

|                                    | ≥ 1 MHz   | _    | _                 | -130 | dBc/Hz |

| R <sub>REF</sub>                   | _         | _    | 2000 ±1%          | _    | Ω      |

## Table 1-27: Transceiver Clocks Specifications for Arria V GT and ST Devices

| Symbol/Description                                                             | Condition            | Tran | sceiver Speed Gra | Unit |       |

|--------------------------------------------------------------------------------|----------------------|------|-------------------|------|-------|

| 3yiiiboi/ Description                                                          | Condition            | Min  | Тур               | Max  | Offic |

| fixedclk clock frequency                                                       | PCIe Receiver Detect | _    | 125               | _    | MHz   |

| Transceiver Reconfiguration<br>Controller IP (mgmt_clk_clk) clock<br>frequency | _                    | 75   | _                 | 125  | MHz   |

### Table 1-28: Receiver Specifications for Arria V GT and ST Devices

| Symbol/Description Condition       |                                          | Ti  | Unit |        |      |  |

|------------------------------------|------------------------------------------|-----|------|--------|------|--|

| Symbol/Description                 | Collattion                               | Min | Тур  | Max    | Onit |  |

| Supported I/O Standards            | 1.5 V PCML, 2.5 V PCML, LVPECL, and LVDS |     |      |        |      |  |

| Data rate (6-Gbps transceiver)(44) | _                                        | 611 | _    | 6553.6 | Mbps |  |

Arria V GX, GT, SX, and ST Device Datasheet

The transmitter REFCLK phase jitter is 30 ps p-p (5 ps RMS) with bit error rate (BER) 10<sup>-12</sup>, equivalent to 14 sigma.

To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

| Quartus Prime 1st                 | Quartus Prime V <sub>OD</sub> Setting |             |             |             |             |             |              |      |

|-----------------------------------|---------------------------------------|-------------|-------------|-------------|-------------|-------------|--------------|------|

| Post Tap Pre-<br>Emphasis Setting | 10 (200 mV)                           | 20 (400 mV) | 30 (600 mV) | 35 (700 mV) | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) | Unit |

| 16                                | _                                     | _           | 9.56        | 7.73        | 6.49        | _           | _            | dB   |

| 17                                | _                                     | _           | 10.43       | 8.39        | 7.02        | _           | _            | dB   |

| 18                                | _                                     | _           | 11.23       | 9.03        | 7.52        | _           | _            | dB   |

| 19                                | _                                     | _           | 12.18       | 9.7         | 8.02        | _           | _            | dB   |

| 20                                | _                                     | _           | 13.17       | 10.34       | 8.59        | _           | _            | dB   |

| 21                                | _                                     | _           | 14.2        | 11.1        | _           | _           | _            | dB   |

| 22                                | _                                     | _           | 15.38       | 11.87       | _           | _           | _            | dB   |

| 23                                | _                                     | _           | _           | 12.67       | _           | _           | _            | dB   |

| 24                                | _                                     | _           | _           | 13.48       | _           | _           | _            | dB   |

| 25                                | _                                     | _           | _           | 14.37       | _           | _           | _            | dB   |

| 26                                | _                                     | _           | _           | _           | _           | _           | _            | dB   |

| 27                                | _                                     | _           | _           | _           | _           | _           | _            | dB   |

| 28                                | _                                     | _           | _           | _           | _           | _           | _            | dB   |

| 29                                | _                                     | _           | _           | _           | _           | _           | _            | dB   |

| 30                                | _                                     | _           | _           | _           | _           | _           | _            | dB   |

| 31                                | _                                     | _           | _           | _           | _           | _           | _            | dB   |

#### **Related Information**

**SPICE Models for Altera Devices**

Provides the Arria V HSSI HSPICE models.

## **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Arria V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Altera Sales Representative.

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

| Protocol                                         | Sub-protocol | Data Rate (Mbps) |

|--------------------------------------------------|--------------|------------------|

|                                                  | SONET 155    | 155.52           |

| SONET                                            | SONET 622    | 622.08           |

|                                                  | SONET 2488   | 2,488.32         |

|                                                  | GPON 155     | 155.52           |

| Gigabit-capable passive optical network (GPON)   | GPON 622     | 622.08           |

| digabit-capable passive optical network (di Oiv) | GPON 1244    | 1,244.16         |

|                                                  | GPON 2488    | 2,488.32         |

| QSGMII                                           | QSGMII 5000  | 5,000            |

# **Core Performance Specifications**

## **Clock Tree Specifications**

Table 1-35: Clock Tree Specifications for Arria V Devices

| Parameter                       |          | Unit     |     |     |

|---------------------------------|----------|----------|-----|-----|

| raiailletei                     | −I3, −C4 | −I5, −C5 | -C6 | ome |

| Global clock and Regional clock | 625      | 625      | 525 | MHz |

| Peripheral clock                | 450      | 400      | 350 | MHz |

## **PLL Specifications**

## Table 1-36: PLL Specifications for Arria V Devices

This table lists the Arria V PLL block specifications. Arria V PLL block does not include HPS PLL.

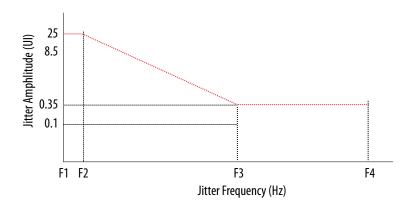

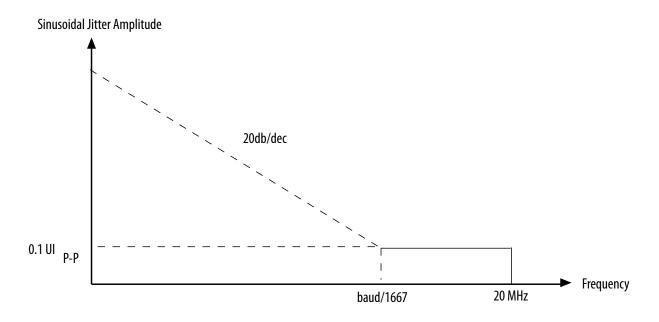

## LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specifications

Figure 1-5: LVDS Soft-Clock Data Recovery (CDR)/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate Equal to 1.25 Gbps

Table 1-42: LVDS Soft-CDR/DPA Sinusoidal Jitter Mask Values for a Data Rate Equal to 1.25 Gbps

| Jitter Freq | uency (Hz) | Sinusoidal Jitter (UI) |

|-------------|------------|------------------------|

| F1          | 10,000     | 25.000                 |

| F2          | 17,565     | 25.000                 |

| F3          | 1,493,000  | 0.350                  |

| F4          | 50,000,000 | 0.350                  |

Figure 1-6: LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate Less than 1.25 Gbps

## **DLL Frequency Range Specifications**

Table 1-43: DLL Frequency Range Specifications for Arria V Devices

| Parameter                     | −I3, −C4  | −I5, −C5  | -C6       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 200 – 667 | 200 – 667 | 200 – 667 | MHz  |

## **DQS Logic Block Specifications**

## Table 1-44: DQS Phase Shift Error Specifications for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Arria V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | −I3, −C4 | −I5, −C5 | -C6 | Unit |

|----------------------------|----------|----------|-----|------|

| 2                          | 40       | 80       | 80  | ps   |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

#### **HPS Clock Performance**

Table 1-48: HPS Clock Performance for Arria V Devices

| Symbol/Description                       | -l3  | -C4 | −C5, −I5 | -C6 | Unit |

|------------------------------------------|------|-----|----------|-----|------|

| mpu_base_clk (microprocessor unit clock) | 1050 | 925 | 800      | 700 | MHz  |

| main_base_clk (L3/L4 interconnect clock) | 400  | 400 | 400      | 350 | MHz  |

| h2f_user0_clk                            | 100  | 100 | 100      | 100 | MHz  |

| h2f_user1_clk                            | 100  | 100 | 100      | 100 | MHz  |

| h2f_user2_clk                            | 200  | 200 | 200      | 160 | MHz  |

## **HPS PLL Specifications**

#### **HPS PLL VCO Frequency Range**

Table 1-49: HPS PLL VCO Frequency Range for Arria V Devices

| Description | Speed Grade   | Minimum | Maximum | Unit |

|-------------|---------------|---------|---------|------|

|             | -C5, -I5, -C6 | 320     | 1,600   | MHz  |

| VCO range   | -C4           | 320     | 1,850   | MHz  |

|             | -I3           | 320     | 2,100   | MHz  |

## **HPS PLL Input Clock Range**

The HPS PLL input clock range is 10 – 50 MHz. This clock range applies to both HPS\_CLK1 and HPS\_CLK2 inputs.

#### **Related Information**

### **Clock Select, Booting and Configuration chapter**

Provides more information about the clock range for different values of clock select (CSEL).

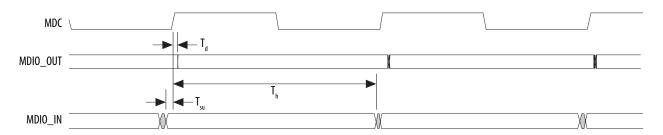

Figure 1-15: MDIO Timing Diagram

## I<sup>2</sup>C Timing Characteristics

Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Cumbal                | Description                                       | Standaı | d Mode | Fast I | Mode | Unit |  |

|-----------------------|---------------------------------------------------|---------|--------|--------|------|------|--|

| Symbol                | Description                                       | Min     | Max    | Min    | Max  | Onit |  |

| $T_{clk}$             | Serial clock (SCL) clock period                   | 10      | _      | 2.5    | _    | μs   |  |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7     | _      | 0.6    | _    | μs   |  |

| $T_{clklow}$          | SCL low time                                      | 4       | _      | 1.3    | _    | μs   |  |

| $T_s$                 | Setup time for serial data line (SDA) data to SCL | 0.25    | _      | 0.1    | _    | μs   |  |

| $T_{h}$               | Hold time for SCL to SDA data                     | 0       | 3.45   | 0      | 0.9  | μs   |  |

| $T_d$                 | SCL to SDA output data delay                      | _       | 0.2    | _      | 0.2  | μs   |  |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7     | _      | 0.6    | _    | μs   |  |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4       | _      | 0.6    | _    | μs   |  |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4       | _      | 0.6    | _    | μs   |  |

| POR Delay | Minimum | Maximum | Unit |

|-----------|---------|---------|------|

| Standard  | 100     | 300     | ms   |

#### **Related Information**

**MSEL Pin Settings**

Provides more information about POR delay based on MSEL pin settings for each configuration scheme.

## **FPGA JTAG Configuration Timing**

Table 1-64: FPGA JTAG Timing Parameters and Values for Arria V Devices

| Symbol                  | Description                              | Min                     | Max                | Unit |

|-------------------------|------------------------------------------|-------------------------|--------------------|------|

| $t_{JCP}$               | TCK clock period                         | 30, 167 <sup>(92)</sup> | _                  | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14                      | _                  | ns   |

| $t_{JCL}$               | TCK clock low time                       | 14                      | _                  | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2                       | _                  | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3                       | _                  | ns   |

| $t_{JPH}$               | JTAG port hold time                      | 5                       | _                  | ns   |

| $t_{ m JPCO}$           | JTAG port clock to output                | _                       | 12 <sup>(93)</sup> | ns   |

| $t_{JPZX}$              | JTAG port high impedance to valid output | _                       | 14 <sup>(93)</sup> | ns   |

| $t_{JPXZ}$              | JTAG port valid output to high impedance | _                       | 14 <sup>(93)</sup> | ns   |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

$<sup>^{(92)}</sup>$  The minimum TCK clock period is 167 ns if  $V_{CCBAT}$  is within the range 1.2 V – 1.5 V when you perform the volatile key programming.

<sup>(93)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

| Symbol                         | Parameter                        | Typical     | Unit |

|--------------------------------|----------------------------------|-------------|------|

| $\mathrm{D}_{\mathrm{OUTBUF}}$ |                                  | 0 (default) | ps   |

|                                | Rising and/or falling edge delay | 50          | ps   |

|                                | Kishig and/or faming edge delay  | 100         | ps   |

|                                |                                  | 150         | ps   |

# Glossary

Table 1-78: Glossary

Arria V GX, GT, SX, and ST Device Datasheet **Altera Corporation**

AV-51002 2017.02.10

| Term                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Definition                 |                     |                     |  |  |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|---------------------|--|--|--|--|

| Single-ended voltage referenced I/O standard | The JEDEC standard for the SSTL and HSTL I/O defines both the AC and DC input signal values indicate the voltage levels at which the receiver must meet its timing specifications. indicate the voltage levels at which the final logic state of the receiver is unambiguously dereceiver input has crossed the AC value, the receiver changes to the new logic state.  The new logic state is then maintained as long as the input stays beyond the DC threshold is intended to provide predictable receiver timing in the presence of input waveform ringing Single-Ended Voltage Referenced I/O Standard |                            |                     |                     |  |  |  |  |

|                                              | Single-Ended voltage Referenced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1/O Standard               |                     |                     |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |                     | V <sub>CC10</sub>   |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |                     |                     |  |  |  |  |

|                                              | V <sub>OH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            | V <sub>IH(AC)</sub> |                     |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |                     | V <sub>IH(DC)</sub> |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V REF                      |                     | V <sub>IL(DC)</sub> |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |                     | V IL(AC)            |  |  |  |  |

|                                              | V <sub>0L</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |                     |                     |  |  |  |  |

|                                              | V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |                     |                     |  |  |  |  |

| $t_{\rm C}$                                  | High-speed receiver/transmitter input and output clock period.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |                     |                     |  |  |  |  |

| TCCS (channel-to-channel-skew)               | The timing difference between the fastest and slowest output edges, including the $t_{CO}$ variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table).                                                                                                                                                                                                                                                                                                                                     |                            |                     |                     |  |  |  |  |

| $t_{ m DUTY}$                                | High-speed I/O block—Duty cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | e on high-speed transmitte | r output clo        | ock.                |  |  |  |  |

Arria V GX, GT, SX, and ST Device Datasheet **Altera Corporation**

### **Bus Hold Specifications**

Table 2-9: Bus Hold Parameters for Arria V GZ Devices

|                              |                   |                                                           | V <sub>ccio</sub> |      |       |      |       |            |       |            |       |      |      |

|------------------------------|-------------------|-----------------------------------------------------------|-------------------|------|-------|------|-------|------------|-------|------------|-------|------|------|

| Parameter                    | Symbol            | Conditions                                                | 1.2               | 2 V  | 1.5   | 5 V  | 1.8   | 8 <b>V</b> | 2.    | 5 <b>V</b> | 3.0   | ) V  | Unit |

|                              |                   |                                                           | Min               | Max  | Min   | Max  | Min   | Max        | Min   | Max        | Min   | Max  |      |

| Low<br>sustaining<br>current | $I_{SUSL}$        | $V_{IN} > V_{IL}$ (maximum)                               | 22.5              | _    | 25.0  | _    | 30.0  | _          | 50.0  | _          | 70.0  | _    | μΑ   |

| High sustaining current      | I <sub>SUSH</sub> | $V_{IN} < V_{IH} \label{eq:VIN}$ (minimum)                | -22.5             | _    | -25.0 | _    | -30.0 | _          | -50.0 | _          | -70.0 | _    | μА   |

| Low<br>overdrive<br>current  | $I_{ODL}$         | $\begin{array}{c} 0 V < V_{IN} < \\ V_{CCIO} \end{array}$ | _                 | 120  | _     | 160  | _     | 200        | _     | 300        | _     | 500  | μΑ   |

| High<br>overdrive<br>current | $I_{ODH}$         | 0V < V <sub>IN</sub> < V <sub>CCIO</sub>                  | _                 | -120 | _     | -160 | _     | -200       | _     | -300       | _     | -500 | μА   |

| Bus-hold<br>trip point       | V <sub>TRIP</sub> | _                                                         | 0.45              | 0.95 | 0.50  | 1.00 | 0.68  | 1.07       | 0.70  | 1.70       | 0.80  | 2.00 | V    |

### **On-Chip Termination (OCT) Specifications**

If you enable OCT calibration, calibration is automatically performed at power-up for I/Os connected to the calibration block.

## Table 2-10: OCT Calibration Accuracy Specifications for Arria V GZ Devices

OCT calibration accuracy is valid at the time of calibration only.

Altera Corporation Arria V GZ Device Datasheet

| Symbol | Description                                           | V <sub>CCIO</sub> (V) | Typical | Unit |  |

|--------|-------------------------------------------------------|-----------------------|---------|------|--|

|        |                                                       | 3.0                   | 0.0297  |      |  |

|        |                                                       | 2.5                   | 0.0344  |      |  |

| dR/dV  | OCT variation with voltage without re-calibration     | 1.8                   | 0.0499  | %/mV |  |

|        |                                                       | 1.5                   | 0.0744  |      |  |

|        |                                                       | 1.2                   | 0.1241  |      |  |

|        |                                                       | 3.0                   | 0.189   |      |  |

|        |                                                       | 2.5                   | 0.208   |      |  |

| dR/dT  | OCT variation with temperature without re-calibration | 1.8                   | 0.266   | %/°C |  |

|        |                                                       | 1.5                   | 0.273   |      |  |

|        |                                                       | 1.2                   | 0.317   |      |  |

## **Pin Capacitance**

Table 2-13: Pin Capacitance for Arria V GZ Devices

| Symbol      | Description                                                      | Maximum | Unit |

|-------------|------------------------------------------------------------------|---------|------|

| $C_{IOTB}$  | Input capacitance on the top and bottom I/O pins                 | 6       | pF   |

| $C_{IOLR}$  | Input capacitance on the left and right I/O pins                 | 6       | pF   |

| $C_{OUTFB}$ | Input capacitance on dual-purpose clock output and feedback pins | 6       | pF   |

| Symbol/Description   | Conditions          | Trans | ceiver Spee | d Grade 2 | Transc | Unit |     |       |

|----------------------|---------------------|-------|-------------|-----------|--------|------|-----|-------|

| 3yiiiboi/Description | Conditions          | Min   | Тур         | Max       | Min    | Тур  | Max | Offic |

|                      | DC gain setting = 0 | _     | 0           | _         | _      | 0    | _   | dB    |

|                      | DC gain setting = 1 | _     | 2           | _         | _      | 2    | _   | dB    |

| Programmable DC gain | DC gain setting = 2 | _     | 4           | _         | _      | 4    | _   | dB    |

|                      | DC gain setting = 3 | _     | 6           | _         | _      | 6    | _   | dB    |

|                      | DC gain setting = 4 | _     | 8           | _         | _      | 8    | _   | dB    |

#### **Related Information**

#### Arria V Device Overview

For more information about device ordering codes.

#### **Transmitter**

### Table 2-25: Transmitter Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description       | Conditions           | Transceiver Speed Grade 2 |     |       | Transc | Unit |         |       |

|--------------------------|----------------------|---------------------------|-----|-------|--------|------|---------|-------|

| Symbol/Description       | Collations           | Min                       | Тур | Max   | Min    | Тур  | Max     | Offic |

| Supported I/O Standards  | 1.4-V and 1.5-V PCML |                           |     |       |        |      |         |       |

| Data rate (Standard PCS) | _                    | 600                       | _   | 9900  | 600    | _    | 8800    | Mbps  |

| Data rate (10G PCS)      | _                    | 600                       | _   | 12500 | 600    | _    | 10312.5 | Mbps  |

| Symbol                     | Parameter                                                                                                | Min | Тур | Max | Unit |

|----------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $ m f_{OUT}$ $^{(169)}$    | Output frequency for an internal global or regional clock (C3, I3L speed grade)                          | _   | _   | 650 | MHz  |

| TOUT                       | Output frequency for an internal global or regional clock (C4, I4 speed grade)                           | _   | _   | 580 | MHz  |

| £ (169)                    | Output frequency for an external clock output (C3, I3L speed grade)                                      | _   | _   | 667 | MHz  |

| f <sub>OUT_EXT</sub> (169) | Output frequency for an external clock output (C4, I4 speed grade)                                       | _   | _   | 533 | MHz  |

| t <sub>OUTDUTY</sub>       | Duty cycle for a dedicated external clock output (when set to 50%)                                       | 45  | 50  | 55  | %    |

| $t_{FCOMP}$                | External feedback clock compensation time                                                                | _   | _   | 10  | ns   |

| f <sub>DYCONFIGCLK</sub>   | Dynamic configuration clock for mgmt_clk and scanclk                                                     | _   | _   | 100 | MHz  |

| t <sub>LOCK</sub>          | Time required to lock from the end-of-device configuration or deassertion of areset                      | _   | _   | 1   | ms   |

| t <sub>DLOCK</sub>         | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) | _   | _   | 1   | ms   |

|                            | PLL closed-loop low bandwidth                                                                            | _   | 0.3 | _   | MHz  |

| $f_{CLBW}$                 | PLL closed-loop medium bandwidth                                                                         | _   | 1.5 | _   | MHz  |

|                            | PLL closed-loop high bandwidth (170)                                                                     | _   | 4   | _   | MHz  |

| t <sub>PLL_PSERR</sub>     | Accuracy of PLL phase shift                                                                              | _   | _   | ±50 | ps   |

| t <sub>ARESET</sub>        | Minimum pulse width on the areset signal                                                                 |     | _   | _   | ns   |

This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $f_{OUT}$  of the PLL. High bandwidth PLL settings are not supported in external feedback mode.

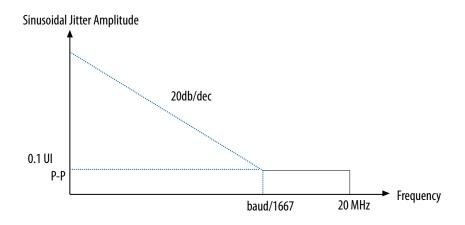

Figure 2-5: LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate < 1.25 Gbps

## Non DPA Mode High-Speed I/O Specifications

### Table 2-46: High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol          | Conditions | C3, I3L |     |     | C4, I4 |     |     | - Unit |

|-----------------|------------|---------|-----|-----|--------|-----|-----|--------|

|                 |            | Min     | Тур | Max | Min    | Тур | Max | Offic  |

| Sampling Window | _          | _       | _   | 300 | _      | _   | 300 | ps     |

**Altera Corporation** Arria V GZ Device Datasheet

| Symbol               | Parameter                                         | Minimum                                                            | Maximum | Unit |

|----------------------|---------------------------------------------------|--------------------------------------------------------------------|---------|------|

| $t_{\mathrm{CD2CU}}$ | CONF_DONE high to CLKUSR enabled                  | 4 × maximum dclk period                                            | _       | _    |

| t <sub>CD2UMC</sub>  | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> +<br>(8576 × CLKUSR<br>period) <sup>(215)</sup> | _       | _    |

#### **Related Information**

- DCLK-to-DATA[] Ratio (r) for FPP Configuration on page 2-57

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Altera Corporation Arria V GZ Device Datasheet

To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

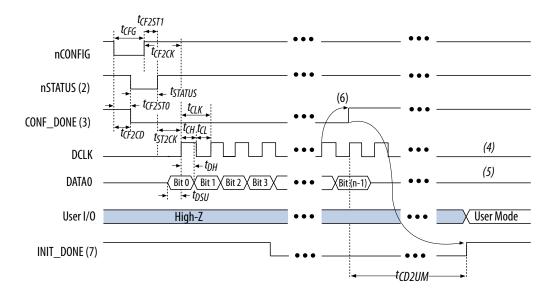

## **Passive Serial Configuration Timing**

### Figure 2-10: PS Configuration Timing Waveform

Timing waveform for a passive serial (PS) configuration when using a MAX II device, MAX V device, or microprocessor as an external host.

#### Notes:

- 1. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 2. After power-up, the Arria V GZ device holds nSTATUS low for the time of the POR delay.

- 3. After power-up, before and during configuration, CONF\_DONE is low.

- 4. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 5. DATA0 is available as a user I/O pin after configuration. The state of this pin depends on the dual-purpose pin settings in the Device and Pins Option.

- 6. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high after the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 7. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.

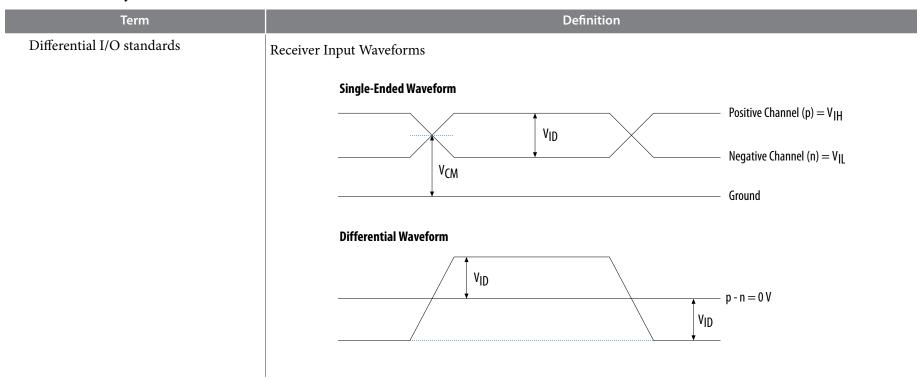

| Term               | Definition                                                                                                                                                       |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| $V_{OCM}$          | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                        |  |  |

| V <sub>OD</sub>    | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. |  |  |

| V <sub>SWING</sub> | Differential input voltage                                                                                                                                       |  |  |

| $V_{X}$            | Input differential cross point voltage                                                                                                                           |  |  |

| V <sub>OX</sub>    | Output differential cross point voltage                                                                                                                          |  |  |

| W                  | High-speed I/O block—clock boost factor                                                                                                                          |  |  |

# **Document Revision History**

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2017 | 2017.02.10 | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is 1" table.</li> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is &gt;1" table.</li> </ul>                                                                                                                     |

|               |            | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "AS Timing Parameters for AS x1 and AS x4 Configurations in Arria V GZ Devices" table.</li> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "PS Timing Parameters for Arria V GZ Devices" table.</li> <li>Changed the minimum number of clock cycles value in the "Initialization Clock Source Option and the Maximum Frequency for Arria V GZ Devices" table.</li> </ul> |

Altera Corporation Arria V GZ Device Datasheet