# E·XFL

#### Intel - 5AGXMA5G4F35C5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 8962                                                       |

| Number of Logic Elements/Cells | 190000                                                     |

| Total RAM Bits                 | 13284352                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxma5g4f35c5n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Transceiver Power Supply Operating Conditions**

| Table 1-4: Transceiver Power Supply Operating Conditions for Arria V Device | es |

|-----------------------------------------------------------------------------|----|

|-----------------------------------------------------------------------------|----|

| Symbol                | Description                                           | Minimum <sup>(5)</sup> | Typical                 | Maximum <sup>(5)</sup> | Unit |

|-----------------------|-------------------------------------------------------|------------------------|-------------------------|------------------------|------|

| V <sub>CCA_GXBL</sub> | Transceiver high voltage power (left side)            | 2.375                  | 2.500                   | 2.625                  | V    |

| V <sub>CCA_GXBR</sub> | Transceiver high voltage power (right side)           | 2.373                  | 2.300                   | 2.025                  | v    |

| V <sub>CCR_GXBL</sub> | GX and SX speed grades—receiver power (left side)     | 1.08/1.12              | 1.1/1.15 <sup>(6)</sup> | 1.14/1.18              | V    |

| V <sub>CCR_GXBR</sub> | GX and SX speed grades—receiver power (right side)    | 1.00/1.12              | 1.1/1.13                | 1.14/1.10              | v    |

| V <sub>CCR_GXBL</sub> | GT and ST speed grades—receiver power (left side)     | 1.17                   | 1.20                    | 1.23                   | V    |

| V <sub>CCR_GXBR</sub> | GT and ST speed grades—receiver power (right side)    | 1.17                   | 1.20                    | 1.23                   | v    |

| V <sub>CCT_GXBL</sub> | GX and SX speed grades—transmitter power (left side)  | 1.08/1.12              | 1.1/1.15 <sup>(6)</sup> | 1.14/1.18              | V    |

| V <sub>CCT_GXBR</sub> | GX and SX speed grades—transmitter power (right side) | 1.00/1.12              | 1.1/1.13                | 1.14/1.10              | v    |

| V <sub>CCT_GXBL</sub> | GT and ST speed grades—transmitter power (left side)  | 1.17                   | 1.20                    | 1.23                   | V    |

| V <sub>CCT_GXBR</sub> | GT and ST speed grades—transmitter power (right side) | 1.17                   | 1.20                    | 1.23                   | v    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power (left side)           | 1.425                  | 1.500                   | 1.575                  | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power (right side)          | 1.423                  | 1.300                   | 1.373                  | v    |

<sup>(5)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(6)</sup> For data rate <=3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub>, V<sub>CCT\_GXBL/R</sub>, or V<sub>CCL\_GXBL/R</sub> to either 1.1-V or 1.15-V power supply. For data rate >3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub>, V<sub>CCT\_GXBL/R</sub>, or V<sub>CCL\_GXBL/R</sub> to a 1.15-V power supply. For details, refer to the Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines.

| Symbol                    | Description                                  | Maximum | Unit |

|---------------------------|----------------------------------------------|---------|------|

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver (RX) pin | 50      | mA   |

#### Internal Weak Pull-Up Resistor

All I/O pins, except configuration, test, and JTAG pins, have an option to enable weak pull-up.

#### Table 1-13: Internal Weak Pull-Up Resistor Values for Arria V Devices

| Symbol | Description                                                                                                                                                     | Condition (V) <sup>(11)</sup> | Value <sup>(12)</sup>    | Unit |    |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------|------|----|

|        |                                                                                                                                                                 | $V_{CCIO} = 3.3 \pm 5\%$      | 25                       | kΩ   |    |

|        | Value of the I/O pin pull-up resistor before and during<br>configuration, as well as user mode if you have enabled the<br>programmable pull-up resistor option. | $V_{CCIO} = 3.0 \pm 5\%$      | 25                       | kΩ   |    |

|        |                                                                                                                                                                 | $V_{CCIO} = 2.5 \pm 5\%$      | 25                       | kΩ   |    |

| D      |                                                                                                                                                                 | $V_{CCIO} = 1.8 \pm 5\%$      | 25                       | kΩ   |    |

| Кру    |                                                                                                                                                                 |                               | $V_{CCIO} = 1.5 \pm 5\%$ | 25   | kΩ |

|        |                                                                                                                                                                 | $V_{CCIO} = 1.35 \pm 5\%$     | 25                       | kΩ   |    |

|        |                                                                                                                                                                 | $V_{CCIO} = 1.25 \pm 5\%$     | 25                       | kΩ   |    |

|        |                                                                                                                                                                 | $V_{CCIO} = 1.2 \pm 5\%$      | 25                       | kΩ   |    |

#### **Related Information**

#### Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

<sup>(10)</sup> The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

$<sup>^{(11)}</sup>$  Pin pull-up resistance values may be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

<sup>&</sup>lt;sup>(12)</sup> Valid with  $\pm 10\%$  tolerances to cover changes over PVT.

| Symbol/Description                                                          | Condition                                                   | Tran | sceiver Speed Gra | Unit |    |

|-----------------------------------------------------------------------------|-------------------------------------------------------------|------|-------------------|------|----|

| Symbol/Description                                                          | Condition                                                   |      | Ont               |      |    |

|                                                                             | 85-Ω setting                                                | —    | 85                | —    | Ω  |

| Differential on-chip termination                                            | 100- $\Omega$ setting                                       |      | 100               |      | Ω  |

| resistors                                                                   | 120-Ω setting                                               | —    | 120               |      | Ω  |

|                                                                             | 150-Ω setting                                               |      | 150               |      | Ω  |

| Intra-differential pair skew                                                | TX $V_{CM}$ = 0.65 V (AC coupled)<br>and slew rate of 15 ps |      |                   | 15   | ps |

| Intra-transceiver block transmitter channel-to-channel skew                 | ×6 PMA bonded mode                                          |      |                   | 180  | ps |

| Inter-transceiver block transmitter channel-to-channel skew <sup>(55)</sup> | × <i>N</i> PMA bonded mode                                  |      |                   | 500  | ps |

### Table 1-30: CMU PLL Specifications for Arria V GT and ST Devices

| Symbol/Description        | Transceiver S | peed Grade 3 | Unit |

|---------------------------|---------------|--------------|------|

| Symbol/Description        | Min           | Max          | Onit |

| Supported data range      | 0.611         | 10.3125      | Gbps |

| fPLL supported data range | 611           | 3125         | Mbps |

<sup>(55)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

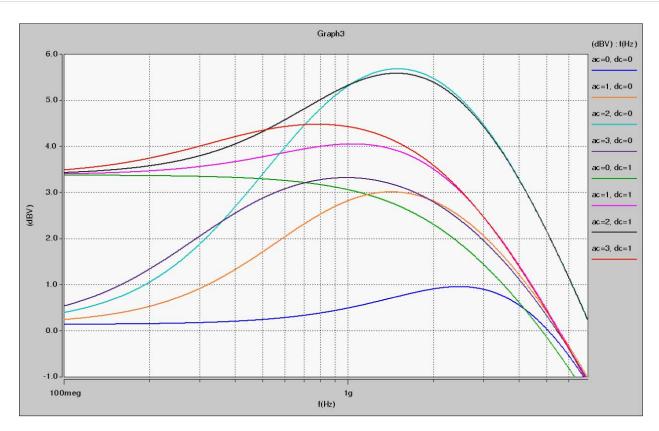

## CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain

#### Figure 1-3: CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

### Typical TX V<sub>OD</sub> Setting for Arria V Transceiver Channels with termination of 100 $\Omega$

| Table 1-32: Typical TX Vor | Setting for Arria V Transceive | r Channels with termination of 100 $\Omega$ |

|----------------------------|--------------------------------|---------------------------------------------|

|                            | , setting to suma t manseerre  |                                             |

| Symbol                                               | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|------------------------------------------------------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|                                                      | 6 <sup>(59)</sup>                       | 120                        | 34                                      | 680                        |

|                                                      | 7 <sup>(59)</sup>                       | 140                        | 35                                      | 700                        |

|                                                      | 8(59)                                   | 160                        | 36                                      | 720                        |

|                                                      | 9                                       | 180                        | 37                                      | 740                        |

|                                                      | 10                                      | 200                        | 38                                      | 760                        |

|                                                      | 11                                      | 220                        | 39                                      | 780                        |

|                                                      | 12                                      | 240                        | 40                                      | 800                        |

|                                                      | 13                                      | 260                        | 41                                      | 820                        |

|                                                      | 14                                      | 280                        | 42                                      | 840                        |

| V <sub>OD</sub> differential peak-to-peak<br>typical | 15                                      | 300                        | 43                                      | 860                        |

| typical                                              | 16                                      | 320                        | 44                                      | 880                        |

|                                                      | 17                                      | 340                        | 45                                      | 900                        |

|                                                      | 18                                      | 360                        | 46                                      | 920                        |

|                                                      | 19                                      | 380                        | 47                                      | 940                        |

|                                                      | 20                                      | 400                        | 48                                      | 960                        |

|                                                      | 21                                      | 420                        | 49                                      | 980                        |

|                                                      | 22                                      | 440                        | 50                                      | 1000                       |

|                                                      | 23                                      | 460                        | 51                                      | 1020                       |

|                                                      | 24                                      | 480                        | 52                                      | 1040                       |

<sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

<sup>(59)</sup> Only valid for data rates  $\leq$  5 Gbps.

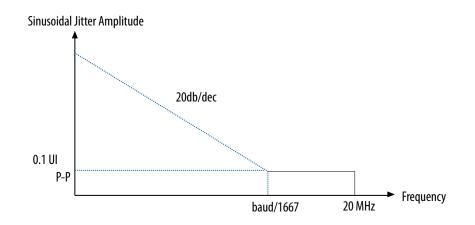

### Table 1-34: Transceiver Compliance Specification for All Supported Protocol for Arria V GX, GT, SX, and ST Devices

| Protocol                                     | Sub-protocol | Data Rate (Mbps) |

|----------------------------------------------|--------------|------------------|

|                                              | PCIe Gen1    | 2,500            |

| PCIe                                         | PCIe Gen2    | 5,000            |

|                                              | PCIe Cable   | 2,500            |

| XAUI                                         | XAUI 2135    | 3,125            |

|                                              | SRIO 1250 SR | 1,250            |

|                                              | SRIO 1250 LR | 1,250            |

| XAUI XAUI Serial RapidIO <sup>®</sup> (SRIO) | SRIO 2500 SR | 2,500            |

|                                              | SRIO 2500 LR | 2,500            |

|                                              | SRIO 3125 SR | 3,125            |

|                                              | SRIO 3125 LR | 3,125            |

| Serial Rapidio (SRIO)                        | SRIO 5000 SR | 5,000            |

|                                              | SRIO 5000 MR | 5,000            |

|                                              | SRIO 5000 LR | 5,000            |

|                                              | SRIO_6250_SR | 6,250            |

|                                              | SRIO_6250_MR | 6,250            |

|                                              | SRIO_6250_LR | 6,250            |

AV-51002 2017.02.10

| Symbol                                                                                                                                       | Condition                                                           |      | –I3, –C4 |      |      | -l5, -C5 |      |      | -C6 |      | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|----------|------|------|----------|------|------|-----|------|------|

| Symbol                                                                                                                                       | Condition                                                           | Min  | Тур      | Max  | Min  | Тур      | Max  | Min  | Тур | Max  | Unit |

|                                                                                                                                              | SERDES factor J ≥<br>8 <sup>(76)(78)</sup> , LVDS TX with<br>RX DPA | (77) |          | 1600 | (77) |          | 1500 | (77) | _   | 1250 | Mbps |

|                                                                                                                                              | SERDES factor J = 1<br>to 2, Uses DDR<br>Registers                  | (77) |          | (79) | (77) |          | (79) | (77) | _   | (79) | Mbps |

| Emulated Differential I/<br>O Standards with Three<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup> | SERDES factor $J = 4$<br>to $10^{(81)}$                             | (77) |          | 945  | (77) |          | 945  | (77) |     | 945  | Mbps |

| Emulated Differential I/<br>O Standards with One<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup>   | SERDES factor $J = 4$<br>to $10^{(81)}$                             | (77) |          | 200  | (77) |          | 200  | (77) |     | 200  | Mbps |

| t <sub>x Jitter</sub> -True Differential<br>I/O Standards                                                                                    | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps               |      |          | 160  |      |          | 160  |      | _   | 160  | ps   |

|                                                                                                                                              | Total Jitter for Data<br>Rate < 600 Mbps                            |      |          | 0.1  | _    | _        | 0.1  | —    | _   | 0.1  | UI   |

$<sup>^{(78)}</sup>$  The V<sub>CC</sub> and V<sub>CCP</sub> must be on a separate power layer and a maximum load of 5 pF for chip-to-chip interface.

<sup>&</sup>lt;sup>(79)</sup> The maximum ideal data rate is the SERDES factor (J) x the PLL maximum output frequency (f<sub>OUT</sub>), provided you can close the design timing and the signal integrity simulation is clean.

<sup>&</sup>lt;sup>(80)</sup> You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine the leftover timing margin.

<sup>&</sup>lt;sup>(81)</sup> When using True LVDS RX channels for emulated LVDS TX channel, only serialization factors 1 and 2 are supported.

| Symbol                                                                                                           | Condition                                                                                    |     | -I3, -C4 |      | –I5, –C5 |     |      | -C6 |     |      | Unit |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|----------|------|----------|-----|------|-----|-----|------|------|

| Symbol                                                                                                           | Condition                                                                                    | Min | Тур      | Max  | Min      | Тур | Мах  | Min | Тур | Max  | Unit |

| t <sub>x Jitter</sub> -Emulated<br>Differential I/O<br>Standards with Three                                      | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps                                        | _   | -        | 260  |          | _   | 300  | _   | _   | 350  | ps   |

| External Output Resistor<br>Network                                                                              | Total Jitter for Data<br>Rate < 600 Mbps                                                     | —   | _        | 0.16 |          | _   | 0.18 | _   |     | 0.21 | UI   |

| t <sub>x Jitter</sub> -Emulated<br>Differential I/O<br>Standards with One<br>External Output<br>Resistor Network | _                                                                                            |     |          | 0.15 |          |     | 0.15 |     |     | 0.15 | UI   |

| t <sub>DUTY</sub>                                                                                                | TX output clock duty<br>cycle for both True<br>and Emulated<br>Differential I/O<br>Standards | 45  | 50       | 55   | 45       | 50  | 55   | 45  | 50  | 55   | %    |

|                                                                                                                  | True Differential I/O<br>Standards <sup>(82)</sup>                                           | _   | _        | 160  |          |     | 180  | _   |     | 200  | ps   |

| t <sub>RISE</sub> and t <sub>FALL</sub>                                                                          | Emulated Differential<br>I/O Standards with<br>Three External Output<br>Resistor Network     | _   | _        | 250  |          |     | 250  |     |     | 300  | ps   |

|                                                                                                                  | Emulated Differential<br>I/O Standards with<br>One External Output<br>Resistor Network       |     |          | 500  |          | _   | 500  |     |     | 500  | ps   |

$<sup>^{(82)}\,</sup>$  This applies to default pre-emphasis and  $V_{OD}$  settings only.

### **DLL Frequency Range Specifications**

#### Table 1-43: DLL Frequency Range Specifications for Arria V Devices

| Parameter                     | -I3, -C4  | -I5, -C5  | -C6       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 200 - 667 | 200 - 667 | 200 - 667 | MHz  |

# DQS Logic Block Specifications

#### Table 1-44: DQS Phase Shift Error Specifications for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Arria V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -I3, -C4 | –I5, –C5 | -C6 | Unit |

|----------------------------|----------|----------|-----|------|

| 2                          | 40       | 80       | 80  | ps   |

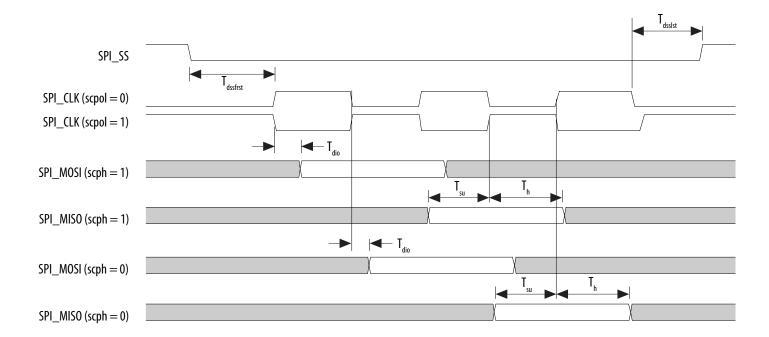

#### Figure 1-9: SPI Master Timing Diagram

#### Table 1-53: SPI Slave Timing Requirements for Arria V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol            | Description                                     | Min | Max | Unit |

|-------------------|-------------------------------------------------|-----|-----|------|

| T <sub>clk</sub>  | CLK clock period                                | 20  |     | ns   |

| T <sub>s</sub>    | MOSI Setup time                                 | 5   |     | ns   |

| T <sub>h</sub>    | MOSI Hold time                                  | 5   |     | ns   |

| T <sub>suss</sub> | Setup time SPI_SS valid before first clock edge | 8   |     | ns   |

| T <sub>hss</sub>  | Hold time SPI_SS valid after last clock edge    | 8   |     | ns   |

| T <sub>d</sub>    | MISO output delay                               |     | 6   | ns   |

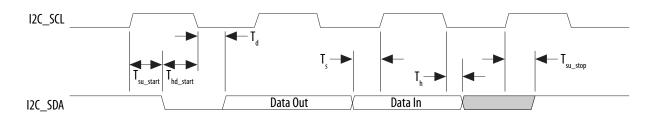

#### Figure 1-16: I<sup>2</sup>C Timing Diagram

#### **NAND Timing Characteristics**

#### Table 1-60: NAND ONFI 1.0 Timing Requirements for Arria V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the c4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                             | Description                                     | Min | Max | Unit |

|------------------------------------|-------------------------------------------------|-----|-----|------|

| T <sub>wp</sub> <sup>(89)</sup>    | Write enable pulse width                        | 10  | _   | ns   |

| T <sub>wh</sub> <sup>(89)</sup>    | Write enable hold time                          | 7   |     | ns   |

| T <sub>rp</sub> <sup>(89)</sup>    | Read enable pulse width                         | 10  |     | ns   |

| T <sub>reh</sub> <sup>(89)</sup>   | Read enable hold time                           | 7   |     | ns   |

| T <sub>clesu</sub> <sup>(89)</sup> | Command latch enable to write enable setup time | 10  |     | ns   |

| T <sub>cleh</sub> <sup>(89)</sup>  | Command latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>cesu</sub> <sup>(89)</sup>  | Chip enable to write enable setup time          | 15  |     | ns   |

| T <sub>ceh</sub> <sup>(89)</sup>   | Chip enable to write enable hold time           | 5   |     | ns   |

| T <sub>alesu</sub> <sup>(89)</sup> | Address latch enable to write enable setup time | 10  |     | ns   |

| T <sub>aleh</sub> <sup>(89)</sup>  | Address latch enable to write enable hold time  | 5   |     | ns   |

| T <sub>dsu</sub> <sup>(89)</sup>   | Data to write enable setup time                 | 10  |     | ns   |

<sup>(89)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

#### **HPS JTAG Timing Specifications**

| Symbol                  | Description                              | Min | Мах                | Unit |

|-------------------------|------------------------------------------|-----|--------------------|------|

| t <sub>JCP</sub>        | TCK clock period                         | 30  |                    | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14  |                    | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14  |                    | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2   |                    | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3   |                    | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5   |                    | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |     | 12 <sup>(90)</sup> | ns   |

| t <sub>JPZX</sub>       | JTAG port high impedance to valid output |     | 14 <sup>(90)</sup> | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | _   | 14 <sup>(90)</sup> | ns   |

### Table 1-62: HPS JTAG Timing Parameters and Values for Arria V Devices

# **Configuration Specifications**

This section provides configuration specifications and timing for Arria V devices.

# **POR Specifications**

#### Table 1-63: Fast and Standard POR Delay Specification for Arria V Devices

| POR Delay | Minimum | Maximum            | Unit |

|-----------|---------|--------------------|------|

| Fast      | 4       | 12 <sup>(91)</sup> | ms   |

<sup>&</sup>lt;sup>(90)</sup> A 1-ns adder is required for each  $V_{CCIO\_HPS}$  voltage step down from 3.0 V. For example,  $t_{JPCO}$ = 13 ns if  $V_{CCIO\_HPS}$  of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

<sup>&</sup>lt;sup>(91)</sup> The maximum pulse width of the fast POR delay is 12 ms, providing enough time for the PCIe hard IP to initialize after the POR trip.

# **Remote System Upgrades**

#### Table 1-74: Remote System Upgrade Circuitry Timing Specifications for Arria V Devices

| Parameter                                 | Minimum | Unit |  |  |

|-------------------------------------------|---------|------|--|--|

| t <sub>RU_nCONFIG</sub> <sup>(110)</sup>  | 250     | ns   |  |  |

| t <sub>RU_nRSTIMER</sub> <sup>(111)</sup> | 250     | ns   |  |  |

#### **Related Information**

- **Remote System Upgrade State Machine** Provides more information about configuration reset (RU\_CONFIG) signal.

- User Watchdog Timer Provides more information about reset\_timer (RU\_nRSTIMER) signal.

# User Watchdog Internal Oscillator Frequency Specifications

#### Table 1-75: User Watchdog Internal Oscillator Frequency Specifications for Arria V Devices

| Parameter                                   | Minimum | Typical | Maximum | Unit |

|---------------------------------------------|---------|---------|---------|------|

| User watchdog internal oscillator frequency | 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O timing and the Quartus Prime Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

<sup>&</sup>lt;sup>(110)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification.

<sup>&</sup>lt;sup>(111)</sup> This is equivalent to strobing the reset timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification.

| Symbol | Description                                             | V <sub>CCIO</sub> (V) | Typical | Unit |

|--------|---------------------------------------------------------|-----------------------|---------|------|

|        |                                                         | 3.0                   | 0.0297  |      |

|        |                                                         | 2.5                   | 0.0344  |      |

| dR/dV  | dR/dV OCT variation with voltage without re-calibration | 1.8                   | 0.0499  | %/mV |

|        |                                                         | 1.5                   | 0.0744  |      |

|        |                                                         | 1.2                   | 0.1241  |      |

|        |                                                         | 3.0                   | 0.189   |      |

|        |                                                         | 2.5                   | 0.208   |      |

| dR/dT  | OCT variation with temperature without re-calibration   | 1.8                   | 0.266   | %/°C |

|        |                                                         | 1.5                   | 0.273   |      |

|        |                                                         | 1.2                   | 0.317   |      |

# Pin Capacitance

# Table 2-13: Pin Capacitance for Arria V GZ Devices

| Symbol             | Description                                                      | Maximum | Unit |

|--------------------|------------------------------------------------------------------|---------|------|

| C <sub>IOTB</sub>  | Input capacitance on the top and bottom I/O pins                 | 6       | pF   |

| C <sub>IOLR</sub>  | Input capacitance on the left and right I/O pins                 | 6       | pF   |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output and feedback pins | 6       | pF   |

# **Switching Characteristics**

# **Transceiver Performance Specifications**

### **Reference Clock**

#### Table 2-22: Reference Clock Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                               | Conditions                                                                      | Transceiver Speed Grade 2 |     | Transceiver Speed Grade 3 |     |     | Unit |      |

|------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------|-----|---------------------------|-----|-----|------|------|

| Symbol/Description                                               | Conditions                                                                      | Min                       | Тур | Max                       | Min | Тур | Max  | Onit |

| Reference Clock                                                  | Reference Clock                                                                 |                           |     |                           |     |     |      |      |

| Supported I/O Standards                                          | Dedicated reference clock pin                                                   |                           |     |                           |     |     |      |      |

|                                                                  | RX reference clock pin     1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |                           |     |                           |     | 'DS |      |      |

| Input Reference Clock<br>Frequency<br>(CMU PLL) <sup>(137)</sup> | _                                                                               | 40                        | _   | 710                       | 40  | _   | 710  | MHz  |

| Input Reference Clock<br>Frequency<br>(ATX PLL) <sup>(137)</sup> | _                                                                               | 100                       | _   | 710                       | 100 | _   | 710  | MHz  |

<sup>(137)</sup> The input reference clock frequency options depend on the data rate and the device speed grade.

#### Table 2-26: CMU PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the Arria V Device Overview.

| Symbol/Description                          | Conditions | Transceiver Speed Grade 2 |     |       | Transc | - Unit |         |      |

|---------------------------------------------|------------|---------------------------|-----|-------|--------|--------|---------|------|

| Symbol/Description                          |            | Min                       | Тур | Max   | Min    | Тур    | Мах     | Onic |

| Supported data range                        | —          | 600                       | _   | 12500 | 600    | _      | 10312.5 | Mbps |

| t <sub>pll_powerdown</sub> <sup>(153)</sup> | _          | 1                         | _   |       | 1      | _      |         | μs   |

| t <sub>pll_lock</sub> <sup>(154)</sup>      | _          |                           | —   | 10    | _      |        | 10      | μs   |

#### **Related Information**

#### Arria V Device Overview

For more information about device ordering codes.

### ATX PLL

#### Table 2-27: ATX PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the Arria V Device Overview.

Arria V GZ Device Datasheet

$t_{pll\_powerdown}$  is the PLL powerdown minimum pulse width. (153)

<sup>(154)</sup>  $t_{\text{pll} \text{ lock}}$  is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

#### Table 2-52: Worst-Case DCD on Arria V GZ I/O Pins

The DCD numbers do not cover the core clock network.

| Symbol            | C3, I3L |     | C4, I4 |     | Unit |

|-------------------|---------|-----|--------|-----|------|

|                   | Min     | Мах | Min    | Мах | Onit |

| Output Duty Cycle | 45      | 55  | 45     | 55  | %    |

# **Configuration Specification**

# **POR Specifications**

#### Table 2-53: Fast and Standard POR Delay Specification for Arria V GZ Devices

Select the POR delay based on the MSEL setting as described in the "Configuration Schemes for Arria V Devices" table in the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

| POR Delay | Minimum (ms) | Maximum (ms) |  |

|-----------|--------------|--------------|--|

| Fast      | 4            | 12 (202)     |  |

| Standard  | 100          | 300          |  |

**Related Information**

Configuration, Design Security, and Remote System Upgrades in Arria V Devices

<sup>&</sup>lt;sup>(202)</sup> The maximum pulse width of the fast POR delay is 12 ms, providing enough time for the PCIe hard IP to initialize after the POR trip.

#### **Related Information**

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices For more information about the reconfiguration input for the ALTREMOTE\_UPDATE IP core, refer to the "User Watchdog Timer" section.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices For more information about the reset\_timer input for the ALTREMOTE\_UPDATE IP core, refer to the "Remote System Upgrade State Machine" section.

# User Watchdog Internal Oscillator Frequency Specification

#### Table 2-65: User Watchdog Internal Oscillator Frequency Specifications

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O Timing and the Quartus II Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Quartus II Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete placeand-route.

#### **Related Information**

# **Arria V Devices Documentation page**

For the Excel-based I/O Timing spreadsheet

#### Arria V GZ Device Datasheet

<sup>&</sup>lt;sup>(226)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "Remote System Upgrade State Machine" section in the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

<sup>&</sup>lt;sup>(227)</sup> This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "User Watchdog Timer" section in the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

| Term                               | Definition                                                                                                                                                                                                                                                                 |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>C</sub>                     | High-speed receiver and transmitter input and output clock period.                                                                                                                                                                                                         |

| TCCS (channel-to-<br>channel-skew) | The timing difference between the fastest and slowest output edges, including t <sub>CO</sub> variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table). |

| t <sub>DUTY</sub>                  | High-speed I/O block—Duty cycle on the high-speed transmitter output clock.                                                                                                                                                                                                |

| t <sub>FALL</sub>                  | Signal high-to-low transition time (80-20%)                                                                                                                                                                                                                                |

| t <sub>INCCJ</sub>                 | Cycle-to-cycle jitter tolerance on the PLL clock input.                                                                                                                                                                                                                    |

| t <sub>OUTPJ_IO</sub>              | Period jitter on the general purpose I/O driven by a PLL.                                                                                                                                                                                                                  |

| t <sub>OUTPJ_DC</sub>              | Period jitter on the dedicated clock output driven by a PLL.                                                                                                                                                                                                               |

| t <sub>RISE</sub>                  | Signal low-to-high transition time (20-80%)                                                                                                                                                                                                                                |

| Timing Unit Interval<br>(TUI)      | The timing budget allowed for skew, propagation delays, and the data sampling window.<br>(TUI = $1/(\text{receiver input clock frequency multiplication factor}) = t_C/w)$                                                                                                 |

| V <sub>CM(DC)</sub>                | DC common mode input voltage.                                                                                                                                                                                                                                              |

| V <sub>ICM</sub>                   | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                                                                                                                      |

| V <sub>ID</sub>                    | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                                                                                               |

| V <sub>DIF(AC)</sub>               | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                                                                                                                                |

| V <sub>DIF(DC)</sub>               | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                                                                                                                               |

| V <sub>IH</sub>                    | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                                                                                                                      |

| V <sub>IH(AC)</sub>                | High-level AC input voltage                                                                                                                                                                                                                                                |

| V <sub>IH(DC)</sub>                | High-level DC input voltage                                                                                                                                                                                                                                                |

| V <sub>IL</sub>                    | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                                                                                                                        |

| V <sub>IL(AC)</sub>                | Low-level AC input voltage                                                                                                                                                                                                                                                 |

| V <sub>IL(DC)</sub>                | Low-level DC input voltage                                                                                                                                                                                                                                                 |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.8     | <ul> <li>Updated Table 21.</li> <li>Updated Table 22 V<sub>OCM</sub> (DC Coupled) condition.</li> <li>Updated the DCLK note to Figure 6, Figure 7, and Figure 9.</li> <li>Added note to Table 5 and Table 6.</li> <li>Added the DCLK specification to Table 50.</li> <li>Added note to Table 51.</li> <li>Updated the list of parameters in Table 53.</li> </ul> |

| February 2014 | 3.7     | Updated Table 28.                                                                                                                                                                                                                                                                                                                                                |

| December 2013 | 3.6     | <ul> <li>Updated Table 2, Table 13, Table 18, Table 19, Table 22, Table 30, Table 33, Table 37, Table 38, Table 45, Table 46, Table 47, Table 56, Table 49.</li> <li>Updated "PLL Specifications".</li> </ul>                                                                                                                                                    |

| August 2013   | 3.5     | Updated Table 28.                                                                                                                                                                                                                                                                                                                                                |

| August 2013   | 3.4     | <ul> <li>Removed Preliminary tags for Table 2, Table 4, Table 5, Table 14, Table 27, Table 28, Table 29, Table 31, Table 32, Table 43, Table 45, Table 46, Table 47, Table 48, Table 49, Table 50, and Table 54.</li> <li>Updated Table 2 and Table 28.</li> </ul>                                                                                               |

| June 2013     | 3.3     | Updated Table 23, Table 28, Table 51, and Table 55.                                                                                                                                                                                                                                                                                                              |

| May 2013      | 3.2     | <ul> <li>Added Table 23.</li> <li>Updated Table 5, Table 22, Table 26, and Table 57.</li> <li>Updated Figure 6, Figure 7, Figure 8, and Figure 9.</li> </ul>                                                                                                                                                                                                     |

| March 2013    | 3.1     | <ul> <li>Updated Table 2, Table 6, Table 7, Table 8, Table 19, Table 22, Table 26, Table 29, Table 52.</li> <li>Updated "Maximum Allowed Overshoot and Undershoot Voltage".</li> </ul>                                                                                                                                                                           |

| December 2012 | 3.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                 |