Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Product Status                 | Obsolete                                                   |

|--------------------------------|------------------------------------------------------------|

| Number of LABs/CLBs            | 11460                                                      |

| Number of Logic Elements/Cells | 242000                                                     |

| Total RAM Bits                 | 15470592                                                   |

| Number of I/O                  | 384                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.12V ~ 1.18V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 896-BBGA, FCBGA                                            |

| Supplier Device Package        | 896-FBGA (31x31)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxma7g4f31i3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### I/O Pin Leakage Current

## Table 1-6: I/O Pin Leakage Current for Arria V Devices

| Symbol          | Description        | Condition                      | Min | Тур | Max | Unit |

|-----------------|--------------------|--------------------------------|-----|-----|-----|------|

| II              | Input pin          | $V_{I} = 0 V$ to $V_{CCIOMAX}$ | -30 | —   | 30  | μΑ   |

| I <sub>OZ</sub> | Tri-stated I/O pin | $V_{O} = 0 V$ to $V_{CCIOMAX}$ | -30 |     | 30  | μΑ   |

## **Bus Hold Specifications**

#### Table 1-7: Bus Hold Parameters for Arria V Devices

The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

|                                             |                   |                                                             |     | V <sub>CCIO</sub> (V) |     |      |     |      |     |      |     |      |     |      |      |

|---------------------------------------------|-------------------|-------------------------------------------------------------|-----|-----------------------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                   | Symbol            | Condition                                                   | 1   | .2                    | 1   | .5   | 1   | .8   | 2   | .5   | 3   | .0   | 3.  | .3   | Unit |

|                                             |                   |                                                             | Min | Max                   | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus-hold,<br>low,<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub><br>(max)                  | 8   |                       | 12  |      | 30  |      | 50  |      | 70  |      | 70  | _    | μΑ   |

| Bus-hold,<br>high,<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(min)                  | -8  |                       | -12 |      | -30 |      | -50 |      | -70 |      | -70 | _    | μΑ   |

| Bus-hold,<br>low,<br>overdrive<br>current   | I <sub>ODL</sub>  | $\begin{array}{c} 0 \ V < V_{IN} \\ < V_{CCIO} \end{array}$ | _   | 125                   |     | 175  | _   | 200  |     | 300  | _   | 500  |     | 500  | μΑ   |

| Bus-hold,<br>high,<br>overdrive<br>current  | I <sub>ODH</sub>  | 0 V <v<sub>IN<br/><v<sub>CCIO</v<sub></v<sub>               | _   | -125                  |     | -175 |     | -200 | _   | -300 |     | -500 |     | -500 | μΑ   |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

## Table 1-31: Transceiver-FPGA Fabric Interface Specifications for Arria V GT and ST Devices

| Symbol/Description                  | Transceiver S | peed Grade 3                                | Unit |  |

|-------------------------------------|---------------|---------------------------------------------|------|--|

| Symbol/Description                  | Min           | Мах                                         | Unit |  |

| Interface speed (PMA direct mode)   | 50            | 153.6 <sup>(56)</sup> , 161 <sup>(57)</sup> | MHz  |  |

| Interface speed (single-width mode) | 25            | 187.5                                       | MHz  |  |

| Interface speed (double-width mode) | 25            | 163.84                                      | MHz  |  |

**Related Information**

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 1-35

- CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain on page 1-36

<sup>&</sup>lt;sup>(56)</sup> The maximum frequency when core transceiver local routing is selected.

<sup>&</sup>lt;sup>(57)</sup> The maximum frequency when core transceiver network routing (GCLK, RCLK, or PCLK) is selected.

| Symbol | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|--------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|        | 25                                      | 500                        | 53                                      | 1060                       |

|        | 26                                      | 520                        | 54                                      | 1080                       |

|        | 27                                      | 540                        | 55                                      | 1100                       |

|        | 28                                      | 560                        | 56                                      | 1120                       |

|        | 29                                      | 580                        | 57                                      | 1140                       |

|        | 30                                      | 600                        | 58                                      | 1160                       |

|        | 31                                      | 620                        | 59                                      | 1180                       |

|        | 32                                      | 640                        | 60                                      | 1200                       |

|        | 33                                      | 660                        |                                         |                            |

## **Transmitter Pre-Emphasis Levels**

The following table lists the simulation data on the transmitter pre-emphasis levels in dB for the first post tap under the following conditions:

- Low-frequency data pattern—five 1s and five 0s

- Data rate—2.5 Gbps

The levels listed are a representation of possible pre-emphasis levels under the specified conditions only and the pre-emphasis levels may change with data pattern and data rate.

Arria V devices only support 1st post tap pre-emphasis with the following conditions:

- The 1st post tap pre-emphasis settings must satisfy  $|B| + |C| \le 60$  where  $|B| = V_{OD}$  setting with termination value,  $R_{TERM} = 100 \Omega$  and |C| = 1st post tap pre-emphasis setting.

- |B| |C| > 5 for data rates < 5 Gbps and |B| |C| > 8.25 for data rates > 5 Gbps.

- $(V_{MAX}/V_{MIN} 1)\% < 600\%$ , where  $V_{MAX} = |B| + |C|$  and  $V_{MIN} = |B| |C|$ .

Exception for PCIe Gen2 design:  $V_{OD}$  setting = 43 and pre-emphasis setting = 19 are allowed for PCIe Gen2 design with transmit de-emphasis – 6dB setting (pipe\_txdeemp = 1'b0) using Altera PCIe Hard IP and PIPE IP cores.

<sup>&</sup>lt;sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

For example, when  $V_{OD}$  = 800 mV, the corresponding  $V_{OD}$  value setting is 40. The following conditions show that the 1st post tap pre-emphasis setting = 2 is valid:

- $|B| + |C| \le 60 \Rightarrow 40 + 2 = 42$ ٠

- $|B| |C| > 5 \rightarrow 40 2 = 38$

- $(V_{MAX}/V_{MIN} 1)\% < 600\% \Rightarrow (42/38 1)\% = 10.52\%$

To predict the pre-emphasis level for your specific data rate and pattern, run simulations using the Arria V HSSI HSPICE models.

## Table 1-33: Transmitter Pre-Emphasis Levels for Arria V Devices

| Quartus Prime 1st                 |             |             | Quar        | tus Prime V <sub>OD</sub> Se | etting      |             |              |      |

|-----------------------------------|-------------|-------------|-------------|------------------------------|-------------|-------------|--------------|------|

| Post Tap Pre-<br>Emphasis Setting | 10 (200 mV) | 20 (400 mV) | 30 (600 mV) | 35 (700 mV)                  | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) | Unit |

| 0                                 | 0           | 0           | 0           | 0                            | 0           | 0           | 0            | dB   |

| 1                                 | 1.97        | 0.88        | 0.43        | 0.32                         | 0.24        | 0.19        | 0.13         | dB   |

| 2                                 | 3.58        | 1.67        | 0.95        | 0.76                         | 0.61        | 0.5         | 0.41         | dB   |

| 3                                 | 5.35        | 2.48        | 1.49        | 1.2                          | 1           | 0.83        | 0.69         | dB   |

| 4                                 | 7.27        | 3.31        | 2           | 1.63                         | 1.36        | 1.14        | 0.96         | dB   |

| 5                                 | _           | 4.19        | 2.55        | 2.1                          | 1.76        | 1.49        | 1.26         | dB   |

| 6                                 | _           | 5.08        | 3.11        | 2.56                         | 2.17        | 1.83        | 1.56         | dB   |

| 7                                 | _           | 5.99        | 3.71        | 3.06                         | 2.58        | 2.18        | 1.87         | dB   |

| 8                                 | _           | 6.92        | 4.22        | 3.47                         | 2.93        | 2.48        | 2.11         | dB   |

| 9                                 | _           | 7.92        | 4.86        | 4                            | 3.38        | 2.87        | 2.46         | dB   |

| 10                                | _           | 9.04        | 5.46        | 4.51                         | 3.79        | 3.23        | 2.77         | dB   |

| 11                                | _           | 10.2        | 6.09        | 5.01                         | 4.23        | 3.61        | —            | dB   |

| 12                                | _           | 11.56       | 6.74        | 5.51                         | 4.68        | 3.97        | —            | dB   |

| 13                                | _           | 12.9        | 7.44        | 6.1                          | 5.12        | 4.36        | —            | dB   |

| 14                                | _           | 14.44       | 8.12        | 6.64                         | 5.57        | 4.76        | _            | dB   |

| 15                                | _           | _           | 8.87        | 7.21                         | 6.06        | 5.14        | —            | dB   |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

#### 1-40 Transceiver Compliance Specification

| Quartus Prime 1st                 |             |             | Quar        | tus Prime V <sub>OD</sub> Se | etting      |             |              |      |

|-----------------------------------|-------------|-------------|-------------|------------------------------|-------------|-------------|--------------|------|

| Post Tap Pre-<br>Emphasis Setting | 10 (200 mV) | 20 (400 mV) | 30 (600 mV) | 35 (700 mV)                  | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) | Unit |

| 16                                | _           | _           | 9.56        | 7.73                         | 6.49        |             | _            | dB   |

| 17                                | _           | _           | 10.43       | 8.39                         | 7.02        |             | _            | dB   |

| 18                                | _           |             | 11.23       | 9.03                         | 7.52        |             | _            | dB   |

| 19                                | _           |             | 12.18       | 9.7                          | 8.02        |             | _            | dB   |

| 20                                | _           | _           | 13.17       | 10.34                        | 8.59        | _           | _            | dB   |

| 21                                | _           | _           | 14.2        | 11.1                         | —           | _           | _            | dB   |

| 22                                | _           |             | 15.38       | 11.87                        |             |             | _            | dB   |

| 23                                | _           | _           | —           | 12.67                        | —           |             | _            | dB   |

| 24                                | _           |             |             | 13.48                        | _           |             | _            | dB   |

| 25                                | _           |             |             | 14.37                        | —           |             | _            | dB   |

| 26                                | _           | _           | _           | _                            | _           | _           | _            | dB   |

| 27                                | _           |             |             |                              | _           |             | _            | dB   |

| 28                                |             |             |             |                              |             |             | _            | dB   |

| 29                                | _           |             |             |                              | —           |             | _            | dB   |

| 30                                | _           |             |             |                              | _           |             | _            | dB   |

| 31                                |             |             |             |                              |             |             | —            | dB   |

#### **Related Information**

### SPICE Models for Altera Devices

Provides the Arria V HSSI HSPICE models.

## **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Arria V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Altera Sales Representative.

## Table 1-34: Transceiver Compliance Specification for All Supported Protocol for Arria V GX, GT, SX, and ST Devices

| Protocol                           | Sub-protocol | Data Rate (Mbps) |

|------------------------------------|--------------|------------------|

|                                    | PCIe Gen1    | 2,500            |

| PCIe                               | PCIe Gen2    | 5,000            |

|                                    | PCIe Cable   | 2,500            |

| XAUI                               | XAUI 2135    | 3,125            |

|                                    | SRIO 1250 SR | 1,250            |

|                                    | SRIO 1250 LR | 1,250            |

|                                    | SRIO 2500 SR | 2,500            |

|                                    | SRIO 2500 LR | 2,500            |

|                                    | SRIO 3125 SR | 3,125            |

| Serial RapidIO <sup>®</sup> (SRIO) | SRIO 3125 LR | 3,125            |

| Serial Rapidio (SRIO)              | SRIO 5000 SR | 5,000            |

|                                    | SRIO 5000 MR | 5,000            |

|                                    | SRIO 5000 LR | 5,000            |

|                                    | SRIO_6250_SR | 6,250            |

|                                    | SRIO_6250_MR | 6,250            |

|                                    | SRIO_6250_LR | 6,250            |

# **DLL Frequency Range Specifications**

### Table 1-43: DLL Frequency Range Specifications for Arria V Devices

| Parameter                     | -I3, -C4  | -I5, -C5  | -C6       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 200 - 667 | 200 - 667 | 200 - 667 | MHz  |

# DQS Logic Block Specifications

## Table 1-44: DQS Phase Shift Error Specifications for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Arria V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -I3, -C4 | –I5, –C5 | -C6 | Unit |

|----------------------------|----------|----------|-----|------|

| 2                          | 40       | 80       | 80  | ps   |

| Symbol               | Description          | Min                                                  | Тур | Max | Unit |

|----------------------|----------------------|------------------------------------------------------|-----|-----|------|

| T <sub>din_end</sub> | Input data valid end | $(2 + R_{delay}) \times T_{qspi\_clk} - 1.21^{(85)}$ |     | _   | ns   |

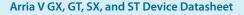

### Figure 1-8: Quad SPI Flash Timing Diagram

This timing diagram illustrates clock polarity mode 0 and clock phase mode 0.

#### **Related Information**

# Quad SPI Flash Controller Chapter, Arria V Hard Processor System Technical Reference Manual

Provides more information about Rdelay.

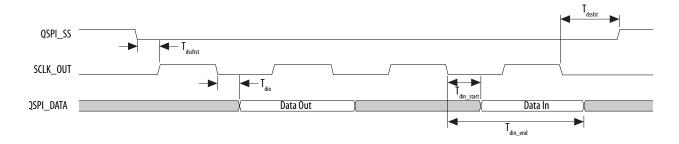

## **SPI Timing Characteristics**

### Table 1-52: SPI Master Timing Requirements for Arria V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol           | Description                               | Min       | Max | Unit |

|------------------|-------------------------------------------|-----------|-----|------|

| T <sub>clk</sub> | CLK clock period                          | 16.67     | _   | ns   |

| T <sub>su</sub>  | SPI Master-in slave-out (MISO) setup time | 8.35 (86) | _   | ns   |

$<sup>^{(85)}</sup>$  R<sub>delay</sub> is set by programming the register <code>qspiregs.rddatacap</code>. For the SoC EDS software version 13.1 and later, Altera provides automatic Quad SPI calibration in the preloader. For more information about R<sub>delay</sub>, refer to the Quad SPI Flash Controller chapter in the Arria V Hard Processor System Technical Reference Manual.

#### Figure 1-10: SPI Slave Timing Diagram

#### **Related Information**

#### SPI Controller, Arria V Hard Processor System Technical Reference Manual

Provides more information about rx\_sample\_delay.

## **SD/MMC Timing Characteristics**

#### Table 1-54: Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Arria V Devices

After power up or cold reset, the Boot ROM uses drvsel = 3 and smplsel = 0 to execute the code. At the same time, the SD/MMC controller enters the Identification Phase followed by the Data Phase. During this time, the value of interface output clock SDMMC\_CLK\_OUT changes from a maximum of 400 kHz (Identification Phase) up to a maximum of 12.5 MHz (Data Phase), depending on the internal reference clock SDMMC\_CLK and the CSEL setting. The value of SDMMC\_CLK is based on the external oscillator frequency and has a maximum value of 50 MHz.

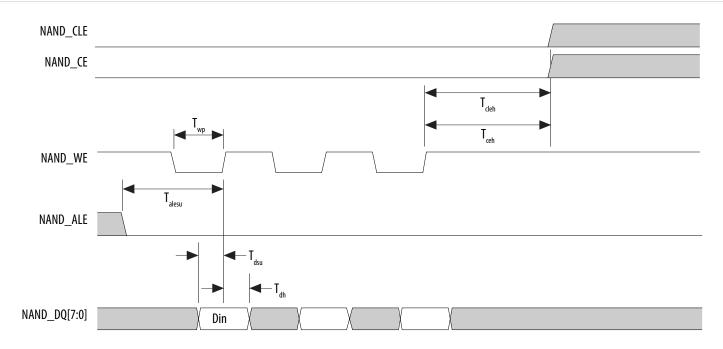

## Figure 1-19: NAND Data Write Timing Diagram

#### 1-76 FPGA JTAG Configuration Timing

| POR Delay | Minimum Maximum |     | Unit |  |

|-----------|-----------------|-----|------|--|

| Standard  | 100             | 300 | ms   |  |

#### **Related Information**

## **MSEL Pin Settings**

Provides more information about POR delay based on MSEL pin settings for each configuration scheme.

# **FPGA JTAG Configuration Timing**

## Table 1-64: FPGA JTAG Timing Parameters and Values for Arria V Devices

| Symbol                  | Description                              | Min                            | Мах                | Unit |

|-------------------------|------------------------------------------|--------------------------------|--------------------|------|

| t <sub>JCP</sub>        | TCK clock period                         | <b>30, 167</b> <sup>(92)</sup> | _                  | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14                             |                    | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14                             |                    | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2                              |                    | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3                              |                    | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5                              |                    | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |                                | 12 <sup>(93)</sup> | ns   |

| t <sub>JPZX</sub>       | JTAG port high impedance to valid output |                                | 14 <sup>(93)</sup> | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | _                              | 14 <sup>(93)</sup> | ns   |

<sup>&</sup>lt;sup>(92)</sup> The minimum TCK clock period is 167 ns if  $V_{CCBAT}$  is within the range 1.2 V – 1.5 V when you perform the volatile key programming.

<sup>&</sup>lt;sup>(93)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

# **Remote System Upgrades**

## Table 1-74: Remote System Upgrade Circuitry Timing Specifications for Arria V Devices

| Parameter                                 | Minimum | Unit |

|-------------------------------------------|---------|------|

| t <sub>RU_nCONFIG</sub> <sup>(110)</sup>  | 250     | ns   |

| t <sub>RU_nRSTIMER</sub> <sup>(111)</sup> | 250     | ns   |

#### **Related Information**

- **Remote System Upgrade State Machine** Provides more information about configuration reset (RU\_CONFIG) signal.

- User Watchdog Timer Provides more information about reset\_timer (RU\_nRSTIMER) signal.

# User Watchdog Internal Oscillator Frequency Specifications

## Table 1-75: User Watchdog Internal Oscillator Frequency Specifications for Arria V Devices

| Parameter                                   | Minimum | Typical | Maximum | Unit |

|---------------------------------------------|---------|---------|---------|------|

| User watchdog internal oscillator frequency | 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O timing and the Quartus Prime Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

<sup>&</sup>lt;sup>(110)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification.

<sup>&</sup>lt;sup>(111)</sup> This is equivalent to strobing the reset timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide For more information about the EPE tool.

- **PowerPlay Power Analysis** ٠ For more information about PowerPlay power analysis.

#### **Power Consumption**

Altera offers two ways to estimate power consumption for a design-the Excel-based Early Power Estimator and the Quartus II PowerPlay Power Analyzer feature.

Note: You typically use the interactive Excel-based Early Power Estimator before designing the FPGA to get a magnitude estimate of the device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-and-route. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide For more information about the EPE tool.

- PowerPlay Power Analysis For more information about PowerPlay power analysis.

#### I/O Pin Leakage Current

#### Table 2-8: I/O Pin Leakage Current for Arria V GZ Devices

If  $V_O = V_{CCIO}$  to  $V_{CCIOMax}$ , 100 µA of leakage current per I/O is expected.

| Symbol          | Description           | Conditions                     | Min | Тур | Max | Unit |

|-----------------|-----------------------|--------------------------------|-----|-----|-----|------|

| II              | Input pin             | $V_{I} = 0 V$ to $V_{CCIOMAX}$ | -30 |     | 30  | μΑ   |

| I <sub>OZ</sub> | Tri-stated I/O<br>pin | $V_{O} = 0 V$ to $V_{CCIOMAX}$ | -30 | —   | 30  | μΑ   |

| 2-28 | Transmitter |

|------|-------------|

|------|-------------|

| Symbol/Description                                                             | Conditions                                        | Transceiver Speed Grade 2 |              |     | Transceiver Speed Grade 3 |              |     | Unit |

|--------------------------------------------------------------------------------|---------------------------------------------------|---------------------------|--------------|-----|---------------------------|--------------|-----|------|

| Symbol/Description                                                             | Conditions                                        | Min                       | Тур          | Мах | Min                       | Тур          | Мах | Onic |

|                                                                                | 85- $\Omega$ setting                              | _                         | 85 ± 20%     | _   |                           | 85<br>± 20%  | _   | Ω    |

| Differential on-chip termination                                               | 100-Ω setting                                     | —                         | 100<br>± 20% | _   |                           | 100<br>± 20% |     | Ω    |

| resistors                                                                      | 120-Ω setting                                     | _                         | 120<br>± 20% | _   |                           | 120<br>± 20% |     | Ω    |

|                                                                                | 150-Ω setting                                     | _                         | 150<br>± 20% | _   |                           | 150<br>± 20% |     | Ω    |

| V <sub>OCM</sub> (AC coupled)                                                  | 0.65-V setting                                    | _                         | 650          |     |                           | 650          |     | mV   |

| V <sub>OCM</sub> (DC coupled)                                                  | _                                                 |                           | 650          |     |                           | 650          |     | mV   |

| Intra-differential pair skew                                                   | Tx V <sub>CM</sub> = 0.5 V and slew rate of 15 ps | _                         | _            | 15  | _                         | _            | 15  | ps   |

| Intra-transceiver block transmitter x6 PMA bonded mode channel-to-channel skew |                                                   | —                         |              | 120 |                           | _            | 120 | ps   |

| Inter-transceiver block transmitter channel-to-channel skew                    | xN PMA bonded mode                                | —                         | —            | 500 | _                         | _            | 500 | ps   |

### **Related Information**

## Arria V Device Overview

For more information about device ordering codes.

#### 2-42 Memory Block Specifications

| Mode                          | Performar | nce     |     | Unit |  |

|-------------------------------|-----------|---------|-----|------|--|

| imoue                         | C3, I3L   | C4      | 14  |      |  |

| One sum of two $27 \times 27$ | 380       | 300     | 290 | MHz  |  |

| One sum of two $36 \times 18$ | 380       | 300     |     | MHz  |  |

| One complex 18 × 18           | 400       | 350     |     | MHz  |  |

| One 36 × 36                   | 380       | 300     |     | MHz  |  |

| Modes using Three DSP Blocks  |           | •       |     |      |  |

| One complex 18 × 25           | 340       | 275 265 |     | MHz  |  |

| Modes using Four DSP Blocks   |           |         |     |      |  |

| One complex $27 \times 27$    | 350       | 310     |     | MHz  |  |

## **Memory Block Specifications**

#### Table 2-36: Memory Block Performance Specifications for Arria V GZ Devices

To achieve the maximum memory block performance, use a memory block clock that comes through global clock routing from an on-chip PLL set to **50%** output duty cycle. Use the Quartus II software to report timing for this and other memory block clocking schemes.

When you use the error detection cyclical redundancy check (CRC) feature, there is no degradation in F<sub>MAX</sub>.

| Memory                                                      | Mode                              | Resources Used |        |     | Unit |     |     |      |

|-------------------------------------------------------------|-----------------------------------|----------------|--------|-----|------|-----|-----|------|

|                                                             |                                   | ALUTs          | Memory | C3  | C4   | I3L | 14  | Omit |

| MLAB Simple dual-port, x32/x64<br>Simple dual-port, x16 dep | Single port, all supported widths | 0              | 1      | 400 | 315  | 400 | 315 | MHz  |

|                                                             | Simple dual-port, x32/x64 depth   | 0              | 1      | 400 | 315  | 400 | 315 | MHz  |

|                                                             | Simple dual-port, x16 depth (178) | 0              | 1      | 533 | 400  | 533 | 400 | MHz  |

|                                                             | ROM, all supported widths         | 0              | 1      | 500 | 450  | 500 | 450 | MHz  |

<sup>(178)</sup> The F<sub>MAX</sub> specification is only achievable with Fitter options, **MLAB Implementation In 16-Bit Deep Mode** enabled.

AV-51002 2017.02.10

| Symbol                                                                    | Conditions                                                                                      | C3, I3L |     |     |     | Unit |      |      |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------|-----|-----|-----|------|------|------|

| Symbol                                                                    | Conditions                                                                                      | Min     | Тур | Мах | Min | Тур  | Мах  | Onic |

| t <sub>x Jitter</sub> - True Differential I/O                             | Total Jitter for Data Rate<br>600 Mbps - 1.25 Gbps                                              | _       | _   | 160 | _   |      | 160  | ps   |

| Standards                                                                 | Total Jitter for Data Rate<br>< 600 Mbps                                                        | _       | _   | 0.1 | _   |      | 0.1  | UI   |

| t <sub>x Jitter</sub> - Emulated Differential<br>I/O Standards with Three | Total Jitter for Data Rate<br>600 Mbps - 1.25 Gbps                                              | —       | _   | 300 | _   |      | 325  | ps   |

| External Output Resistor<br>Network                                       | Total Jitter for Data Rate<br>< 600 Mbps                                                        | _       | _   | 0.2 | _   |      | 0.25 | UI   |

| t <sub>DUTY</sub>                                                         | Transmitter output clock duty<br>cycle for both True and Emulated<br>Differential I/O Standards | 45      | 50  | 55  | 45  | 50   | 55   | %    |

|                                                                           | True Differential I/O Standards                                                                 |         | _   | 200 |     |      | 200  | ps   |

| t <sub>RISE</sub> & t <sub>FALL</sub>                                     | Emulated Differential I/O<br>Standards with three external<br>output resistor networks          | _       | _   | 250 | _   | _    | 300  | ps   |

|                                                                           | True Differential I/O Standards                                                                 |         | _   | 150 |     | _    | 150  | ps   |

| TCCS                                                                      | Emulated Differential I/O<br>Standards                                                          | _       | —   | 300 |     |      | 300  | ps   |

# **Receiver High-Speed I/O Specifications**

## Table 2-41: Receiver High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Number of DQS Delay Buffers | C3, I3L | C4, I4 | Unit |  |

|-----------------------------|---------|--------|------|--|

| 4                           | 120     | 128    | ps   |  |

## **Memory Output Clock Jitter Specifications**

#### Table 2-50: Memory Output Clock Jitter Specification for Arria V GZ Devices

The clock jitter specification applies to the memory output clock pins generated using differential signal-splitter and DDIO circuits clocked by a PLL output routed on a PHY, regional, or global clock network as specified. Altera recommends using PHY clock networks whenever possible.

The clock jitter specification applies to the memory output clock pins clocked by an integer PLL.

The memory output clock jitter is applicable when an input jitter of 30 ps peak-to-peak is applied with bit error rate (BER) -12, equivalent to 14 sigma.

| Clock Notwork                                            | Parameter                    | Symbol                 | С3,   | I3L  | C4    | Unit |    |

|----------------------------------------------------------|------------------------------|------------------------|-------|------|-------|------|----|

| CIOCK NELWOIK                                            | ralameter                    | Symbol                 | Min   | Мах  | Min   | Мах  |    |

|                                                          | Clock period jitter          | t <sub>JIT(per)</sub>  | -55   | 55   | -55   | 55   | ps |

| Regional                                                 | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -110  | 110  | -110  | 110  | ps |

|                                                          | Duty cycle jitter            | t <sub>JIT(duty)</sub> | -82.5 | 82.5 | -82.5 | 82.5 | ps |

|                                                          | Clock period jitter          | t <sub>JIT(per)</sub>  | -82.5 | 82.5 | -82.5 | 82.5 | ps |

| Global                                                   | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -165  | 165  | -165  | 165  | ps |

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ | -90                          | 90                     | -90   | 90   | ps    |      |    |

|                                                          | Clock period jitter          | t <sub>JIT(per)</sub>  | -30   | 30   | -35   | 35   | ps |

| PHY Clock                                                | Cycle-to-cycle period jitter | t <sub>JIT(cc)</sub>   | -60   | 60   | -70   | 70   | ps |

|                                                          | Duty cycle jitter            | t <sub>JIT(duty)</sub> | -45   | 45   | -56   | 56   | ps |

Note: When you enable the decompression or design security feature, the DCLK-to-DATA[] ratio varies for FPP ×8, FPP ×16, and FPP ×32. For the respective DCLK-to-DATA[] ratio, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

#### Table 2-56: FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is 1

Use these timing parameters when the decompression and design security features are disabled.

| Symbol                      | Parameter                                    | Minimum                | Maximum     | Unit |

|-----------------------------|----------------------------------------------|------------------------|-------------|------|

| t <sub>CF2CD</sub>          | nCONFIG low to CONF_DONE low                 | _                      | 600         | ns   |

| t <sub>CF2ST0</sub>         | nconfig low to nstatus low                   | _                      | 600         | ns   |

| t <sub>CFG</sub>            | nCONFIG low pulse width                      | 2                      | _           | μs   |

| t <sub>STATUS</sub>         | nSTATUS low pulse width                      | 268                    | 1,506 (205) | μs   |

| t <sub>CF2ST1</sub>         | nCONFIG high to nSTATUS high                 |                        | 1,506 (206) | μs   |

| t <sub>CF2CK</sub><br>(207) | nCONFIG high to first rising edge on DCLK    | 1,506                  | _           | μs   |

| t <sub>ST2CK</sub> (20      | hstatus high to first rising edge of DCLK    | 2                      | _           | μs   |

| t <sub>DSU</sub>            | DATA[] setup time before rising edge on DCLK | 5.5                    | _           | ns   |

| t <sub>DH</sub>             | DATA[] hold time after rising edge on DCLK   | 0                      | _           | ns   |

| t <sub>CH</sub>             | DCLK high time                               | $0.45 	imes 1/f_{MAX}$ | —           | s    |

| t <sub>CL</sub>             | DCLK low time                                | $0.45 	imes 1/f_{MAX}$ | —           | s    |

| t <sub>CLK</sub>            | DCLK period                                  | 1/f <sub>MAX</sub>     | —           | s    |

| f                           | DCLK frequency (FPP ×8/×16)                  |                        | 125         | MHz  |

| $f_{MAX}$                   | DCLK frequency (FPP ×32)                     | —                      | 100         | MHz  |

| t <sub>CD2UM</sub>          | CONF_DONE high to user mode <sup>(208)</sup> | 175                    | 437         | μs   |

<sup>&</sup>lt;sup>(205)</sup> This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>&</sup>lt;sup>(206)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>&</sup>lt;sup>(207)</sup> If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

| Symbol                  | Parameter                                         | Minimum                                                 | Maximum | Unit |

|-------------------------|---------------------------------------------------|---------------------------------------------------------|---------|------|

| t <sub>CD2CU</sub>      | CONF_DONE high to CLKUSR enabled                  | $4 \times maximum$                                      | —       | —    |

|                         |                                                   | DCLK period                                             |         |      |

| t <sub>CD2UM</sub><br>C | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> +<br>(8576 × CLKUSR period)<br>(209) | _       | _    |

#### **Related Information**

- DCLK-to-DATA[] Ratio (r) for FPP Configuration on page 2-57 ٠

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Arria V GZ Device Datasheet

**Altera Corporation**

<sup>&</sup>lt;sup>(208)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

<sup>&</sup>lt;sup>(209)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

#### Table 2-60: PS Timing Parameters for Arria V GZ Devices

| Symbol                              | Parameter                                         | Minimum                                               | Maximum     | Unit |

|-------------------------------------|---------------------------------------------------|-------------------------------------------------------|-------------|------|

| t <sub>CF2CD</sub>                  | nCONFIG low to CONF_DONE low                      | —                                                     | 600         | ns   |

| t <sub>CF2ST0</sub>                 | nCONFIG low to nSTATUS low                        | _                                                     | 600         | ns   |

| t <sub>CFG</sub>                    | nCONFIG low pulse width                           | 2                                                     |             | μs   |

| t <sub>STATUS</sub>                 | nSTATUS low pulse width                           | 268                                                   | 1,506 (217) | μs   |

| t <sub>CF2ST1</sub>                 | nCONFIG high to nSTATUS high                      | _                                                     | 1,506 (218) | μs   |

| t <sub>CF2CK</sub><br>(219)         | nCONFIG high to first rising edge on DCLK         | 1,506                                                 | _           | μs   |

| t <sub>ST2CK</sub> <sup>(219)</sup> | nSTATUS high to first rising edge of DCLK         | 2                                                     |             | μs   |

| t <sub>DSU</sub>                    | DATA[] setup time before rising edge on DCLK      | 5.5                                                   |             | ns   |

| t <sub>DH</sub>                     | DATA[] hold time after rising edge on DCLK        | 0                                                     | _           | ns   |

| t <sub>CH</sub>                     | DCLK high time                                    | $0.45 	imes 1/f_{MAX}$                                |             | s    |

| t <sub>CL</sub>                     | DCLK low time                                     | $0.45 	imes 1/f_{MAX}$                                | —           | S    |

| t <sub>CLK</sub>                    | DCLK period                                       | 1/f <sub>MAX</sub>                                    |             | s    |

| f <sub>MAX</sub>                    | DCLK frequency                                    | _                                                     | 125         | MHz  |

| t <sub>CD2UM</sub>                  | CONF_DONE high to user mode <sup>(220)</sup>      | 175                                                   | 437         | μs   |

| t <sub>CD2CU</sub>                  | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period                 |             |      |

| t <sub>CD2UMC</sub>                 | CONF_DONE high to user mode with CLKUSR option on | $t_{CD2CU}$ + (8576 × CLKUSR period) <sup>(221)</sup> | _           |      |

<sup>&</sup>lt;sup>(217)</sup> This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>&</sup>lt;sup>(218)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>&</sup>lt;sup>(219)</sup> If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

<sup>&</sup>lt;sup>(220)</sup> The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.