Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 14151                                                      |

| Number of Logic Elements/Cells | 300000                                                     |

| Total RAM Bits                 | 17358848                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxmb1g4f35i5g |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Transceiver Specifications for Arria V GT and ST Devices

Table 1-26: Reference Clock Specifications for Arria V GT and ST Devices

| Symbol/Description                         | Condition                                                | Tran            | sceiver Speed Gra | Unit                            |                |

|--------------------------------------------|----------------------------------------------------------|-----------------|-------------------|---------------------------------|----------------|

| Symbol/Description                         | Condition                                                | Min             | Тур               | Max                             | Offic          |

| Supported I/O standards                    | 1.2 V PCML, 1.4 VPCML,                                   | 1.5 V PCML, 2.5 | V PCML, Differe   | ential LVPECL <sup>(40)</sup> , | HCSL, and LVDS |

| Input frequency from REFCLK input pins     | _                                                        | 27              | _                 | 710                             | MHz            |

| Rise time                                  | Measure at ±60 mV of differential signal <sup>(41)</sup> | _               | _                 | 400                             | ps             |

| Fall time                                  | Measure at ±60 mV of differential signal <sup>(41)</sup> | _               | _                 | 400                             | ps             |

| Duty cycle                                 | _                                                        | 45              | _                 | 55                              | %              |

| Peak-to-peak differential input voltage    | _                                                        | 200             | _                 | 300 <sup>(42)</sup> /2000       | mV             |

| Spread-spectrum modulating clock frequency | PCI Express (PCIe)                                       | 30              | _                 | 33                              | kHz            |

| Spread-spectrum downspread                 | PCIe                                                     | _               | 0 to -0.5%        | _                               | _              |

| On-chip termination resistors              | _                                                        | _               | 100               | _                               | Ω              |

| V <sub>ICM</sub> (AC coupled)              | _                                                        | _               | 1.2               | _                               | V              |

| V <sub>ICM</sub> (DC coupled)              | HCSL I/O standard for the PCIe reference clock           | 250             | _                 | 550                             | mV             |

Send Feedback

<sup>(40)</sup> Differential LVPECL signal levels must comply to the minimum and maximum peak-to-peak differential input voltage specified in this table.

<sup>(41)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

<sup>(42)</sup> The maximum peak-to peak differential input voltage of 300 mV is allowed for DC coupled link.

| Symbol/Description                          | Condition                                                     | Transceiver Speed Grade 3                                                                                                                                                                                                                               |     |     | Unit  |

|---------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| Symbol/Description                          | Condition                                                     | Min                                                                                                                                                                                                                                                     | Тур | Max | Offic |

| $t_{\mathrm{LTD\_manual}}^{(51)}$           | _                                                             | 4                                                                                                                                                                                                                                                       | _   | _   | μs    |

| t <sub>LTR_LTD_manual</sub> <sup>(52)</sup> | _                                                             | 15                                                                                                                                                                                                                                                      | _   | _   | μs    |

| Programmable ppm detector <sup>(53)</sup>   | _                                                             | ±62.5, 100, 125, 200, 250, 300, 500, and 1000                                                                                                                                                                                                           |     |     | ppm   |

| Run length                                  | _                                                             | _                                                                                                                                                                                                                                                       | _   | 200 | UI    |

| Programmable equalization AC and DC gain    | AC gain setting = 0 to $3^{(54)}$<br>DC gain setting = 0 to 1 | Refer to CTLE Response at Data Rates > 3.25 Gbps across Supported AC Ga and DC Gain for Arria V GX, GT, SX, and ST Devices and CTLE Response Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain for Arria GX, GT, SX, and ST Devices diagrams. |     |     |       |

Table 1-29: Transmitter Specifications for Arria V GT and ST Devices

| Symbol/Description              | Condition                  | Tran  | sceiver Speed Gra | Unit    |       |

|---------------------------------|----------------------------|-------|-------------------|---------|-------|

|                                 | Condition                  | Min   | Тур               | Max     | Offic |

| Supported I/O standards         | 1.5 V PCML                 |       |                   |         |       |

| Data rate (6-Gbps transceiver)  | _                          | 611   | _                 | 6553.6  | Mbps  |

| Data rate (10-Gbps transceiver) | _                          | 0.611 | _                 | 10.3125 | Gbps  |

| V <sub>OCM</sub> (AC coupled)   | _                          | _     | 650               | _       | mV    |

| V <sub>OCM</sub> (DC coupled)   | ≤ 3.2 Gbps <sup>(48)</sup> | 670   | 700               | 730     | mV    |

Arria V GX, GT, SX, and ST Device Datasheet

$t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{LTR\_LTD\_manual}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

<sup>(53)</sup> The rate match FIFO supports only up to  $\pm 300$  ppm.

<sup>(54)</sup> The Quartus Prime software allows AC gain setting = 3 for design with data rate between 611 Mbps and 1.25 Gbps only.

### **DSP Block Performance Specifications**

Table 1-37: DSP Block Performance Specifications for Arria V Devices

| Mode                          |                                                          | Performance |          |              | Unit  |

|-------------------------------|----------------------------------------------------------|-------------|----------|--------------|-------|

|                               | Mode                                                     |             | −I5, −C5 | - <b>C</b> 6 | Offic |

|                               | Independent 9 × 9 multiplication                         | 370         | 310      | 220          | MHz   |

|                               | Independent 18 × 19 multiplication                       | 370         | 310      | 220          | MHz   |

|                               | Independent 18 × 25 multiplication                       | 370         | 310      | 220          | MHz   |

| C                             | Independent 20 × 24 multiplication                       | 370         | 310      | 220          | MHz   |

| Block                         | Independent 27 × 27 multiplication                       | 310         | 250      | 200          | MHz   |

|                               | Two 18 × 19 multiplier adder mode                        | 370         | 310      | 220          | MHz   |

|                               | $18 \times 18$ multiplier added summed with 36-bit input | 370         | 310      | 220          | MHz   |

| Modes using Two<br>DSP Blocks | Complex 18 × 19 multiplication                           | 370         | 310      | 220          | MHz   |

## **Memory Block Performance Specifications**

To achieve the maximum memory block performance, use a memory block clock that comes through global clock routing from an on-chip PLL and set to 50% output duty cycle. Use the Quartus Prime software to report timing for the memory block clocking schemes.

When you use the error detection cyclical redundancy check (CRC) feature, there is no degradation in  $f_{MAX}$ .

## **Memory Output Clock Jitter Specifications**

## Table 1-45: Memory Output Clock Jitter Specifications for Arria V Devices

The memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2/DDR3 SDRAM standard. The memory output clock jitter is applicable when an input jitter of 30 ps (p-p) is applied with bit error rate (BER)  $10^{-12}$ , equivalent to 14 sigma. Altera recommends using the UniPHY intellectual property (IP) with PHYCLK connections for better jitter performance.

| Parameter                    | Clock Network | Symbol                | -l3, | -C4 | −I5, | -C5 | -(  | <b>C6</b> | Unit |

|------------------------------|---------------|-----------------------|------|-----|------|-----|-----|-----------|------|

|                              | Clock Network | Зуппоп                |      | Max | Min  | Max | Min | Max       | Onit |

| Clock period jitter          | PHYCLK        | t <sub>JIT(per)</sub> | -41  | 41  | -50  | 50  | -55 | 55        | ps   |

| Cycle-to-cycle period jitter | PHYCLK        | t <sub>JIT(cc)</sub>  | 6    | 3   | 9    | 0   | 9   | 4         | ps   |

## **OCT Calibration Block Specifications**

Table 1-46: OCT Calibration Block Specifications for Arria V Devices

| Symbol                | Description                                                                                                                                                 | Min | Тур  | Max | Unit   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by OCT calibration blocks                                                                                                                    | _   | _    | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of octusrclk clock cycles required for $R_{S}$ OCT/ $\!R_{T}$ OCT calibration                                                                        | _   | 1000 | _   | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for OCT code to shift out                                                                                         | _   | 32   | _   | Cycles |

| $T_{RS\_RT}$          | Time required between the $dyn\_term\_ctrl$ and $oe$ signal transitions in a bidirectional I/O buffer to dynamically switch between $R_S$ OCT and $R_T$ OCT | _   | 2.5  | _   | ns     |

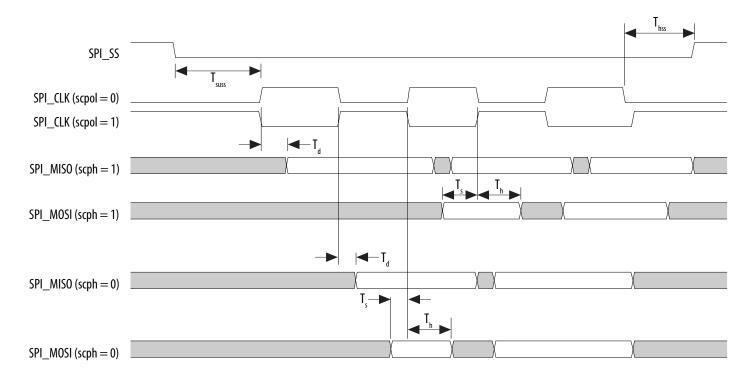

Figure 1-10: SPI Slave Timing Diagram

#### **Related Information**

SPI Controller, Arria V Hard Processor System Technical Reference Manual

Provides more information about rx\_sample\_delay.

## **SD/MMC Timing Characteristics**

### Table 1-54: Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Arria V Devices

After power up or cold reset, the Boot ROM uses <code>drvsel = 3</code> and <code>smplsel = 0</code> to execute the code. At the same time, the SD/MMC controller enters the Identification Phase followed by the Data Phase. During this time, the value of interface output clock <code>SDMMC\_CLK\_OUT</code> changes from a maximum of 400 kHz (Identification Phase) up to a maximum of 12.5 MHz (Data Phase), depending on the internal reference clock <code>SDMMC\_CLK</code> and the <code>CSEL</code> setting. The value of <code>SDMMC\_CLK</code> is based on the external oscillator frequency and has a maximum value of 50 MHz.

| Symbol               | Parameter                                                 | Minimum                                                   | Maximum | Unit   |

|----------------------|-----------------------------------------------------------|-----------------------------------------------------------|---------|--------|

| $t_{\mathrm{CD2CU}}$ | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                                   | _       | _      |

| t <sub>CD2UMC</sub>  | CONF_DONE high to user mode with CLKUSR option on         | $t_{\text{CD2CU}}$ + ( $T_{\text{init}}$ × CLKUSR period) | _       | _      |

| T <sub>init</sub>    | Number of clock cycles required for device initialization | 8,576                                                     | _       | Cycles |

#### **Related Information**

**FPP Configuration Timing**

Provides the FPP configuration timing waveforms.

## **AS Configuration Timing**

### Table 1-68: AS Timing Parameters for AS ×1 and ×4 Configurations in Arria V Devices

The minimum and maximum numbers apply to both the internal oscillator and CLKUSR when either one is used as the clock source for device configuration.

The  $t_{CF2CD}$ ,  $t_{CF2ST0}$ ,  $t_{CFG}$ ,  $t_{STATUS}$ , and  $t_{CF2ST1}$  timing parameters are identical to the timing parameters for passive serial (PS) mode listed in PS Timing Parameters for Arria V Devices table. You can obtain the  $t_{CF2ST1}$  value if you do not delay configuration by externally holding <code>nstatus</code> low.

| Symbol               | Parameter                                                 | Minimum                                                   | Maximum | Unit   |

|----------------------|-----------------------------------------------------------|-----------------------------------------------------------|---------|--------|

| $t_{CO}$             | DCLK falling edge to the AS_DATAO/ASDO output             | _                                                         | 2       | ns     |

| t <sub>SU</sub>      | Data setup time before the falling edge on DCLK           | 1.5                                                       | _       | ns     |

| t <sub>DH</sub>      | Data hold time after the falling edge on DCLK             | 0                                                         |         | ns     |

| t <sub>CD2UM</sub>   | CONF_DONE high to user mode                               | 175                                                       | 437     | μs     |

| $t_{\mathrm{CD2CU}}$ | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                                   | _       | _      |

| t <sub>CD2UMC</sub>  | CONF_DONE high to user mode with CLKUSR option on         | $t_{\text{CD2CU}}$ + ( $T_{\text{init}}$ × CLKUSR period) | _       | _      |

| $T_{\rm init}$       | Number of clock cycles required for device initialization | 8,576                                                     | _       | Cycles |

| Date      | Version    | Changes                                                                                                                                                                                                                                                                                                      |

|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2015 | 2015.06.16 | Added the supported data rates for the following output standards using true LVDS output buffer types in the High-Speed I/O Specifications for Arria V Devices table:                                                                                                                                        |

|           |            | True RSDS output standard: data rates of up to 360 Mbps                                                                                                                                                                                                                                                      |

|           |            | True mini-LVDS output standard: data rates of up to 400 Mbps                                                                                                                                                                                                                                                 |

|           |            | Added note in the condition for Transmitter—Emulated Differential I/O Standards f <sub>HSDR</sub> data rate parameter in the High-Speed I/O Specifications for Arria V Devices table. Note: When using True LVDS RX channels for emulated LVDS TX channel, only serialization factors 1 and 2 are supported. |

|           |            | Changed Queued Serial Peripheral Interface (QSPI) to Quad Serial Peripheral Interface (SPI) Flash.                                                                                                                                                                                                           |

|           |            | Updated T <sub>h</sub> location in I <sup>2</sup> C Timing Diagram.                                                                                                                                                                                                                                          |

|           |            | Updared T <sub>wp</sub> location in NAND Address Latch Timing Diagram.                                                                                                                                                                                                                                       |

|           |            | • Corrected the unit for t <sub>DH</sub> from ns to s in FPP Timing Parameters When DCLK-to-DATA[] Ratio is >1 for Arria V Devices table.                                                                                                                                                                    |

|           |            | • Updated the maximum value for $t_{CO}$ from 4 ns to 2 ns in AS Timing Parameters for AS $\times 1$ and $\times 4$ Configurations in Arria V Devices table.                                                                                                                                                 |

|           |            | Moved the following timing diagrams to the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.                                                                                                                                                                            |

|           |            | FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is 1                                                                                                                                                                                                                                             |

|           |            | FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is >1                                                                                                                                                                                                                                            |

|           |            | AS Configuration Timing Waveform                                                                                                                                                                                                                                                                             |

|           |            | PS Configuration Timing Waveform                                                                                                                                                                                                                                                                             |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2012 | 3.0     | <ul> <li>Updated Table 2, Table 4, Table 9, Table 14, Table 16, Table 17, Table 20, Table 21, Table 25, Table 29, Table 36, Table 56, Table 57, and Table 60.</li> <li>Removed table: Transceiver Block Jitter Specifications for Arria V Devices.</li> <li>Added HPS information: <ul> <li>Added "HPS Specifications" section.</li> <li>Added Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, and Table 50.</li> <li>Added Figure 7, Figure 8, Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, Figure 14, Figure 15, Figure 16, Figure 17, Figure 18, and Figure 19.</li> <li>Updated Table 3 and Table 5.</li> </ul> </li> </ul> |

| October 2012  | 2.4     | <ul> <li>Updated Arria V GX V<sub>CCR_GXBL/R</sub>, V<sub>CCT_GXBL/R</sub>, and V<sub>CCL_GXBL/R</sub> minimum and maximum values, and data rate in Table 4.</li> <li>Added receiver V<sub>ICM</sub> (AC coupled) and V<sub>ICM</sub> (DC coupled) values, and transmitter V<sub>OCM</sub> (AC coupled) and V<sub>OCM</sub> (DC coupled) values in Table 20 and Table 21.</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| August 2012   | 2.3     | Updated the SERDES factor condition in Table 30.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| July 2012     | 2.2     | <ul> <li>Updated the maximum voltage for V<sub>I</sub> (DC input voltage) in Table 1.</li> <li>Updated Table 20 to include the Arria V GX -I3 speed grade.</li> <li>Updated the minimum value of the fixedclk clock frequency in Table 20 and Table 21.</li> <li>Updated the SERDES factor condition in Table 30.</li> <li>Updated Table 50 to include the IOE programmable delay settings for the Arria V GX -I3 speed grade.</li> </ul>                                                                                                                                                                                                                                                                        |

| June 2012     | 2.1     | Updated $V_{CCR\_GXBL/R}$ , $V_{CCT\_GXBL/R}$ , and $V_{CCL\_GXBL/R}$ values in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% of the duty cycle.

For example, a signal that overshoots to 3.95 V can be at 3.95 V for only  $\sim 21\%$  over the lifetime of the device; for a device lifetime of 10 years, the overshoot duration amounts to  $\sim 2$  years.

Table 2-4: Maximum Allowed Overshoot During Transitions for Arria V GZ Devices

| Symbol  | Description      | Condition (V) | Overshoot Duration as % @ T <sub>J</sub> = 100°C | Unit |

|---------|------------------|---------------|--------------------------------------------------|------|

|         |                  | 3.8           | 100                                              | %    |

|         |                  | 3.85          | 64                                               | %    |

|         |                  | 3.9           | 36                                               | %    |

|         |                  | 3.95          | 21                                               | %    |

| Vi (AC) | AC input voltage | 4             | 12                                               | %    |

|         |                  | 4.05          | 7                                                | %    |

|         |                  | 4.1           | 4                                                | %    |

|         |                  | 4.15          | 2                                                | %    |

|         |                  | 4.2           | 1                                                | %    |

## **Recommended Operating Conditions**

### Table 2-5: Recommended Operating Conditions for Arria V GZ Devices

Power supply ramps must all be strictly monotonic, without plateaus.

| Symbol   | Description                                             | Condition | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|----------|---------------------------------------------------------|-----------|--------------------------|---------|--------------------------|------|

| $V_{CC}$ | Core voltage and periphery circuitry power supply (115) | _         | 0.82                     | 0.85    | 0.88                     | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

Altera Corporation Arria V GZ Device Datasheet

<sup>(115)</sup> The V<sub>CC</sub> core supply must be set to 0.9 V if the Partial Reconfiguration (PR) feature is used.

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>DIF(DC)</sub> (V) |      | $V_{X(AC)}(V)$          |                                      | V <sub>CM(DC)</sub> (V) |                                     |                           | V <sub>DIF(AC)</sub> (V)          |                              |      |                             |

|------------------------|-----------------------|-----|--------------------------|------|-------------------------|--------------------------------------|-------------------------|-------------------------------------|---------------------------|-----------------------------------|------------------------------|------|-----------------------------|

| i/O Standard           | Min                   | Тур | Max                      | Min  | Max                     | Min                                  | Тур                     | Max                                 | Min                       | Тур                               | Max                          | Min  | Max                         |

| HSTL-12 Class<br>I, II | 1.14                  | 1.2 | 1.26                     | 0.16 | V <sub>CCIO</sub> + 0.3 | _                                    | $0.5 \times V_{CCIO}$   | _                                   | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub><br>IO | $0.6 \times V_{\text{CCIO}}$ | 0.3  | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14                  | 1.2 | 1.3                      | 0.26 | 0.26                    | 0.5 ×<br>V <sub>CCIO</sub> –<br>0.12 | $0.5 \times V_{CCIO}$   | $0.5 \times V_{\rm CCIO} \\ + 0.12$ | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub>       | 0.6 ×<br>V <sub>CCIO</sub>   | 0.44 | 0.44                        |

Table 2-21: Differential I/O Standard Specifications for Arria V GZ Devices

| I/O Standard   | Vo    | :CIO (V) ( | 128)  | V <sub>ID</sub> (mV) <sup>(129)</sup> |                   |     | V <sub>ICM(DC)</sub> (V) |                                   | V <sub>OD</sub> (V) <sup>(130)</sup> |       |     | V <sub>OCM</sub> (V) <sup>(130)</sup> |       |         |       |

|----------------|-------|------------|-------|---------------------------------------|-------------------|-----|--------------------------|-----------------------------------|--------------------------------------|-------|-----|---------------------------------------|-------|---------|-------|

| i/O Standard   | Min   | Тур        | Max   | Min                                   | Condition         | Max | Min                      | Condition                         | Max                                  | Min   | Тур | Max                                   | Min   | Тур     | Max   |

| PCML           |       |            |       | -                                     |                   | -   | _                        | speed transceiv<br>Transceiver Pe |                                      |       |     |                                       |       | nitter, |       |

| 2.5 V<br>LVDS  | 2.375 | 2.5        | 2.625 | 100                                   | V <sub>CM</sub> = |     | 0.05                     | $D_{MAX} \le 700 \text{ Mbps}$    | 1.8                                  | 0.247 | _   | 0.6                                   | 1.125 | 1.25    | 1.375 |

| (131)          | 2.373 | 2.3        | 2.023 | 100                                   | 1.25 V            | _   | 1.05                     | D <sub>MAX</sub> > 700 Mbps       | 1.55                                 | 0.247 | _   | 0.6                                   | 1.125 | 1.25    | 1.375 |

| BLVDS<br>(132) | 2.375 | 2.5        | 2.625 | 100                                   | _                 | _   | _                        | _                                 | _                                    | _     | _   | _                                     | _     | _       | _     |

$<sup>^{\</sup>left(128\right)}\,$  Differential inputs are powered by VCCPD which requires 2.5 V.

<sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>(130)</sup> RL range:  $90 \le RL \le 110 \Omega$ .

<sup>(131)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.6 V for data rates above 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

<sup>(132)</sup> There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

| I/O Standard           | Vo    | clo (V) | (128) | V <sub>ID</sub> (mV) <sup>(129)</sup> |                          |     | V <sub>ICM(DC)</sub> (V) |                                | V <sub>OD</sub> (V) <sup>(130)</sup> |      |     | V <sub>OCM</sub> (V) <sup>(130)</sup> |     |     |     |

|------------------------|-------|---------|-------|---------------------------------------|--------------------------|-----|--------------------------|--------------------------------|--------------------------------------|------|-----|---------------------------------------|-----|-----|-----|

| 1/O Standard           | Min   | Тур     | Max   | Min                                   | Condition                | Max | Min                      | Condition                      | Max                                  | Min  | Тур | Max                                   | Min | Тур | Max |

| RSDS<br>(HIO)          | 2.375 | 2.5     | 2.625 | 100                                   | V <sub>CM</sub> = 1.25 V | _   | 0.3                      | _                              | 1.4                                  | 0.1  | 0.2 | 0.6                                   | 0.5 | 1.2 | 1.4 |

| Mini-<br>LVDS<br>(HIO) | 2.375 | 2.5     | 2.625 | 200                                   | _                        | 600 | 0.4                      | _                              | 1.325                                | 0.25 | _   | 0.6                                   | 1   | 1.2 | 1.4 |

| LVPECL                 | _     | _       | _     | 300                                   | _                        | _   | 0.6                      | D <sub>MAX</sub> ≤<br>700 Mbps | 1.8                                  | _    | _   | _                                     | _   | _   | _   |

| (135), (136)           | _     | _       | _     | 300                                   | _                        | _   | 1                        | D <sub>MAX</sub> > 700 Mbps    | 1.6                                  | _    | _   | _                                     | _   | _   | _   |

#### **Related Information**

**Glossary** on page 2-73

Altera Corporation

Arria V GZ Device Datasheet

<sup>(128)</sup> Differential inputs are powered by VCCPD which requires 2.5 V.

<sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>(130)</sup> RL range:  $90 \le RL \le 110 \Omega$ .

<sup>(133)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.45 V.

<sup>(134)</sup> For optimized Mini-LVDS receiver performance, the receiver voltage input range must be between 0.3 V to 1.425 V.

<sup>(135)</sup> LVPECL is only supported on dedicated clock input pins.

For optimized LVPECL receiver performance, the receiver voltage input range must be between 0.85 V to 1.75 V for data rate above 700 Mbps and 0.45 V to 1.95 V for data rate below 700 Mbps.

## **Switching Characteristics**

## **Transceiver Performance Specifications**

#### **Reference Clock**

#### Table 2-22: Reference Clock Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                               | Conditions                    | Transc                                                                              | eiver Speed | Grade 2 | Transce | eiver Speed | Grade 3 | Unit  |  |  |

|------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------|-------------|---------|---------|-------------|---------|-------|--|--|

| Symbol/Description                                               | Conditions                    | Min                                                                                 | Тур         | Max     | Min     | Тур         | Max     | Offic |  |  |

| Reference Clock                                                  |                               |                                                                                     |             |         |         |             |         |       |  |  |

| Supported I/O Standards                                          | Dedicated reference clock pin | 1.2-V PCML, 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, Differential LVPECL, LVDS, and HCSL |             |         |         |             |         |       |  |  |

|                                                                  | RX reference clock pin        | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS                                |             |         |         |             |         |       |  |  |

| Input Reference Clock<br>Frequency<br>(CMU PLL) (137)            | _                             | 40                                                                                  | _           | 710     | 40      | _           | 710     | MHz   |  |  |

| Input Reference Clock<br>Frequency<br>(ATX PLL) <sup>(137)</sup> | _                             | 100                                                                                 | _           | 710     | 100     | _           | 710     | MHz   |  |  |

$<sup>^{(137)}</sup>$  The input reference clock frequency options depend on the data rate and the device speed grade.

| Symbol/Description                                 | Conditions                  | Transce | eiver Speed ( | Grade 2 | Transce | eiver Speed ( | Grade 3 | Unit     |  |

|----------------------------------------------------|-----------------------------|---------|---------------|---------|---------|---------------|---------|----------|--|

| Symbol/Description                                 | Conditions                  | Min     | Тур           | Max     | Min     | Тур           | Max     | Offic    |  |

|                                                    | 100 Hz                      | _       | _             | -70     | _       | _             | -70     | dBc/Hz   |  |

|                                                    | 1 kHz                       | _       | _             | -90     | _       | _             | -90     | dBc/Hz   |  |

| Transmitter REFCLK Phase<br>Noise (622 MHz) (141)  | 10 kHz                      | _       | _             | -100    | _       | _             | -100    | dBc/Hz   |  |

| 1,000 (022 11112)                                  | 100 kHz                     | _       | _             | -110    | _       | _             | -110    | dBc/Hz   |  |

|                                                    | ≥1 MHz                      | _       | _             | -120    | _       | _             | -120    | dBc/Hz   |  |

| Transmitter REFCLK Phase<br>Jitter (100 MHz) (142) | 10 kHz to 1.5 MHz<br>(PCIe) | _       | _             | 3       | _       | _             | 3       | ps (rms) |  |

| R <sub>REF</sub>                                   | _                           | _       | 1800 ±1%      | _       | _       | 1800 ±1%      | _       | Ω        |  |

#### **Related Information**

#### Arria V Device Overview

For more information about device ordering codes.

#### **Transceiver Clocks**

### Table 2-23: Transceiver Clocks Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

To calculate the REFCLK phase noise requirement at frequencies other than 622 MHz, use the following formula: REFCLK phase noise at f(MHz) = REFCLK phase noise at

To calculate the REFCLK rms phase jitter requirement for PCIe at reference clock frequencies other than 100 MHz, use the following formula: REFCLK rms phase jitter at f(MHz) = REFCLK rms phase jitter at  $100 MHz \times 100/f$ .

| Symbol/Description                   | Conditions                                           | Trans | ceiver Spee | d Grade 2 | Transc | eiver Spe | ed Grade 3 | Unit  |

|--------------------------------------|------------------------------------------------------|-------|-------------|-----------|--------|-----------|------------|-------|

| symbol/Description                   | Collattions                                          | Min   | Тур         | Max       | Min    | Тур       | Max        | Offic |

|                                      | $V_{CCR\_GXB} = 0.85 \text{ V}$ full bandwidth       | _     | 600         | _         | _      | 600       | _          | mV    |

| $ m V_{ICM}$ (AC and DC coupled)     | $V_{CCR\_GXB} = 0.85 \text{ V}$<br>half bandwidth    | _     | 600         | _         | _      | 600       | _          | mV    |

| V <sub>ICM</sub> (AC and DC coupled) | $V_{CCR\_GXB} = 1.0 \text{ V}$ full bandwidth        | _     | 700         | _         | _      | 700       | _          | mV    |

|                                      | $V_{CCR\_GXB} = 1.0 \text{ V}$<br>half bandwidth     | _     | 700         | _         | _      | 700       | _          | mV    |

| t <sub>LTR</sub> (149)               | _                                                    | _     | _           | 10        | _      | _         | 10         | μs    |

| t <sub>LTD</sub> (150)               | _                                                    | 4     | _           | _         | 4      | _         | _          | μs    |

| t <sub>LTD_manual</sub> (151)        | _                                                    | 4     | _           | _         | 4      | _         | _          | μs    |

| t <sub>LTR_LTD_manual</sub> (152)    | _                                                    | 15    | _           | _         | 15     | _         | _          | μs    |

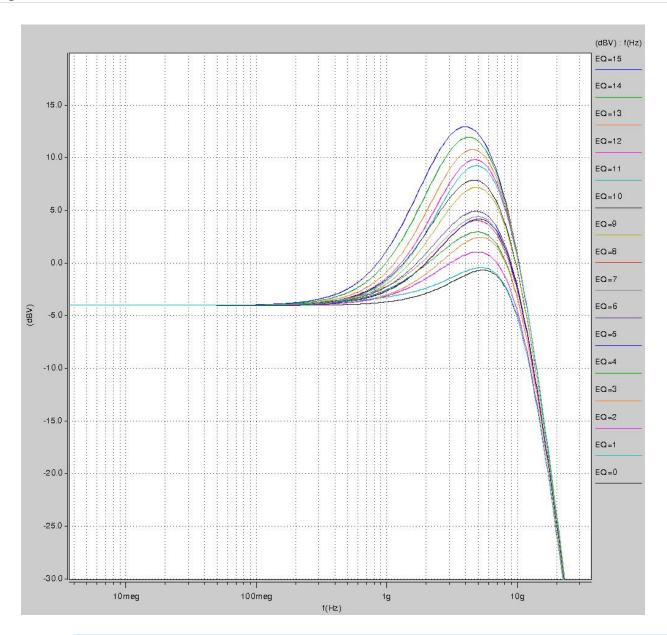

| Programmable equalization (AC Gain)  | Full bandwidth (6.25 GHz) Half bandwidth (3.125 GHz) | _     | _           | 16        | _      | _         | 16         | dB    |

Altera Corporation

Arria V GZ Device Datasheet

$<sup>^{(149)}</sup>$   $t_{LTR}$  is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

<sup>(150)</sup> t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

$t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{LTR\_LTD\_manual}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

|                    |                           | ATX PLL               |                                                                                                       |                           | CMU PLL (161)         |                                                | fPLL                      |                       |                                                      |  |

|--------------------|---------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|------------------------------------------------|---------------------------|-----------------------|------------------------------------------------------|--|

| Clock Network      | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                                                                       | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                      |  |

| xN (PCIe)          | _                         | 8.0                   | 8                                                                                                     | _                         | 5.0                   | 8                                              | _                         | _                     | _                                                    |  |

| xN (Native PHY IP) | 8.0                       | 8.01 to<br>9.8304     | Up to 13<br>channels<br>above and<br>below PLL<br>Up to 7<br>channels<br>above<br>and<br>below<br>PLL | 7.99                      | 7.99                  | Up to 13<br>channels<br>above and<br>below PLL | 3.125                     | 3.125                 | Up to 13<br>channels<br>above<br>and<br>below<br>PLL |  |

#### **Standard PCS Data Rate**

## Table 2-30: Standard PCS Approximate Maximum Date Rate (Gbps) for Arria V GZ Devices

The maximum data rate is also constrained by the transceiver speed grade. Refer to the "Commercial and Industrial Speed Grade Offering for Arria V GZ Devices" table for the transceiver speed grade.

| Mode <sup>(164)</sup> | Transceiver | PMA Width                  | 20  | 20  | 16   | 16   | 10  | 10  | 8    | 8    |

|-----------------------|-------------|----------------------------|-----|-----|------|------|-----|-----|------|------|

|                       | Speed Grade | PCS/Core Width             | 40  | 20  | 32   | 16   | 20  | 10  | 16   | 8    |

| FIFO                  | 2           | C3, I3L core speed grade   | 9.9 | 9   | 7.84 | 7.2  | 5.3 | 4.7 | 4.24 | 3.76 |

| THO                   | 3           | C4, I4<br>core speed grade | 8.8 | 8.2 | 7.2  | 6.56 | 4.8 | 4.3 | 3.84 | 3.44 |

<sup>(161)</sup> ATX PLL is recommended at 8 Gbps and above data rates for improved jitter performance.

Altera Corporation

Arria V GZ Device Datasheet

<sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

Figure 2-2: AC Gain Curves for Arria V GZ Channels (full bandwidth)

Altera Corporation Arria V GZ Device Datasheet

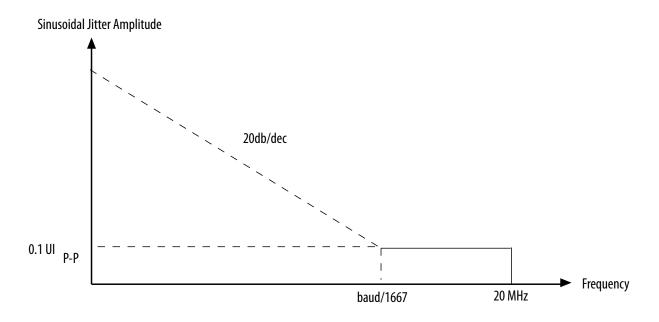

Figure 2-5: LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate < 1.25 Gbps

## Non DPA Mode High-Speed I/O Specifications

### Table 2-46: High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol          | Conditions | C3, I3L |     |     |     | Unit |     |       |

|-----------------|------------|---------|-----|-----|-----|------|-----|-------|

| Syllibol        | Conditions | Min     | Тур | Max | Min | Тур  | Max | Offic |

| Sampling Window | _          | _       | _   | 300 | _   | _    | 300 | ps    |

**Altera Corporation** Arria V GZ Device Datasheet

## **DLL Range Specifications**

#### Table 2-47: DLL Range Specifications for Arria V GZ Devices

Arria V GZ devices support memory interface frequencies lower than 300 MHz, although the reference clock that feeds the DLL must be at least 300 MHz. To support interfaces below 300 MHz, multiply the reference clock feeding the DLL to ensure the frequency is within the supported range of the DLL.

| Parameter                     | C3, I3L   | C4, I4    | Unit |

|-------------------------------|-----------|-----------|------|

| DLL operating frequency range | 300 – 890 | 300 – 890 | MHz  |

### **DQS Logic Block Specifications**

#### Table 2-48: DQS Phase Offset Delay Per Setting for Arria V GZ Devices

The typical value equals the average of the minimum and maximum values.

The delay settings are linear with a cumulative delay variation of 40 ps for all speed grades. For example, when using a -3 speed grade and applying a 10-phase offset setting to a 90° phase shift at 400 MHz, the expected average cumulative delay is  $[625 \text{ ps} + (10 \times 11 \text{ ps}) \pm 20 \text{ ps}] = 735 \text{ ps} \pm 20 \text{ ps}$ .

| Speed Grade | Min | Max | Unit |

|-------------|-----|-----|------|

| C3, I3L     | 8   | 15  | ps   |

| C4, I4      | 8   | 16  | ps   |

## Table 2-49: DQS Phase Shift Error Specification for DLL-Delayed Clock (t<sub>DQS\_PSERR</sub>) for Arria V GZ Devices

This error specification is the absolute maximum and minimum error. For example, skew on three DQS delay buffers in a -3 speed grade is  $\pm 84$  ps or  $\pm 42$  ps.

| Number of DQS Delay Buffers | C3, I3L C4, I4 |    | Unit |

|-----------------------------|----------------|----|------|

| 1                           | 30             | 32 | ps   |

| 2                           | 60             | 64 | ps   |

| 3                           | 90             | 96 | ps   |

Table 2-57: FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is >1

Use these timing parameters when you use the decompression and design security features.

| Symbol                              | Parameter                                    | Minimum                     | Maximum     | Unit |

|-------------------------------------|----------------------------------------------|-----------------------------|-------------|------|

| $t_{CF2CD}$                         | nconfig low to conf_done low                 | _                           | 600         | ns   |

| t <sub>CF2ST0</sub>                 | nconfig low to nstatus low                   | _                           | 600         | ns   |

| t <sub>CFG</sub>                    | nconfig low pulse width                      | 2                           | _           | μs   |

| t <sub>STATUS</sub>                 | nstatus low pulse width                      | 268                         | 1,506 (210) | μs   |

| t <sub>CF2ST1</sub>                 | nconfig high to nstatus high                 | _                           | 1,506 (211) | μs   |

| t <sub>CF2CK</sub> (212)            | nconfig high to first rising edge on DCLK    | 1,506                       | _           | μs   |

| t <sub>ST2CK</sub> <sup>(212)</sup> | nstatus high to first rising edge of DCLK    | 2                           | _           | μs   |

| $t_{ m DSU}$                        | DATA[] setup time before rising edge on DCLK | 5.5                         | _           | ns   |

| t <sub>DH</sub>                     | DATA[] hold time after rising edge on DCLK   | N-1/f <sub>DCLK</sub> (213) | _           | S    |

| $t_{CH}$                            | DCLK high time                               | $0.45 \times 1/f_{MAX}$     | _           | S    |

| $t_{ m CL}$                         | DCLK low time                                | $0.45 \times 1/f_{MAX}$     | _           | s    |

| $t_{ m CLK}$                        | DCLK period                                  | 1/f <sub>MAX</sub>          | _           | S    |

| f <sub>MAY</sub>                    | DCLK frequency (FPP ×8/×16)                  | _                           | 125         | MHz  |

|                                     | DCLK frequency (FPP ×32)                     | _                           | 100         | MHz  |

| t <sub>R</sub>                      | Input rise time                              | _                           | 40          | ns   |

| $t_{\mathrm{F}}$                    | Input fall time                              | _                           | 40          | ns   |

| t <sub>CD2UM</sub>                  | CONF_DONE high to user mode (214)            | 175                         | 437         | μs   |

<sup>(210)</sup> You can obtain this value if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>(211)</sup> You can obtain this value if you do not delay configuration by externally holding the nSTATUS low.

$<sup>^{(212)}</sup>$  If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

$<sup>^{(213)}</sup>$  N is the DCLK-to-DATA ratio and  $f_{DCLK}$  is the DCLK frequency the system is operating.

The minimum and maximum numbers apply only if you use the internal oscillator as the clock source for initializing the device.