Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 14151                                                      |

| Number of Logic Elements/Cells | 300000                                                     |

| Total RAM Bits                 | 17358848                                                   |

| Number of I/O                  | 544                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA Exposed Pad                               |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxmb1g6f35c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Operating Conditions                                                                                                                                                                             | 2-1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Operating Conditions  Switching Characteristics  Transceiver Performance Specifications  Core Performance Specifications  Periphery Performance  Configuration Specification  POR Specifications | 2-21 |

| Transceiver Performance Specifications                                                                                                                                                           | 2-21 |

| Core Performance Specifications                                                                                                                                                                  | 2-37 |

| Periphery Performance                                                                                                                                                                            | 2-44 |

| Configuration Specification                                                                                                                                                                      | 2-56 |

| POR Specifications                                                                                                                                                                               | 2-56 |

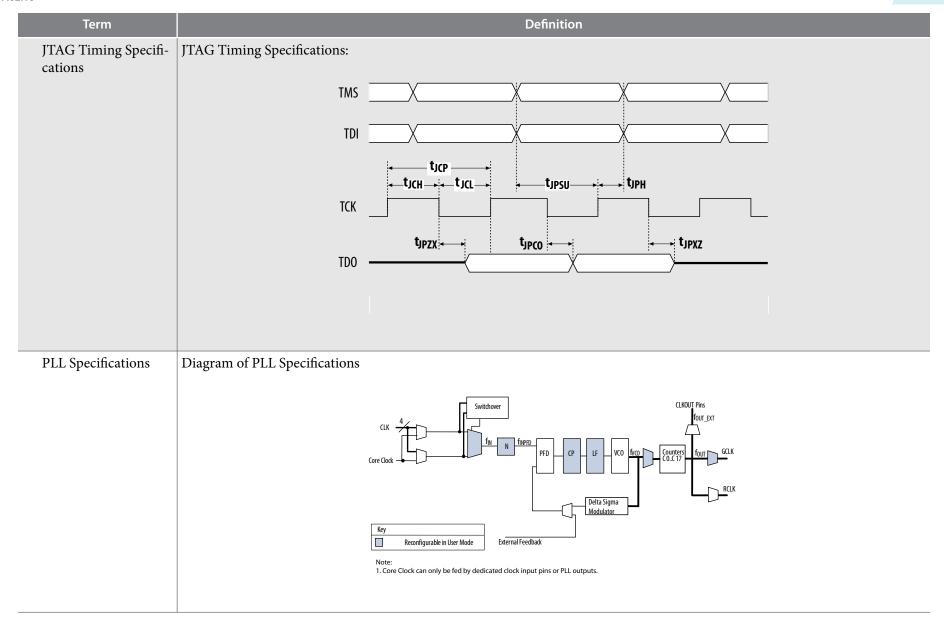

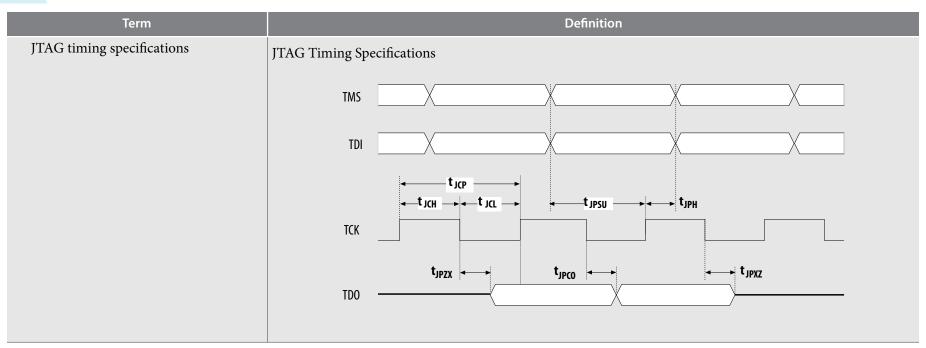

| JTAG Configuration Specifications                                                                                                                                                                | 2-57 |

| Fast Passive Parallel (FPP) Configuration Timing                                                                                                                                                 | 2-57 |

| Active Serial Configuration Timing                                                                                                                                                               | 2-65 |

| Active Serial Configuration Timing Passive Serial Configuration Timing                                                                                                                           | 2-67 |

| Initialization                                                                                                                                                                                   | 2-69 |

| Initialization                                                                                                                                                                                   | 2-69 |

| Remote System Upgrades Circuitry Timing Specification                                                                                                                                            | 2-70 |

| User Watchdog Internal Oscillator Frequency Specification                                                                                                                                        | 2-71 |

| User Watchdog Internal Oscillator Frequency Specification                                                                                                                                        | 2-71 |

| Programmable IOE Delay                                                                                                                                                                           | 2-72 |

| Programmable Output Buffer Delay                                                                                                                                                                 | 272. |

| Glossary                                                                                                                                                                                         | 2-73 |

| Document Revision History                                                                                                                                                                        | 2-78 |

|                                                                                                                                                                                                  |      |

## Arria V GX, GT, SX, and ST Device Datasheet

1

2017.02.10

AV-51002

This datasheet describes the electrical characteristics, switching characteristics, configuration specifications, and I/O timing for Arria<sup>®</sup> V devices.

Arria V devices are offered in commercial and industrial grades. Commercial devices are offered in -C4 (fastest), -C5, and -C6 speed grades. Industrial grade devices are offered in the -I3 and -I5 speed grades.

#### Related Information

**Arria V Device Overview**

Provides more information about the densities and packages of devices in the Arria V family.

### **Electrical Characteristics**

The following sections describe the operating conditions and power consumption of Arria V devices.

### **Operating Conditions**

Arria V devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Arria V devices, you must consider the operating requirements described in this section.

#### **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Arria V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms.

The functional operation of the device is not implied for these conditions.

© 2017 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, NIOS, Quartus and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

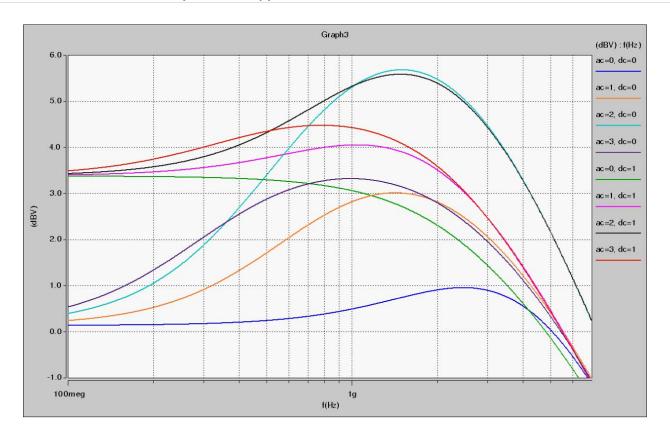

### CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain

Figure 1-3: CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

## Typical TX $V_{\text{OD}}$ Setting for Arria V Transceiver Channels with termination of 100 $\Omega$

Table 1-32: Typical TX  $V_{\text{OD}}$  Setting for Arria V Transceiver Channels with termination of 100  $\Omega$

| Symbol                                               | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|------------------------------------------------------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|                                                      | 6 <sup>(59)</sup>                       | 120                        | 34                                      | 680                        |

|                                                      | 7 <sup>(59)</sup>                       | 140                        | 35                                      | 700                        |

|                                                      | 8 <sup>(59)</sup>                       | 160                        | 36                                      | 720                        |

|                                                      | 9                                       | 180                        | 37                                      | 740                        |

|                                                      | 10                                      | 200                        | 38                                      | 760                        |

|                                                      | 11                                      | 220                        | 39                                      | 780                        |

|                                                      | 12                                      | 240                        | 40                                      | 800                        |

|                                                      | 13                                      | 260                        | 41                                      | 820                        |

|                                                      | 14                                      | 280                        | 42                                      | 840                        |

| V <sub>OD</sub> differential peak-to-peak<br>typical | 15                                      | 300                        | 43                                      | 860                        |

| -,, r · · ·                                          | 16                                      | 320                        | 44                                      | 880                        |

|                                                      | 17                                      | 340                        | 45                                      | 900                        |

|                                                      | 18                                      | 360                        | 46                                      | 920                        |

|                                                      | 19                                      | 380                        | 47                                      | 940                        |

|                                                      | 20                                      | 400                        | 48                                      | 960                        |

|                                                      | 21                                      | 420                        | 49                                      | 980                        |

|                                                      | 22                                      | 440                        | 50                                      | 1000                       |

|                                                      | 23                                      | 460                        | 51                                      | 1020                       |

|                                                      | 24                                      | 480                        | 52                                      | 1040                       |

<sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

<sup>(59)</sup> Only valid for data rates  $\leq$  5 Gbps.

|                  | Symbol                                                    | Condition                                            |      | −I3, −C4 |       |      | −l5, −C5 |       | -C6  |     |       | Unit  |

|------------------|-----------------------------------------------------------|------------------------------------------------------|------|----------|-------|------|----------|-------|------|-----|-------|-------|

|                  | Зупівої                                                   | Condition                                            | Min  | Тур      | Max   | Min  | Тур      | Max   | Min  | Тур | Max   | Offic |

|                  | TCCS                                                      | True Differential I/O<br>Standards                   | _    | _        | 150   | _    | _        | 150   | _    | _   | 150   | ps    |

|                  | 1003                                                      | Emulated Differential I/O Standards                  |      | _        | 300   | _    | _        | 300   | _    | _   | 300   | ps    |

|                  | True Differential I/O<br>Standards - f <sub>HSDRDPA</sub> | SERDES factor J =3 to 10 <sup>(76)</sup>             | 150  | _        | 1250  | 150  | _        | 1250  | 150  | _   | 1050  | Mbps  |

|                  | (data rate)                                               | SERDES factor $J \ge 8$ with DPA <sup>(76)(78)</sup> | 150  | _        | 1600  | 150  | _        | 1500  | 150  | _   | 1250  | Mbps  |

| Receiver         |                                                           | SERDES factor J = 3<br>to 10                         | (77) | _        | (83)  | (77) | _        | (83)  | (77) | _   | (83)  | Mbps  |

|                  | f <sub>HSDR</sub> (data rate)                             | SERDES factor J = 1<br>to 2, uses DDR<br>registers   | (77) | _        | (79)  | (77) | _        | (79)  | (77) | _   | (79)  | Mbps  |

| DPA Mode         | DPA run length                                            | _                                                    | _    | _        | 10000 | _    | _        | 10000 | _    | _   | 10000 | UI    |

| Soft-CDR<br>Mode | Soft-CDR ppm tolerance                                    | _                                                    | _    | _        | 300   | _    | _        | 300   | _    | _   | 300   | ±ppm  |

| Non-DPA<br>Mode  | Sampling Window                                           | _                                                    | _    | _        | 300   | _    | _        | 300   | _    | _   | 300   | ps    |

You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

### **Memory Output Clock Jitter Specifications**

### Table 1-45: Memory Output Clock Jitter Specifications for Arria V Devices

The memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2/DDR3 SDRAM standard. The memory output clock jitter is applicable when an input jitter of 30 ps (p-p) is applied with bit error rate (BER)  $10^{-12}$ , equivalent to 14 sigma. Altera recommends using the UniPHY intellectual property (IP) with PHYCLK connections for better jitter performance.

| Parameter                    | Clock Network | Symbol                | -l3, | -C4 | −I5, | -C5 | -(  | <b>C6</b> | Unit |

|------------------------------|---------------|-----------------------|------|-----|------|-----|-----|-----------|------|

|                              | Clock Network | Зуппоп                | Min  | Max | Min  | Max | Min | Max       | Onic |

| Clock period jitter          | PHYCLK        | t <sub>JIT(per)</sub> | -41  | 41  | -50  | 50  | -55 | 55        | ps   |

| Cycle-to-cycle period jitter | PHYCLK        | t <sub>JIT(cc)</sub>  | 6    | 3   | 9    | 0   | 9   | 4         | ps   |

### **OCT Calibration Block Specifications**

Table 1-46: OCT Calibration Block Specifications for Arria V Devices

| Symbol                | Description                                                                                                                                                 | Min | Тур  | Max | Unit   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by OCT calibration blocks                                                                                                                    | _   | _    | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of octusrclk clock cycles required for $R_{S}$ OCT/ $\!R_{T}$ OCT calibration                                                                        | _   | 1000 | _   | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for OCT code to shift out                                                                                         | _   | 32   | _   | Cycles |

| $T_{RS\_RT}$          | Time required between the $dyn\_term\_ctrl$ and $oe$ signal transitions in a bidirectional I/O buffer to dynamically switch between $R_S$ OCT and $R_T$ OCT | _   | 2.5  | _   | ns     |

#### **HPS PLL Input Jitter**

Use the following equation to determine the maximum input jitter (peak-to-peak) the HPS PLLs can tolerate. The divide value (N) is the value programmed into the denominator field of the VCO register for each PLL. The PLL input reference clock is divided by this value. The range of the denominator is 1 to 64.

Maximum input jitter = Input clock period  $\times$  Divide value (N)  $\times$  0.02

**Table 1-50: Examples of Maximum Input Jitter**

| Input Reference Clock Period | Divide Value (N) | Maximum Jitter | Unit |

|------------------------------|------------------|----------------|------|

| 40 ns                        | 1                | 0.8            | ns   |

| 40 ns                        | 2                | 1.6            | ns   |

| 40 ns                        | 4                | 3.2            | ns   |

### **Quad SPI Flash Timing Characteristics**

Table 1-51: Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Arria V Devices

| Symbol                 | Description                                        | Min  | Тур                      | Max                                                  | Unit |

|------------------------|----------------------------------------------------|------|--------------------------|------------------------------------------------------|------|

| F <sub>clk</sub>       | SCLK_OUT clock frequency (External clock)          | _    | _                        | 108                                                  | MHz  |

| $T_{qspi\_clk}$        | QSPI_CLK clock period (Internal reference clock)   | 2.32 | _                        | _                                                    | ns   |

| T <sub>dutycycle</sub> | SCLK_OUT duty cycle                                | 45   | _                        | 55                                                   | %    |

| $T_{dssfrst}$          | Output delay QSPI_SS valid before first clock edge | _    | 1/2 cycle of<br>SCLK_OUT | _                                                    | ns   |

| $T_{dsslst}$           | Output delay QSPI_SS valid after last clock edge   | -1   | _                        | 1                                                    | ns   |

| $T_{ m dio}$           | I/O data output delay                              | -1   | _                        | 1                                                    | ns   |

| T <sub>din_start</sub> | Input data valid start                             | _    | _                        | $(2 + R_{delay}) \times T_{qspi\_clk} - 7.52^{(85)}$ | ns   |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

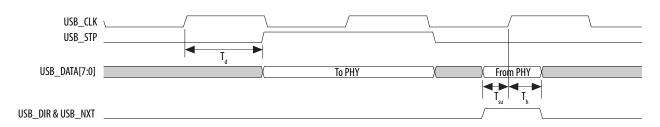

Figure 1-12: USB Timing Diagram

### **Ethernet Media Access Controller (EMAC) Timing Characteristics**

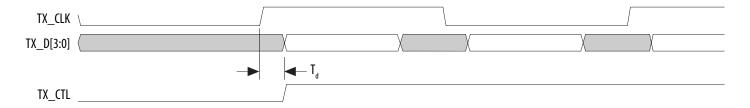

Table 1-56: Reduced Gigabit Media Independent Interface (RGMII) TX Timing Requirements for Arria V Devices

| Symbol                        | Description                            | Min   | Тур | Max  | Unit |

|-------------------------------|----------------------------------------|-------|-----|------|------|

| T <sub>clk</sub> (1000Base-T) | TX_CLK clock period                    | _     | 8   | _    | ns   |

| T <sub>clk</sub> (100Base-T)  | TX_CLK clock period                    | _     | 40  | _    | ns   |

| T <sub>clk</sub> (10Base-T)   | TX_CLK clock period                    | _     | 400 | _    | ns   |

| T <sub>dutycycle</sub>        | TX_CLK duty cycle                      | 45    | _   | 55   | %    |

| $T_d$                         | TX_CLK to TXD/TX_CTL output data delay | -0.85 | _   | 0.15 | ns   |

Figure 1-13: RGMII TX Timing Diagram

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

AV-51002 2017.02.10

| Term                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Definition                 |              |                     |  |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------|---------------------|--|--|--|--|--|

| Single-ended voltage referenced I/O standard | The JEDEC standard for the SSTL and HSTL I/O defines both the AC and DC input sign values indicate the voltage levels at which the receiver must meet its timing specification indicate the voltage levels at which the final logic state of the receiver is unambiguously or receiver input has crossed the AC value, the receiver changes to the new logic state.  The new logic state is then maintained as long as the input stays beyond the DC threshol is intended to provide predictable receiver timing in the presence of input waveform ring Single-Ended Voltage Referenced I/O Standard |                            |              |                     |  |  |  |  |  |

|                                              | Single-Ended voltage Referenced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1/O Standard               |              |                     |  |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |              | V <sub>CC10</sub>   |  |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |              |                     |  |  |  |  |  |

|                                              | V <sub>OH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |              | V <sub>IH(AC)</sub> |  |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |              | V <sub>IH(DC)</sub> |  |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V REF                      |              | V <sub>IL(DC)</sub> |  |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |              | V IL(AC)            |  |  |  |  |  |

|                                              | V <sub>0L</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |              |                     |  |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |              | V <sub>SS</sub>     |  |  |  |  |  |

| $t_{\rm C}$                                  | High-speed receiver/transmitter input and output clock period.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |              |                     |  |  |  |  |  |

| TCCS (channel-to-channel-skew)               | The timing difference between the fastest and slowest output edges, including the $t_{\rm CO}$ variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table).                                                                                                                                                                                                                                                                                                                          |                            |              |                     |  |  |  |  |  |

| $t_{ m DUTY}$                                | High-speed I/O block—Duty cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e on high-speed transmitte | r output clo | ock.                |  |  |  |  |  |

Arria V GX, GT, SX, and ST Device Datasheet **Altera Corporation**

### **Bus Hold Specifications**

Table 2-9: Bus Hold Parameters for Arria V GZ Devices

|                              |                   |                                                              |       |      |       |      | V <sub>C</sub> | CIO        |       |      |       |      |      |

|------------------------------|-------------------|--------------------------------------------------------------|-------|------|-------|------|----------------|------------|-------|------|-------|------|------|

| Parameter                    | Symbol            | Conditions                                                   | 1.2   | 2 V  | 1.5   | 5 V  | 1.8            | 8 <b>V</b> | 2.    | 5 V  | 3.0   | V    | Unit |

|                              |                   |                                                              | Min   | Max  | Min   | Max  | Min            | Max        | Min   | Max  | Min   | Max  |      |

| Low<br>sustaining<br>current | $I_{SUSL}$        | V <sub>IN</sub> > V <sub>IL</sub> (maximum)                  | 22.5  | _    | 25.0  | _    | 30.0           | _          | 50.0  | _    | 70.0  | _    | μΑ   |

| High sustaining current      | $I_{SUSH}$        | $\begin{aligned} V_{IN} < V_{IH} \\ (minimum) \end{aligned}$ | -22.5 | _    | -25.0 | _    | -30.0          | _          | -50.0 | _    | -70.0 | _    | μА   |

| Low<br>overdrive<br>current  | $I_{ODL}$         | $0V < V_{IN} < V_{CCIO}$                                     | _     | 120  | _     | 160  | _              | 200        | _     | 300  | _     | 500  | μА   |

| High<br>overdrive<br>current | $I_{ODH}$         | 0V < V <sub>IN</sub> < V <sub>CCIO</sub>                     | _     | -120 | _     | -160 | _              | -200       | _     | -300 | _     | -500 | μΑ   |

| Bus-hold<br>trip point       | V <sub>TRIP</sub> | _                                                            | 0.45  | 0.95 | 0.50  | 1.00 | 0.68           | 1.07       | 0.70  | 1.70 | 0.80  | 2.00 | V    |

### On-Chip Termination (OCT) Specifications

If you enable OCT calibration, calibration is automatically performed at power-up for I/Os connected to the calibration block.

### Table 2-10: OCT Calibration Accuracy Specifications for Arria V GZ Devices

OCT calibration accuracy is valid at the time of calibration only.

Altera Corporation

Arria V GZ Device Datasheet

| Symbol | Description                                           | V <sub>CCIO</sub> (V) | Typical | Unit |  |

|--------|-------------------------------------------------------|-----------------------|---------|------|--|

|        |                                                       | 3.0                   | 0.0297  |      |  |

|        |                                                       | 2.5                   | 0.0344  |      |  |

| dR/dV  | OCT variation with voltage without re-calibration     | 1.8                   | 0.0499  | %/mV |  |

|        |                                                       | 1.5                   | 0.0744  |      |  |

|        |                                                       | 1.2                   | 0.1241  |      |  |

|        |                                                       | 3.0                   | 0.189   |      |  |

|        |                                                       | 2.5                   | 0.208   |      |  |

| dR/dT  | OCT variation with temperature without re-calibration | 1.8                   | 0.266   | %/°C |  |

|        |                                                       | 1.5                   | 0.273   |      |  |

|        |                                                       | 1.2                   | 0.317   |      |  |

### **Pin Capacitance**

Table 2-13: Pin Capacitance for Arria V GZ Devices

| Symbol      | Description                                                      | Maximum | Unit |

|-------------|------------------------------------------------------------------|---------|------|

| $C_{IOTB}$  | Input capacitance on the top and bottom I/O pins                 | 6       | pF   |

| $C_{IOLR}$  | Input capacitance on the left and right I/O pins                 | 6       | pF   |

| $C_{OUTFB}$ | Input capacitance on dual-purpose clock output and feedback pins | 6       | pF   |

### **Hot Socketing**

Table 2-14: Hot Socketing Specifications for Arria V GZ Devices

| Symbol                    | Description                                | Maximum               |

|---------------------------|--------------------------------------------|-----------------------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                     | 300 μΑ                |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                     | 8 mA <sup>(124)</sup> |

| I <sub>XCVR-TX (DC)</sub> | DC current per transceiver transmitter pin | 100 mA                |

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver pin    | 50 mA                 |

#### **Internal Weak Pull-Up Resistor**

### Table 2-15: Internal Weak Pull-Up Resistor for Arria V GZ Devices

All I/O pins have an option to enable the weak pull-up resistor except the configuration, test, and JTAG pins. The internal weak pull-down feature is only available for the JTAG TCK pin. The typical value for this internal weak pull-down resistor is approximately 25 k $\Omega$ .

| Symbol   | Description                                                             | V <sub>CCIO</sub> Conditions (V) (125) | Value (126) | Unit |

|----------|-------------------------------------------------------------------------|----------------------------------------|-------------|------|

|          |                                                                         | 3.0 ±5%                                | 25          | kΩ   |

|          |                                                                         | 2.5 ±5%                                | 25          | kΩ   |

|          | Value of the I/O pin pull-up resistor                                   | 1.8 ±5%                                | 25          | kΩ   |

| $R_{PU}$ | before and during configuration, as well as user mode if you enable the | 1.5 ±5%                                | 25          | kΩ   |

|          | programmable pull-up resistor option.                                   | 1.35 ±5%                               | 25          | kΩ   |

|          |                                                                         | 1.25 ±5%                               | 25          | kΩ   |

|          |                                                                         | 1.2 ±5%                                | 25          | kΩ   |

The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{\rm IOPIN}| = C \, dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

Altera Corporation

Arria V GZ Device Datasheet

The pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{\rm CCIO}$ .

$<sup>^{(126)}</sup>$  These specifications are valid with a  $\pm 10\%$  tolerance to cover changes over PVT.

### **I/O Standard Specifications**

The  $V_{OL}$  and  $V_{OH}$  values are valid at the corresponding  $I_{OH}$  and  $I_{OL}$ , respectively.

Table 2-16: Single-Ended I/O Standards for Arria V GZ Devices

| I/O Standard  |       | V <sub>CCIO</sub> (V) |       | V <sub>II</sub> | _(V)                                                       | V <sub>IH</sub>            | (V)                     | V <sub>OL</sub> (V)                                        | V <sub>OH</sub> (V)           | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) |  |

|---------------|-------|-----------------------|-------|-----------------|------------------------------------------------------------|----------------------------|-------------------------|------------------------------------------------------------|-------------------------------|----------------------|----------------------|--|

| i/O Staildaid | Min   | Тур                   | Max   | Min             | Max                                                        | Min                        | Max                     | Max                                                        | Min                           | IOL (IIIA)           | •ОП (****,*)         |  |

| LVTTL         | 2.85  | 3                     | 3.15  | -0.3            | 0.8                                                        | 1.7                        | 3.6                     | 0.4                                                        | 2.4                           | 2                    | -2                   |  |

| LVCMOS        | 2.85  | 3                     | 3.15  | -0.3            | 0.8                                                        | 1.7                        | 3.6                     | 0.2                                                        | V <sub>CCIO</sub> - 0.2       | 0.1                  | -0.1                 |  |

| 2.5 V         | 2.375 | 2.5                   | 2.625 | -0.3            | 0.7                                                        | 1.7                        | 3.6                     | 0.4                                                        | 2                             | 1                    | -1                   |  |

| 1.8 V         | 1.71  | 1.8                   | 1.89  | -0.3            | $0.35 \times V_{\rm CCIO}$                                 | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | 0.45                                                       | V <sub>CCIO</sub> - 0.45      | 2                    | -2                   |  |

| 1.5 V         | 1.425 | 1.5                   | 1.575 | -0.3            | $0.35 \times V_{\rm CCIO}$                                 | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | $\begin{array}{c} 0.25 \times \\ V_{\rm CCIO} \end{array}$ | $0.75 \times V_{\text{CCIO}}$ | 2                    | -2                   |  |

| 1.2 V         | 1.14  | 1.2                   | 1.26  | -0.3            | $\begin{array}{c} 0.35 \times \\ V_{\rm CCIO} \end{array}$ | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | $\begin{array}{c} 0.25 \times \\ V_{\rm CCIO} \end{array}$ | $0.75 \times V_{\text{CCIO}}$ | 2                    | -2                   |  |

Table 2-17: Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Arria V GZ Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>REF</sub> (V)   |                                                           |                            |                                                        | <sub>TT</sub> (V) |                         |

|------------------------|-------|-----------------------|-------|------------------------|-----------------------------------------------------------|----------------------------|--------------------------------------------------------|-------------------|-------------------------|

| i/O Standard           | Min   | Тур                   | Max   | Min                    | Тур                                                       | Max                        | Min                                                    | Тур               | Max                     |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                   | 2.625 | $0.49 \times V_{CCIO}$ | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} \end{array}$ | $0.51 \times V_{\rm CCIO}$ | V <sub>REF</sub> - 0.04                                | $V_{REF}$         | V <sub>REF</sub> + 0.04 |

| SSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.833                  | 0.9                                                       | 0.969                      | V <sub>REF</sub> - 0.04                                | $V_{REF}$         | V <sub>REF</sub> + 0.04 |

| SSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | $0.49 \times V_{CCIO}$ | $0.5 \times V_{\rm CCIO}$                                 | $0.51 \times V_{\rm CCIO}$ | $\begin{array}{c} 0.49 \times \\ V_{CCIO} \end{array}$ | 0.5 ×<br>VCCIO    | $0.51 \times V_{CCIO}$  |

| I/O Standard           |      | V <sub>CCIO</sub> (\ | <b>/</b> ) | V <sub>DIF</sub> | <sub>(DC)</sub> (V)     | $V_{X(AC)}(V)$                       |                       | V <sub>CM(DC)</sub> (V)             |                           |                                   | V <sub>DIF(AC)</sub> (V)     |      |                             |

|------------------------|------|----------------------|------------|------------------|-------------------------|--------------------------------------|-----------------------|-------------------------------------|---------------------------|-----------------------------------|------------------------------|------|-----------------------------|

| i/O Standard           | Min  | Тур                  | Max        | Min              | Max                     | Min                                  | Тур                   | Max                                 | Min                       | Тур                               | Max                          | Min  | Max                         |

| HSTL-12 Class<br>I, II | 1.14 | 1.2                  | 1.26       | 0.16             | V <sub>CCIO</sub> + 0.3 | _                                    | $0.5 \times V_{CCIO}$ | _                                   | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub><br>IO | $0.6 \times V_{\text{CCIO}}$ | 0.3  | V <sub>CCIO</sub><br>+ 0.48 |

| HSUL-12                | 1.14 | 1.2                  | 1.3        | 0.26             | 0.26                    | 0.5 ×<br>V <sub>CCIO</sub> –<br>0.12 | $0.5 \times V_{CCIO}$ | $0.5 \times V_{\rm CCIO} \\ + 0.12$ | $0.4 \times V_{\rm CCIO}$ | 0.5<br>×<br>V <sub>CC</sub>       | 0.6 ×<br>V <sub>CCIO</sub>   | 0.44 | 0.44                        |

Table 2-21: Differential I/O Standard Specifications for Arria V GZ Devices

| I/O Standard   | I/O Standard                                                                                                                                                                                                                                          |     | 128)  | V <sub>ID</sub> (mV) <sup>(129)</sup> |                   |     | V <sub>ICM(DC)</sub> (V) |                                |      | V <sub>OD</sub> (V) (130) |     |     | V <sub>OCM</sub> (V) (130) |      |       |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------------------------------------|-------------------|-----|--------------------------|--------------------------------|------|---------------------------|-----|-----|----------------------------|------|-------|

| i/O Standard   | Min                                                                                                                                                                                                                                                   | Тур | Max   | Min                                   | Condition         | Max | Min                      | Condition                      | Max  | Min                       | Тур | Max | Min                        | Тур  | Max   |

| PCML           | Transmitter, receiver, and input reference clock pins of the high-speed transceivers use the PCML I/O standard. For transmitter, receiver, and reference clock I/O pin specifications, refer to the "Transceiver Performance Specifications" section. |     |       |                                       |                   |     |                          |                                |      |                           |     |     |                            |      |       |

| 2.5 V<br>LVDS  | 2.375                                                                                                                                                                                                                                                 | 2.5 | 2.625 | 100                                   | V <sub>CM</sub> = | _   | 0.05                     | D <sub>MAX</sub> ≤<br>700 Mbps | 1.8  | 0.247                     | _   | 0.6 | 1.125                      | 1.25 | 1.375 |

| (131)          | 2.373                                                                                                                                                                                                                                                 | 2.3 | 2.023 | 100                                   | 1.25 V            | _   | 1.05                     | D <sub>MAX</sub> > 700 Mbps    | 1.55 | 0.247                     | _   | 0.6 | 1.125                      | 1.25 | 1.375 |

| BLVDS<br>(132) | 2.375                                                                                                                                                                                                                                                 | 2.5 | 2.625 | 100                                   | _                 | _   | _                        | _                              | _    | _                         | _   | _   | _                          | _    | _     |

$<sup>^{\</sup>left(128\right)}\,$  Differential inputs are powered by VCCPD which requires 2.5 V.

<sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>(130)</sup> RL range:  $90 \le RL \le 110 \Omega$ .

<sup>(131)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.6 V for data rates above 700 Mbps, and 0 V to 1.85 V for data rates below 700 Mbps.

<sup>(132)</sup> There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

| I/O Standard           | Vo    | clo (V) | (128) |     | V <sub>ID</sub> (mV) <sup>(129)</sup> | (129) V <sub>ICM(DC)</sub> (V) |     |                                | Vo    | <sub>D</sub> (V) <sup>(13</sup> | 0)  | V <sub>OCM</sub> (V) <sup>(130)</sup> |     |     |     |

|------------------------|-------|---------|-------|-----|---------------------------------------|--------------------------------|-----|--------------------------------|-------|---------------------------------|-----|---------------------------------------|-----|-----|-----|

| 1/O Standard           | Min   | Тур     | Max   | Min | Condition                             | Max                            | Min | Condition                      | Max   | Min                             | Тур | Max                                   | Min | Тур | Max |

| RSDS<br>(HIO)          | 2.375 | 2.5     | 2.625 | 100 | V <sub>CM</sub> = 1.25 V              | _                              | 0.3 | _                              | 1.4   | 0.1                             | 0.2 | 0.6                                   | 0.5 | 1.2 | 1.4 |

| Mini-<br>LVDS<br>(HIO) | 2.375 | 2.5     | 2.625 | 200 | _                                     | 600                            | 0.4 | _                              | 1.325 | 0.25                            | _   | 0.6                                   | 1   | 1.2 | 1.4 |

| LVPECL                 | _     | _       | _     | 300 | _                                     | _                              | 0.6 | D <sub>MAX</sub> ≤<br>700 Mbps | 1.8   | _                               | _   | _                                     | _   | _   | _   |

| (135), (136)           | _     | _       | _     | 300 | _                                     | _                              | 1   | D <sub>MAX</sub> > 700 Mbps    | 1.6   | _                               | _   | _                                     | _   | _   | _   |

#### **Related Information**

**Glossary** on page 2-73

Altera Corporation

Arria V GZ Device Datasheet

<sup>(128)</sup> Differential inputs are powered by VCCPD which requires 2.5 V.

<sup>(129)</sup> The minimum VID value is applicable over the entire common mode range, VCM.

<sup>(130)</sup> RL range:  $90 \le RL \le 110 \Omega$ .

<sup>(133)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be between 0.25 V to 1.45 V.

<sup>(134)</sup> For optimized Mini-LVDS receiver performance, the receiver voltage input range must be between 0.3 V to 1.425 V.

<sup>(135)</sup> LVPECL is only supported on dedicated clock input pins.

For optimized LVPECL receiver performance, the receiver voltage input range must be between 0.85 V to 1.75 V for data rate above 700 Mbps and 0.45 V to 1.95 V for data rate below 700 Mbps.

| Symbol/Description                                                                                                         | Conditions                                                                | Trans | ceiver Spee  | d Grade 2 | Transc | eiver Spee   | ed Grade 3 | Unit  |  |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------|--------------|-----------|--------|--------------|------------|-------|--|

| Symbol/Description                                                                                                         | Conditions                                                                | Min   | Тур          | Max       | Min    | Тур          | Max        | Offic |  |

| $\label{eq:maximum peak-to-peak differential} \\ input voltage \ V_{ID} \ (diff \ p-p) \ before \\ device \ configuration$ | _                                                                         | _     | _            | 1.6       | _      | _            | 1.6        | V     |  |

| Maximum peak-to-peak differential input voltage V <sub>ID</sub> (diff p-p) after                                           | $V_{\text{CCR\_GXB}} = 1.0 \text{ V}$ $(V_{\text{ICM}} = 0.75 \text{ V})$ | _     | _            | 1.8       | _      | _            | 1.8        | V     |  |

| device configuration (146)                                                                                                 | $V_{\text{CCR\_GXB}} = 0.85 \text{ V}$ $(V_{\text{ICM}} = 0.6 \text{ V})$ | _     | _            | 2.4       | _      | _            | 2.4        | V     |  |

| Minimum differential eye opening at receiver serial input pins (147)(148)                                                  | _                                                                         | 85    | _            | _         | 85     | _            | _          | mV    |  |

|                                                                                                                            | 85– $\Omega$ setting                                                      | _     | 85 ± 30%     | _         | _      | 85<br>± 30%  | _          | Ω     |  |

| Differential on-chip termination                                                                                           | 100–Ω setting                                                             | _     | 100<br>± 30% | _         | _      | 100<br>± 30% | _          | Ω     |  |

| resistors                                                                                                                  | 120–Ω setting                                                             | _     | 120<br>± 30% | _         | _      | 120<br>± 30% | _          | Ω     |  |

|                                                                                                                            | 150– $\Omega$ setting                                                     | _     | 150<br>± 30% | _         | _      | 150<br>± 30% | _          | Ω     |  |

The maximum peak to peak differential input voltage  $V_{ID}$  after device configuration is equal to  $4 \times$  (absolute  $V_{MAX}$  for receiver pin -  $V_{ICM}$ ).

The differential eye opening specification at the receiver input pins assumes that **Receiver Equalization** is disabled. If you enable **Receiver Equalization**, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

<sup>(148)</sup> Minimum eye opening of 85 mV is only for the unstressed input eye condition.

| Mode <sup>(164)</sup> | Transceiver | PMA Width                  | 20  | 20  | 16   | 16   | 10  | 10   | 8    | 8    |

|-----------------------|-------------|----------------------------|-----|-----|------|------|-----|------|------|------|

|                       | Speed Grade | PCS/Core Width             | 40  | 20  | 32   | 16   | 20  | 10   | 16   | 8    |

| Darietan              | 2           | C3, I3L core speed grade   | 9.9 | 9   | 7.92 | 7.2  | 4.9 | 4.,5 | 3.92 | 3.6  |

| Register              | 3           | C4, I4<br>core speed grade | 8.8 | 8.2 | 7.04 | 6.56 | 4.4 | 4.1  | 3.52 | 3.28 |

#### **Related Information**

**Operating Conditions** on page 2-1

#### **10G PCS Data Rate**

Table 2-31: 10G PCS Approximate Maximum Data Rate (Gbps) for Arria V GZ Devices

| Mode (165) | Transceiver Speed | PMA Width                  | 64      | 40      | 40    | 40      | 32       | 32    |

|------------|-------------------|----------------------------|---------|---------|-------|---------|----------|-------|

| Mode       | Grade             | PCS Width                  | 64      | 66/67   | 50    | 40      | 64/66/67 | 32    |

| FIFO       | 2                 | C3, I3L core speed grade   | 12.5    | 12.5    | 10.69 | 12.5    | 10.88    | 10.88 |

| FIFO       | 3                 | C4, I4 core speed<br>grade | 10.3125 | 10.3125 | 10.69 | 10.3125 | 9.92     | 9.92  |

| Register   | 2                 | C3, I3L core speed grade   | 12.5    | 12.5    | 10.69 | 12.5    | 10.88    | 10.88 |

| register   | 3                 | C4, I4 core speed<br>grade | 10.3125 | 10.3125 | 10.69 | 10.3125 | 9.92     | 9.92  |

<sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

<sup>(165)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

| Symbol      | Parameter                                                     | Min    | Тур     | Max        | Unit |

|-------------|---------------------------------------------------------------|--------|---------|------------|------|

| $k_{VALUE}$ | Numerator of Fraction                                         | 128    | 8388608 | 2147483648 | _    |

| $f_{RES}$   | Resolution of VCO frequency ( $f_{INPFD} = 100 \text{ MHz}$ ) | 390625 | 5.96    | 0.023      | Hz   |

#### **Related Information**

- Duty Cycle Distortion (DCD) Specifications on page 2-56

- DLL Range Specifications on page 2-53

### **DSP Block Specifications**

Table 2-35: DSP Block Performance Specifications for Arria V GZ Devices

| Mode                                                           | Performance |     |     | Unit |

|----------------------------------------------------------------|-------------|-----|-----|------|

|                                                                | C3, I3L     | C4  | 14  | Unit |

| Modes using One DSP Block                                      |             |     |     |      |

| Three 9 × 9                                                    | 480         | 420 |     | MHz  |

| One 18 × 18                                                    | 480         | 420 | 400 | MHz  |

| Two partial $18 \times 18$ (or $16 \times 16$ )                | 480         | 420 | 400 | MHz  |

| One 27 × 27                                                    | 400         | 350 |     | MHz  |

| One 36 × 18                                                    | 400         | 350 |     | MHz  |

| One sum of two $18 \times 18$ (One sum of two $16 \times 16$ ) | 400         | 350 |     | MHz  |

| One sum of square                                              | 400         | 350 |     | MHz  |

| One $18 \times 18$ plus $36$ (a × b) + c                       | 400         | 350 |     | MHz  |

| Modes using Two DSP Blocks                                     |             |     |     |      |

| Three 18 × 18                                                  | 400         | 350 |     | MHz  |

| One sum of four $18 \times 18$                                 | 380         | 300 |     | MHz  |